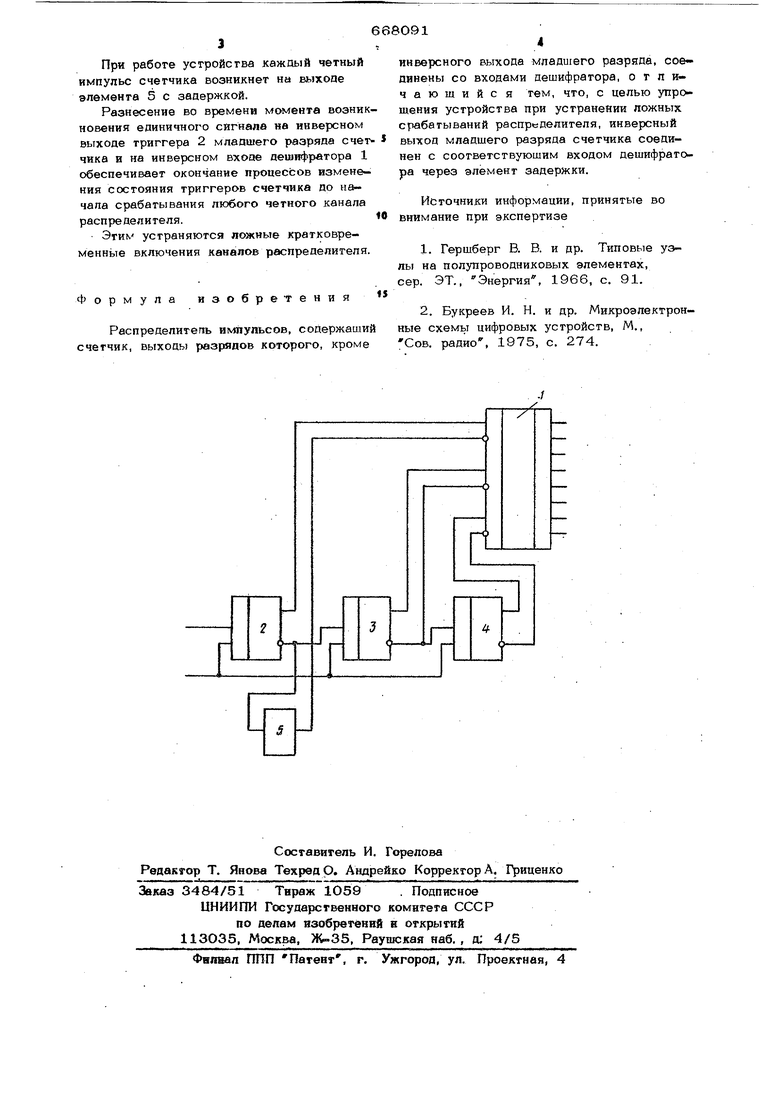

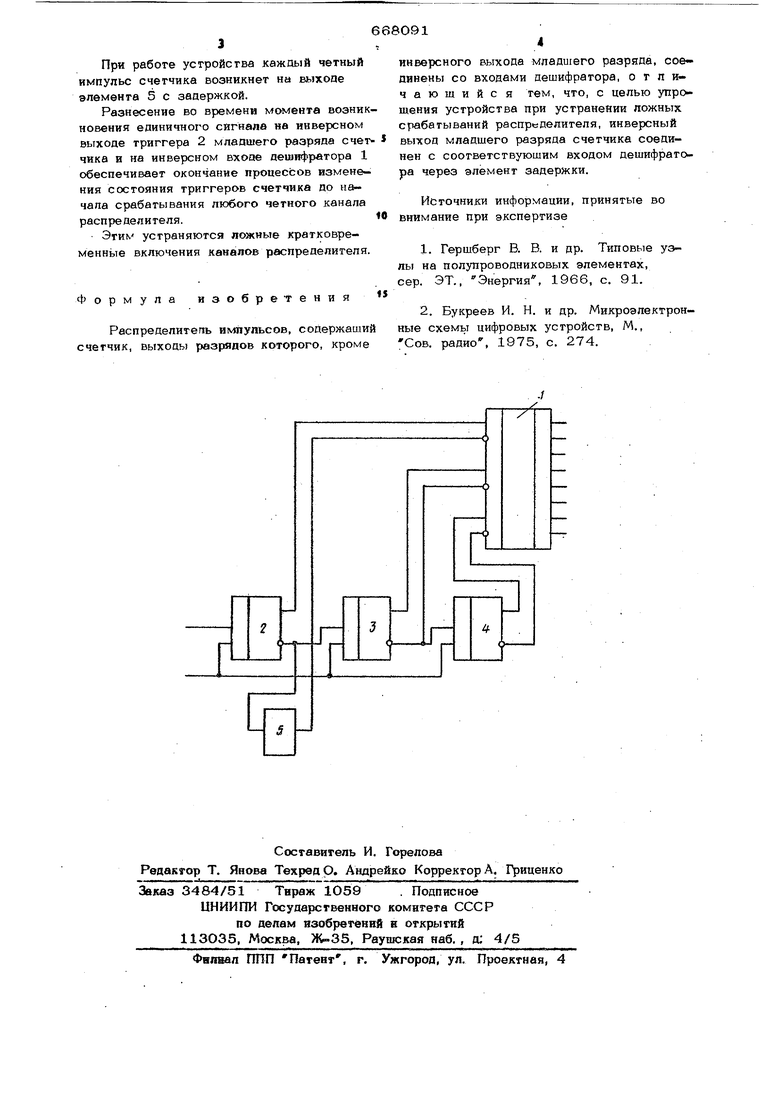

Изобретение относится к автоматике и вычислительной технике. Известны распределители импульсов, содержащие двоичный счетчик и дешифратор. Такой распределитель имеет низкое быстродействие. Наиболее близким техническим решением к данному изобретению является распределитель импульсов, содержащий счетчик импульсов, вь1ход разрядов которого, кроме инверсного выхода младшего разряда, подключен к выходам дешифратора, фик сируюшего состояние счетчика 2. Недостатком такого -устройства является кратковременное ложное включение всех четных каналов распределителя.импульсов при построении последнего на однотактных быстродействующих счетчиках последовательного и параллельно-последовательного типа. Целью изобретения является упрощение устройсава при устранении ложных срабатываний распределителя. Указанная цель достигается тем, что в устройстве инверсный выход младшего разряда счетчика соединен с соответствующим входом дешифратора через элемент задержки. На чертеже показана функциональпая блок-схема, предлагаемого устройства, выполненного на потенциальных элементах с числом разрядов счетчика, равным трем. Устройство содержит дешифратор 1, счетчик на триггерах 2-4 со счетными и установочными входами и элемент 5 задержки. Триггеры 2-4 соединены в цепь дво11Чного счетчика со счетным и установочным входами. Прямой выход триггера 2 и прямые и инверсные выходы триггеров 3 и 4 соеди- HeHEii с соот тствуюшими входами дешифратора 1, инверсный-выход триггера 2 младшего разряда счетчика соединен с соответствующим входом дешифратора 1 через элемент 5. При работе устройства каждый четный импульс счетчика возникнет на выходе элемента 5 с задержкой. Разнесение во времени момента возник новения единичного сигнала на инверсном выходе триггера 2 младшего разряда счет чика и на инверсном входе дешифратора 1 обеспечивает окончание процессов изменения состояния триггеров счетчика до начала срабатывания любого четного канала распределителя. Этим устраняются ложные кратковременные включения каналов распределителя Формула изобретения Распределитегть импупьсов, содержащий счетчик, выходы разрядов которого, кроме инверсного выхода младшего разряда, соединены со входами дешифратора, отличающийся тем, что, с целью упрощения устройства при устранении ложных срабатываний распределителя, инверсный выход младшего разряда счетчика соединен с соответствующим входом дешифратора через элемент задержки. Источники информации, принятые во внимание при экспертизе 1.Гершберг В. В. и др. Типовые уэлы на полупроводниковых элементах, сер. ЭТ., Энергия, 1966, с. 91. 2.Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств, М., Сов. радио, 1975, с. 274.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1990 |

|

SU1784963A1 |

| Устройство для коррекции сбойных кодов в кольцевом распределителе | 1979 |

|

SU888125A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1314388A1 |

| Управляемый делитель частоты импульсов | 1983 |

|

SU1088135A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU333552A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Генератор функций Хаара | 1987 |

|

SU1449982A1 |

| Делитель частоты импульсов | 1985 |

|

SU1298907A1 |

Авторы

Даты

1979-06-15—Публикация

1975-07-31—Подача