и два элемента ИЛИ, причем первый управляющий вход блока соединен с первыми входами первых элементов ИЛИ и И,- выход регистра памяти фазы соединен с вторым входом первого элемента И, выход которого соединен с первым входом счетчика импульсов и входом триггера пуска, первый выход которого соединен с первым входом второго элемента И, другой вход которого соединен с синхронизирующим входом блока/7 а выход второго элемента И соединен с первым разрешающим выходом блока и с вторым,входом счетчика импульсов, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с третьим входом счетчика импульсов, вторым входом триггера пуска и вторым разрешающим выходом блока, второй управляющий вход которого соединен с третьим входом первого элемента ИЛИ, четвертый вход последнего соединен с формирователем импульсов сброса второй выход триггера пуска соединен с первым входом третьего элемента И., второй вход которого соединен с выходом второго элемента ИЛИ, а выход третьего элемента И соединен с первым входом триггера пуска/ первый и второй запускающие входы блока соединены соответственно с первыми входами четвертого и пятого элементов И, вторые входы которых соединены с входом готовности блока, третьи входы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ

3. Устройство по п. 1, отличающееся тем, что блок управления приемом содержит триггер, элемент задержк три элемента И и элемент НЕ, причем первый разрешающий выход блока соединен с входом элемента задержки и выходом триггера. пер.вый выход которого соединен с выходом элемента задержки, дыход первого элемента И соединен с вторым разрешающим выходом блока и вторым входом триггера,- третий вход которого соединен с выходом- второго элемента И и дервым входом третьего элемента ИЛИ, второй вход которого соединен с выходом элемента;НЕ, а выход третьего элемента И соединен с зaдaющи;v{ выходом блока, первый установочный вход блока соединен с первым входом второго элемента И, второй установочный, вход - с входом элемента НЕ и первым входом первого элемента И| а третий установочный вход - с вторыми входами первого и второго элементов И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1980 |

|

SU935939A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными | 1979 |

|

SU842778A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство ввода-вывода информации | 1988 |

|

SU1619283A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

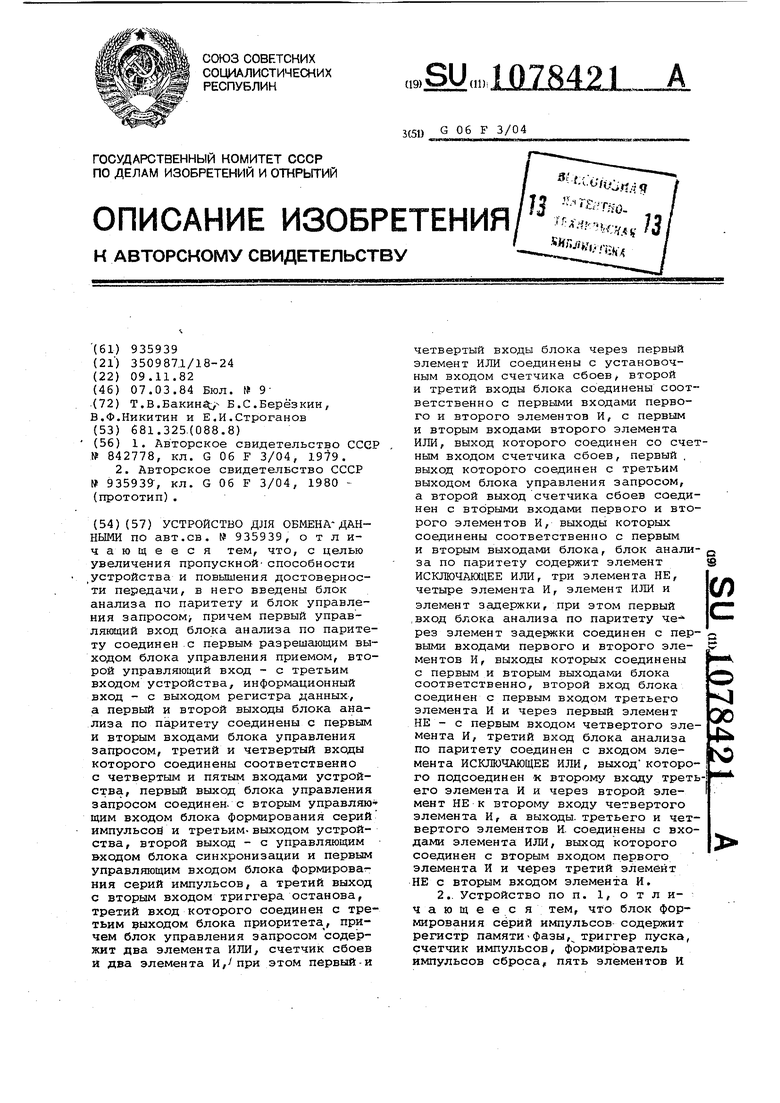

УСТРОЙСТВО ДЛЯ ОБМЕНА-ДАННЫМИ по авт.св. № 935939, отличающееся тем, что, с целью увеличения пропускной- способности устройства и повышения достоверности передачи, в него введены блок анализа по паритету и блок управления запросом причем первый управляющий вход блока анализа по паритету соединен с первым разрешающим выходом блока управления приемом, второй управляющий вход - с третьим входом устройства информационный вход - с выходом регистра данных, а первый и второй выходы блока анализа по паритету соединены с первым и вторым входами блока управления запросом, третий и четвертый входы которого соединены соответственно с четвертым и пятым входами устройства, первый выход блока управления запросом соединен, с вторым управляю щим входом блока формирования серий импульсов и третьим.выходом устройства, второй выход - с управляющим входом блока синхронизации и первым управляющим входом блока формироваг ния серий импульсов, а третий выход с вторым входом триггера останова, третий вход которого соединен с третьим 9ЫХОДОМ блока приоритета, причем блок управления запросом содержит два элемента ИЛИ счетчик сбоев И два элемента И, этом первый-и четвертый входы блока через первый элемент ИЛИ соединены с установочным входом счетчика сбоев, второй и третий входы блока соединены соответственно с первыми входами первого и второго элементов И, с первым и вторым входами второго элемента ИЛИ, выход которого соединен со счетным входом счетчика сбоев, первый , выход которого соединен с третьим выходом блока управления запросом, а второй выход счетчика сбоев соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым выходами блока, блок анализа по паритету содержит элемент t ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента НЕ, (Л четыре элемента И, элемент ИЛИ и элемент задержки, при этом первый ,вход блока анализа по паритету че- рез элемент задержки соединен с первыми входами первого и второго элементов И, выходы которых соединены с первым и вторым выхощами блока соответственно, второй вход блока соединен с первым входом третьего элемента И и через первый элемент НЕ - с первым входом четвертого элемента И, третий вход блока анализа по паритету соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подсоединен к второму вхсду треть- его элемента И и через второй элемент НЕ к второму входу четвертого элемента И, а выходы, третьего и четвертого элементов И. соединены с входами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и через третий элемент НЕ с вторым входом элемента И. 2.. Устройство по п. 1, отличающееся тем, что блок формирования серий импульсов содержит регистр памятифазы, триггер пуска, счетчик импульсов, формирователь импульсов сброса, пять элементов И

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано для сопряжения устройств с различными скоростями обмена информа1 1;иеЙ1

По основному авт. св. № 935939 известно устройство для обмена данными, содержащее блок приоритета, первый и второй выходы которого соединены соответственно о первым и вторым режимными входами блока синхронизации, блок управления выдачей, разрешающий выход которого соединен с управляющим входом коммутатора, регистр признаков, разрешающий выход-которого соединен с первым управляющим входом входного коммутатора. блок управления приемом, первый разрешающий выход которого соединен с управляющим входом регистра данных, триггер останова, выход которого соединен с ус тановочными входами регистра признаков и блока приоритета, причем первый запросный вход блока приоритета и первый информационный вхсщ

входного коммутатора, второй запросный вход блока приоритета и второй информационный вход входного комму- , татора соединен соответственно с

первым и вторым входа1 ш устройства, третий вход устройства соединен с входом готовности регистра признаков, первый и второй информационные входы которого соединены соответственQ НО с первым и вторым выходами блока приоритета., первый, второй, третий признаковые выходы регистра признаков соединены соответственно с первым, вторым установочными входай пя

с блока управления приемом и первым установочным входом блока управления выдачей, второй установочный вход блоки управления выдачей и третий установочный вход блока управления приемом соединены соответственно

с первым и вторым разрешающими выходами блока синхронизации/ задающие выходы блоков управления выдачей и приемом соединены с входом триггера останова, второй разрешающий выход блока управления приемом соединен с вторым упралякхцим входом входного

коммутатора, выход которо,го соединен с информационным входом регистра данных, а выход регистра данных соединен с информационнЕлм входом выходного коммутатора, выходы которого являются первым и вторым выходами устройства, блок формирования серии импульсов, синхронизирующий вход и вход готовности, первый и второй запускающие входы которого соединены соответственно с тактовым выходом блока синхронизации, с третьим входом устройства, с первым и вторым выходами блока приоритета, а первый и второй разрешающие выходы блока формирования серии импульсов соединены соответственно с первым и вторым запускающими входами блока синхронизации.

Известное устройство позволяет сопрягать ра зноскоростные устройства, обеспечивает достаточную скорость обмена при отсутствии ошибок при передаче информации 1 и 2

Однако, при ошибок и сбоев в известном устройстве приходится повторно передавать весь массив информации, что значительно снижает пропускную способность системы, в которой работает устройство.

Цель изобретения - увеличение пропускной способности устройства и повышени.е достоверности передачи.

Поставленная цель достигается тем что в устройство для обмена данными введены блок анализа по паритету и блок управления запросом, причем первый управляющий вход блока анализа по паритету соединен с первым разрешающим выходом блока управления приемом, второй управляющий вход с - третьим входом устройства, информационный вход - с выходом регистра данных, а первый и второй выходы блока анализа по паритету соединены с первым и вторым входами блока управления запросом, третий и четвертый входы которого соединены соответственно с четвертым и пятым входами устройства, первый выход блока управления запросом соединен с вторым управляющим входом блока формирования серий импульсов и третьим выходом устройства, второй выход - с управляющим входом блока синхронизации и первым управляющим входом блока формирования серий импульсов, а третий выход - с вторым входом триггера останова, третий рход которого соединен с третьим выходом блока приоритета, причем блок управления запросом содержит два элемента ИЛИ, счетчик сбоев и два элемента И, при этом первый и четвертый входы блока через первый элемент ИЛИ соединены с установочным входом счетчика сбоев, второй и третий входы блока coeдинены соответственно с первыми вхо

дами первого и второго элементов И, с первым и вторым входами второго элемента ИЛИ, выход которого соединен со счетным входом счетчика сбоев, первый выход которого соединен с третьим выходом блока управления запросом, а второй выход счетчика сбоев соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым выходами блока, блок анализа по паритету содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛ11, три элемента НЕ, четыре элемента И, элемент ИЛИ и элемент задержки, при этом первый вход блока анализа по паритету через элемент задержки соединен с первыми входами первого и второго элементов И, выходы которых соединены с первым и вторым выходами блока соответственно, второй вход блока соединен с первым входом третьего элемента И и через первый элемент НЕ - с первым входом четвертого элемента И, третий вход блока анализа по паритету соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подсоединен к второму входу третьего элемента через второй элемент НЕ к второму входу четвертого элемента И, а выходы третьего и четвертого элементов И соединены с входами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и через третий элемент НЕ с вторым входом элемента и.

Кроме того, блок формирования серий импульсов содержит регистр памяти фазы, триггер пуска, счетчик импульсов ,формирователь импульсов сброса, пять элементов И и два элемента ИЛИ, причем первый управляющий вход блока соединен с первыми входами первых элементов ИЛИ и И, выход регистра памяти фазы соединен с вторым входом первого элемента И, выход которого соединен с первым входом счетчика импульсов и входом триггера пуска, первый выход которого соединен с первым входом второго элемента И, другой вход которого соединен с синхронизирующим входом блока, а выход второго элемента И соединен с первым разрешающим выходом блока и с вторым входом счетчика импульсов выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с третьим входом счетчика импульсов, вторым входом триггера пуска и вторым разрешающим выходом блока, второй управляющий вход которого соединен с третьим входом первого элемента ИЛИ, четвертый вход последнего соединен с формирователем импульсов сброса, второй выход триггера пуска соединен с первым входом третьего элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, а выход третьего элемента И соединен с первым входом триггера пуска, первый и второй запускающие входы блока соединены соответственно с первыми входами четвертого и пятого элементов вторые входы которых соединены с входом готовности блока, третьи входы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ.

Причем блок управления приемом содержит триггер, элемент задержки, три элемента И и элемент НЕ, причем первый разрешающий выход блока соединен с входом элемента задержки и выходом триггера-, первый выход которого соединен с выходом элемента задержки, выход первого элемента И соединен с вторым разрешающим выходом блока и вторым входом триггера, третий вход которого соединен с выходом второго элемента И и первым входом третьего элемента ИЛИ, второ вход которого соединен с вьаходом элемента НЕ, а выход третьего элемента И соединен с задающим выходом блока, первый установочный вход блока соединен с первым -входом второго элемента И, второй установочный вхо с входом элемента НЕ и первым входо первого элемента И, третий установоный вход - с вторыми входами первого и второго элементов И.

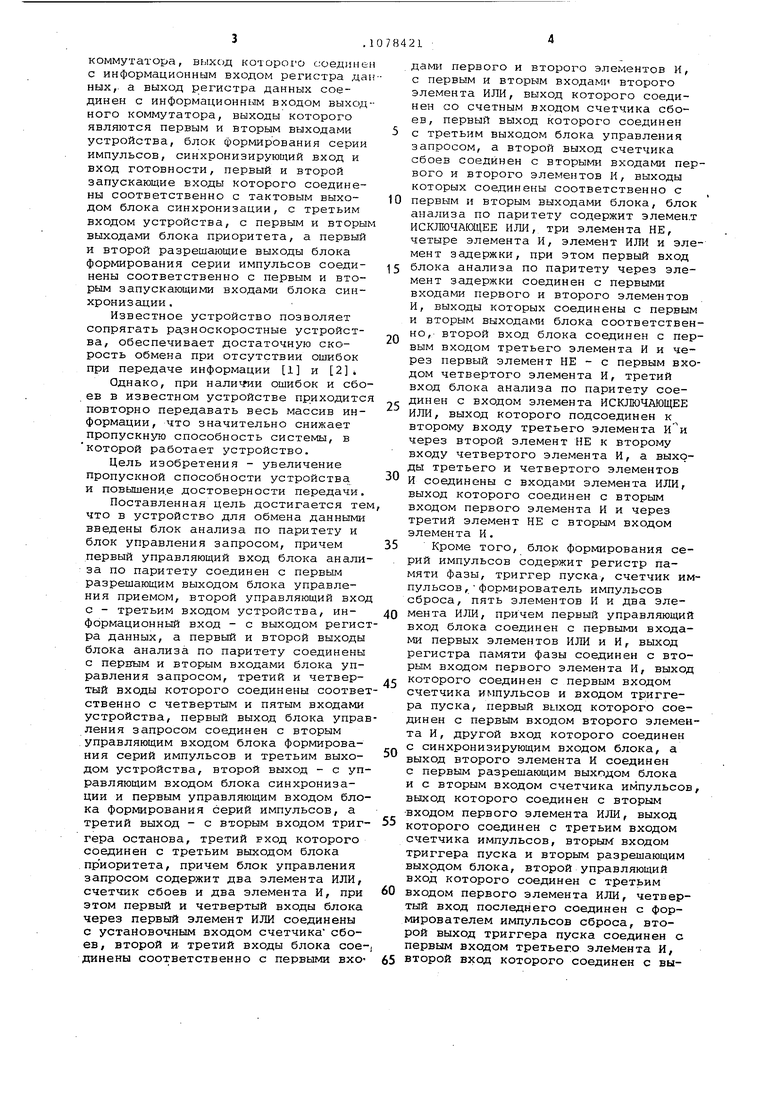

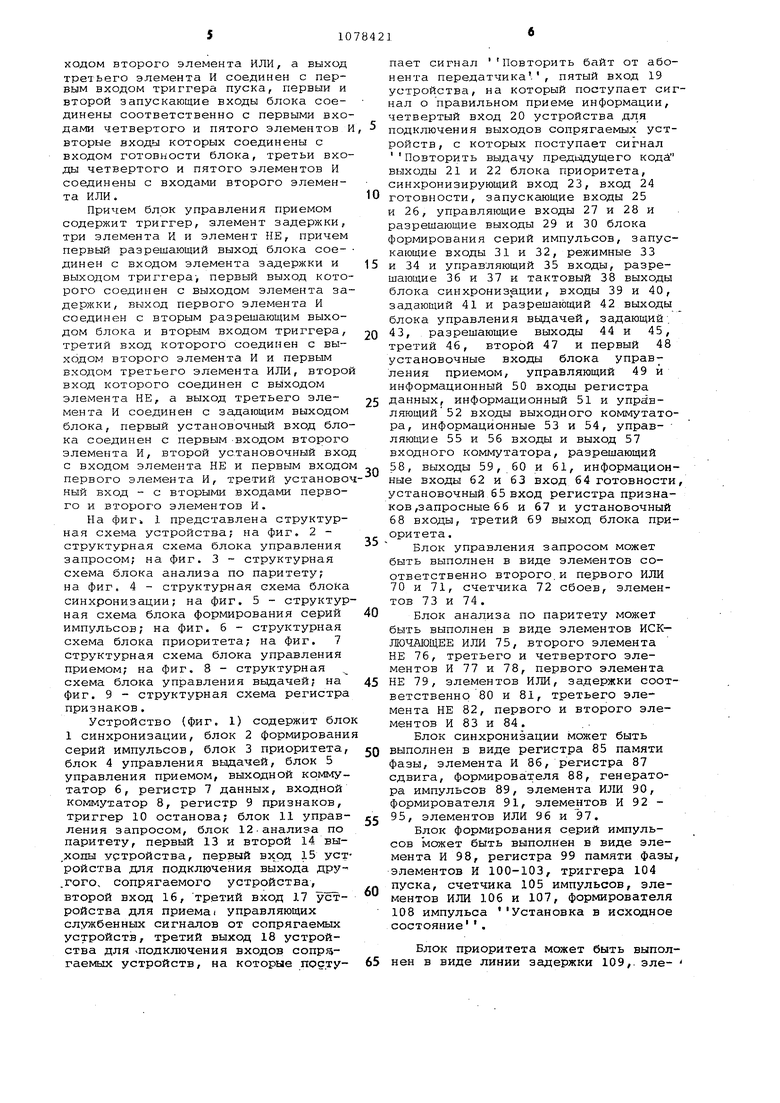

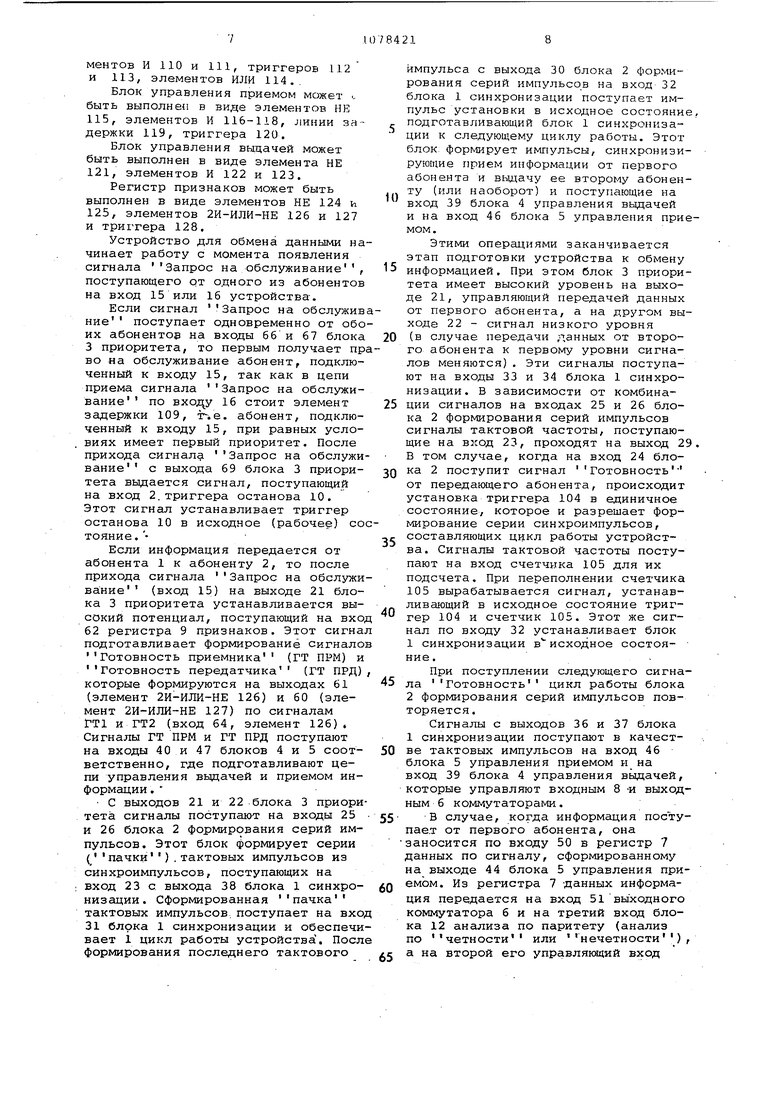

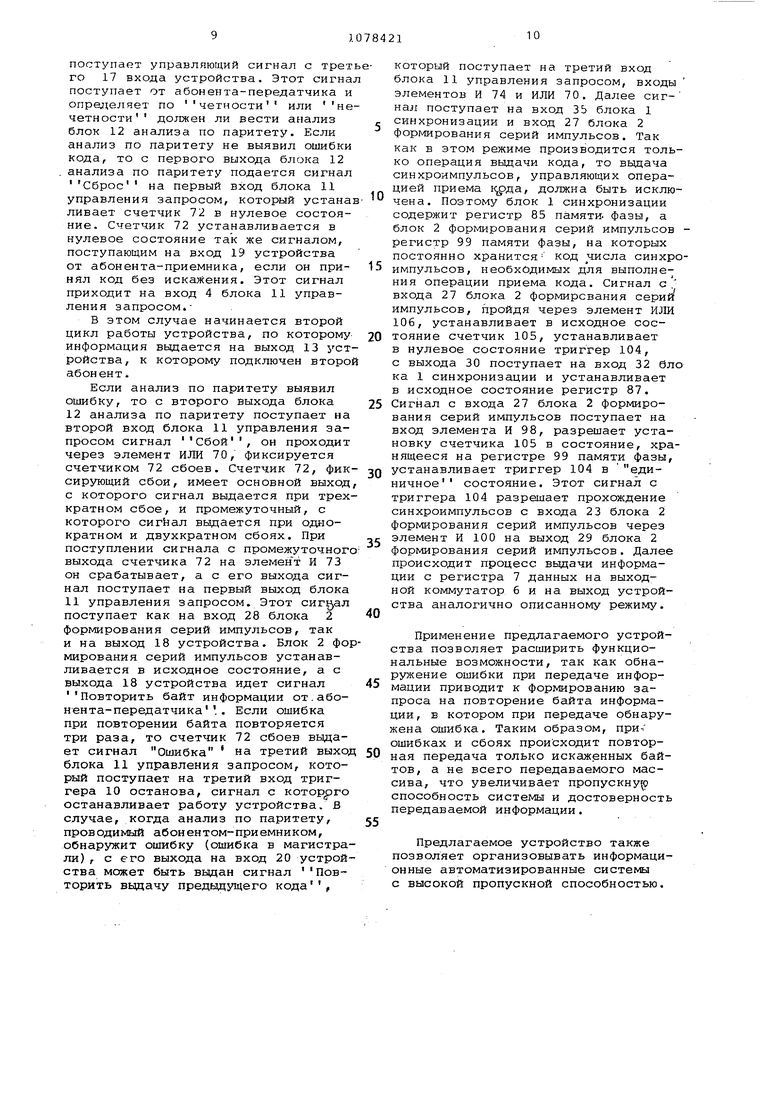

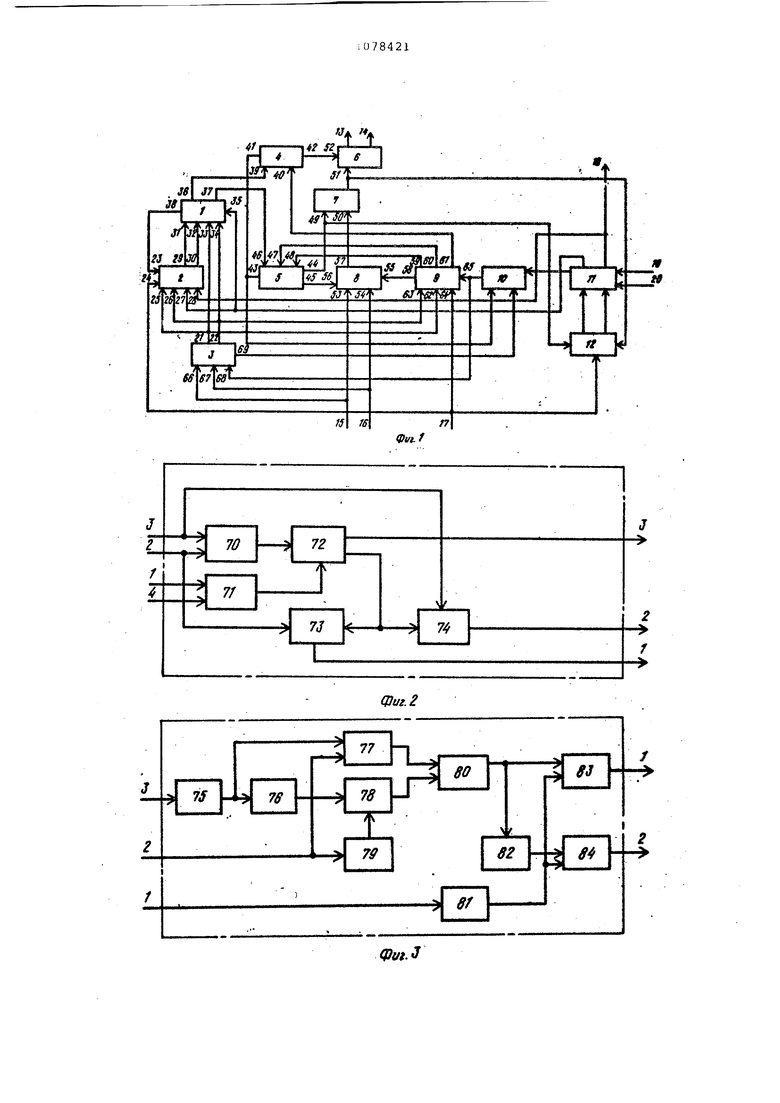

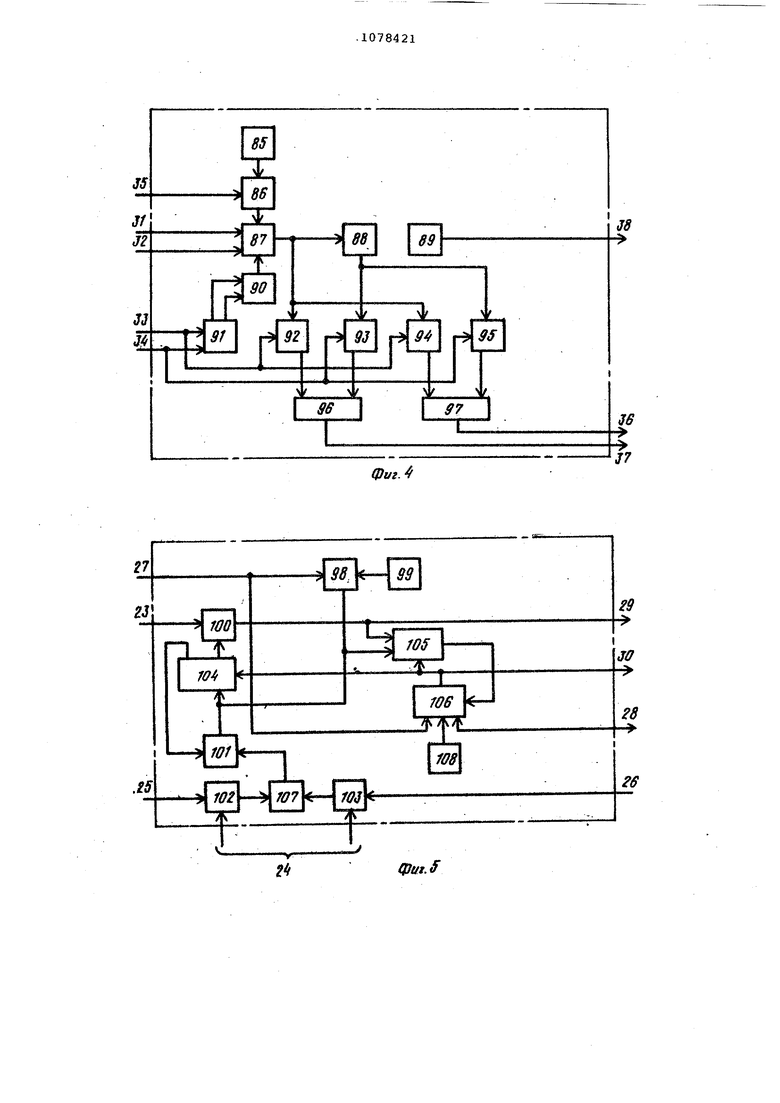

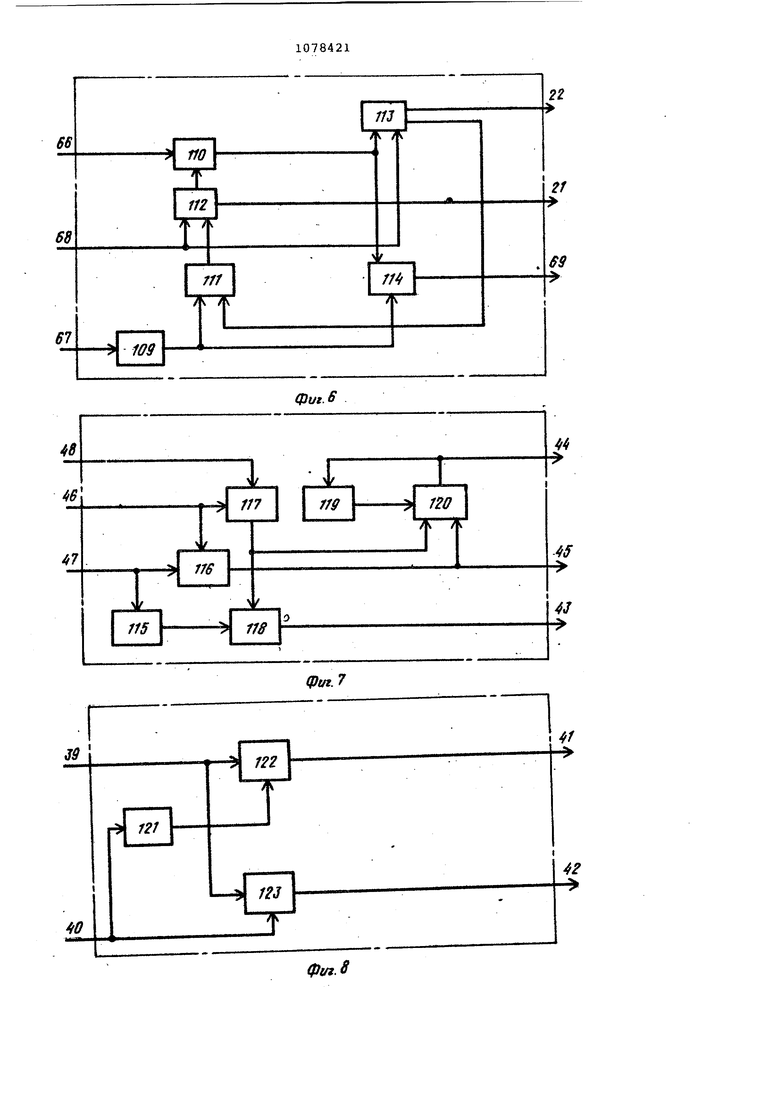

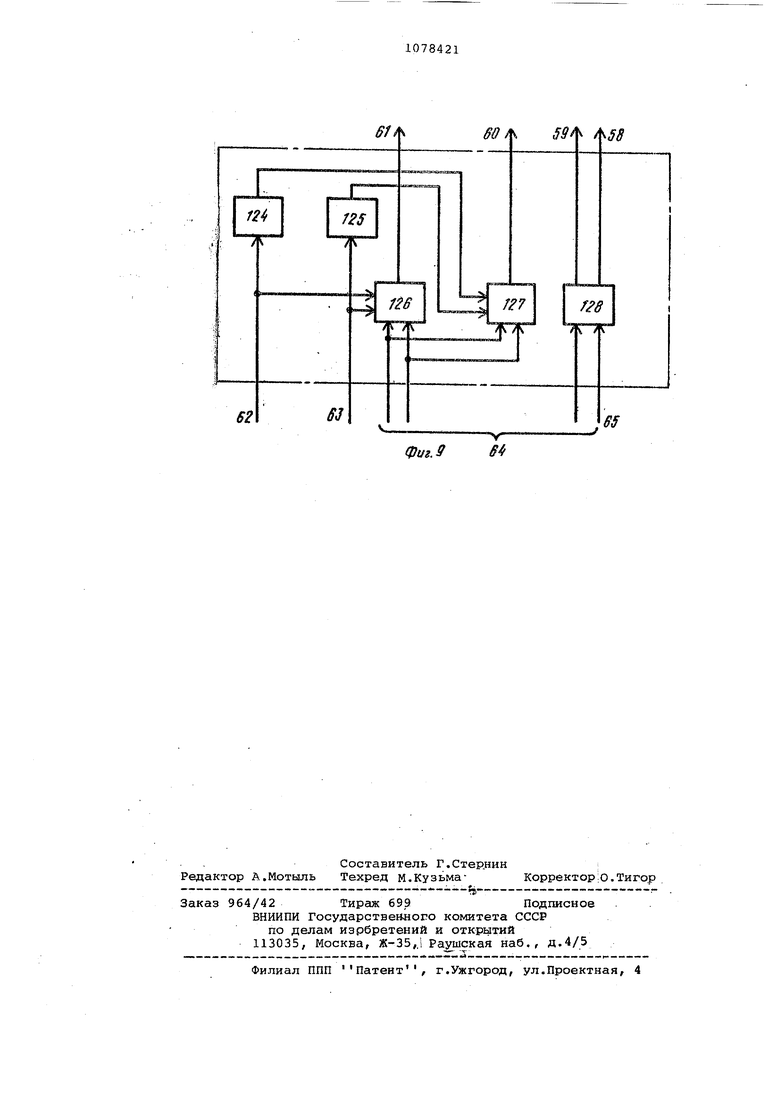

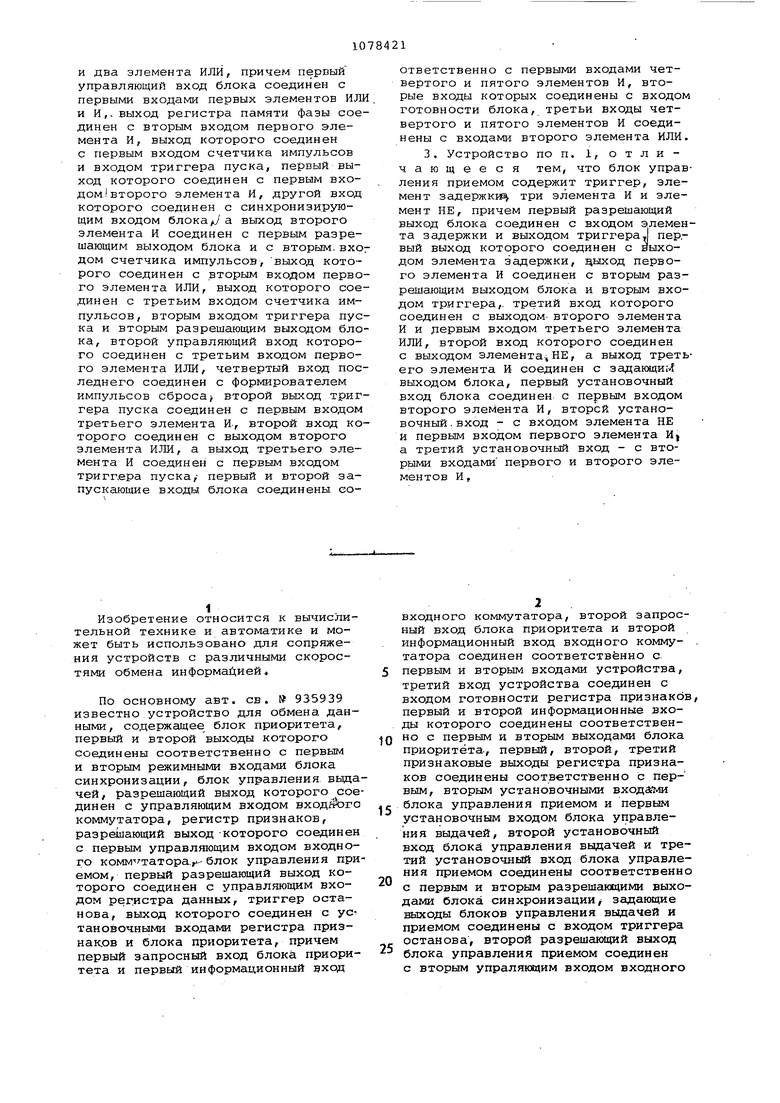

На фиг 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока управления запросом; на фиг. 3 структурная схема блока анализа по паритету; на фиг. 4 - структурная схема блока синхронизации; на фиг. 5 - структурная схема блока формирования серий импульсов; на фиг. 6 - структурная схема блока приоритета; иа фиг. 7 структурная схема блока управления приемом; на фиг. 8 - структурная схема блока управления выдачей; на фиг. 9 структурная схема регистра признаков.

Устройство (фиг. 1) содержит бло 1 синхронизации, блок 2 формировани серий импульсов, блок 3 приоритета, блок 4 управления выдачей, блок 5 управления приемом, выходной коммутатор 6, регистр 7 данных, входной коммутатор 8, регистр 9 признаков, триггер 10 останова; блок 11 управления запросом, блок 12-анализа по паритету, первый 13 и второй 14 вн.ходы устройства, первый вход 15 устройства для подключения выхода дру-.гого, сопрягаемого устройства, второй вход 16, третий вход 17 устройства для приема, управляющих службенньлх сигналов от сопрягаемых устройств, третий выход 18 устройства для подключения входов сопрягаемых устройств, на которые поступает сигнал Повторить байт от абонента передатчика-, пятый вход 19 устройства, на который поступает синал о правильном приеме информации, четвертый вход 20 устройства для подключения выходов сопрягаемых устройств, с которых поступает сигнал Повторить выдачу предыдущего кода выходы 21 и 22 блока приоритета, синхронизирующий вход 23, вход 24 готовности, запускающие входы 25 и 26, управляющие входы 27 и 28 и разрешающие выходы 29 и 30 блока формирования серий импульсов, запускающие входы 31 и 32, режимные 33 и 34 и управляющий 35 входы, разрешающие 36 и 37 и тактовый 38 выходы блока синхронизации, входы 39 и 40, задающий 41 и разрешающий 42 выходы блока управления выдачей, задающий. 43, разрешающие выходы 44 и 45, третий 46, второй 47 и первый 48 установочные входы блока управления приемом, управляющий 49 и информационный 50 входы регистра данных, информационный 51 и управляющий 52 входы выходного коммутатора, информационные 53 и 54, управ- ляющие 55 и 56 входы и выход 57 входного коммутатора, разрешающий 58, выходы 59, 60 и 61, информационные входы 62 и 63 вход 64 готовности установочный 65 вход регистра признаков,запросные 66 и 67 и установочный 68 входы, третий 69 выход блока приоритета.

Блок управления запросом может быть выполнен в виде элементов соответственно второго.и первого ИЛИ 70 и 71, счетчика 72 сбоев, элементов 73 и 74.

Блок анализа по паритету может быть выполнен в виде элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 75, второго элемента НЕ 76, третьего и четвертого элементов И 77 и 78, первого элемента НЕ 79, элементов ИЛИ, задержки соответственно 80 и 81, третьего элемента НЕ 82, первого и второго элементов И 83 и 84.

Блок синхронизации может быть выполнен в виде регистра 85 памяти фазы, элемента И 86, регистра 87 сдвига, формирователя 88, генератора импульсов 89, элемента ИЛИ 90, формирователя 91, элементов И 92 95, элементов ИЛИ 96 и 97.

Блок формирования серий импульсов мажет быть выполнен в виде элемента И 98, регистра 99 памяти фазы элементов И 100-103, триггера 104 пуска, счетчика 105 импульсов, элементов ИЛИ 106 и 107, формирователя 108 импульса Установка в исходное состояние.

Блок приоритета может быть выполнен в виде линии задержки 109,. злементов И 110 и 111, триггеров 112 и 113, элементов ИЛИ 114.. Блок управления приемом может ., быть выполнен в виде элементов НЕ 115, элементов И 116-118, линии задержки 119, триггера 120. Блок управления вы,цачей может быть выполнен в виде элемента НЕ 121, элементов И 122 и 123. Регистр признаков может быть выполнен в виде элементов НЕ 124 и 125, элементов 2И-ИЛИ-НЕ 126 и 127 и триггера 128. Устройство для обмена данными на чинает работу с момента появления сигнала Запрос на обслуживание, поступающего от одного из абонентов на вход 15 или 16 устройства. Если сигнал Запрос на обслужив ние поступает одновременно от обо их абонентов на входы 66 и 67 блока 3 приоритета, то первым получает пр во на обслуживание абонент, подключенный к входу 15, так как в цепи приема сигнала Запрос на обслуживание по 16 стоит элемент задержки 109, Ь/е. абонент, подключенный к входу 15, при равных условиях имеет первый приоритет. После прихода сигнала Запрос на обслужи вание с выхода 69 блока 3 приоритета выдается сигнал, поступающий на вход 2.триггера останова 10. Этот сигнсш устанавливает триггер останова 10 в исходное (рабочее) со тояние. Если информация передается от абонента 1 к абоненту 2, то после прихода сигнала Запрос на обслужи ва:ние (вход 15) на выходе 21 блока 3 приоритета устанавливается высокий потенциал, поступающий на вхо 62 регистра 9 признаков. Этот сигна подготавливает формирование сигнало Готовность приемника (ГТ ПРИ) и Готовность передатчика (ГТ ПРД) которые формируются на выходах 61 (элемент 2И-ИЛИ-НЕ 126) и 60 (элемент 2И-ИЛИ-НЕ 127) по сигналам ГТ1 и ГТ2 (вход 64, элемент 126). Сигналы ГТ ПРИ и ГТ ПРД поступают на входы 40 и 47 блоков 4 и 5 соответственно, где подготавливают цепи управления выдачей и приемом информации . С выходов 21 и 22 блока 3 приори тета сигналы поступают на входы 25 и 26 блока 2 формирования серий импульсов. Этот блок формирует серии (пачки).тактовых импульсов из синхроимпульсов, поступающих на вход 23 с выхода 38 блока 1 синхронизации. Сформированная пачка тактовых импульсов, поступает на вхо 31 блока 1 синхронизации и обеспечи вает 1 цикл работы устройства. Посл формирования последнего тактового импульса с выхода 30 блока 2 формирования серий импульсов на вход 32 блока 1 синхронизации поступает импульс установки в исходное состояние, подготавливающий блок 1 синхронизации к следующему циклу работы. Этот блок, формирует импульсы, синхронизирующие прием информации от первого абонента и выдачу ее второму абоненту (или наоборот) и поступающие на вход 39 блока 4 управления выдачей и на вход 46 блока 5 управления приемом. Этими операциями заканчивается этап подготовки устройства к обмену информацией. При этом блок 3 приоритета имеет высокий уровень на выходе 21, управляющий передачей данных от первого абонента, а на другом выходе 22 - сигнал низкого уровня (в случае передачи ланных от второго абонента к первому уровни сигналов меняются). Эти сигналы поступают на входы 33 и 34 блока 1 синхронизации. В зависимости от комбинации сигналов на входах 25 и 26 блока 2 формирования серий импульсов сигналы тактовой частоты, поступающие на вход 23, проходят на выход 29. В том случае, когда на вход 24 блока 2 поступит сигнал Готовность от передающего абонента, происходит установка триггера 104 в единичное состояние, которое и разрешает формирование серии синхроимпульсов, составляющих цикл работы устройства. Сигналы тактовой частоты поступают на вход счетчика 105 для их подсчета. При переполнении счетчика 105 вырабатывается сигнал, устанавливающий в исходное состояние триггер 104 и счетчик 105. Этот же сигнал по входу 32 устанавливает блок 1синхронизации неисходное состояние. При поступлении следующего сигнала Готовность цикл работы блока 2формирования серий импульсов повторяется. Сигналы с выходов 36 и 37 блока 1 синхронизации поступаиот в качестве тактовых импульсов на вход 46 блока 5 управления приемом и на вход 39 блока 4 управления вьщачей, которые управляют входным 8 « выходным 6 коммутаторами. В случае, когда информация поступает от первого абонента, она заносится по входу 50 в регистр 7 данных по сигналу, сформированному на выходе 44 блока 5 управления приемом. Из регистра 7 данных информация передается на вход 51 выходного коммутатора 6 и на третий вход блока 12 анализа по паритету (анализ по четности или нечетности ), а на второй его управлякхдий вход

поступает управляющий сигнал с третго 17 входа устройства. Этот сигна поступает от абонента-передатчика и определяет по четности или нечетности должен ли вести анализ блок 12 анализа по паритету. Если анализ по паритету не выявил ошибки кода, то с первого выхода блока 12 . анализа по паритету подается сигнал Сброс на первый вход блока И управления запросом, который устава ливает счетчик 12 s нулевое состояние. Счетчик 72 устанавливается в нулевое состояние так же сигналом, поступающим на вход 19 устройства от абонента-приемника, если он принял код без искажения. Этот сигнал приходит на вход 4 блока 11 управления запросом.В этом случае начинается второй цикл работы устройства, по которому информация выдается на выход 13 устройства, к которому подключен второ абонент i

Если анализ по паритету выявил ошибку, то с второго выхода блока 12 анализа по паритету поступает на второй вход блока 11 управления запросом сигнал Сбой, он проходит через элемент ИЛИ 70, фиксируется счетчиком 72 сбоев. Счетчик 72, фик сирующий сбои, имеет основной выход с которого сигнал выдается при трехкратном сбое, и промежуточный, с которого сигнал выдается при однократном и двухкратном сбоях. При поступлении сигнала с промежу точног выхода счетчика 72 на элемент И 73 он срабатывает, а с его выхода сигнал поступает на первый выход блока 11 управления запросом. Этот сигнал поступает как на вход 28 блока 2 формирования серий импульсов, так и на выход 18 устройства. Блок 2 фомирования серий импульсов устанавливается в исходное состояние, а с выхода 18 устройства идет сигнал Повторить байт информации от.абонента-передатчика .. Если ошибка при повторении байта повторяется три раза, то счетчик 72 сбоев выдает сигнал Ошибка на третий выход блока 11 управления запросом, который поступает на третий вход триггера 10 останова, сигнал с которого останавливает работу устройства. В случае, когда анализ по паритету, проводимый абонентом-приемником, обнаружит ошибку (ошибка в магистрали) f с его выхода на вход 20 устройства может быть выдан сигнал Повторить вьщачу предыдущего кода,

который поступает на третий вход блока 11 управления запросом, входы элементов И 74 и ИЛИ 70. Далее сигнал поступает на вход 35 блока 1 синхронизации и вход 27 блока 2 формирования серий импульсов. Так как в этом режиме производится только операция выдачи кода, то выдача синхроимпульсов, управляющих операцией приема 1фда, должна быть исключена. Поэтому блок 1 синхронизации содержит регистр 85 памяти- фазы, а блок 2 формирования серий импульсов регистр 99 памяти фазы, на которых постоянно хранится- код числа синхримпульсов, необходимых для выполнения операции приема кода. Сигнал с входа 27 блока 2 формирования серии импульсов, пройдя через элемент ИЛИ 106, устанавливает в исходное состояние счетчик 105, устанавливает в нулевое состояние триггер 104, с выхода 30 поступает на вход 32 бл ка 1 синхронизации и устанавливает в исходное состояние регистр 87. Сигнал с входа 27 блока 2 формирования серий импульсов поступает на вход элемента И 98, разрешает установку счетчика 105 в состояние, хранящееся на регистре 99 памяти фазы, устанавливает триггер 104 в единичное состояние. Этот сигнал с триггера 104 разрешает прохождение синхроимпульсов с входа 23 блока 2 формирования серий импульсов через элемент И 100 на выход 29 блока 2 формирования серий импульсов. Далее происходит процесс вьщачи информации с регистра 7 данных на выходной коммутатор 6 и на выход устройства аналогично описанному режиму.

Применение предлагаемого устройства позволяет расширить функциональные возможности, так как обнаружение ошибки при передаче информации приводит к формированию запроса на повторение байта информации, в котором при передаче обнаружена ошибка. Таким образом, при-. ошибках и сбоях происходит повторная передача только искаженных байтов, а не всего передаваемого массива, что увеличивает пропускну способность системы и достоверность передаваемой информации.

Предлагаемое устройство также позволяет организовывать информационные автоматизированные системы с высокой пропускной способностью.

JA л

Ч Ч

4tt1 / Л 1-1-Ц

-| I Л 1

фуг. J

фиг.

фиг.В

Фт.7

фга.З

&д/Ь SS

фиг. 9e4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена данными | 1979 |

|

SU842778A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обмена данными | 1980 |

|

SU935939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-07—Публикация

1982-11-09—Подача