(5) УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1982 |

|

SU1078421A2 |

| Устройство для обмена данными | 1979 |

|

SU842778A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1336020A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для сопряжения абонентов с каналом передачи данных | 1986 |

|

SU1357969A2 |

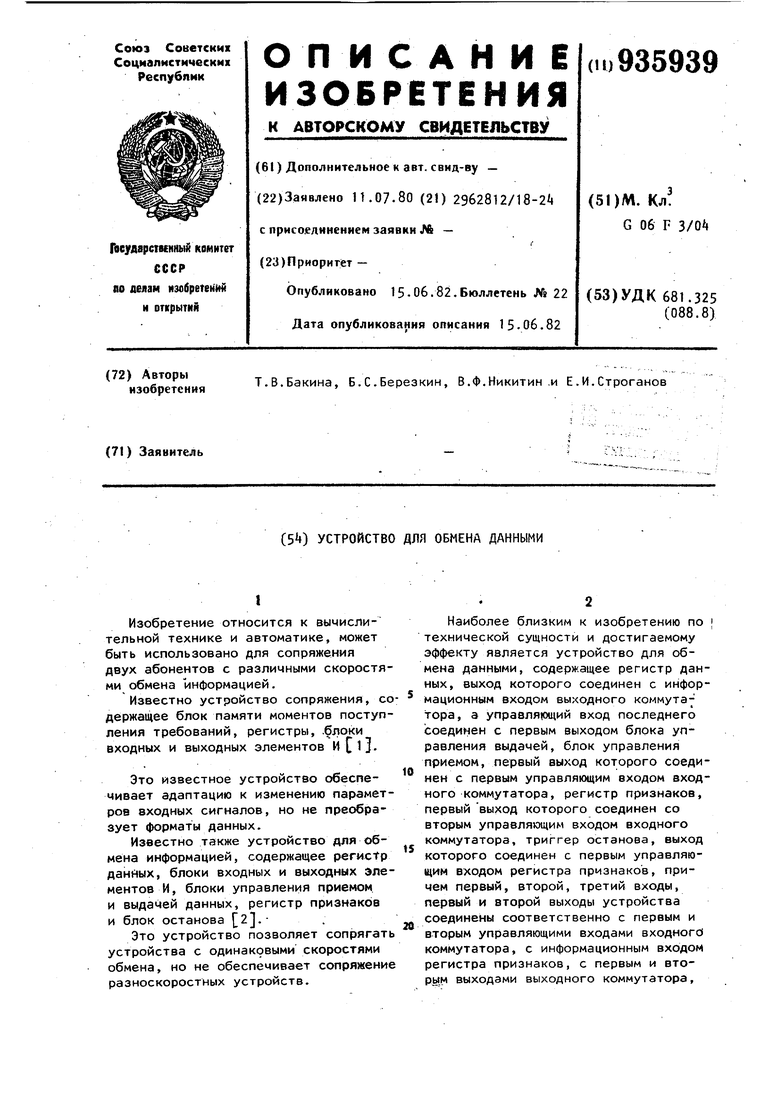

Изобретение относится к вычислительной технике и автоматике, может быть использовано для сопряжения двух абонентов с различными скоростя ми обмена информацией. Известно устройство сопряжения, с держащее блок памяти моментов поступ ления требований, регистры, .блоки входных и выходных элементов И 111Это известное устройство обеспечивает адаптацию к изменению парамет ров входных сигналов, но не преобразует форматы данных. Известно также устройство для обмена информацией, содержащее регистр данйых, блоки входных и выходных эле ментов И, блоки управления приемом и выдачей данных, регистр признаков и блок останова 2.Это устройство позволяет сопрягат устройства с одинаковыми скорюстями обмена, но не обеспечивает сопряжени разноскоростных устройств. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является устройство для обмена данными, содержащее регистр данных, выход которого соединен с информационным входом выходного коммутатора, а управляющий вход последнего соединен с первым выходом блока управления выдачей, блок управления приемом, первый выход которого соединен с первым управляющим входом входного коммутатора, регистр признаков, первый выход которого соединен со вторым управляющим входом входного коммутатора, триггер останова, выход которого соединен с первым управляющим входом регистра признаков, причем первый, второй, третий входы, первый и второй выходы устройства соединены соответственно с первым и вторым управляющими входами входного коммутатора, с информационным входом регистра признаков, с первым и вторы,м выходами выходного коммутатора.

39359394

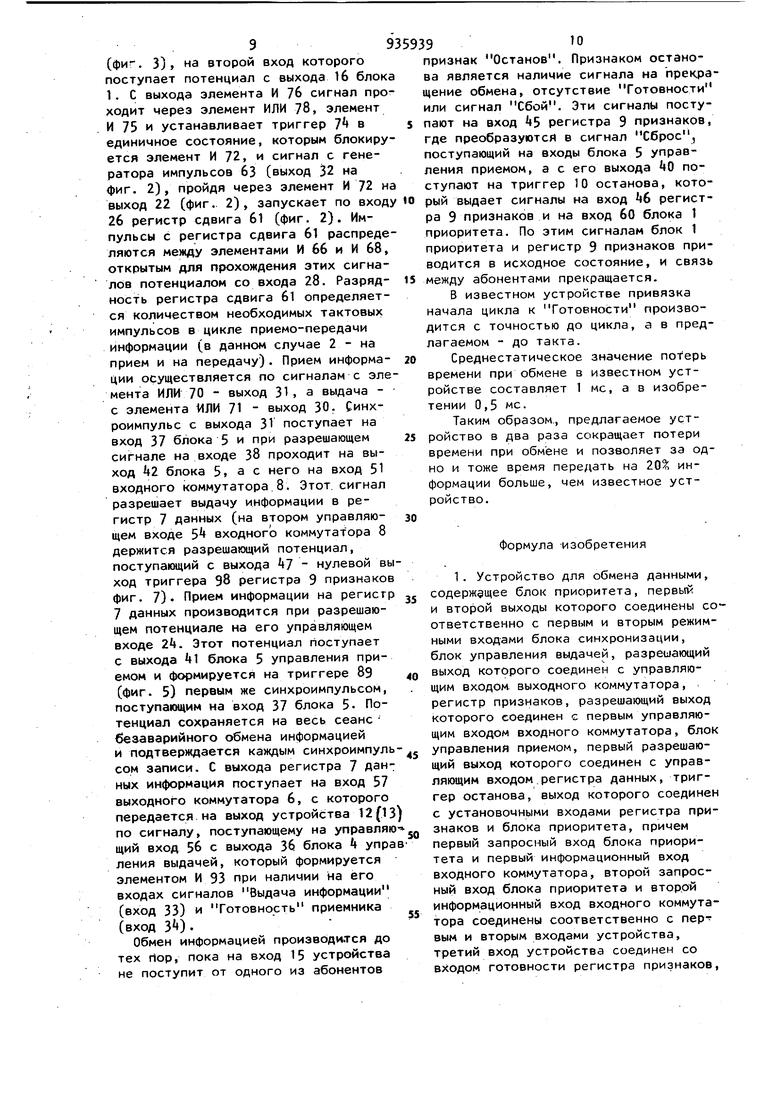

второй выход блока управления выда-соединены соответственно с первым и чей соединён со входом триггера ос-вторым выходами блока приоритета, танова, первый и второй выходы реги-первый у втброй, третий признаковые стра признаков соединены соответст-выходы регистра признаков соединены венно с первым и вторым входами бло- sсоответственно с первым, вторым устаков управления приемом и выдачей,новочными входами блока управления третьи входы которых соединены междуприемом и первым установочным входом собой, а выход входного коммутатораблока управления вьщаией, второй уссОединен с первым входом регистратановочный вход блока управления выданных, блок приоритета, информацион юдачей и третий установочный вход блоные входы которого соединены с пер-ка управления приемом соединены соотвым, вторым входами устройства, уп-ветственно с первым и вторым разрешаюравляющий вход - с выходом триггеращими выходами блока синхронизации, останова, выходы блока приоритетазадающие выходы блоков управления высоединены со входами блока синхрони- isдачей и приемом соединены со входом зации и со вторым, третьим управляю-триггера останова, второй разрешающий щими входами регистра признаков, пер-выход блока управления приемом соеди8ЫЙ выход блока синхронизации соеди-нен со вторым управляющим входом вынен с третьими входами блоков управ-входного коммутатора, выход которого ления приемом и выдачей, второй выход соединен с информационным входом реблока синхронизации соединен с четвер-гистра данных, а выход регистра дантым входом блока управления приемом,ных соединен с информационным входом второй и третий выходы которого сое-выходного коммутатора, выходы котородинены соответственно со входом триг-го являются первым и вторым выходами гера останова и со вторым входом ре- jsустройства, введен блок формирования гистра данных з.серии импульсов, синхронизирующий

Указанное устройство позволяет со-вход и вход готовности, первый и втопрягать разноскоростные абоненты, норой пускающие входы которого соедине обеспечивает достаточную скоростьнены соответственно с тактовым выхообмена информацией.дом блока синхронизации, с третьим

Цель изобретения - повышенв 1е быст-входом устройства, с первым и вторым

родействия устройства.выходами блока приоритета, а рврвый

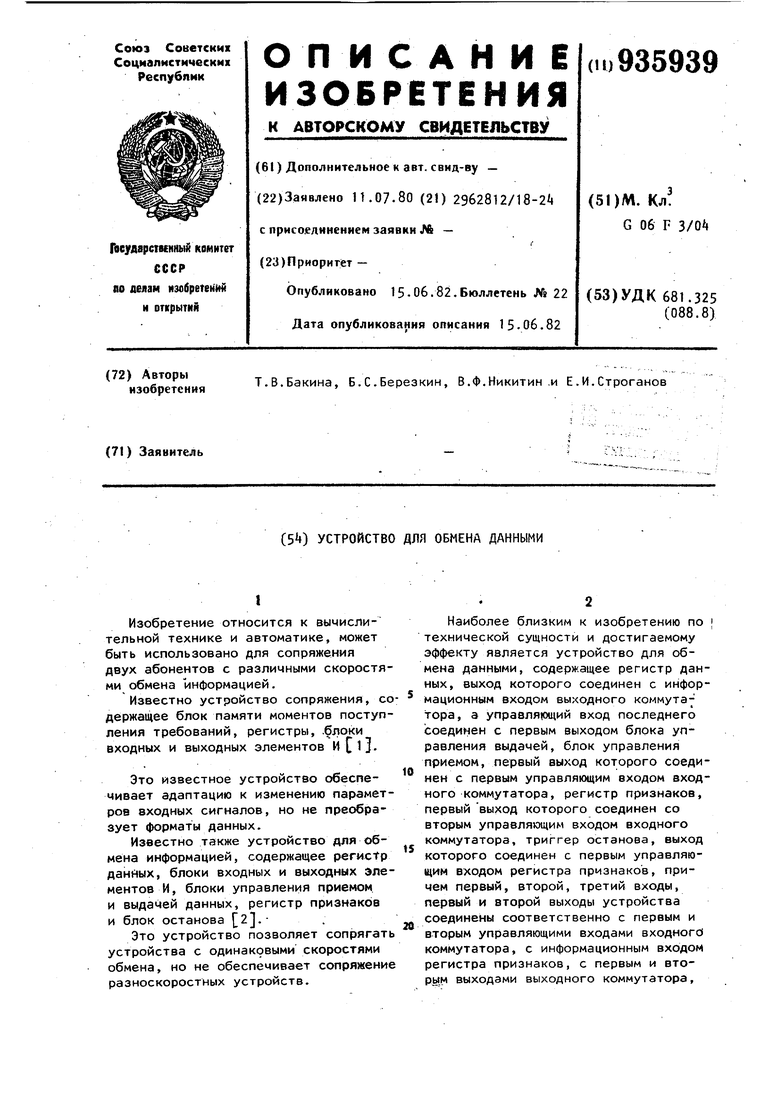

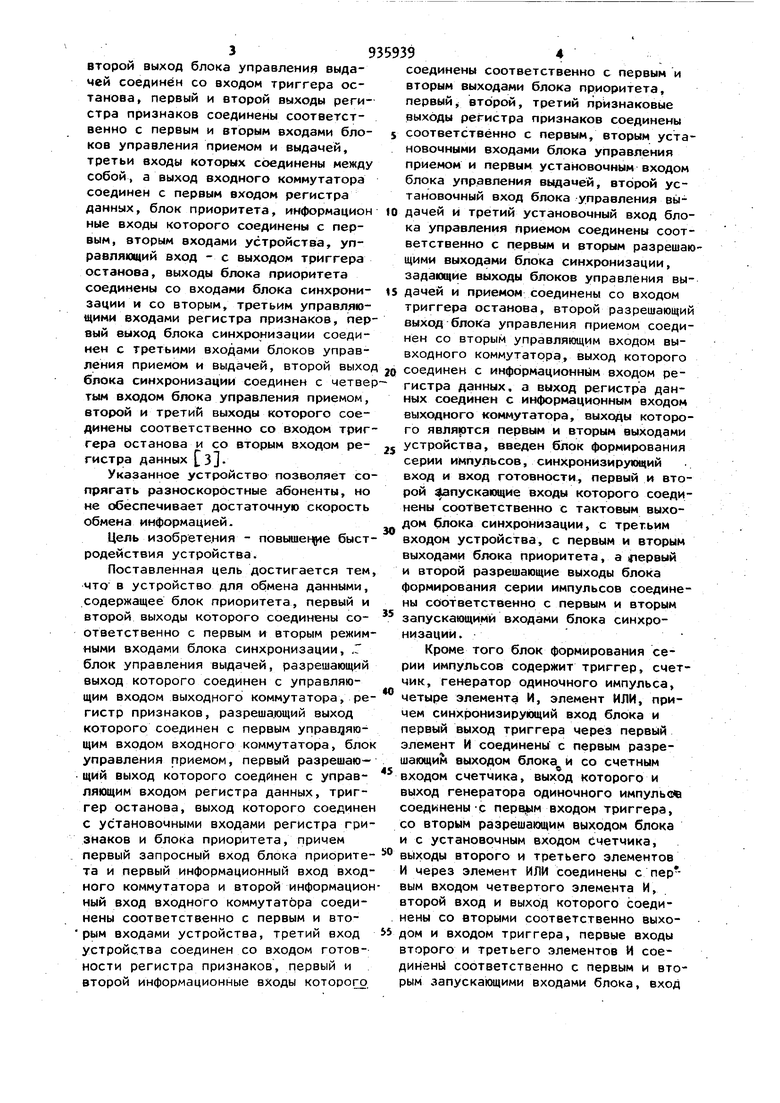

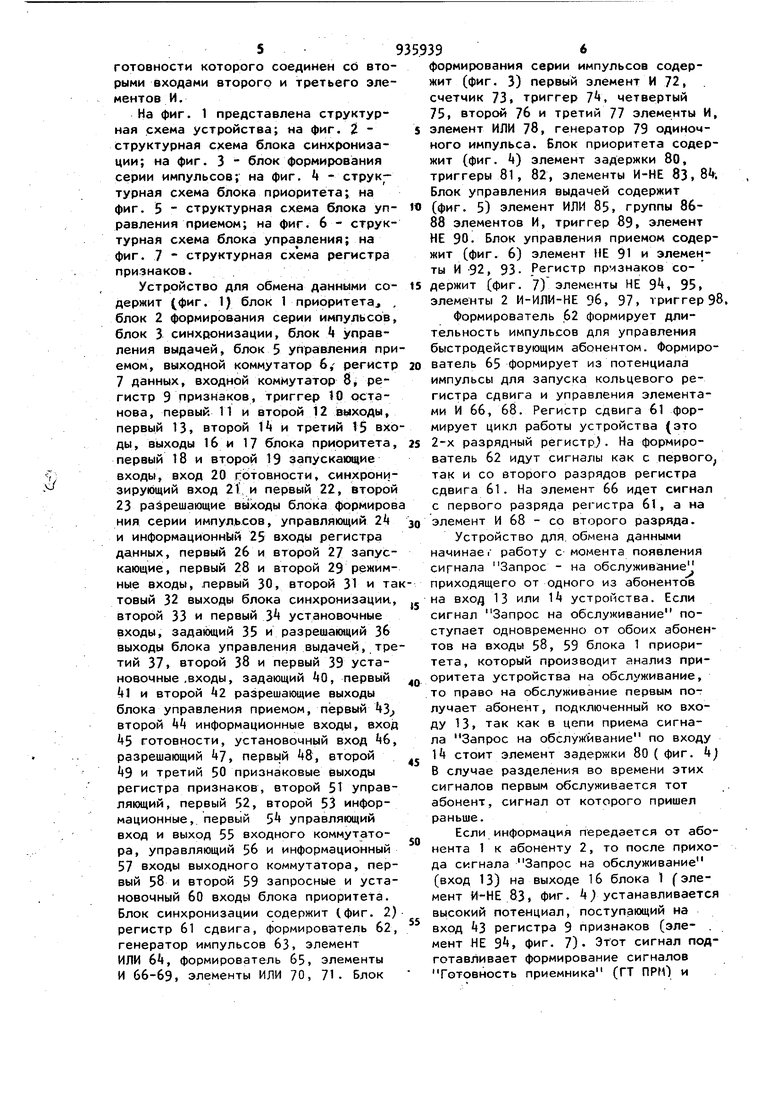

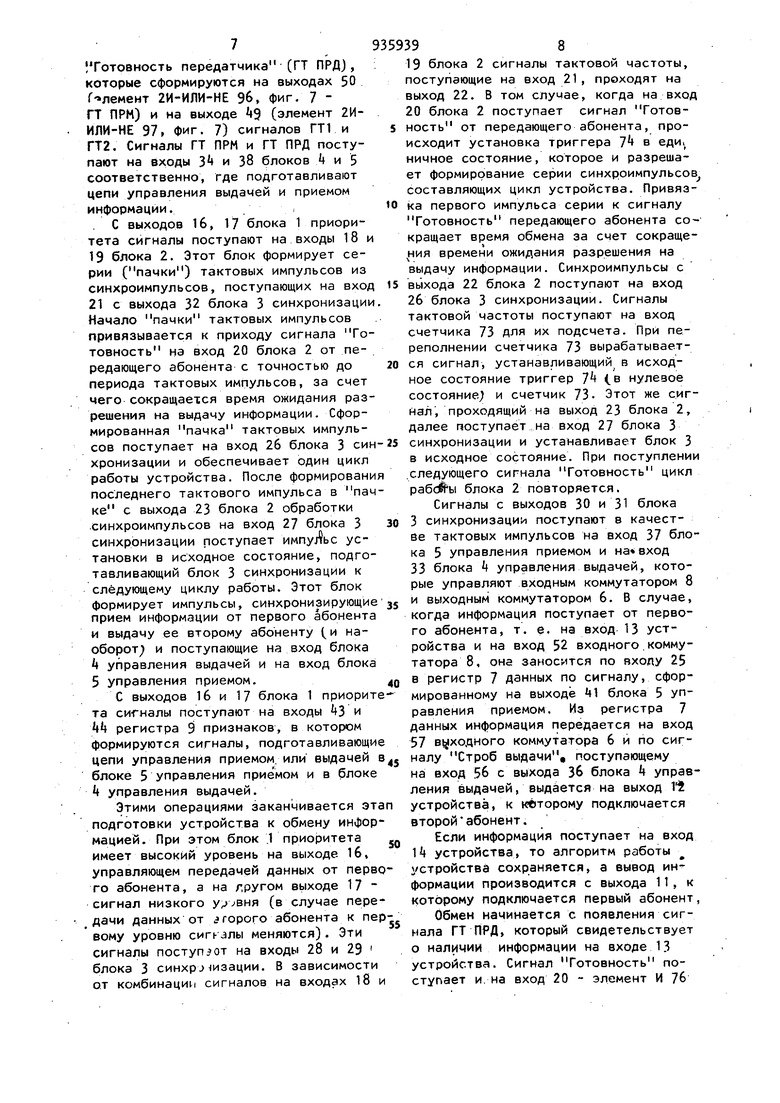

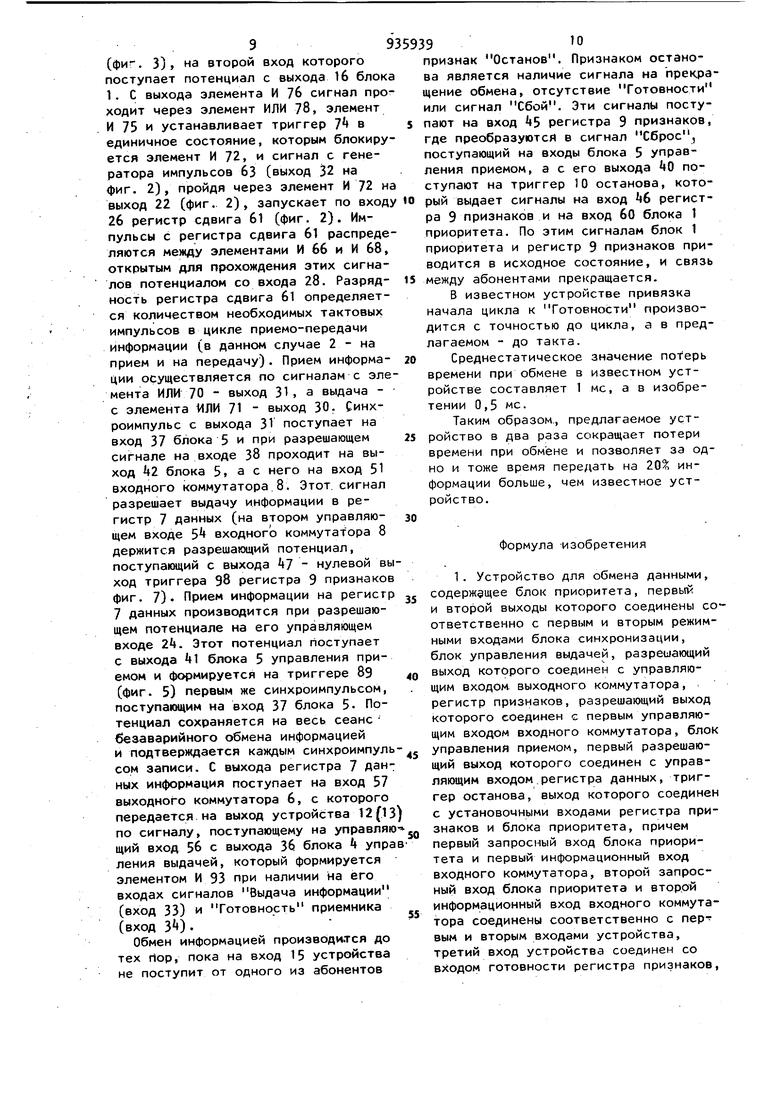

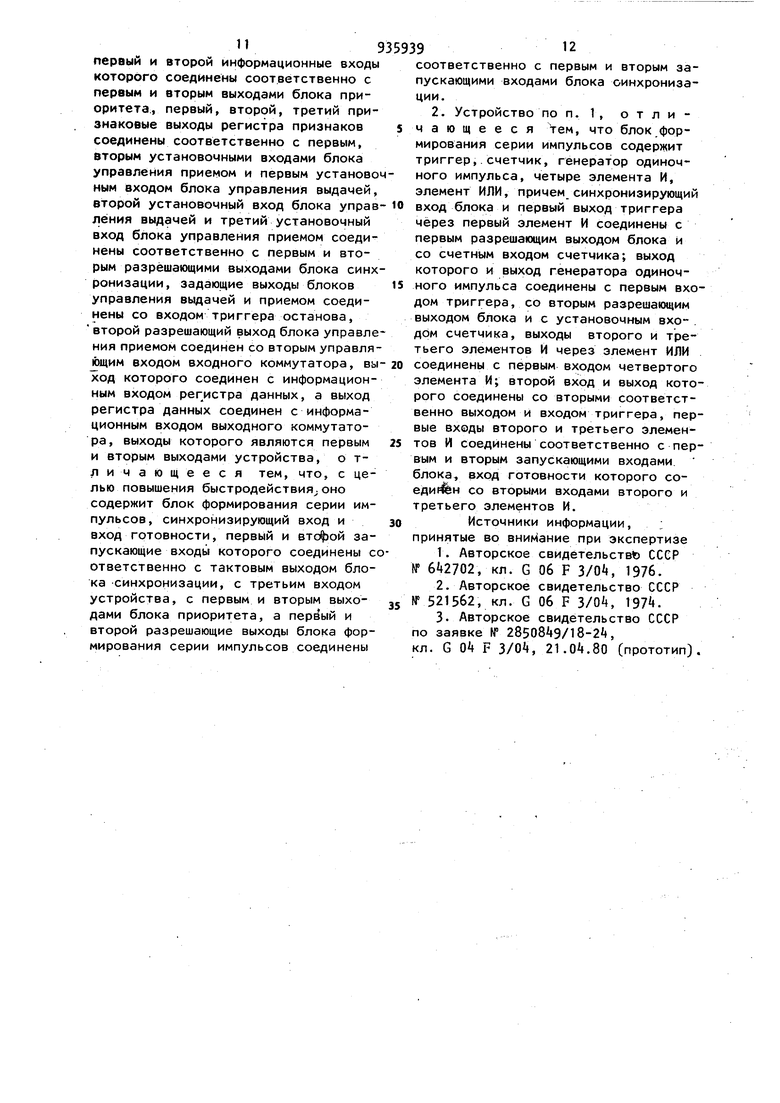

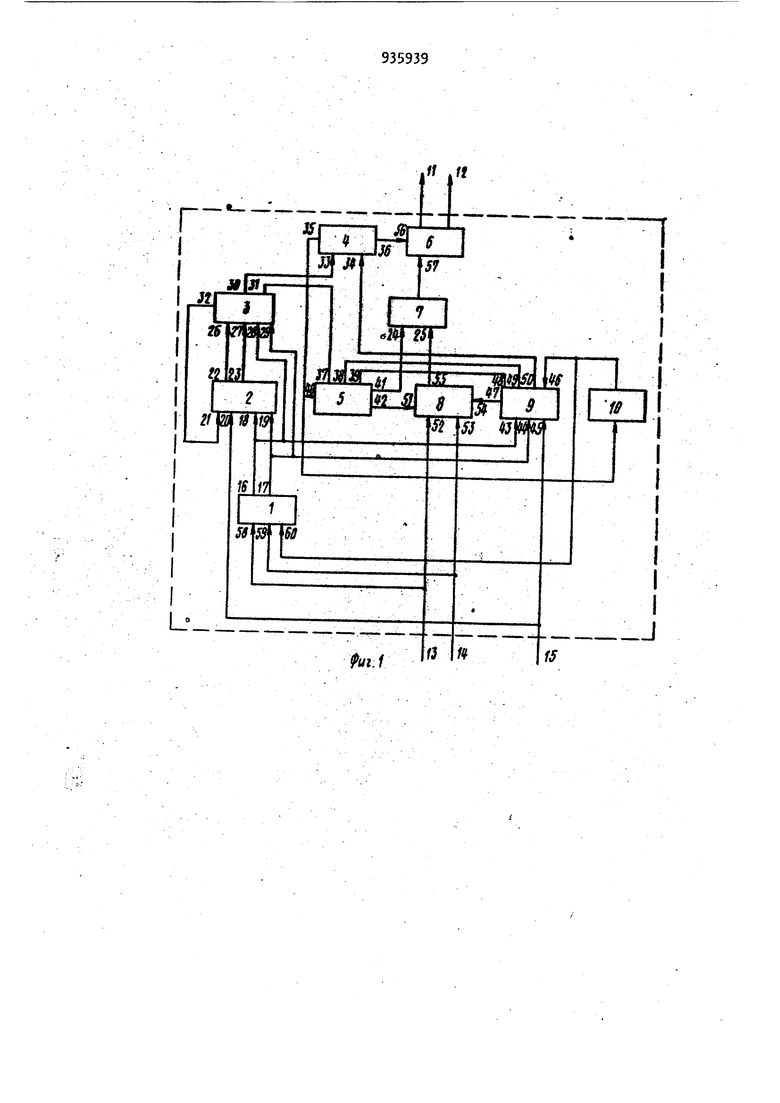

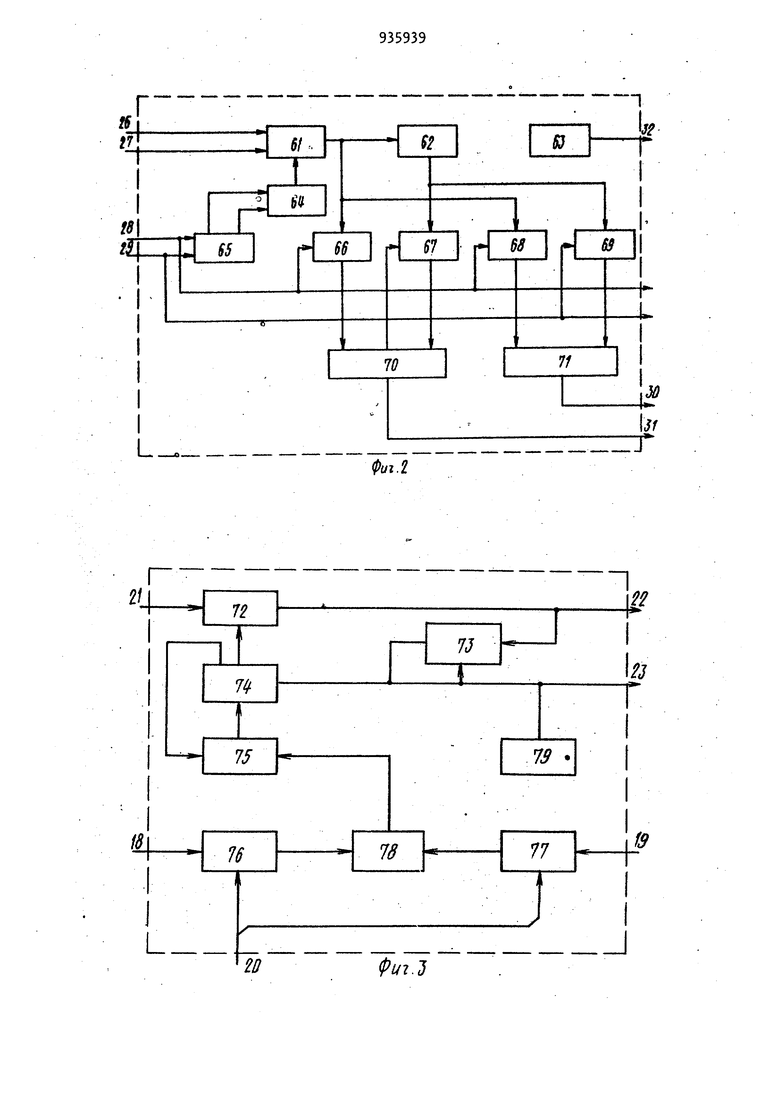

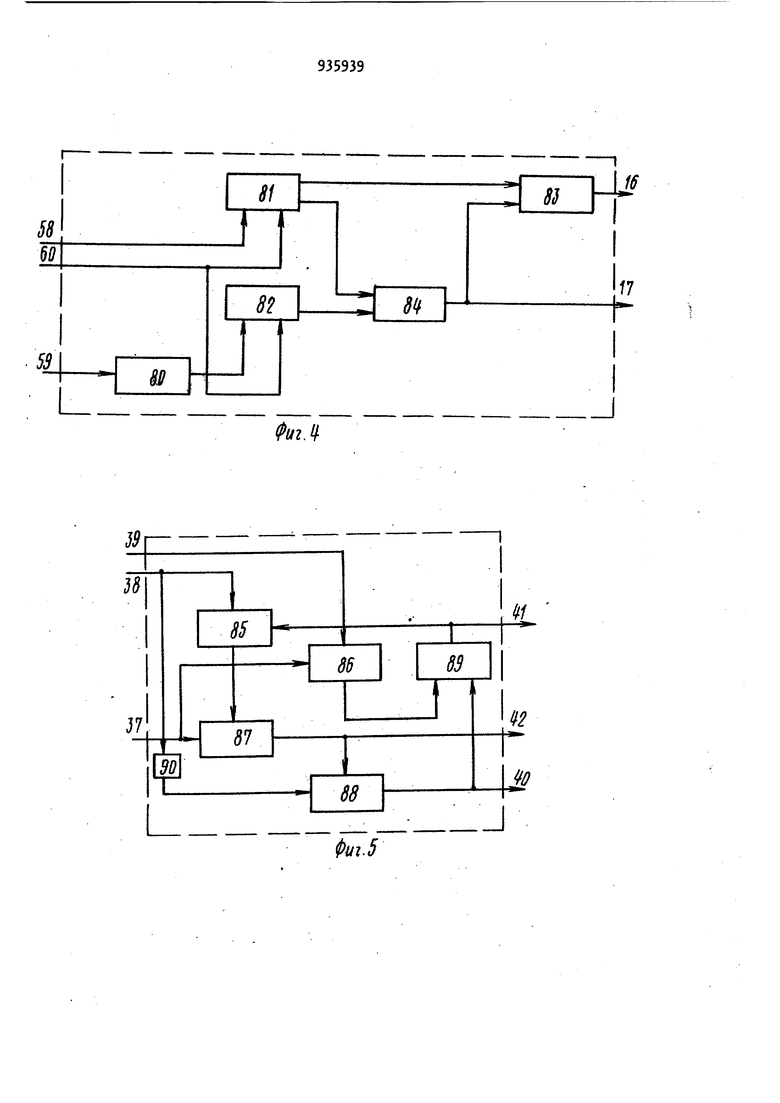

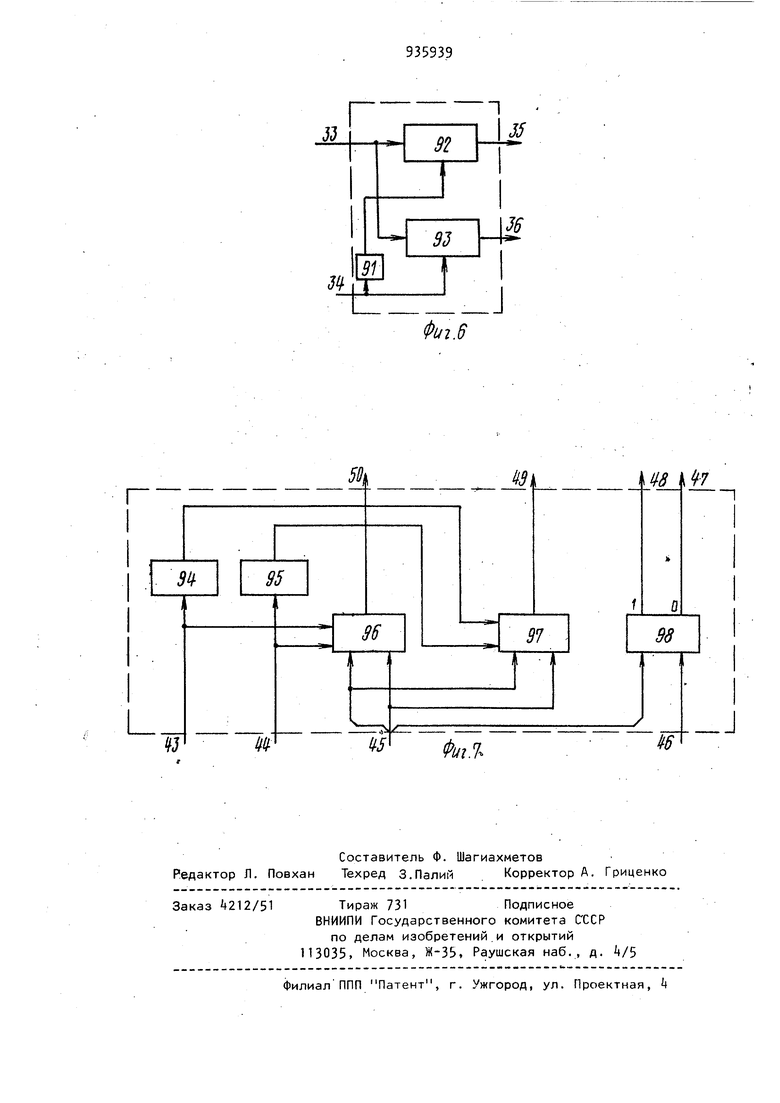

Поставленная цель достигается тем,и второй разрешающие выходы блока что в устройство для обмена данными,формирования серии импульсов соединесодержащее блок приоритета, первый ины соответственно с первым и вторым второй выходы которого соединены со- запускающими входами блока синхроответственно с первым и вторым режим-низаций. ными входами блока синхронизации, .Г Кроме того блок формирования себлок управления выдачей, разрешающийрии импульсов содержит триггер, счетвыход которого соединен с управляю-чик, генератор одиночного импульса, щим входом выходного коммутатора, ре-четыре элемента И, элемент ИЛИ, пригистр признаков, разрешающий выходчем синхронизируюдий вход блока и которого соединен с первым управляю-первый выход триггера через первый щим входом входного коммутатора, блокэлемент И соединены с первым разреуправления приемом, первый разрешаю-шающим выходом блоками со счетным щйй выход которого соединен с управ- входом счетчика, выход которого и пяющим входом регистра данных, триг-выход генератора одиночного импульс гер останова, выход которого соединенсоединеныС пере,мм входом триггера, с установочными входами регистра гри-со вторым разрешающим выходом блока знаков и блока приоритета, причеми с установочным входом счетчика, первый запросный вход блока приорите- выходы второго и третьего элементов та и первый информационный вход вход-И через элемент ИЛИ соединены с пер ного коммутатора и второй информацион-вым входом четвертого элемента И, ный вход входного коммутатора соеди-второй вход и выход которого соединены соответственно с первым и вто-нены со вторыми соответственно выхо рым входами устройства, третий вход wдом и входом триггера, первые входы устройства соединен со входом готов-второго и третьего элементов И соености регистра признаков, первый идинены соответственно с первым и втовторой информационные входы которого.рым запускающими входами блока, вход готовности которого соединен со вторыми входами второго и третьего элементов И, На фиг. 1 представлена структурная схема устройства; на фиг. структурная схема блока синхронизации; на фиг. 3 блок формирования серии импульсов; на фиг. - структурная схема блока приоритета; на фиг. 5 - структурная схема блока упрааления приемом; на фиг. 6 - структурная схема блока управления; на фиг. 7 - структурная схема регистра признаков. Устройство для обмена данными содержит (фиг. 1) блок 1 приоритетаj , блок 2 формирования серии импульсов, блок 3 синхронизации, блок k управления выдачей, блок 5 управления при емом, выходной коммутатор 6, регистр 7 данных, входной коммутатор 8j регистр 9 признаков, триггер 10 останова, первый П и второй 12 (зыходы, первый 13, второй 1 и третий 15 вхо ды, выходы 16 и 17 блока приоритета, первый 18 и второй 19 запускающие входы, вход 20 готовности, синхронизирующий вход 21 и первый 22, второй 23 разрешающие выходы блока формиров ния серии импульсов, управляющий 2 и информационный 25 входы регистра данных, первый 26 и второй 27 запускающие, первый 28 и второй 29 режимные входы, .первый 30, второй 31 и та товый 32 выходы блока синхронизации., второй 33 и первый 3 установочные входы, задающий 35 и разрешающий 36 выходы блока управления выдачей, тре тий 37, второй 38 и первый 39 установочные .входы, задающий Цй, первый tl и второй Ц2 разрешающие выходы блока управления приемом, первый ) второй ЦЦ информационные входы, вход kS готовности, установочный вход k6, разрешающий kj, первь1й 8, второй 49 и третий 50 признаковые выходы регистра признаков, второй 51 управляющий, первый 52, второй 53 информационные,, первый 5 управляющий вход и выход 55 входного коммутатора, управляющий 56 и информационный 57 входы выходного коммутатора, первый 58 и второй 59 запросные и установочный 60 входы блока приоритета. Блок синхронизации содержит (фиг. 2) регистр 61 сдвига, формирователь б2, генератор импульсов 63, элемент ИЛИ 6, формирователь б5, элементы И 66-69, элементы ИЛИ 70, 71. Блок формирования серии импульсов содержит (фиг. 3) первый элемент И 72, счетчик 73, триггер 7, четвертый 75, второй 76 и третий 77 элементы И, элемент ИЛИ 78, генератор 79 одиночного импульса. Блок приоритета содержит (фиг. ) элемент задержки 80, триггеры 81, 82, элементы И-НЕ 83, 8. Блок управления выдачей содержит (фиг. 5) элемент ИЛИ 85, группы 8688 элементов И, триггер 89, элемент НЕ 90. Блок управления приемом содержит (фиг. 6) элемент НЕ 91 и элементы И -92, 93- Регистр признаков содержит (фиг. 7) элементы НЕ 9, 95, элементы 2 И-ИЛИ-НЕ 96, 97, триггер 98. Формирователь 62 формирует длительность импульсов для управления быстродействующим абонентом. Формирователь 65 формирует из потенциала импульсы для запуска кольцевого регистра сдвига и управления элементами И 66, б8. Регистр сдвига 61 формирует цикл работы устройства (это 2-х разрядный регистр). На формирователь 62 идут сигналы как с первого так и со второго разрядов регистра сдвига 61. На элемент 66 идет сигнал с первого разряда регистра 61, а на элемент И 68 - со второго разряда. Устройство для. обмена данными начинав/ работу с момента появления сигнала Запрос - на обслуживание приходящего от одного из абонентов на вхо/} 13 или Н устройства. Если сигнал Запрос на обслуживание поступает одновременно от обоих абонентов на входы 58, 59 блока 1 приоритета, который производит анализ приоритета устройства на обслуживание, то право на обслуживание первым по-г лучает абонент, подключенный ко входу 13, так как в цепи приема сигнала Запрос на обслужйвание по входу 1 стоит элемент задержки 80 ( фиг. k) В случае разделения во времени этих сигналов первым обслуживается тот абонент, сигнал от которого пришел раньше. Если информация передается от абонента 1 к абоненту 2, то после прихода сигнала Запрос на обслуживание (вход 13) на выходе 16 блока 1 (элемент И-НЕ 83, фиг. АI устанавливается высокий потенциал, поступающий на вход kj регистра 9 признаков (эле- . мент НЕ 9, фиг. 7). Этот сигнал подготавливает формирование сигналов Готовность приемника (ГТ ПРМ) и 1Готовность передатчика (ГТ ПРД), которые сформируются на выходах 50 f-элемент 2И-ИЛИ-НЕ 9б, фиг. 7 ГТ ПРМ) и на выходе k (элемент 2ИИЛИ-НЕ 97, фиг. 7) сигналов ГТ1 и ГТ2. Сигналы ГТ ПРМ и ГТ ПРД поступают на Входы 3 и 38 блоков Л и 5 соответственно, где подготавливают цепи управления выдачей и приемом информации. . С выходов 16, 17 блока 1 приоритета сигналы поступают на входы 18 и 19 блока 2. Этот блок формирует серии (пачки) тактовых импульсов из синхроимпульсов, поступающих на вход 21 с выхода 32 блока 3 синхронизации Начало пачки тактовых импульсов привязывается к приходу сигнала Готовность на вход 20 блока 2 от передающего абонента с точностью до периода тактовых импульсов, за счет чего сокращается время ожидания разрешения на выдачу информации. Сформированная пачка тактовых импульсов поступает на вход 2б блока 3 син хронизации и обеспечивает один цикл работы устройства. После формировани последнего тактового импульса в пач ке с выхода 23 блока 2 обработки синхроимпульсов на вход 27 блока 3 синхронизации поступает импyJ ьc установки в исходное состояние, подготавливающий блок 3 синхронизации к следующему циклу работы. Этот блок формирует импульсы, синхронизирующие прием информации от первого абонента и выдачу ее второму абоненту (и наоборот и поступающие на вход блока А управления выдачей и на вход блока 5 управления приемом. С выходов 16 и 17 блока 1 приорит та сигналы поступают на входы 13 и kk регистра 9 признаков, в котором формируются сигналы, подготавливающи цепи управления приемом, или выдачей блоке 5 управления приемом и в блоке управления выдачей. Этими операциями заканчивается эт подготовки устройства к обмену инфор мацией. При этом блок .1 приоритета имеет ВЫСОКИЙ уровень на выходе 16, управляющем передачей данных от перв го абонента, а на гругом вь1ходе 17 сигнал низкого (в случае пере дачи данных от второго абонента к пе вому уровню cиг алы меняются). Эти сигналы поступает на входы 28 и 29 блока 3 синхрлизации. В зависимости от комбинации сигналов на входах 18 398 19блока 2 сигналы тактовой частоты, поступающие на вход 21, проходят на выход 22. В том случае, когда на вход 20блока 2 поступает сигнал Готовность от передающего абонента, происходит установка триггера 7 в еди, ничное состояние, которое и разрешает формирование серии синхроимпульсов составляющих цикл устройства. Привязка первого импульса серии к сигналу Готовность передающего абонента сокращает время обмена за счет сокращеН1ИЯ времени ожидания разрешения на выдачу информации. Синхроимпульсы с вь1хода 22 блока 2 поступают на вход 26 блока 3 синхронизации. Сигналы тактовой частоты поступают на вход счетчика 73 для их подсчета. При переполнении счетчика 73 вырабатывается сигнал, устанавливающий в исходное состояние триггер .в нулевое состояние и счетчик 73. Этот же си|- Нал, проходящий на выход 23 блока 2, далее поступает на вход 27 блока 3 синхронизации и устанавливает блок 3 в исходное состояние. При поступлении следующего сигнала Готовность цикл pa6dfrbi блока 2 повторяется. Сигналы с выходов 30 и 31 блока 3 синхронизации поступают в качестве тактовых импульсов на вход 37 блока 5 управления приемом и 33 блока i управления выдачей, которые управляют входным коммутатором 8 выходным коммутатором 6. В случае, когда информация поступает от первого абонента, т. е. на вход 13 устройства и на вход 52 входного.коммутатора 8, она заносится по входу 25 в регистр 7 данных по сигналу, сформированному на выходе Ml блока 5 управления приемом. Из регистра 7 данных информация передается на вход 57 выходного коммутатора 6 и по сигналу Строб выдачи, поступающему на вход 56 с выхода Зб блока k управления выдачей, выдается на выход 1i устройства, к которому подключается второйабонент. Если информация поступает на вход 1 устройства, то алгоритм работы устройства сохраняется, а вывод информации производится с выхода 11, к которому подключается первый абонент, Обмен начинается с появления сигнала ГТ ПРД, который свидетельствует о наличии информации на входе 13 устройства. Сигнал Готовность поступает и. на вход 20 - элемент И 7б (фи-. 3), на второй вход которого поступает потенциал с выхода 16 блок 1. С выхода элемента И 7б сигнал про ходит через элемент ИЛИ 78, элемент И 75 и устанавливает триггер 7 в единичное состояние, которым блокиру ется элемент И 72, и сигнал с генератора импульсов 63 (выход 32 на фиг. 2), пройдя через элемент И 72 н ВЫХОД 22 (фиг. 2), запускает по вход 26 регистр сдвига 61 (фиг. 2). Импульсы с регистра сдвига 61 распреде ляются между элементами И 66 и И 68, открытым для прохождения этих сигналов потенциалом со входа 28. Разрядность регистра сдвига б1 определяется количеством необходимых тактовых импульсов в цикле приемо-передачи информации (в данном случае 2 - на прием и на передачу). Прием информации осуществляется по сигналам с эле мента ИЛИ 70 - выход 31, а выдача с элемента 71 - выход 30- Синхроимпульс с выхода 31 поступает на вход 37 блока 5 и при разрешающем сигнале на входе 38 проходит на выход k2 блока 5, а с него на вход 51 входного коммутатора 8. Этот сигнал разрешает выдачу информации в регистр 7 данных (на втором управляющем входе 5 входного коммутатора 8 держится разрешающий потенциал, поступающий с выхода kj - нулевой вы ход триггера 9В регистра 9 признаков фиг. 7). Прием информации на регистр 7 данных производится при разрешающем потенциале на его управляющем входе 2. Этот потенциал поступает с выхода k блока 5 управления приемом и формируется на триггере 89 (фиг. 5) первым же синхроимпульсом, поступающим на вход 37 блока 5- Потенциал сохраняется на весь сеанс безаварийного обмена информацией И подтверждается каждым синхроимпульсом записи. С выхода регистра 7 данных информация поступает на вход 57 выходного коммутатора 6, с которого передается на выход устройства 12(13) по сигналу, поступающему на управляю щий вход 56 с выхода 36 блока управ ления выдачей, который формируется элементом И 93 при наличии на его входах сигналов Выдача информации (вход 33) и Готовность приемника (вход ЗЮОбмен информацией производится до тех Пор, пока на вход 15 устройства не поступит от одного из абонентов 9О признак Останов. Признаком останова является наличие сигнала на прекращение обмена, отсутствие Готовности или сигнал Сбой. Эти сигналы поступают на вход k регистра 9 признаков, где преобразуются в сигнал Сброс, поступающий на входы блока 5 управления приемом, а с его выхода 0 поступают на триггер 10 останова, KOTOрый выдает сигналы на вход регистра 9 признаков и на вход 60 блока 1 приоритета. По этим сигналам блок 1 приоритета и регистр 9 признаков приводится в исходное состояние, и связь между абонентами прекращается. В известном устройстве привязка начала цикла к Готовности производится с точностью до цикла, а в предлагаемом - до такта. Среднестатическое значение потерь времени при обмене в известном устройстве составляет 1 мс, а в изобретении 0,5 мс. Таким образом., предлагаемое устройство в два раза сокращает потери времени при обмене и позволяет за одно и тоже время передать на 20% информации больше, чем известное устройство. Формула изобретения 1. Устройство для обмена данными, содержащее блок приоритета, первый и второй выходы которого соединены со ответственно с первым и вторым режимными входами блока синхронизации, блок управления выдачей, разрешающий выход которого соединен с управляющим входом выходного коммутатора, регистр признаков, разрешающий выход которого соединен с первым управляющим входом входного коммутатора, блок управления приемом, первый разрешающии выход которого соединен с управляющим входом регистра данных, триггер останова, выход которого соединен с установочными входами регистра признаков и блока приоритета, причем первый запросный вход блока приоритета и первый информационный вход входного коммутатора, второй запросный вход блока приоритета и второй информационный вход входного коммутатора соединены соответственно с первым и вторым входами устройства, третий вход устройства соединен со входом готовности регистра признаков.

первый и второй информационные входы которого соединены соответственно с первым и вторым выходами блока приоритета., первый, второй, третий признаковые выходы регистра признаков соединены соответственно с первым, вторым установочными входами блока управления приемом и первым установоным Входом блока управления выдачей, второй установочный вход блока управ лёния выдачей и третий установочный вход блока управления приемом соединены соответственно с первым и вторым разрешающими выходами блока синхронизации, задающие выходы блоков управления выдачей и приемом соединены со входом триггера останова, второй разрешающий выход блока управления приемом соединен со вторым управляющим входом входного коммутатора, вы ход которого соединен с информационным входом рег истра данных, а выход регистра данных соединен с информационным входом выходного коммутатора, выходы которого являются первым и вторым выходами устройства, о тли чающееся тем, что, с целью повышения быстродействия оно содержит блок формирования серии импульсов, синхронизирующий вход и вход готовности, первый и вто|)ой запускающие входы которого соединены сответственно с тактовым выходом блока синхронизации, с третьим входом устройства, с первым и вторым выходами блока приоритета, а первый и второй разрешающие выходы блока формирования серии импульсов соединены

соответственно с первым и вторым запускающими входами блока синхронизации,

Источники информации, ; принятые во внимание при экспертизе

кл. G 04 F З/О, 21.0i.80 (прототип.

.

: Г I

SI

82

L

ФигЛ

Фш.5

lAjS

8S

dif

I

П

J

J

Фи.б

Авторы

Даты

1982-06-15—Публикация

1980-07-11—Подача