Изобретение относится к специали зированным средствам автоматики и вычислительной техники, предназначенным для определения характеристик случайных процессов в условиях недостатка априорной информации например в океанологии, метеорологии и радиофизике. Известен адаптивный амплитудный анализатор, содерусащий аналого-цифровой преобразователь, запоминагацее устройство и сумматор, соединеннне поспедовательно, выход сумматора соединен с информационным вуодомзапоминающего устройства, усреднитель, блок вычитания, регистр числа, блок сравнения, регулируемый делитель частоты и блок синхронизации Г . Недостаток устройства - необходимость априорного знания свойств сигнст;а для рационального задания порога сравнения , определяквдего точность вычислений и скорость сходимости алгоритма. Известен адаптивный анализатор, содержащий счетчик выборок, блок фиксации момента окончания выборки два блока памяти, блок запоминания минимального кода, источник единичного напряжения, сумматор, комм татор, регистр переноса сдвига, вы ход которого соединен с адресными входами блоков памяти . Недостатками анализатора являют ся невысокое быстродействие и большой объем памяти. Наиболее близким по технической сущности к предлагаемому является время-импульсный амплитудный анализатор, содержащий устройство выч тания (пороговое устройство), блок синхронизации, подключенный к тактовому входу регистра сдвига, выхо ды которого через первЕлй коммутато (схемы совпадения) соединены с вхо дами второго коммутатора, выходы которого соединены с входами блока счетчиков, при этом управлякадие входь: второго коммутаторз соединен с Biji ;;одами дешифратора, вход котор го подключен к выходу счетчика Sj Недостатками анализатора-протот па являются необходимость итератив ной установки уровня порогового на пряжения, задаваемого человекомоператором в эксперименте, однократное задание ширины дифференциальных коридоров, необходимость рационального выбора (вручную) режимов работы в зависимости от свойств входного сиг-нала, так как при различных размахах (диапазоне амплитуд) в анализаторе обеспечивается различная точность аппроксимации гистограмгЛЫ, различная величина среднего значения сигнала приводит к смещению гистограммы относительно середины диапазона (шкалы) анализа. В совокупности это приводит к необходимости значительного увеличения объема памяти (количества счетчиков), к увеличению длительности экспериментов для установки оптимальных параметров анализа или к пропорциональному уменьшению точности анализа амплитудньс: свойств сигнала. Цель изобретения - повыиение точности анализа в условиях априорной неопределенности свойств сигнала. Поставленная цель достигается тем, что в адаптивный амплитудный анализатор, содержащий блок вычитания, первый информационный вход которого является входом анализатора, а тактовый вход блока вычитания объединен с входом сброса регистра сдвига и соединен с первым выходом блока синхронизации, второй выход которого подключен к информационному входу счетчика, разрядные выходы которого соединены соответственно с разрядными входами де чифратора, разрядные выходы которого подключены к первой группе разрядных входов первого коммутатора, вторая группа разрядных входов которого соединена соответственно с выходами блока задания весовых коэффициентов, разрядные выходы регистра сдвига подключены соответственно к разрядньом входам второго коммута|тора, разрядные выходы которого со|единены соответственно с первой группой входов блока счетчиков, введены дискриминатор знака, третий коммутатор, ключ, элемент задержки, схема сравнения, элементы И, вычислитель максимума, формирователь модуля и усреднитель, вход которого подключен к входу анализатора, а выход является первьлм ВЕ-ЖОДОМ анализатора и подключен к второму информационному входу блока вычитания, выход которого соединен с входом дискриминатора знака и входом формирователя модуля, выход которого подключен к первому входу схемы сравнения и информационному входу вычислителя максимума, тактовый вход которого соединен с третьим выходом блока синхронизации, а Btход подключен к входу блока задания весовых коэффициентов, второй вход схемы сравнения соединен с вьзходом первого коммутатора, а выход подключен, к входу сброса счетчика и к информационным входам ключа и первого и второго элементов И, управляющие входы которых соединены соответственно с первым и вторым знаковыми выходами дискримииатора знака а выхолн элементов К подключены соответственно к информационны. входам второго и третьего коммутаторов, разрядные входы третьего коммутатора подключены к разрядным вькодам регистра сдвига, а разрядные третьего коммутатора соединены с второй группой .олов блока счетчиков соответственно, выход блока счетчиков является BTOps-.iM выходом анализатора, тактовый вход ключа соедин с вторып выходом блока синхронизации, первьпТ выход которого подключ через элемент задеруски к инЛормаиионному входу регистра сдвига, сдвиговый вход которого соединен с выходом ключа.

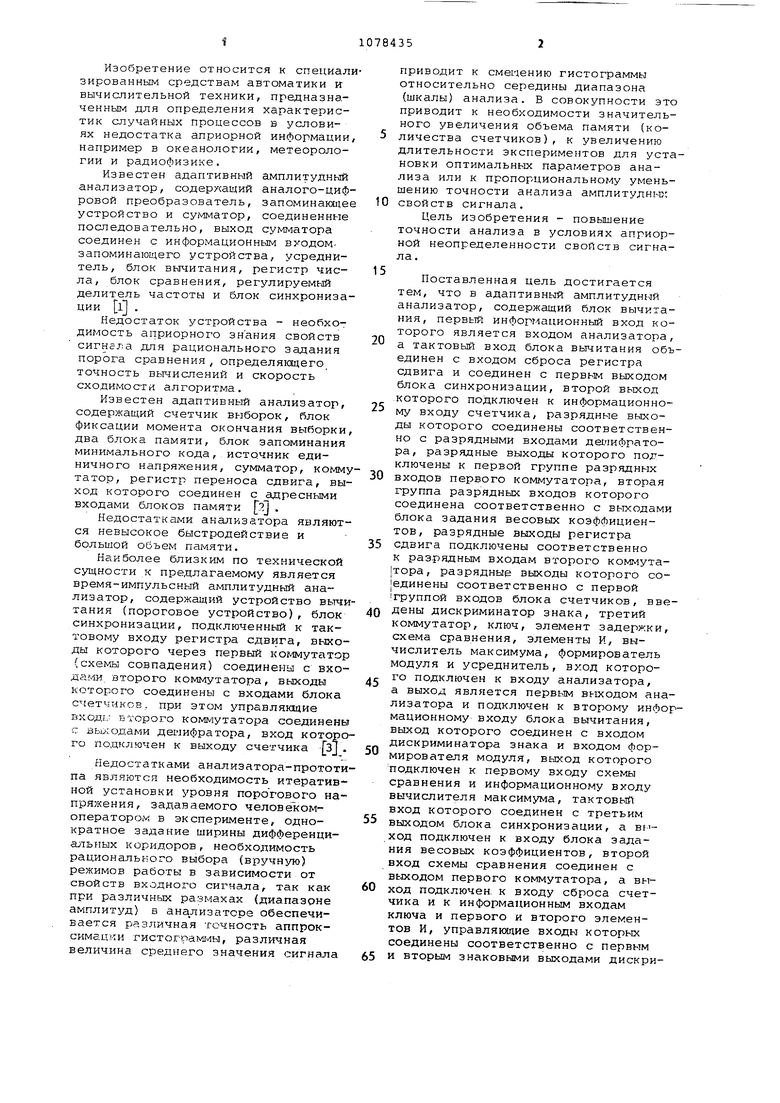

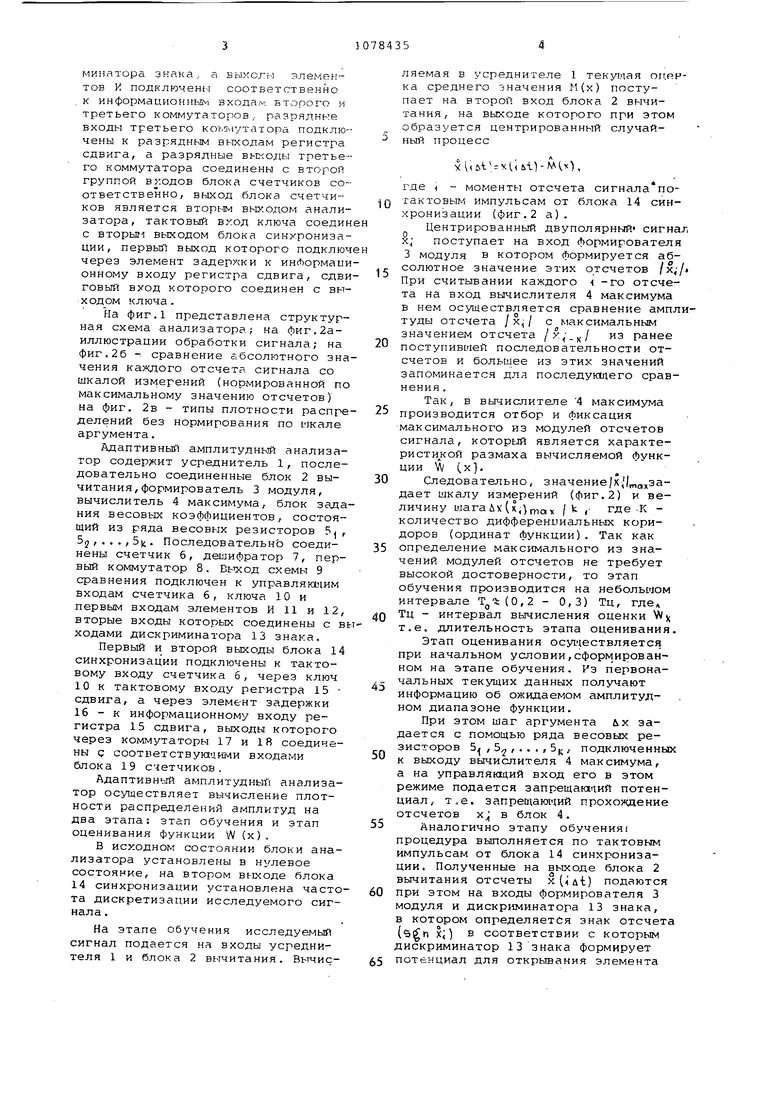

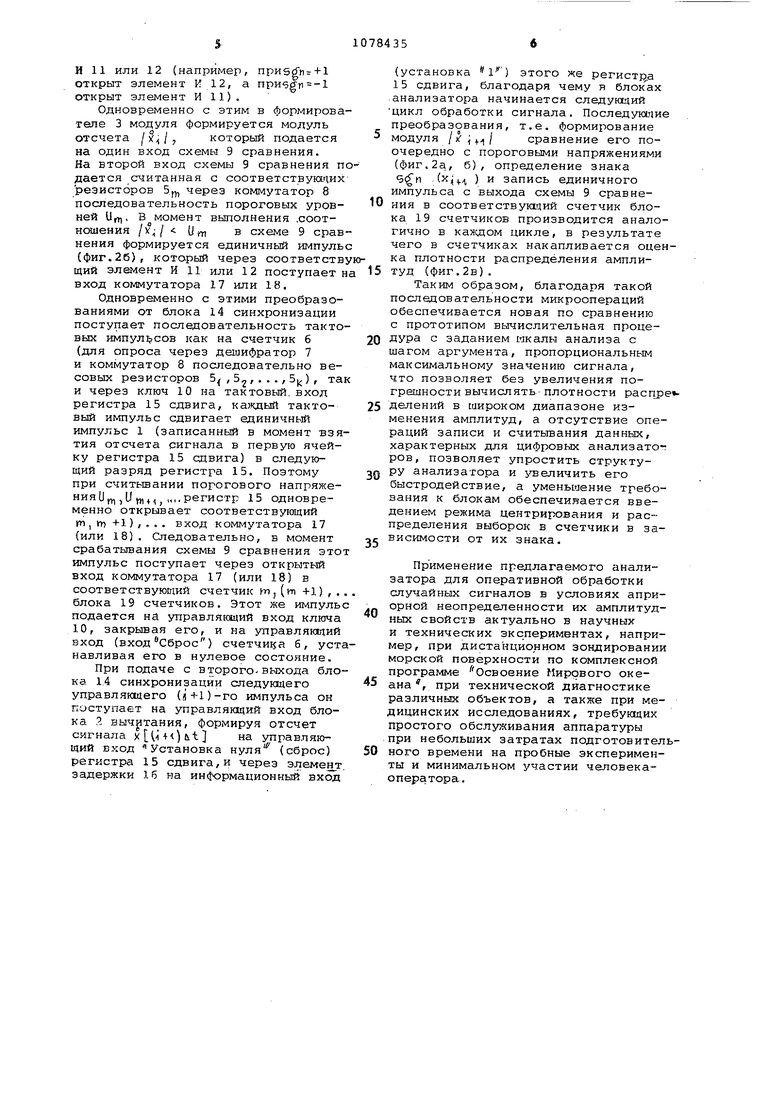

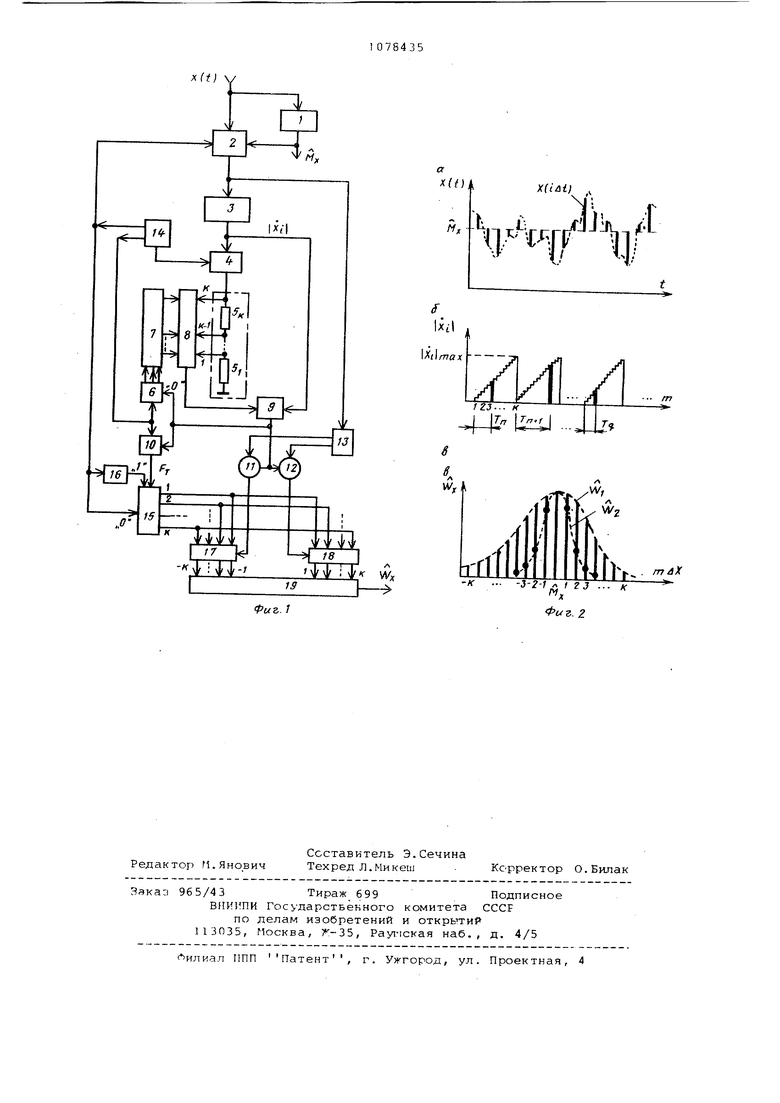

На фиг.1 представлена структурная схема анализатора; на фиг.2аиллюстрации обработки сигнала; на фиг.26 - сравнение абсолютного значения каждого отсчета сигнала со шкалой измерений (нормированной по максимальному значению отсчетов) на фиг. 2в - типы плотности распределений без нормирования по аргумента.

Адаптивный амплитудный анализатор содержит усреднитель 1, последовательно соединенные блок 2 вычитания, формирователь 3 модуля, вычислитель 4 максимума, блок задания весовых коэффициентов, состоящий из ряда весовых резисторов 5|, 5y,,.,,5}i. Последовательно соединены счетчик 6, дешифратор 7, перВЕЛй коммутатор 8. Вьтход схемы 9 сравнения подключен к управлягапим входам счетчика 6, ключа 10 и первым входам элементов И 11 и 12, вторые входы которых соединены с входами дискриминатора 13 знака.

Первый и второй вьоходы блока 14 синхронизации подключены к тактовому входу счетчика 6, через ключ 10 к тактовому входу регистра 15 сдвига, а через элемент задержки 16 - к информационному входу регистра 15 сдвига, выходы которого через коммутаторы 17 и 18 соединены с соответствугацими входами блока 19 счетчиков.

Адаптивный амплитудный анализатор осуществляет вычисление плотности распределений амплитуд на два этапа: этап обучения и этап оценивания функции W (х).

В исходном состоянии блоки анализатора установлены в нулевое состояние, на втором вькоде блока 14 синхронизации установлена частота дискретизации исследуемого сигнала.

На этапе обучения исследуемый сигнал подается на входы усреднителя 1 и блока 2 вычитания. Вычисляемая в усреднителе 1 текущая оггерка среднего значения М(х) поступает на второй вход блока 2 вычитания, на выходе которого при этом образуется центрированный случайНЫ1Ч процесс

x.(),

где н - моменты отсчета сигнала потактовым импульсам от блока 14 синхронизации (фиг.2 а).

Центрированный двуполярный сигна х; поступает на вход формирователя 3 модуля в котором формируется абсолютное значение этих отсчетов /х При считывании каждого -го отсчета на вход вычислителя 4 максимума в нем осуществляется сравнение амплтуды отсчета /х / с максимальным значением отсчета ранее поступившей последовательности отсчетов и большее из этих значений запоминается для последуктцего сравнения .

Так, в вычислителе 4 максимума производится отбор и фиксация максимального из модулей отсчетов сигнала, который является характеристи сой размаха вычисляемой функции V/ (х).

Следовательно, значение/Х |„д,задает шкалу измерений (фиг.2) и величину шага ЛК (х,) рта X / k , где -К количество дифференциальных коридоров (ординат функции). Так как определение максимального из значений модулей отсчетов не требует высокой достоверности, то этап обучения производится на небольшом интервале TgJ:(0,2 - 0,3) Тц, где, Тц - интервал вычисления оценки Vx т.е. длительность этапа оценивания

Этап оценивания осу11ествляется при начальном условии,сформ ированном на этапе обучения. Из первоначальных текущих данных получают информацию об ожидаемом амплитудном диапазоне функции.

При этом шаг аргумента &х задается с помощью ряда весовых резисторов 5 , 5, , . . . , 5 , подключенных к выходу вычислителя 4 максимума, а на управлягаций вход его в этом режиме подается запрещакщий потенциал, т.е. запрео1аю1Шй прохо5 щение отсчетов Xjj в блок 4.

Аналогично этапу обучения процедура выполняется по тактовым импульсам от блока 14 синхронизации. Полученные на выходе блока 2 вычитания отсчеты x(4ut) подаются при этом на входы формирователя 3 модуля и дискриминатора 13 знака, в котором определяется знак отсчета ( xi) в соответствии с которым дискриминатор 13 знака формирует потенциал для открывания элемента И 11 или 12 (например, npHSgur+l открыт элемент И 12, а -1 открыт элемент И 11). Одновременно с этим в формирова теле 3 модуля формируется модуль отсчета ,который подается на один вход схемы 9 сравнения. На второй вход схемы 9 сравнения п дается считанная с соответствукхчих резисторов 5fy, через коммутатор 8 последовательность пороговых уровней U, В момент выполнения .соотношения иni в схеме 9 срав нения формируется единичный импуль (фиг.26)г который через соответств щий элемент И 11 или 12 поступает вход коммутатора 17 или 18. Одновременно с этими преобразованиями от блока 14 синхронизации поступает последовательность такто вых импульсов как на счетчик 6 (для опроса через дешифратор 7 и коммутатор 8 последовательно весовых резисторов 5| , 5 ,, . ., 5|) , та и через ключ 10 на тактовый, вход регистра 15 сдвига, каждый тактовый импульс сдвигает единичный импульс 1 (записанный в момент взя тия отсчета сигнала в первую ячейку регистра 15 сдвига) в следующий разряд регистра 15. Поэтому при считьшании порогового напряженияУ ,и n,t, „..регистр 15 одновременно открывает соответствующий m , m +1),,.. вход коммутатора 17 (или 18). Следовательно, в момент срабатывания схемы 9 сравнения это импульс поступает через открытый вход коммутатора 17 (или 18) в соответствующий счетчик hij (кп +1) , . блока 19 счетчиков. Этот же импуль подается на унравлягаций вход ключа 10, закрывая его, и на управляющий вход (вход Сброс) счетчика 6, уст навливая его в нулевое состояние. При подаче с второго-выхода бло ка 14 синхронизации следукщего управляквдего ()-ro импульса он поступает на управляющий вход блока 2 вычртания, формируя отсчет сигнала )bt на управляющий вход Установка нуля (сброс) регистра 15 сдвига, и через элемеЕгг задержки 16 на информационньлй вход (установка ) этого же регист1;.а 15 сдвига, благодаря чему в блоках анализатора начинается следующий цикл обработки сигнала. Последующие преобразования, т.е. формирование модуля сравнение его поочередно с пороговыми напряжениями (фигс2а, б), определение знака (г. ) и запись единичного импульса с выхода схемы 9 сравнения в соответствугадий счетчик блока 19 счетчиков производится аналогично в камодом цикле, в результате чего в счетчиках накапливается оценка плотности распределения амплитуд (фиг.2в). Таким образом, благодаря такой последовательности микроопераций обеспечивается новая по сравнению с прототипом вычислительная процедура с заданием шкалы анализа с шагом аргумента, пропорциональным максимальному значению сигнала, что позволяет без увеличения погрешности вычислять- плотности распре делений в широком диапазоне изменения амплитуд, а отсутствие операций записи и считывания данных, характерных для цифровых анализатор ров, позволяет упростить структуру анализатора и величить его быстродействие, а уменьшение требования к блокам обеспечивается введением режима центрирования и распределения выборок в счетчики в зависимости от их знака. Применение предлагаемого анализатора для оперативной обработки случайных сигналов в условиях априорной неопределенности их амплитудных свойств актуально в научных и технических эксперимвнтах, например , при дистанционном зондировании морской поверхности по комплексной программе Освоение Мирового океана , при технической диагностике различных объектов, а также при медицинских исследованиях, требуквдих простого обслуживания аппаратуры при небольших затратах подготовительного времени на пробные эксперименты и минимальном участии человекаоператора.

(t) V

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Адаптивный анализатор плотности распределения вероятностей | 1986 |

|

SU1310841A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2012052C1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

АДАПТИВНЬТЙ АМПЛКТУДНЬТЙ АНАЛИЗАТОР, содержащий блок вычитания, первый информационный вход которого является входом анализатора, а тактовый вход блока вычитания объединен с входом сброса регистра сдвига и соединен с первым выходом блока синхронизации, второй выход которого подключен к информационному входу счетчика, разрядные выходы которого соединены соответственно с разрядными входами дешифратора, разрядные выходы которого подключены к первой группе разрядных входов первого коммутатора, вторая группа разрядных входов которого соединена соответственно с выходами блока задания весовых коэффициентов, разрядные выходы регистра сдвига подключены соответственно к разрядным входам второго коммутатора, разрядные выходы которого соединены соответственно с первой группой входов блока счетчиков, отличающий ся тем, что, с целью повышения точности в условиях априорной неопределен-. ности свойств сигнала, он содержит дискриминатор знака, третий коммутатор, ключ, элемент задержки, схему сравнения, элементы И, вычислитель максимума, формирователь модуля и усреднитель, вход которого подключен к входу анализатора, а выход является первым выходом анализатора и подключен к второму информационному входу блока вычитания, выход которого соединен с входом дискриминатора знака и входом формирователя модуля, выход которого подключен к первому входу схемы сравнения и информационному входу вычислителя максимума, тактовый вход которого i соединен с третьим выходом блока синхрЬнизации, а выход - подключен к входу блока задания весовых коэффициентов, второй вход схемы сравнения соединен с выходом первого коммутатора, а выход подключен к входу сброса счетчика и к информационным входам ключа и первого и второго элементов И, управлякйше входы которых соединены соответ-. ственно с первым и вторым знаковыми выходами дискриминатора знака, vj а выходы элементов И подключены X 4 00 СП соответственно к информационным входам второго и третьего коммутаторов, разрядные входы третьего коммутатора подключены к разрядным выходам регистра сдвига, а разрядные выходы третьего коммутатора соединены с второй группой входов блока счетчиков соответственно, выход блока счетчиков является вторым выходом анализатора, тактовий вход ключа соединен с вторым выходом блока синхронизации, первый выход которого подключен через элемент задержки к информационному входу регистра сдвига, сдвиговый вход которого соединен с выходом ключа.

. /

a

(iui) ,,

I/ ч

f

Ixil IXdmex

2И

fZ3--- к

1

/. / J ... Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Статистические информационные системы | |||

| Киев | |||

| Наукова думка, 1979, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1984-03-07—Публикация

1982-09-28—Подача