со со

;Р

Ч

О5 Од

1

tfia.i

Изобретение относится к вычислительной технике и предназначено для анализа вероятностных характеристик случайных сигналов для анализа веро- ятностных характеристик случайных сигналов в задачах распознавания и идентификации свойств данных,

Цель изобретения - уменьшение времени анализа.

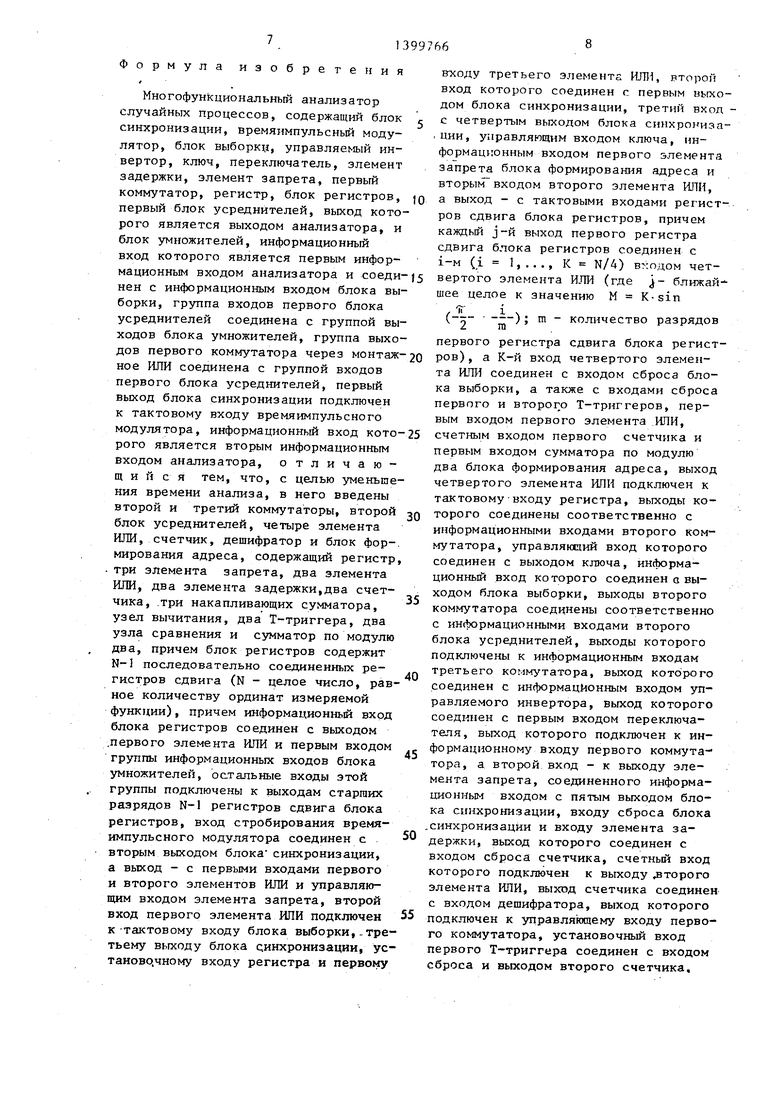

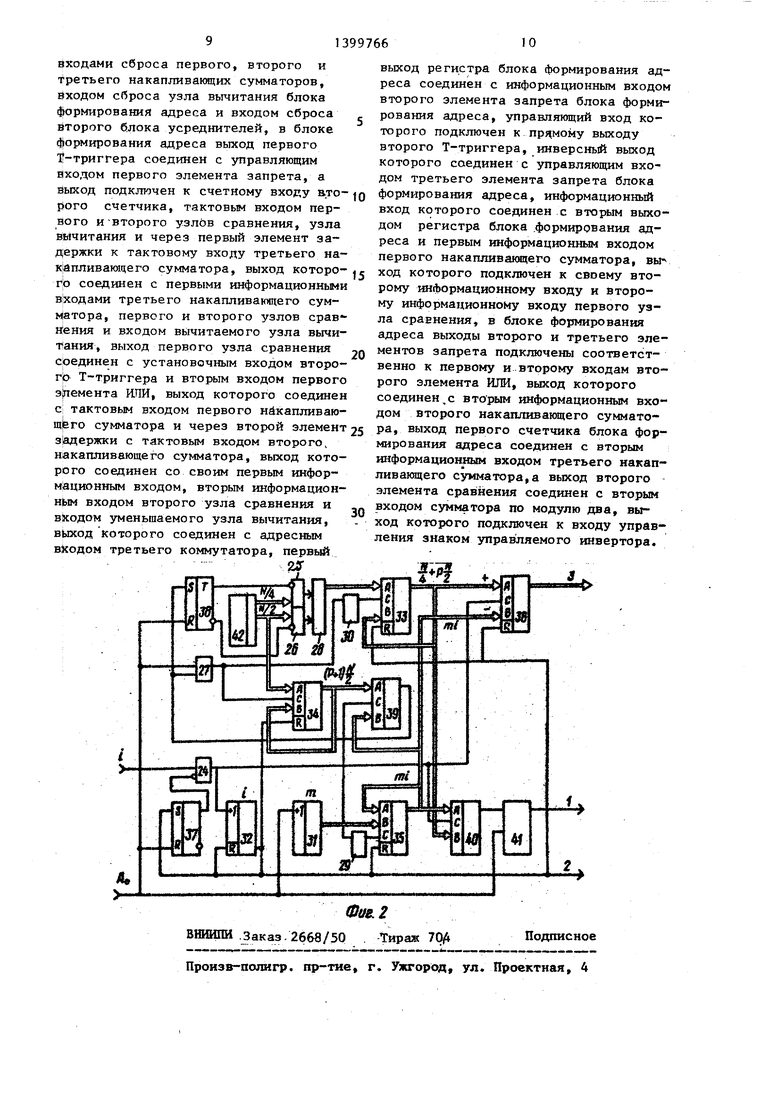

На фиг.1 изображена структурная схема многофункционального анализатора случайных цроцессов; на фиг,2 - структурная схема блока формирования адреса,

Mнoгoфy гкциoнaльный анализатор . случайных процессов (фиг.1) состоит из блока 1 синхронизации, времяим- пульсного модулятора 2, первого 3, третьего 4 и четвертого 5 элементов ИЛИ, блока 6 регистров, блока 7 умножителей, первого блока 8 усредните- :лей, блока 9 выборки, ключа 10, ре- :гистра П, второго блока 12 усреднимте л ей, управляемо го инвертора 13, пе- реключателя 14, первого коммутатора 15, блока 16 формирования адреса, второго элемента .ИЛИ 17, элемеита 18 запрета, элемента 19 задержки, счетчика 20, дешифратора 21, второго 22 и третьего 23 коммутаторов.

Блок формирования адреса (фиг.2) состоит из первого 24, второго 25 и третьего 26 элементов запрета, перво |го 27 и второго 28 элементов ИЛИ, первого 29 и второго 30 элементов за держкь, первого 31 и второго 32 счетчиков, первого 33, второго 34 и третьего 35 накапливающих сумматоров, узла 36 вычитария, первого 37 и второго 38 Т-триггеров, первого 39 и второго 40 узлов сравнения, сумматора 1 по модулю два и регистра 42, Многофункциональный анализатор случайньсх процессов работает в трех режимах: вычисление корреляционной функции и Лурье-преобразования сигнала (амплитуцного спектра) и плотност распределения вероятностей.

При вычислении корреляционной ,., функции выполнение последовательное- ти преобразований сигнала производится в соответствии с алгоритмом Стиль тьеса,

На выходе 1 блока 1 синхронизации вырабатьшаются тактовые импульсы с интервалом it, а на выходе 2 - строб импульсы дискретизации mut.

Q

5

0 5 Q

0

0

5

Непрерывньй сигнал X(t) поступает непосредственно на вход блока 7 умножителей. С выхода времяимпульсного модулятора 2 подаются отсчеты квантованного сигнала Y(mut) в виде пачек импульсов L (шириной п квантов) которые через первый элемент ИЛИ 3 поступают на информационный вход блока 6 регистров и при помощи тактовых импульсов сдвигаются в нем, одновременно поступая на вторые входы блока 7 умножителей, выходные сигналы с N выходов которого подаются на соответствующие входы первого блока 8 усреднителей.

По окончании реализации сигнала X(t) в первом блоке 8 усреднителей будет сформировано N ординат корреляционной функции в реальном масштабе времени в соответствии с алгоритмом Стильтьеса.

Вычисление спектра сигнала осуществляется следующим образом,

В исходном состоянии переключатель I4 подключен к выходу управляемого инвертора 13,

Анализируемьй сигнал подается на вход Х анализатора, являющийся входом блока 9 выборки, Стробимпульсы m с выхода 3 блока 1 синхронизации осуществляют дискретизацию сигнала, от- счеты X(mAt) которого запоминаются в блоке 9 выборки на время , Тактовые импульсы i с выхода 4 блока 1 синхронизации стробируют ключ 1-0, осуществляя ряд считываний отсчета X(mAt) Х во второй блок 12 усреднителей через второй коммутатор 22,

Одновременно стробимпульс m поступает на установочньй вход регистра 11, устанавливая все его разряды в состояние , т,е, открывая все выходы второго коммутатора 22, и через первый элемент ИПИ 3 на информационный вход блока 6 регистров, устанавливая в состояние 1 первый разряд первого регистра сдвига блока 6 регистров. По каждому i-му тактовому импульсу в состояние 1 устанавливается очередной i-й разряд 100,,,О, 010,,,О, 0010„..О и т.д. При сдвиге единичного состояния н разряд, соответствующий выходу j I первого регистра сдвига блока 6 регистров, на выходе четвертого-элемента ИЛИ 5 формируется импульс, осуществляющий сдвиг на один разряд содержимого регистра 11, устанавливая его равным 0111.,,1,

Вследствие этого закрывается 1-й выз- ход второго коммутатора 22 и прекращается накапливание импульсов амплитудой Х в 1-го ячейку второго блока 12 усреднителей, содержимое которой при этом является пропорциональным произведению

X sin

ьт мч

---лг,.

По мере сдвига единичного ния разрядов и установления его на следующих выходах j 2, 3,..., К происходит соответствующее поступление импульсов с выхода четвертого элемента ИЛИ 5 на вход регистра I1, вследствие чего -осуществляется сдвиг его содержимого в состояния 001 Г... fo0011...lj и т.д. до состояния fOOO...O, при котором закрываются все выходы второго коммутатора 22, запрещая накапливание во всех К ячейках второго блока 12 усреднителей.

Вследствие того, что микрокоманды запре та записи поступают с ряда j 1, К первого регистра сдвига блока 6 регистров через интервалы времени , пропорциональные приращениям первой четверти синусной функции, во втором блоке 12 усреднителей накапливается ряд произведений четверти периода синуса на т-й отсчет входного сигнала

Wr j 1,

2 м- sin ---

2,..., К.При поступлении импульса с К-го выхода блока 6 регистров он одновре-, менно подается на вход сброса блока 9 выборки, устанавливая его содержимое равным нулю, и на вход блока 16 формирования адреса, являясь для него микрокомандой установки начального -условия Ад и разрешения преобразований кодов. Эта микрокоманда устанавливает Т-триггеры 37 и 38 (фиг,2) в начальное состояние, при котором открыты первый 24 и второй 25 элементы запрета, а в первом счетчике 31 шага аргумента устанавливается код т. После этого микрокоманда поступает через первый элемент ИЛИ 27 и второй элемент 30 задержки на тактовые входы накапливакяцих сумматоров 33 и 34, разрешая запись в них соответственно кода N/2 и начального граничного значения кода АГО Ад N/4 из регистра 42, а тактовый импульс устанавли-:

вает во i 1 и в узле N/4.

втором счетчике 32 содержимое

разрешает операп.ию ныччтания

36 вычитания |А,д| N/4 .- О

Через интервал времени Г « ,, заданный первым элементом 29 яадержки, тактовый импульс разрешает запись в третий накапливающий сумматор 35 начального кода, рав- кого значению т, из первого счетчика 31. По следующим тактовым импульсам в третьем накапливающем суммато- ре 25 поочередно формируются суммы (т + га) 2т, (т + 2tn) Зга,. .., (mi) , которые используются для формирования выходного кода в узле 36 вычита

ния N/4 - mi.

Эти значения кода подаются на адресный вход третьего коммутатора 23, осуществляя считывания значений произведений из соответствующих ячеек j {К N/4, (К-т) , (К-2т), . .-. ..., (K-mi),...j второго блока 12 усреднителей. Эти выборки поступают через управляемый инвертор 13 на вход первого коммутатора 15. Так как одновременно с преобразованием кодов в блоке 16 формирования адреса тактовые импульсы подаются через второй элемент ИЛИ 17 на счетный вход счетчика 20, в нем формируется ряд чисел, дешифратор 21 преобразует их, управляя накапливанием по индексу п, т.е. последовательно открывая ключи 1, 2, 3,..., п,... первого коммутатора 15 для распределения выборе к на соответствукяцие входы первого блока 8 усреднителей.

При этом в первом узле 39 сравнения осуществляются операции сравнения текуг5их кодов mi с граничными условиями (р N/2), изменяющимися при

переходе функцией косинуса экстре- мальт 1х значений, а во втором узле 40 сравнения - операции сравнения текущих кодов с кодами граничных условий (N/4 + р N/2), установленных в первом

накапливающем сумматоре 33. При срабатывании второго узла 40 сравнения происходит изменение состояния сумматора 41 по модулю два, управляющего знаком (il) коэффициента передачи управляемого инвертора 13 в соответствии с законом косинусоиды.

В общем случае процедура управления знаком управляемого инвертора 13 и формирования кодов адресов опроса

третьего коммутатора 23 в течение тактов описывается соотношениями:

Предыдущий знак при N . N

mi

. , р .

sgn С ,

Измененный знак tni

N ,

-г- +

-Т Ш1

N mis ---;

N

р - mi

mi

де р 0,2т - номер перехода функции через нулевой уровень.

Следовательно, по каждому i-му fактовому тшпульсу с второго блока 12 Усреднителей считывается определеннай Фрдината косинусной функции с соот- ветствуклдим знаком при гааге аргумента uA, равным номеру m отсчета входного сигнала (X ), и распределяется 3 п-ю ячейку первого блока 8 усредниteлeй. При этом за N тактов независи- 30 МО от номера m входного отсчета в йервый блок 8 усреднителей считывают- |;я все N значений произведения, вход- фого отсчета на та периодов косинус- йой функции.

При номере тактового импульса, превыгаакщем на единицу количество импульсов-В пачке L , т.е. п:ри i (п + О, .элемент 18 запрета оказы вается не закрытым импульсом на управляющем входе, поэтому (.п+1)-й тактовый импульс поступает через пе реключатель 14 и п-й ключ первого коммутатора 15 на п-й вход первого

1C

Процедура анализа.спектра заканчи- блока 8 усреднителей. Одновременно

(п+1)-й тактовь1Й импульс постзттает через элемент 19 задержки на вход обнуления счетчика 20, возвращая е через интервал времени ьТ 0,5 t в нулевое состояние, а также являе ся импульсом сброса S, для блока синхронизации: импульс У поступа на вход сброса блока 1 синхронизации, запрещая прохождение тактовых импульсов на выход 4 в течение инт вала времени до следующего (ш+О-го стробимпульса на выходе 2 (исключая ложное поступле гае информации в пе вый блок 8 усреднителей).

йается по окончании o6pa6oTKH.in-N-ro Отсчета сигнала, т.е. при считьюании -го значения произведения {0м1{ фервый блок 8 усреднителей. При этом во втором счетчике 32 блока 16 форми- |)ования адреса образуется импульс пе- |)еполнения, который устанавливает в исходное состояние все элементы блока 16 формирования адреса и обнуляет Второй блок 12 усреднителей.

В результате процедуры анализа че рез синтез ряда Фурье в первом блоке 8 усреднителей сформирован дискрет-, иый ряд ординат, характеризующих спектральное распределение частот

1 JL (mut)

П 1

, n о , 1,.. ., (т1-1) .

2m р

nC-i)

Р О

Вычисление плотности распределения вероятностей осуществляется следующим образом.

в исходном состоянии переключатель 14 подключен к выходу элемента 18 запрета.

Анализируемый сигнал подается на вход Y анализатора, являющийся входом времяимпульсного модулятора 2,- стробимпульсы осуществляют дискретизацию сигнала, а по тактовым импульсам с выхода блока 1 синхронизации осуществляется квантование-преобразование в гаиротно-модулирова.нный вид, т.е. в пачку импульса .L количеством п импульсов в каяодой пачке.

По мере формирования пачки импульсов оьш поступают с выхода времяимпульсного модулятора 2 на управлякяций вход элемента 18 запрета, закрывая

его на эти моменты для прохождения тактовых импульсов, а также через второй элемент ШШ 17 на счетный вход счетчика 20, увеличивая его содержимое. Дешифратор 21 поочередно (от 1

до п-го) замыкает ключи первого коммутатора 15.

При номере тактового импульса, превыгаакщем на единицу количество импульсов-В пачке L , т.е. п:ри i (п + О, .элемент 18 запрета оказывается не закрытым импульсом на управляющем входе, поэтому (.п+1)-й тактовый импульс поступает через переключатель 14 и п-й ключ первого коммутатора 15 на п-й вход первого

блока 8 усреднителей. Одновременно

(п+1)-й тактовь1Й импульс постзттает через элемент 19 задержки на вход обнуления счетчика 20, возвращая его через интервал времени ьТ 0,5 t в нулевое состояние, а также является импульсом сброса S, для блока 1 синхронизации: импульс У поступает на вход сброса блока 1 синхронизации, запрещая прохождение тактовых импульсов на выход 4 в течение интервала времени до следующего (ш+О-го стробимпульса на выходе 2 (исключая ложное поступле гае информации в первый блок 8 усреднителей).

Таким образом, по окончании реализации исследуемого случайного процесса в первом блоке 8 усреднителей сформированы дискретные значения оцен- 55 ки плотности распределения вероятностей амплитуд со статистической по- rpemHocTbjra, определяемой количеством аналлзиру емых отсчетов М входного

Формула изобретения

Многофункциональный анализатор случайных процессов, содержащий блок синхронизации, времяимпульсный модулятор, блок выборки, управляемый инвертор, ключ, переключатель, элемент задержки, элемент запрета, первый коммутатор, регистр, блок регистров, первый блок усреднителей, выход которого является выходом анализатора, и блок умножителей, информационный вход которого является первым информационным входом анализатора и соеди нен с информационным входом блока выборки, группа входов первого блока усреднителей соединена с группой выходов блока умножителей, группа выходов первого коммутатора через монтаж ное РШИ соединена с группой входов первого блока усреднителей, первый выход блока синхронизации подключен к тактовому входу времяимпульсного модулятора, информационный вход кото рого является вторым информационным входом анализатора, отличаю- щ и и с я тем, что, с целью уменьшения времени анализа, в него введены второй и третий коммутаторы, второй блок усреднителей, четыре элемента ИЛИ, счетчик, дешифратор и блок формирования адреса, содержащий регистр три элемента запрета, два элемента ИЛИ, два элемента задержки,два счетчика, .три накапливающих сумматора, узел вычитания, два Т-триггера, два узла сравнения и сумматор по модулю два, причем блок регистров содержит N-1 последовательно соединенных регистров сдвига (N - целое число, равное количеству ординат измеряемой функции), причем информационный вход блока регистров соединен с выходом .первого элемента ИЛИ и первым входом группы информационных входов блока умножителей, остальные входы этой группы подключены к выходам старгаих разрядов N-1 регистров сдвига блока регистров, вход стрОбирования время- импульсного модулятора соединен с вторым выходом блока синхронизации, а выход - с первыми входами первого и второго элементов ИЛИ и управляющим входом элемента запрета, второй вход первого элемента ИЛИ подключен к-тактовому входу блока выборки,-третьему выходу блока синхронизации, ус- таново.чному входу регистра и первому

о 5 0 5 Q 5

5

0

5

0

входу третьего элемента ИЛИ, второй вход которого соединен с первым ныхо- дом блока синхронизации, третий вход - с четвертым выходом блока синхро}тиза- |Ции, управляющим входом ключа, информационным входом первого элемента запрета блока формирования адреса и вторым входом второго элемента ИЛИ, а выход - с тактовыми входами регистров сдвига блока регистров, причем каждый j-й выход первого регистра сдвига блока регистров соединен с i-M (i 1,..., К N/4) входом четвертого элемента ИЛИ (где - ближай-- шее целое к значению М К-sin

(). и, количество разрядов

2 га

первого регистра сдвига блока регистров) , а К-й вход четвертого элемента ИЛИ соединен с входом сброса блока выборки, а также с входами сброса первого и второго Т-триггеров, первым входом первого элемента ИЛИ, счетным входом первого счетчика и первым входом сумматора по модулю два блока формирования адреса, выход четвертого элемента ИЛИ подключен к тактовомувходу регистра, выходы которого соединены соответственно с информационными входами второго коммутатора, управляющий вход которого соединен с выходом ключа, информационный вход которого соединен а выходом блока выборки, выходы второго коммутатора соединены соответственно с информационными входами второго блока усреднителей, выходы которого подключены к информационньгм входам третьего коммутатора, выход которого соединен с информационным входом управляемого инвертора, выход которого соединен с первым входом переключателя, выход которого подключен к информационному входу первого коммутатора, а второй вход - к выходу элемента запрета, соединенного информационным входом с пятым выходом блока синхронизации, входу сброса блока .синхронизации и входу элемента задержки, выход которого соединен с входом сброса счетчика, счетный вход которого подключен к выходу второго элемента ИЛИ, выход счетчика соединен с входом дешифратора, выход которого подключен к управля ощему входу первого коммутатора, установочный вход первого Т-триггера соединен с входом сброса и выходом второго счетчика.

входами сброса первого, второго и третьего накапливающих сумматоров, входом сброса узла вычитания блока формирования адреса и входом сброса второго блока усреднителей, в блоке формирования адреса выход первого Т-триггера соединен с управляющим входом первого элемента запрета, а

139976610

выход регистра блока формирования ад реса соединен с информационным входо второго элемента запрета блока форми 5 рования адреса, управляющий вход которого подключен к пржмому выходу второго Т-триггера, инверсный выход которого соединен с управляющим входом третьего элемента запрета блока

йыход подключен к счетному вхопу Iro- TJ элемента запрета блока .ого счетчика, тактовьЛход м п:: ° информационньй

рого счетчика, тактовым входом первого и-второго узлов сравнения, узла вычитания и через первый элемент задержки к тактовому входу третьего на- к|апливающего сумматора, выход которо-,, то соединен с первыми информационньми входами третьего накапливающего сумматора, первого и второго узлов срав- и входом вычитаемого узла вычитания, выход первого узла сравнения соединен с установочным входом второ- г|о Т-триггера и вторым входом первого элемента ИПИ, выход которого соединен с тактовым входом первого нйкапливающЬго сумматора и через второй элемент Г накапливающего суммато- зМержки с ..ктовым вход:Ито::Г 25Ра. выход первого счетчика блока форз адержки с тактовым входом второго накапливающего сумматора, выход которого соединен со своим первым информационным входом, вторым информацион- HbiM входом второго узла сравнения и вводом уменьшаемого узла вычитания, выход которого соединен с адресным входом третьего коммутатора, первый

2ff

вход которого соединен с вторым выходом регистра блока .формирования адреса и первым информационным входом первого накапливающего сумматора, выход которого подключен к своему второму шформационному входу и второму информационному входу первого узла сравнения, в блоке формирования адреса вьпсоды второго и третьего элементов запрета подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен.с вторым информационным входом второго накапливающего суммато30

мирования адреса соединен с вторым информационтам входом третьего накапливающего сумматора,а выход второго элемента сравнения соединен с вторым входом сумматора по модулю два, выход которого подключен к входу управления знаком управляемого инвертора.

6610

выход регистра блока формирования адреса соединен с информационным входом второго элемента запрета блока форми- рования адреса, управляющий вход которого подключен к пржмому выходу второго Т-триггера, инверсный выход которого соединен с управляющим входом третьего элемента запрета блока

TJ элемента запрета блока информационньй

TJ элемента запрета блока информационньй

Г накапливающего суммато- Ра. выход первого счетчика блока форвход которого соединен с вторым выходом регистра блока .формирования адреса и первым информационным входом первого накапливающего сумматора, выход которого подключен к своему второму шформационному входу и второму информационному входу первого узла сравнения, в блоке формирования адреса вьпсоды второго и третьего элементов запрета подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен.с вторым информационным входом второго накапливающего сумматоГ накапливающего суммато- Ра. выход первого счетчика блока фор

мирования адреса соединен с вторым информационтам входом третьего накапливающего сумматора,а выход второго элемента сравнения соединен с вторым входом сумматора по модулю два, выход которого подключен к входу управления знаком управляемого инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

Йногофункциональный анализатор случайных процессов относится к специализированным средствам вычисли- .х- .тельной техники, предназначенным для исследования вероятностных свойств случайных процессов. Устройство вычисляет корреляционную функцию, реализует Фурье-преобразование сигнала и определяет плотность распределения. Цель изобретения - уменьшение времени анализа. Устройство содержит блок 1 синхронизации, времяимпульсный модулятор 2,.блок умножителей 7, блок регистров 6, четыре элемента ИЛИ 3, 4, 5 и 17, блок выборки 9, ключ 10, регистр 11, три коммутатора 15, 22 . и 23, два блока усреднителей 8 и 12, управляемый инвертор 13, блок 16 формирования адреса, переключатель 14, элемент запрета 18, элемент задержки 19, счетчик 20 и дешифратор 21. 2 ил. с $ (Л

| Время-импульсный анализаторСигНАлА | 1979 |

|

SU817725A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР Р 1180924, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-07-29—Подача