мяти соединен со вторым входом четвертого элемента 2И-НЕ, выход которого подключен к управляющему входу вычитающего счетчика, шестой информационный выход узла постоянной па-. мяти подключен ко второму входу второго сумматора по модулю два i го узла блокировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1981 |

|

SU999062A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1980 |

|

SU922763A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1985 |

|

SU1298766A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый и второй реверсивные счетчики, дадифратор, регистр, N узлов блокировки, блок управления, вькоды переноса и эаема первого реверсивного счетчика соединены соответственно с суммирующим и вычитакщим входами второго реверсивного счетчика, информационный выход которого соединен со входом дешифратора, информационный выход регистра является информационньол выходом устройства, каждьл из Н узлов блокировки содержит элемент 2И-НЕ, элемент. 2ИЛИ-НЕ и два сумматора по модулр . два, причем выход элемента 2 ИЛИ-НБ подключен к первому входу первого сумматора по модулю два, выход которого подключен к первому входу второго сумматора по модулю два, второй вход первого сумматора по модулю два соеДинен с выходом элемента 2И-НЕ, первый вход которого объединен с первым входом элемента 2 ИЛИ-НЕ, при этом втор вход элемента 2 ИЛИ-НЕ л-го (i«l,N) узла блокировки соединен с выходом i го разряда первого реверсивного счетчика, выход второго сумматора по модулю два i-го узла блокировки соединен со входом -го разряда регистра и входим-i-го разряда первого реверсивного счетчика, отличающееся тем, что, с целью расширения функционсшьных возможностей за счет реализации алгоритмов с различными основаниями, в него введен вычитающий счетчик, выход j-го (jri,Eog к, к-основанйе алгоритма) разряда котоГрого подключен ко второму входу элемента 2И-НЕ с-го ( bj Щг) +2EogjX«,N) узла блокировки, а 8 -ый ( I 0, М-1) выход дешифратора подключен к первому входу элемента 2 ИЛИ-НЕ -го (is - og4lcH, Eog) узла блокировки, причём елок управления содержит счетчик, узел постоянной памяти и четыре элемента 2И-НЕ, при этом тактовый вход счетчика и первые вхо(О ды элементов 2И-НЕ объединены между собой и являются тактовымчвходом С устройства, информационный выход счетчика подключен к. адресному вхоQ ду узла постоянной памяти, вход С старшего разряда адресного входа которого подключен к выходу старше.го разряда дешифратора, первый информационный выход узла постоянной эо памяти подключен ко второму входу . первого элемента 2И-НЕ, выход которого подключен к суммирующему входу первого реверсивного счет чика, второй информационный выход х узла постоянной памяти соединен со вторьм входом втброго элемента 2ИНЕ, выход которого подключён к вычитающему входу первого реверсивного счетчика, третий информационный выход узла постоянной памяти соединен со вторь входом третьего эле-, мента 2И-НЕ, выход которого подключен ко входу занесения информации первого реверсивного счетчика, четвертый информационный выход узла постоянной псмяти подключен к тактовому входу регистра, пятый информационный выход узла постоянной па

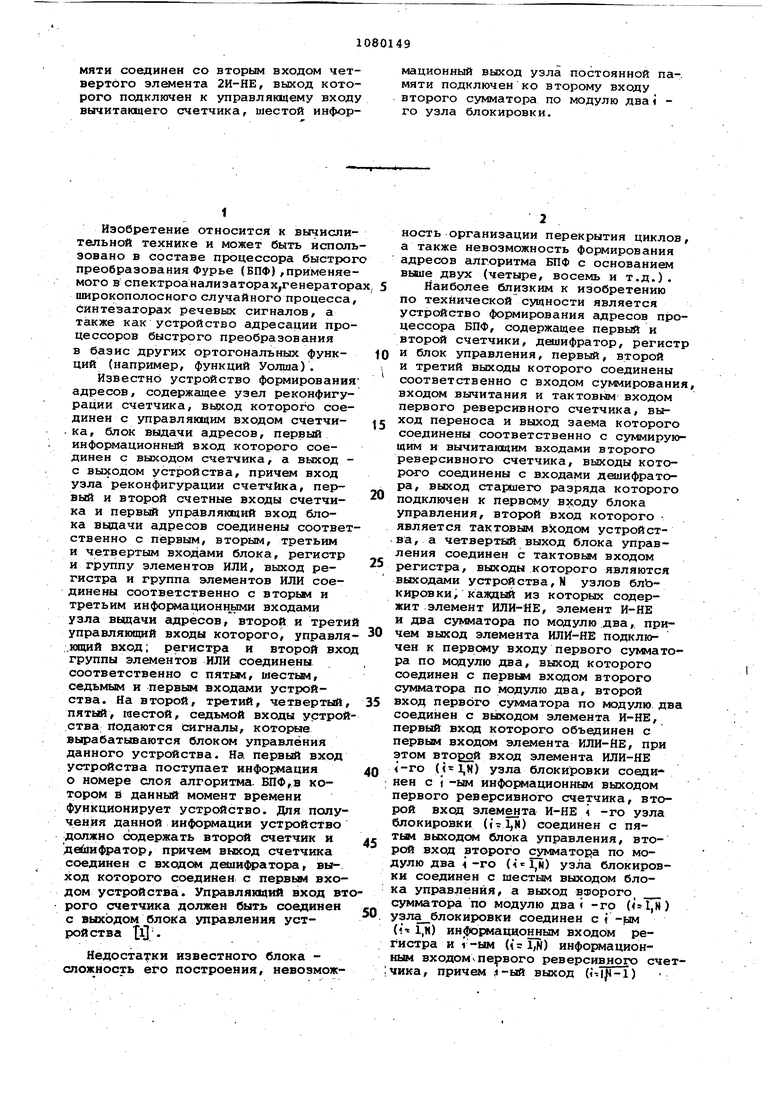

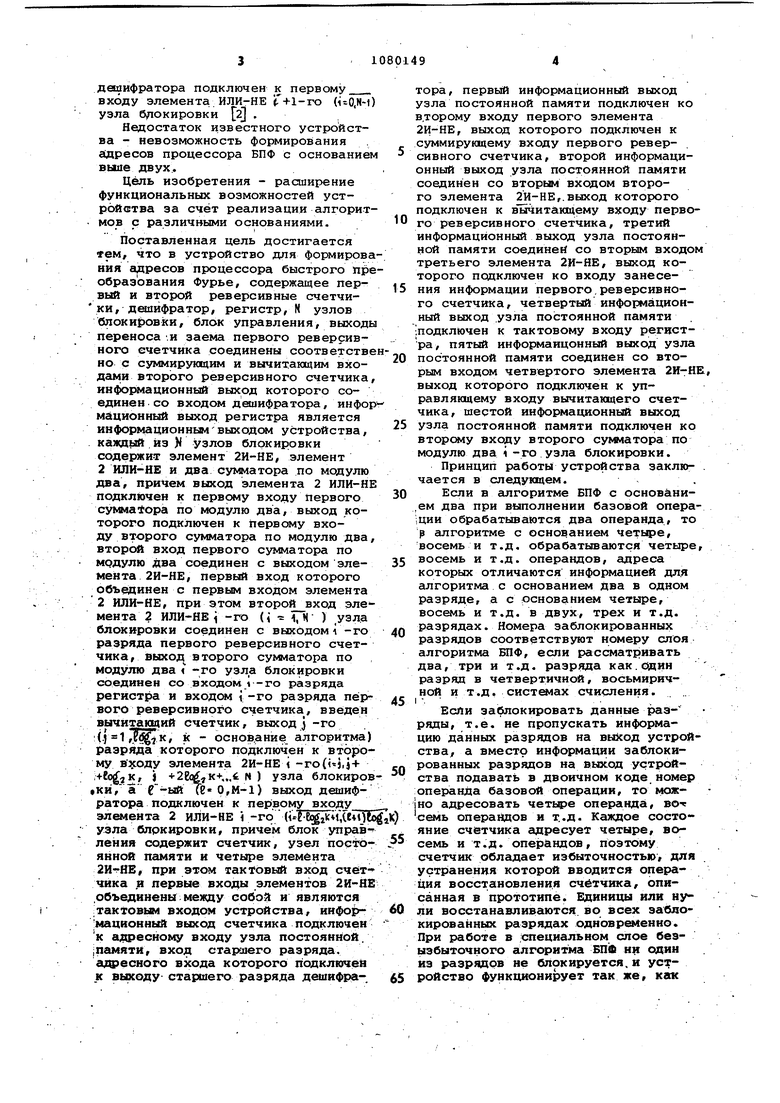

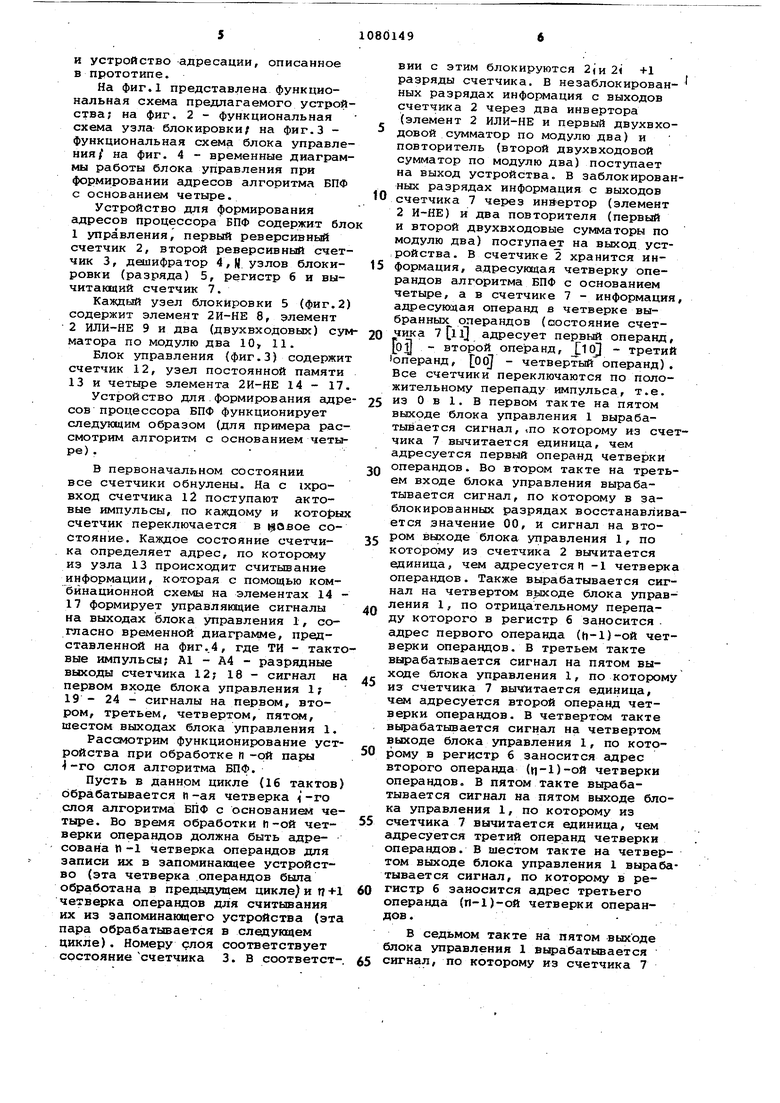

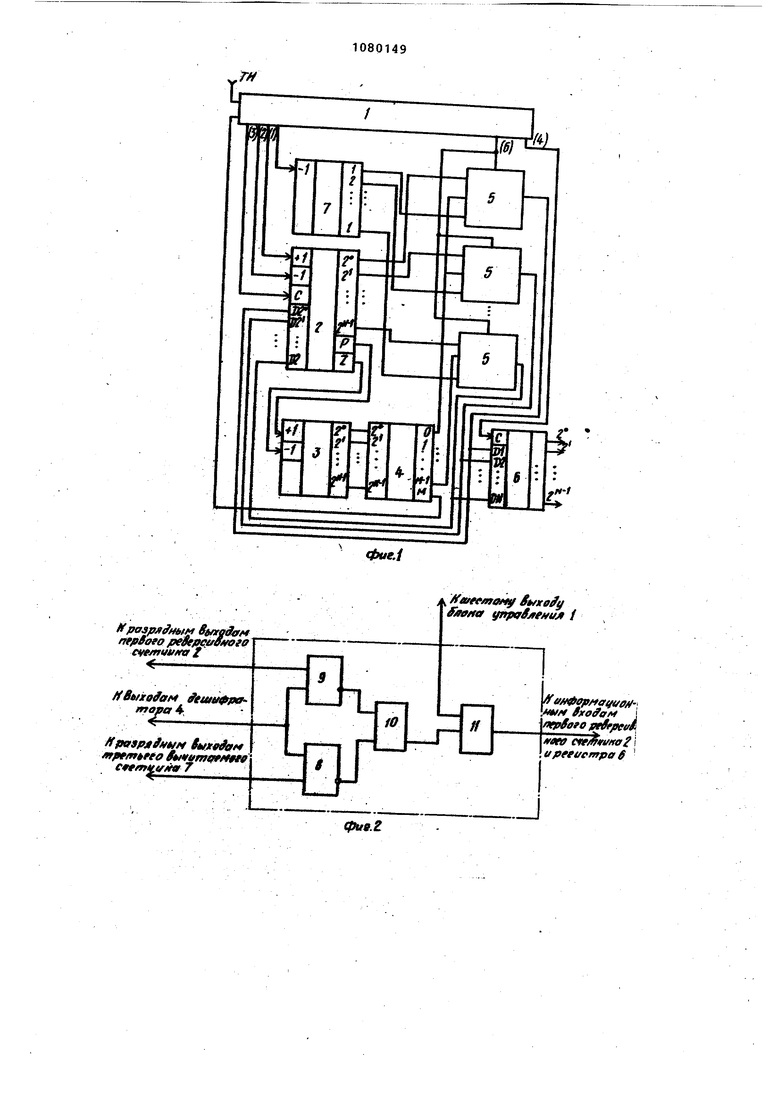

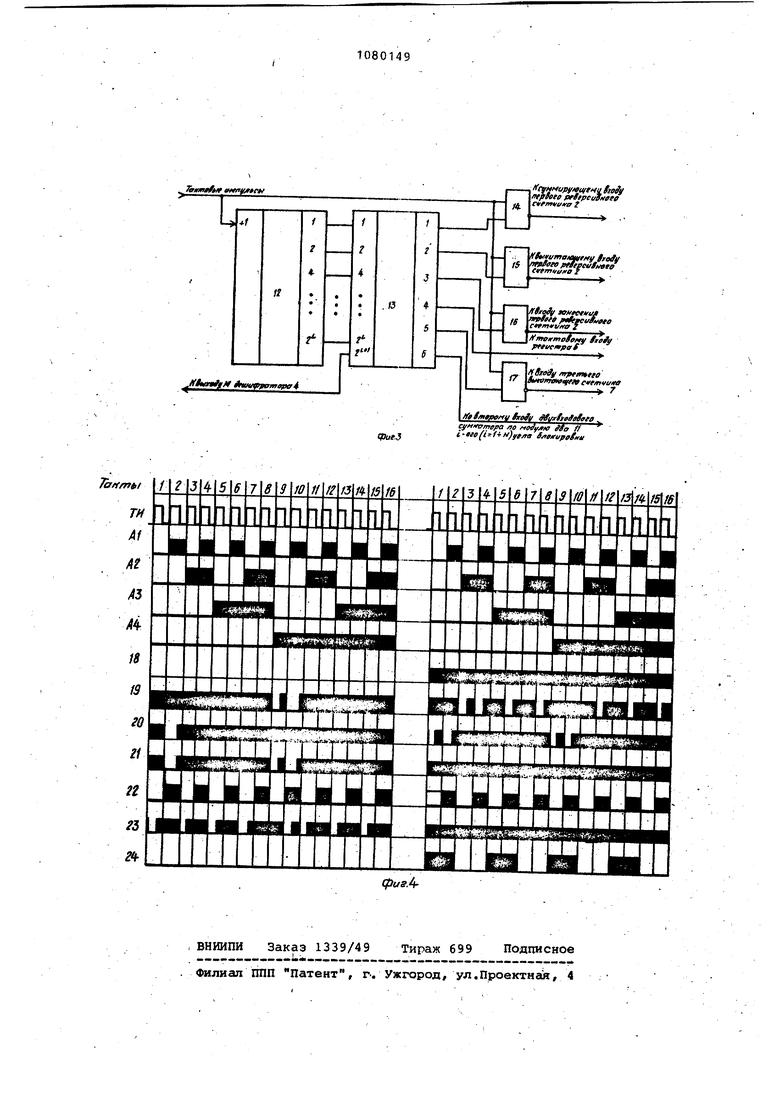

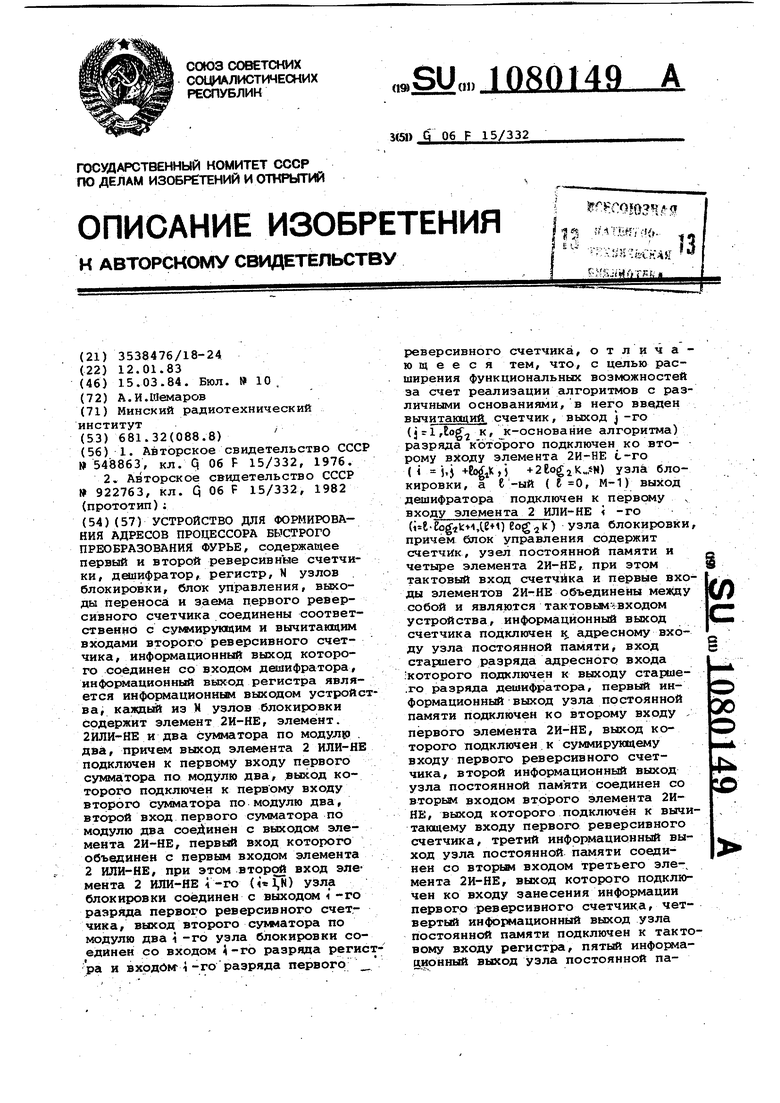

Изобретение относится к вычисли тельной технике и может быть испол зовано в составе процессора быстро преобразования Фурье (БПФ)/применяе мого в спектроанализаторах,генератор широкополосного случайного процесса Синтезаторах речевых сигналов, а также как устройство адресации про цессоров быстрого преобразования в базис других ортогональных функций (например, функций Уолша). Известно устройство формировани адресов, содержащее узел реконфигурации счетчика, вьрсод которого соединен с управляющим входом счетчи- ка, блок выдачи адресов, первый информационный вход которого соединен с выходом счетчика, а выход с выходом устройства, причем вход узла реконфигурации счетчика, первый и второй счетные входы счетчика и первый управлягаций вход блока вьщачи адресов соединены соответ ственно с первым, вторым, третьим и четвертым входами блока, регистр и группу элементов ИЛИ, выход регистра и группа элементов ИЛИ соединены соответственно с вторьвл и третьим информационными входами узла вццачи адресов, второй и трети управляющий входы которого, управля .ющий вход; регистра и второй вхо группы элементов ИЛИ соединены соответственно с пятьм, шестым, седьмым и первым входами устройства. На второй, третий, четвертый пятый, шестой, седьмой входы устрой ства подаются сигналы, которые вырабатываются блоком управления данного устройства. На первый вход устройства поступает инфо1 1ация о номере слоя алгоритма. БПФ,в котором S данный момент времени функционирует устройство. Для получения данной информации устройство должно содержать второй счетчик и де 11ифратор, причем выход счетчика соединен с входом дезакфр&тора, выход которого соединен с первьм входом устройства. Управляющий вход вт рого счетчика должен быть соединен с выходом блойа управления устройства ИНедостатки известного блока сложность его построения, невозможность организации перекрытия циклов, а также невозможность формирования адресов алгоритма БПФ с основанием выше двух (четыре, восемь и т.д.). Наиболее близким к изобретению по технической сзлцности является устройство формирования адресов процессора БПФ, содержащее первый и второй счетчики, дешифратор, регистр и блок управления, первый, второй и третий выходы которого соединены соответственно с входом суммирования, входом вычитания и тактовым входом первого реверсивного счетчика, выход переноса и выход заема которого соединены соответственно с суммирующим и вычитающим входами второго реверсивного счетчика, выходы которого соединены с входами дешифратора, выход старшего разряда которого подключен к первому входу блока управления, второй вход которого является тактовым вход сии устройства, а четвертый выход блока управления соединен с тактовьм входом регистра, выходы которого являются выходами устройства,N узлов блЬкировки, каждый из которых содержит элемент ИЛИ-НЕ, элемент И-НЕ и два сумматора по модулю два, причем выход элемента ИЛЙ-НЕ подключен к входу первого сумматора по модулю два, выход которого соединен с первым входом второго сумматора по модулю два, второй вход первого сумматора по модулю два соединен с В{яходом элемента И-НЕ, первый вхрд которого объединен с первым входом элемента ИЛИ-ЙЕ, при этом вто2Ой вход элемента ИЛИ-НЕ 4-го (1,N) узла блокировки соединен с i-ым информационным выходом первого реверсивного счетчика, второй вхсд элемента И-НЕ ч -го узла блокировки («trljN) соединен с пятым выходом блока управления, второй вход iBTOporo сумматора по модулю два (,N) узла блокировки соединен с шестым выходом блока управления, а выход вшорого сумматора по модулю два -го (1,Н) узла блокировки соединен с f -ым (i 1,Л) ин |О1Ж1ационным входим регистра и г-ым ( 1;N) информационным входом первого реверсивного счетчика, причем л-ый выход (-ф-1) дешифратора подключен к первому. входу элемента ИЛИ-НЕ Г+1-го (,N-i узла блокировки 2 . Недостаток известного устройства - невозможность формирования сЩресов процессора БПФ с основание выае двух. Цель изобретения - расширение функциональных возможностей устройства за счёт реализации алгорит мов с различными основаниями. .... Поставленная цель достигается ем, что в устройство для формирова ния адресов процессора быстрого пре образования Фурье, содержащее первый и второй реверсивные счетчи ки, дйпифратор, регистр, N узлов блоки)овки, блок управления, выходы переноса .и заема первого реверсивного счетчика соединены соответств но с суммирующим и вычитающим вхоДс1ми второго реверсивного счетчика информационный выход которого соединен -со входом даиифратора, инфор мационный выход регистра является информационнымвыхоДс « устройства, казкяый из ) узлов блокировки содержит элемент 2И-НЕ, элемент 2 ИЛИ-НБ и два сумматора по модулю два, причем выход элемента 2 ИЛИ-НЕ подключен к первому входу первого сумма ора по модулю два, выход которого подключен к первому входу второго сумматора по модулю два второй вход первого сумматора по мрдулю два соединен с выходом элемента 2И-НЕ, первый вход которого объединен с первым входом элемента 2 ИЛИ-НЕ, при этом второй вход элемента 2 ИЛИ-НЕ i -го ( V ) .узла блокировки соединен с выходом л -го разряда первого реверсивного счетчика, выход второго сумматора по модулю два « -го узла блокировки соединен со входом i-го разряда регистра и входом 1-го разряда пёр вого реверсивного счетчика, введен вычитаквдий счетчик, выход -го (.) 1, к - основ.ание алгоритма) разряда которого подключен к второму вуоду элемента 2И-НЕ -го(Ьз,1+ , i ,,,i. N ) узла блокиров кй, а С-ый Те- 0,М-1) выход дешифратора подключен к первому входу элемента 2 ИЛИ-НЕ -го (И it, jt узла блокировки, причем блок управлеиия содержит счетчик, узел постоянной памяти и четыре элемента 2И-гНЕ, при этом тактовый вход счетчика и первые входы элементов 2И-НЕ рбъединены между собой и являются тактовым входом устройства, инфо ;мацконный выход счетчика подключен к адресному входу узла постоянной. |памятй, вход cTap:iiero разряда. адресного входа которого подключен к выходу старшего разряда дешиф1 1-. тора, первьЁй информационный выход узла постоянной памяти подключен ко в.торому входу первого элемента 2И-НЕ, выход которого подключен к суммирукщему входу первого реверсивного счетчика, второй информационный выход узла постоянной паиняти соединен со вторым входом второго элемента 2И-НЕ,.выход которого подключен к вычитаюцему входу первого реверсивного счетчика, третий информационный выход узла постоянной памяти соединен со вторым входом третьего элемента 2И-НЕ, выход которого подключен ко входу занесения информации первого,реверсивного счетчика, четвертый информационный выход узла постоянной памяти подключен к тактовому входу регистра, пятый ннформаицонный выход уЗла постоянной памяти соединен со вторым входом четвертого элемента 2И-НЕ., выход которого подключен к управляющему входу вычитающего счетчика, шестой информационный выход узла постоянной памяти подключен ко второму входу второго сумматора по модулю два i-го узла блокировки. Принцип работы устройства заклю- . чается в следующем.. Если в алгоритме БПФ с основани,ем два при выполнении базовой опера;ции обрабатываются два операнда, то р алгоритме с основанием четыре, восемь и т.д. обрабатываются четыре, восемь и т.д. операндов, адреса которых отличаются информацией для алгоритма с основанием Два в одном разряде, а с основанием четыре, восемь и т.д. в двух, трех и т.д. разрядах. Номера заблокированных разрядов соответствуют номеру слоя алгоритма БПФ, если рассматривать два, три и т.д. разряда как.Сдцин разряд в четвертичной, восьмиричной и т.д. системах счисления. I -. . Если заблокировать данные раз- ряды, т.е. не пропускать информацию данных разрядов на выход устройства а вместо информации заблокированных разрядов на выход устройства подавать в двоичном коде номер операнда базовой операции, то можJHO адресовать операнда, вот семь операндов и т.д. Каждое состояние счетчика адресует четыре, восемь и т.д. операндов, поэтому счетчик обладает избыточностью, для устранения которой вводится операция восстановления счётчика, описанная в прототипе. Единицы или нули восстанавливаются, во всех заблокированных разрядах одновременно. При работе в специальном слое безызбыточного алгоритма БПА ни рдин из разрядов не блокируется, и устройство функционирует так же, как И устройство -адресации, описанное в прототипе. На фиг.1 представлена функциональная схема предлагаемого устрой ства; на фиг. 2 - функциональная схема узла блокировки, на фиг.З функциональная схема блока управле ния/ на фиг. 4 - временные диаграм мы работы блока управления при формировании адресов алгоритма БПФ с основанием четыре. Устройство для формирования адресов процессора БПФ содержит бл 1управления, первый реверсивный счетчик 2, второй реверсивный счет чик 3, дешифратор 4, (J узлов блокировки (разряда) 5, регистр 6 и вычитакжций счетчик 7. Каждый узел блокировки 5 (фиг.2 содержит элемент 2И-НЕ 8, элемент 2ИЛИ-НЕ 9 и два (двухвходовых) су матора по модулю два 10 11. Блок управления (фиг.З) содержи счетчик 12, узел постоянной памяти 13 и четыре элемента 2И-НЕ 14 - 17 Устройство для формирования адр сов процессора БПФ функционирует следующим образом (для примера рас смотрим алгоритм с основанием четы ре) . В первоначальном состоянии все счетчики обнулены. На с ixpoвход счетчика 12 поступают актовые импульсы, по каждому и которы счетчик переключается в овое состояние. Каждое состояние счетчика определяет адрес, по которому из узла 13 происходит считывание информации, которая с помощью комбинационной схемы на элементах 14 17 формирует управляющие сигналы на выходах блока управления 1, согласно временной диагракме, представленной на фиг..4, где ТИ - такт вые импульсы; А1 - А4 - разрядные выходы счетчика 12; 18 - сигнал н первом входе блока управления 1; 19 - 24 - сигналы на первом, втором, третьем, четвертом, пятом, шестом выходах блока управления 1. Расслютрим функционирование уст ройства при обработке п -ой пары )-го слоя алгоритма БПФ. Пусть в данном цикле (16 тактов обрабатывается п-ая четверка 1-го слоя алгоритма БПФ с основанием че тыре. Во время обработки и-ой четверки операндов должна быть адреcoaaka П-1 четверка операндов для записи их в запоминагадее устройство (эта четверка .операндов быгга обработана в предьщущем цикле) и г + четверка операндов для считывания их из запоминакхцего устройства (эт пара обрабатывается в следукщем цикле). Номеру слоя соответствует состояние счетчика 3. В соответст ВИИ с этим блокируются 2{и21 +1 разряды счетчика. В незаблокированных разрядах информация с выходов счетчика 2 через два инвертора (элемент 2 ИЛИ-НЕ и первый двухвходовой сумматор по модулю два) и повторитель (второй двухвходовой сумматор по модулю два) поступает на выход устройства. В заблокированных разрядах информация с выходов счетчика 7 через инвертор (элемент 2 И-НЕ) и два повторителя (первый и второй двухвходовые сумматоры по модулю два) nocTynaej: на выход устройства. В счетчике 2 хранится информация, адресующая четверку операндов алгоритма БПФ с основанием четыре, а в счетчике 7 - информация, адресуюдая операнд в четверке выбранных операндов (состояние счетчика 7 if адресует первый операнд, о - второй операнд, ) третий операнд, 00j - четвертый операнд). Все счетчики переключаются по положительному перепаду импульса, т.е. из О в 1. В первом такте на пятом выходе блока управления 1 вырабатывается сигнал, ,по которому из счетчика 7 вычитается единица, чем адресуется первый операнд четверки операндов. Во втором такте на третьем входе блока управления вырабатывается сигнал, по которому в заблокированных разрядах восстанавливается значение 00, и сигнал на втором выкоде блока управления 1, по которому из счетчика 2 вычитается единица, чем адресуется И -1 четверка операндов. Также вырабатывается сигнал на четвертом выходе блока управления 1, по отрицательному перепаду которого в регистр 6 заносится . адрес первого операнда (h-lJ-ой четверки операндов. В третьем такте вырабатывается сигнал на пятом выходе блока управления 1, по которому из счетчика 7 вычитается единица, чем адресуется второй операнд четверки операндов. В четвертс такте вырабатывается сигнал на четвертом выходе блока управления 1, по которому в регистр 6 заносится адрес второго операнда (ц-1)-ой четверки операндов. В пятом такте вырабатывается сигнал на пятом выходе блока управления 1, по которому из счетчика 7 вычитается единица, чем адресуется третий операнд четверки операндов. В шестом такте на четвертом выходе блока управления 1 вырабатывается сигнал, по которому в регистр б заносится адрес третьего операнда (п-1)-ой четверки операндов . В седьмом такте на пятом выходе блока управления 1 вырабатывается сигнал, по которому из счетчика 7

выч 1тается единица, чем адресуется четвертый операнд четверки операндов. В восьмом такте вырабатывается сигнал на четвертом выходе блока управления 1, по которому в регистр 6 заносится адрес четвертого операнда (.ti-l)-ofl четверки операндов. В девятом такте на третьем выходе блока управления 1 вырабатывается сигнал, по которому в заблокированных разрядах восстанавnkaaetcH значение llj и сигнал на первом выходе блока управления 1 по которому в счетчик 2 добавляется единица, чем адресуется и-ая четверка операндов. В десятом такте вырабатывается сигнал на третьем выходе блока управления 1, по которому в - заблокированных разрядах счетчика 2 восстанавливается значение jll / и сигнал на первом выходе блока управления 1, по которсму в счетчик 2 добавляется единица/ чем адресуется(и+1)-ая четверка операндов, кроме того, в этом такте вырабатывается сигнал на пятом выходе блока управления 1, по которому из счетчика 7 вычитается единица, чем адресуется первый операнд четверки операндов. Также в десятом такте вырабатывается сигнал на четвертом выходе блока управления 1, по которому в регистр 6 заносится первый операнд (п+1)-ой четверки операндов. В одиннадцатом такте вырабатывается сигнал на пятом выходе блока управления 1, по которс у из счетчика 7 вычитается единица, чем адресуется второй операид четверки операндов. В цвенадцатоМ такте на четвертом выходе блока управления 1 вырабатывается сигнгш, по которому в регистр 6 заносится адрес второго операнда (tv+1) -ой четверки операндов. В триннадцатом такте вы)абатывается сигнал на пятом выходе блока управления 1, по которому из счетчика 7 вычитается единица, чем адресуется третий операнд (п+1)-ой четверки операндов. В четырнадцатом такте на четвертом выходе блока управления 1 вырабатывается сигнал,, по которому в регистр 6 заносится третий

операнд (п+1)-ой четверки операндов.. В пятнгщцатом такте вырабатывается сигнал на пятом выходе блока управ;Г1ения 1, по которому из счетчика 7

5 вычитается единица, чем адресуется четвертый операнд четверки операндов. В шестнадцатсл такте вырабатывается сигнал на четвертом выходе блока управления 1, по которому

0 в регистр 6 заносится четвертый операнд (ц+1)-ой четверки операндов. Цикл повторяется снова и снова до тех пор, пока не будут обработаны все четверки операндов по всем

5 слоям, после чего устройство начинает вырабатывать адреса пар операндов специального слоя безизбыточного алгоритма БПФ. В зтом случае устройство функционирует ангшогичг

Q но устройству, описанному в прототипе . На временной диагрс1мме работы блока управления 1 (фиг.4) изображены два цикла восемь тактов.

После обнуления счетчиков устройс ство снова готово к работе.

. . Таким образом, предлагаемое устройство позволяет формировать адреса алгоритма БПФ с основанием выше двух (четыре, , шестнадцать 0 и т.д.), что расширяет его функциональные возможности.

Ifpasp fMbtM rifpfofOflfffe cwjnuttifa

ffSbtitefeM difutu fMfтора 4

/fti93pji/ Mft Stt3t«Atf« arff/n ffo /MHrmniffffW Cfffnutftim 7

, /fatfemet ft/xe y faofta ynftr jrfMM i

ftfff ytffayupff A W fnoffoM j

ofpfitfo i jfeifl

veto ctffhwfta

ujpffvempag

1-вгв()уига f fjrufefiai

ЧЗиг.}

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Блок формирования адресов для устройства, реализующего быстрое преобразование фурье | 1975 |

|

SU548863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1980 |

|

SU922763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-15—Публикация

1983-01-12—Подача