ливающего сумматора, второй вход (2N-M1) мультиплексора соединен с вхо дами второй группы блока синхронизации, выход первого сумматора соединен с информационным входом () . регистра, информационный вход которого подютючен к первому входу первого делителя, выход которого соединен с информационным входом (3N44) регистра, информациоршый выход которого соединен со вторым входом () умножителя, выход которогоподключен к информационному входу (3N45) регистра, информационшж выход которого оединен со вторым входом i-ro (, N) мультиплексора, выход вычитателя соединен с информационным вхо дом (ЗЫ+6) регистра, информационный выход которого соединен со вторым входом (i+3(N+l)/2+2) (, N) ум45ножителя, первый вход (N+2) умножителя объе/данен с первым входом вычитателя, второй вход которого является входом задания единицы фильтра, выход второго сумматора соединен с информационным входом (3N+7) регистра, информационный выход которого подключен к ((N+0/2 + 1) входу второго сумматора и информационному входу (3N+8) регистра, информационный выход которого соединен с вторым входом делителя и является информационным выходом фильтра, а выходы третьей группы блока синхронизации соответственно соединены с тактовыми входами (1 + N+1) регистра (, 2N+7), i-ro (i 1, N) накапливающего сумматора и управляющим входом i-ro (i 1, 2N+1) мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1780089A1 |

| Устройство для цифровой фильтрации | 1981 |

|

SU957416A1 |

| Адаптивный анализатор спектра | 1990 |

|

SU1837240A1 |

| Устройство для коррекции изображений объектов | 1989 |

|

SU1711206A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1483606A2 |

| Устройство для цифровой двумерной свертки | 1986 |

|

SU1363250A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| Цифровой фильтр | 1983 |

|

SU1146798A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

АДАПТИЗНЬЙ'ЦИФРОВОЙ ФИЛЬТР, . содержащий 3 (Nil)/242 умножителя, два сумматора, N+1 регистр, блок синхронизации, причем информационный выход i-ro (i=l. И) регистра подключен к информационного входу (i+1) регистра и первому входу i-ro умножителя, выход которого соединен с i-м входом первого сумматора, информационный выход (N+1) «регистра подключен к первому входу (Нч|) умножителя, выход которого соединен с (N*l) входом первого сумматора, первый -вход tN+^Я) умножителя является входом задания laara оптимизш;йи фильтра, _ выход i-ro (i=N-»-3, 3 (N+1)/2+2) умножителя подключен к i-ому входу второго сумматора, информационный вход 'первого регистра .является информационным входом Лильтра^ выходы первой группы блока синхронизации соответстаенно соединены с тактовыми входами Н+1 регистров, о т -л и ч а ю щ и 11 с я тем, что, с целью увеличения точности фильтрации и повютения быстродействия, в него введены Н-г^ножителей, 2*J+7 регистров, N накаплившрщих сумматоров, 2Н+1 мультиплексоров, вычита- тель и делитель, причем информационный выход i-ro (i=l, N ) регистра объединен с информационным входом (i+N+I) регистра, информационньй выход которого подключен к первому входу i-ro .мультиплексора, выход которого соединен со вторьгм входом i-ro умножителя, выход которого подключен к первому входу i-ro накапливающего сумматора, выход которого соединен с первым входом (i+3 (N+1)/2+2j умножителя, выход которогс соединен со вторым входом i-ro накапливающего сумматора, информационный вход (N-M) регистра о.бъеДинен с информационным входом (215+2.) регистра, информационный выход которого соединен со вторым входом (N+1T умножителя, инфориационный выход i-ro (i=;2k-l, k=l, (N-H)/2) регистра соединен с пepвы^f входом (k+?0 мультиплексора, выход которого подключен к первому Входу (k-(>&N*2) умножителя, второй вход которого. подключен к выходу (k-*-

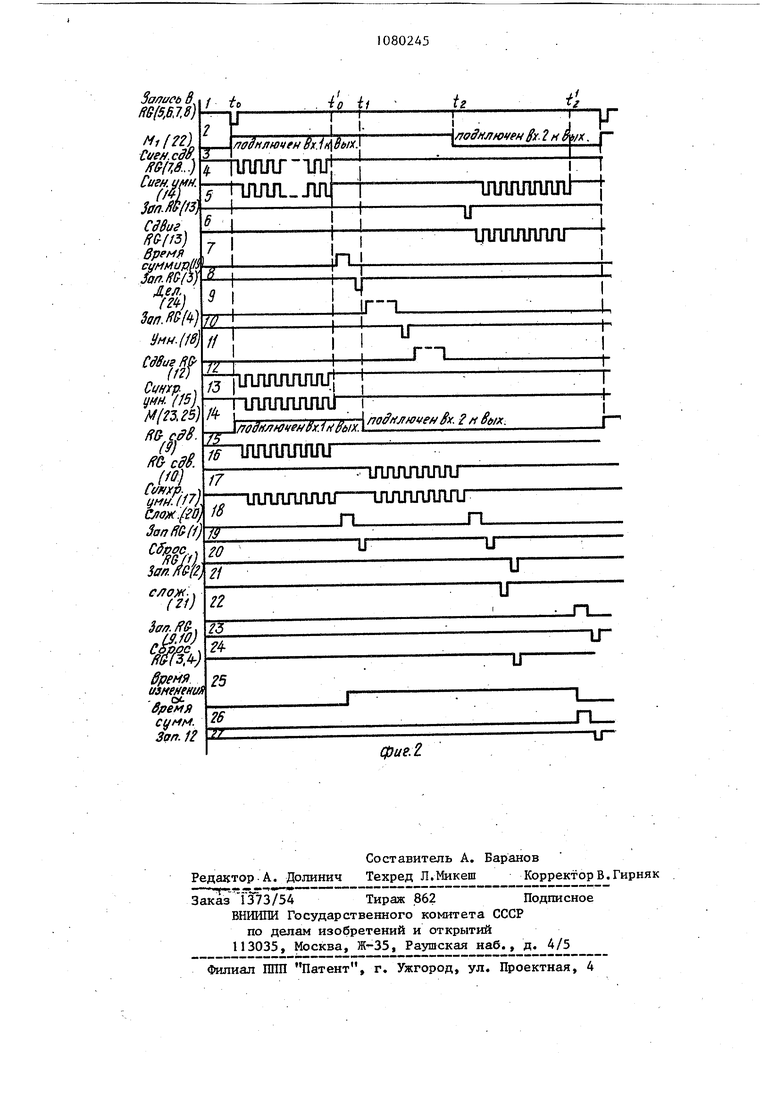

Изобретение относится к передаче дискретной информации и представляе собой специализированное вычислител ное устройство, предназначенное, для использования в системах с частотно телеграфией (ЧТ) или однократной фазовой телеграфией (ОФТ). Наиболее целесообразной областью применения являются системы связи, в которых параметры каналов меняются во времени. Известен адаптивный цифровой фильтр, процедура формирования коэффициентов в котором производится в зависимости от критерия достиже ния минимума среднеквадратичной ошибки. Этот критерий часто используется на практике из-за математического удобства и сравнительно про тон схемной реализации ij . Данный адаптивный фильтр состоит из каскадно включенных адаптивного линейного трансверсального фильтра и нелинейного рекурсивного фильтра, соде|ржащего линию задержки для регенерированных сигналов данных, регуляторов усиления цепи обратной связи и устройств адаптивного управ ления к ним. Этот фильтр может дать приемпсмые результаты только при высокой помехозащищенности принимаемого сигнала. Наиболее близким по технической сущности к изобретению является адаптивный нерекурсивный фильтр, содержащий N регистров, где N - порядок фильтра, (N+1) умножителей, выходы которых соединены со входами многовходового сумматора, выход которого является выходом фильтра и устройства формирования коэффициентов .(УФК), содержащее (N+2) умножителей и (N+-1) сумматор, причем на первые входы (N+1) умножителя подается-входной сигнал, а на вторые входы этих умножителей подается сигнал с выхода (N+2) умножителя УФК, на первый вход которого подается сигнал ошибки сформированный с помощью вычитающейсхемы и генератора опорного напряжения, формирующего эталонный сигнал, а на второй вход этого умножителя поступает сигнал, управляющий шагом оптимизации. Сигнал с выхода (N+1) умножителя УФХ подается на соответствую.щие (N+1) сумматор УФК, обеспечивающие сложение с сигналом, сформированным на предыдущем такте итера3ционного процесса. Сигналы с. иыходо /(N41) сумматоров являются значениям соответствующих коэффициентов фильт ра на данном такте . Эти сигналы поступают на первые входы (N41) умножителей фильтра, на вторые входа которых подается входной сигнал с. соответствующих регистров фильтра. Эти сигналы поступают на сумматор, .вьпсод которого является входом фил ра И. Недостатком данного фильтра является низкая точность фильтрации в условиях использования его в каналах с неизвестными параметрами шумов. Это связано с тем, что адаптивное изменение коэффициентов данного фильтра производится в соответствии с критерием оптимизации , обеспечивающим достижение минимума, среднеквадратичной ошибки . ЦеЛЬ изобретения - увеличение точности фильтрации и увеличение быстродействия фильтра. Для достижения поставленной цели в цифровой фильтр, содержащий 3(N+l)/242 умножителей, два сумматора, N+1 регистр, блок синхронизации, причем информационный выход i-го (, N) регистра подключен к информащшнному входу (i+1) регис ра и первому входу i-ro умножителя выход которого соединен с i-м входо первого сумматора, информационный в ход (N+l)-ro регистра подключен к первому входу (М+1) умножителя, выход которого соединен с (N.+ 1) входом первого сумматора, первый вход (N+2) умножителя, является входом задания гаага оптимизации фильтра, вькод -то (, 3(N+1)/2+2) умножителя подключен к i-му входу второго сумматора, информационный вход первого регистра является информационным входом филь ра, выходы первой группы блока синх ронизации соответственно соединены с тактовыми входами N+1 регистров, введены N умножителей, 2N+7 регист ров, N накапливающих сумматоров, 2N+1 мультиплексоров, вычитатель и делитель, причем информационный вход i-ro (, N) регистра объединен с информационным входом (i+N+1) регистра, информационный выход которого подключен к первому входу i-ro мультиплексора, выход которого соединен со вторым входом i-ro умно жителя, выход которого подключен 2454 к первому входу -го накапливающего сумматора, выход которого соединен с первым входом (i+3(N+l)/2+2) , умножителя, выход которого соединен со вторым входом 1-го накапливающего сумматора, информационный вход (N+1) регистра объединен с информационным входом (2N+2) (N+1) регистра, информационный выход которого соединен со вторым входом (Ы+О умножителя, информационный выход 1-го (i 2k-li , (KVl)/2) регистра соединен с первым входом (F:+N) мультиппексора, выход которого подключен к первому входу (k+N+2) умножителя, второй вход которого подключен к выходу (k4(3N4l)/2) мультиплексора, первый вход которого подключен к информационному выходу (k+2(N+l) регистра, информационный вход которого соединен с выходом i-ro накапливающего сумматора, второй, вход (i+(3N+l)/2) (1 Г7ч«+1)/2н) мультиплексора подключен к информационному выходу (21+2(N+1)) регистра, информационный вход которого подключен к выходу 2i-ro накапливающего сумматора, второй вход (2N+1) мультиплексора соединен с выходами второй группы блока синхронизации, выход первого сумматора соединен с информационным входом (3N+3) регистра, информационный выход которого подключен к первому входу первого делителя, выход которого сдединен с информационным входом (3N+4) регистра, информационный выход которого соединен со вторым входом (N+2) умножителя, выход которого подключен к информационному входу C3N+5) регистра, информационный выход которого соединен со вторым входом i-ro (, N) мультиплексора, выход вычитателя соединен с инфор1 ационным входом (3N+6) регистра, информационный выход кфторого соединен со вторым входом (i+3(N+l)/2+2) (, N) умножителя, первый вход () умножителя объединен с первым входом вычитателя, второй вход которого является входом задания единицы выход второго сумматора соединен с информационным входом (3N+7) реги-, стра, информационный выход которого подключен к ((N+l)/2+l) входу второго сумматора и информационному входу () регистра, информационный вы-... ход которого соединен со вторым входом делителя и является информационSHbiM выходом фильтра, a выхода1 треть группы блока синхронизации соответственно соединены с тактовыми входа ми (i+N+1) регистра (1 1, 2N+7) , 1-го ( , N) накапливающего сумматора и управляющим входом i-ro (iss 1,2N+1) мультиплексора. На фиг. 1 представлена структурн схема адаптивного цифрового фильтpa на фиг. 2 - временная диаграмма его работы. Фильтр содержит регистры 1-13, умножители 14-18, сумматоры 19, 20 накапливающие сумматоры 21 , однораз рядные (двуквходовые) мультиплексоры 22, 23, делитель 24, многоразряд Hbie (двухвходовые) мультиплексоры 25, вычитатель 26, блок синхронизации 27, информационный вход 28, информационньп выход 29, вход задания шага оптимизации 30. Фильтр работает следующим образрм. Отсчеты входного сигнала Z поступают на вход фильтра 28 и параллельно записываются в регистры 5 и предыдущие отсчеты (Z,., ,,. ... 2„) переписываются из регистро 5 в 6 и т.д. Эти отсчеты, записанные в регистрах 5 ,- 6 умножаюггся на значения коэффициентов (с), хранящихся в регистрах 9, 10 и 11 . Эти умножения выполняются в умножителях 17. Следующая операция - это суммирование всех полученных произведений в сумматоре 20. Интервал времени между записью очередных входных отсчетов в регист 5 (tg-t) назовем оснчвным циклом. Остановимся более,подробно на работе блоков устройства, обеспечивающих достижение .цели изобр етрния - повьщ1ение точности фильтрацйи Очередное (новое для каждого цикла на этапе настройки фильтра) значение коэффициента вычисляется с помощью умножителей 14 и 18, сумматоров 19, 21, вычитателя 26, делителя 24. Регистры 3, 4 обеспечивают функционирование делителя 24 и умножителя 18. Регистр 7, 8, 12, 13 необходимы для функционирования умножителей 14, 15. Вычисление очередного коэффициента может быть опи сано атедующим выражением . N (О il С -Z (4 Г f л/ 0 С )С .Е2.„,,-г„. 45 Для одновременного повьпцения загрузки умножителей адаптивного цифрового фильтра, приводящего в результате к уменьшению аппаратурных затрат при реализации устройства, используются дополнительные сумматоры 21, 19, умножители 14, 15, 16, 18, делитель 24, выполняющих описанную в формуле (I) процедуру формирования коэффициентов. Следует отметить, что повьпление загрузки умножителей устройства происходит без снижения быстродействия за счет совмещения операций в умножителях 14 и операций в умножителях 14 и операдни в умножителях 17. Для решения этой задачи используются дополнительные мультиплексоры 22, 23 и 25 коммутирующие на входе умножителей 14 и 17 различные операнды в разные моменты времени (см. графики 2 на фиг. 2) (, ,) и (t:,-t, 2 2 3 о 2 -2 -} (5 1 t.-t,). Рассмотрим подробнее формирование очередного значения коэффициента В момент tjj (см.чфиг. 2) происходит запись отсчета Z входного сигнала в регистры 5 и 7 (график 1). Предьздущее значение 2п. из регистра 5. переписывается в регистр 6. К этому моменту времени (t) регистры схемы устройства находятся в следующих состояниях:в выходном регистре накапливающего сумматора 21 - значение коэффициента С ., в регистре 9 - значение коэффициента CJ ; в регистрах 5, 7 - значение отсчетовв регистрах 6,8- значения отсчё 03 2„,,; в регистре 12 - значение величины (1-сс); в регистре - обнулен (график 20 фиг. 2); в регистре 2 - значение выходного отсчета i}n . Одноразрядный мультиплексор 22 (график 2 фиг. 2) находится в,том состоянии, когда первый его вход подключен к выходу. Таким образом на первом входе умножителя 14 присутствует в параллельном коде значение Z. При подаче синхросигналов сдвига 3 на регистр 7 на второй вход умножителя 14 поступают разряды того же сигнала Z. Параллельно7последовательн.1й умножитель по ссют ветствуюпщм синхросигналам (4) выполняет умножение Z Z. К моменту t В ВЫХОДНОМ регистре умножителя и аналогичных умножителях вплоть до (N41) оказываются соответствующи результаты (Zfl.;, Z, ) и т .д., котор jiyMMHpyraTCH, график (7), в сумматор 19 и aanHCbiBaeT cH 8 в регистр 3. В зто жёвремя (tp-tp) с участием выходного регистра накапливающего сумматора 21 (параллельный операнд) и регистра 12 (последовательный one ранд) выполняется умножение в умножителе 15 (диаграммы 12, 13 фиг. 2) Однако суммирование в сумматоре 21 не выполняется и результат этой one рации хранится в выходном регистре умножителя 15. В течение времени () выполняется деление в делителе 24 и умножение в умножителе 18 с записью результата в регистр 13. Временная последовательность этих операций представлены на графиках (9 10, 11, 5). В момент t пере1спючаетсямультиплексор 22 (график 2), подключается его второй вход к выходу, т.е. умножитель 14, начиная со времени t/J до t/), выполняет операцию, умножая Z (параллёльньш код) из реги L, Iff, стра р на величину ,6i . . . .п- п-л (последовательный код) из регистру 12. Временные диаграммы соответствующих сигналов изображены на гра фиках 2, 4 и 6. Таким образом к моменту tl в выходном регистре умножителя 14 и выходном регистре умножителя 15 находятся операнды, ког торые после сложения в сумматоре -. 1 (график 22) дают новое значение коэффициента, которое записывается (график 23) в регистр 9 и используется в следзпощем цикле для вычиспегщя нового значения выходного сиг нала ; Рассмотрим подробнее процедуру вычисления выходного отсчета.фильтра. Она заключается в умножении текущих отсчетов из регистров 5, 6 на вычисленные в предыдущем цикле коэффициенты из регистров 9, 10 и 1 Умножение выполняется параллельнопоследовательным способом в умножителе 17. Параллельные отсчеты посту пают из регистров 5, 6..., последовательные из регистров 9, 10 и 11. С целью повышения загрузки умножи5телей возможность для этого создается за счет того, что . цоэфф Чыч. вых оТсцёта используются fyльтиплексоры 25 и 23, которые позволяют первую часть времени общего цикла (trt ) ВЫПОЛНЯТЬ умножение для нечетных ветвей схемы, а вторую часть времени (t-t) выполнять умножение для четных ветвей схемы, «функционирование мультиплексоров 23, 25 и умножителей 17 поясняют диаграммы 14-17, Суммирова.ние с накапливанием результата от нечетных и четных ветвей выполняется сумматором 20 и регистром 1, диаграммы 18, 19. Каждый новый цикл требуетобнуления регистра 1 (20) с предварительной переписью результата в выходной регистр 2(21). Общее управление схемой осуществляется подачей сигналов (см. фиг. 2) записи, сдвига; синхронизации и управления дпя. регистров, умножителей, регистров накапливающих сумматоров и мультиплексоров, формируемых общим блоком синхронизации 27, который содержит ПЗУ 31, адресующий ПЗУ суммирзтощий двоичный счетчик 32, работающий от сигналов задающего генератора, выходной регистр 33, выход генератора 34 подключен ко входу счетчика 32, выходы счетчика 32 - к адресным входм ПЗУ 31, выходы ПЗУ 31 - к входам регистра 33 (фиг. В ПЗУ непосредственно записаны сигналы управления мультиплексодами, сигналы синхронизации регистров, сброса и записи в регистры и т.д. для каждого такта работы. схемы (tj,-t) фиг. 2. Кроме того, в ПЗУ записан, последовательный двоичный код 1, подаваемый на последний мультиплексор. .Количество слов хранимых в.ПЗУ, равно количеству элементарных тактов на интервале (tQ-t-j) (фиг, 2), а разрядность каждого слова равна общему количеству управляющих сигналов. Стробируемый выходной регистр блока 27 обеспечивает сопряжение выходов ПЗУ со входами управляемых блоков устройства. Следует отметить некоторые существенные особенности схемы. Ветвь с номером (N+1) отличается от всех прочих и состоит только из умножителя. Это обеспечивает ненулевые начальные условия в схеме во

время вхождения устройства в режим адаптации даже при нулевых начальных значениях коэффициентов. Кроме того, отсутствие умножителя (типа 15) сумматора типа 11, регистра типа 9 в ветви (N+1) требует подключения второго входа последнего одноразрядного мультиплексора (типа 23, с номером {N4-1)/2) к выходу блока 27. Для обеспечения правильной работы в течение времени () (когда идет второе умножение в умножителе 7 на упомянутый вход мультиплексора из блока 27 подается последовательный код, соответствующий значению числа 1.

Кроме того, значение коэффициента oi можно менять на входе управления шагом оптимизации только в течение времени () (график 25). В кон80245Ш

. це цикла () выполняется вычитание (вычитание величины ( и запись результата в регистр 12 (гра фики 26, 27). Параллельный код единицы постоянно подается из устройства управления.

В момент tg возможно поступление нового отсчета на вход 28 и пост-i Зроение всего цикла вычислений. При 10 этом результат - значение выходного отсчета с предыдущего цикла присутствует на выходе 29 почти в течение всего цик/ia вычислений (см, график 21).

Адаптивный ифровой фильтр обеспечивает повышение точности фильтрации при высокой скорости сходимости алгоритма « одновременном увеличении быстродействия.

Авторы

Даты

1984-03-15—Публикация

1982-11-10—Подача