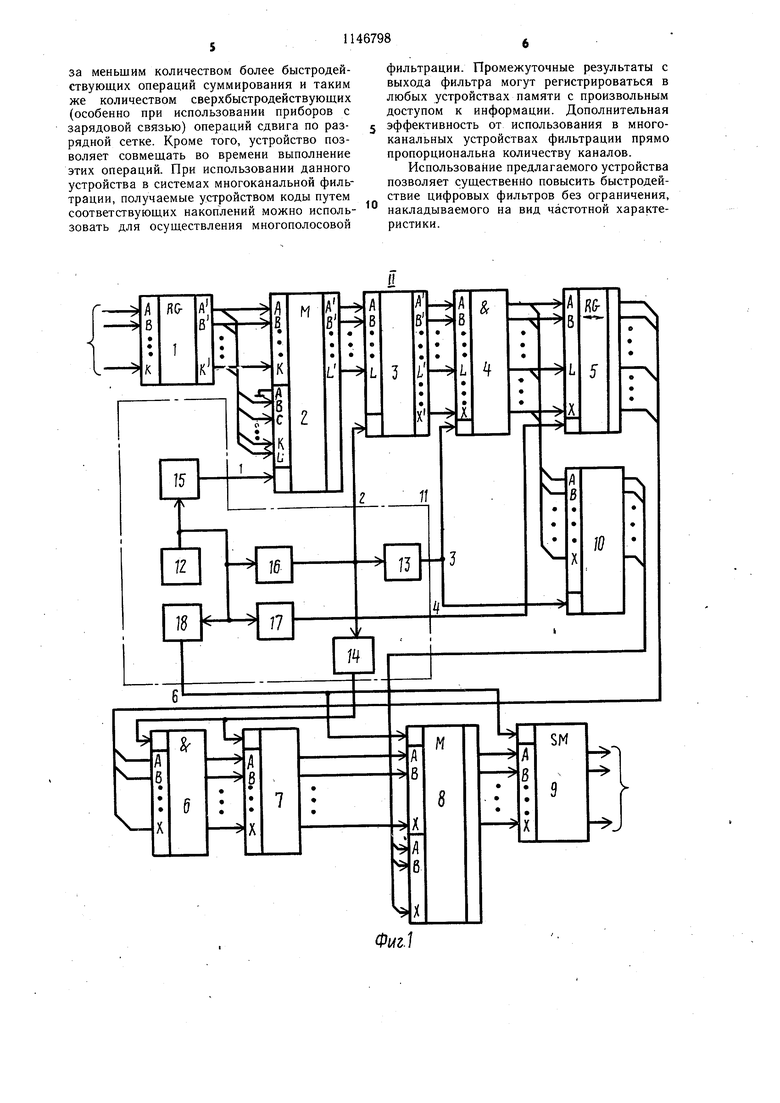

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки информации. Известен цифровой фильтр, содержащийнакапливающий сумматор, ВЬЕХОД которого является выходом цифрового фильтра, последовательно соединенные и подключенные к входу цифрового фильтра первые регистры сдвига, между выходами которых и первыми входами накапливающего сумматора включены первые блоки памяти, последовательно соединенные и подключенные к выходу накапливающего сумматора, вторые регистры сдвига, между выходами которых и вторыми входами накапливающего сумматора включены вторые блоки памяти 1. Недостатком этого цифрового фильтра Является большой требуемый объем памяти каждого блока памяти. Наиболее близким по технической сущности к предлагаемому является цифровой фильтр, содержащий последовательно соединенные формирователь импульсов, адресньш счетчик, первый блок памяти, второй регистр сдвига, умножитель, первый накапливающий сумматор, выход которого является выходом цифрового фильтра, последовательно соединенные второй блок памяти, комбинационный сумматор, третий блок памяти, первый регистр сдвига, мультиплексор и второй накапливающий сумматор, вход управления которого подключен к выходу формирователя импульсов, а выход соединен с другим входом умножителя, а также дещифратор, вход которого подключен к первому выходу второго блока памяти, а выход соединен с входами управления третьего блока памяти и мультиплексора, вторые информационные входы которых Ъбъединены и являются входом цифрового фильтра, блок синхронизации, первый выход которого через первый адресный счетчик подключен к второму информационному входу комбинационного сумматора, второй выход блока синхронизации через второй адресный счетчик соединен с входом второго блока памяти, второй выход которого подключен к входу формирователя импульсов 2. Однако известный цифровой фильтр обладает недостаточно высоким быстродействием. Цель изобретения - повыщение быстродействия цифрового, фильтра. Цель достигается тем, что в цифровой фильтр, содержащий первый накапливающий сумматор, первый блок памяти, блок, синхронизации и последовательно соединенные первый регистра сдвига, первый мультиплексор и второй накапливающий сумматор, введены последовательно соединенные и включенные между выходами второго и входами первого накапливающих сумматоров первый блок элементов И, второй регистр сдвига, второй блок элементов И, второй блок памяти и второй мультиплексор, вторые информационные . входы которого подключены к выходам первого блока памяти,-вторые информационные входы первого мультиплексора объединены с его первыми информационными входами, причем информационный вход, соответствующий i-му (i 1, 2,..., п) разряду первых информационных входов, соединен с информационным входом, соответствующим (i + 1)-му разряду вторых информационных входов, первый -информационный вход которого, соответствующий младщему разряду, соединен с общей щиной, информационные входы первого блока памяти соединены с выходами первого блока элементов И, с первого по шестой выходы блока синхронизации подключены к входу управления первого мультиплексора, к входу управления второго накапливающего сумматора, к объединенным входам управления первого блока элементов И и первого блока памяти, к входу управлени я второго регистра сдвига, к объединенным входам управления второго блока элементов И и второго блока памяти и к входу управления второго мультиплексора соответственно, при этом входы первого регистра сдвига являются входами, а В1|1ходы первого накапливающего сумматора - выходами цифрового фильтра. Блок синхронизации содержит генератор импульсов, первый и второй таймеры, первый, второй, третий и четвертый делители частоты, входы которых соединены с выходом генератора импульсов, выход первого делителя частоты является первым выходом блока синхронизации, выход второго делителя частоты подключен к входам первого и второго таймеров и является вторым выходом -блока синхронизации, а выходы первого таймера, третьего делителя частоты, второго таймера и четвертого делителя частоты являются третьим, четвертым, пятым и щестым выходами блока синхронизации соответственно. На фиг. 1 приведена структурная электрическая схема цифрового фильтра; на фиг. 2 - диаграмма, поясняющая его работу. Цифровой фильтр содержит первый регистр 1 сдвига, первый мультиплексор 2, второй накапливающий сумматор 3, первый блок 4 элементов И, второй регистр 5 сдвига, второй блок 6 элементов И, второй блок 7 памяти, второй мультиплексор 8, первый накапливающий сумматор 9, первый блок 10 памяти, блок 11 синхронизации, который состоит из генератора 12 импульсов, первого и второго таймеров 13 и 14, первого, второго, третьего и четвертого делителей 15-18 частоты. Цифровой фильтр работает следующим образом. Текущая входная выборка сигнала в виде цифрового параллельного кода поступает на вхоД регистра 1 сдвига, где она запоминается до прихода следующей выборки. За время at дискретизации входного фильтрируемого процесса в цифровом фильтре осуществляется формирование произведений входной выборки на все возможные значения коэффициентов. В общем случае значения коэффициентов можно представить в виде ряда натуральных чисел от О до Q, где Q 2 , а q - разрядность кода представления коэффициентов. Произведения формируются косвенно, т.е. не непосредственно путем умножения кода входной выборки на коды коэффициентов.

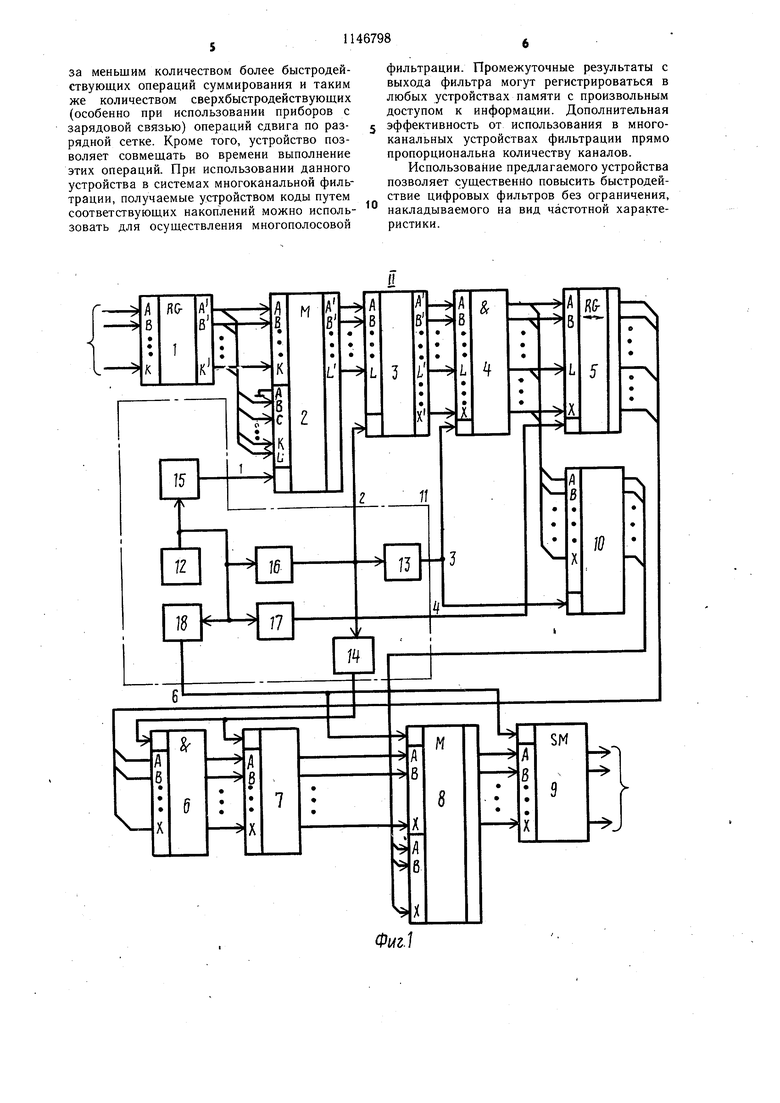

Произведения кода входной выборки на нечетные коэффициенты формируются во втором Накапливающем сумматоре 3 путем потактного прибавления к коду выборки удвоенного значения кода, поступающего во второй накапливающий сумматор 3 через второй информационный вход первого мультиплексора 2. В результате во втором накапливающем сумматоре 3 образуются коды: после поступления кода входной выборки - код соответствующий парному произведению входной выборки на коэффициент 1, после суммирования данного кода с удвоенным значением кода входной выборки - код соответствующий парному произведению входной выборки на коэффициент 3 и т.д. Таким образом, половина парных произведений получается путём выполнения такого же количества более простых и более .быстродействующих операций суммирования во втором накапливающем сумматоре 3. Коды парных произведений по мере их формирования поступают с выхода второго накапливающего сумматора 3 через первый блок 4 элементов И в первый блок 10 памяти для запоминания произведений кода входной выборки на нечетные коэффициенты и на информационный вход второго регистра 5 сдвига. Код, поступивший на параллельный информационный вход второго регистра 5 сдвига потактно сдвигается по разрядной сетке, т.е. с каждым тактом осуществляется сдвиг кода, который можно интерпретировать, -как выполнение операции умножения на число 2, где j - число тактов сдвига. На фиг. 2 представлена последовательность формирования парных произведений входной выборки Xi на коэффициент фильтрации. Вторая половина парных произведений получается путем выполнения операций сдвига кодов по разрядной сетке второго регистра 5 сдвига. При этом операции, выполняемые на втором накапливающем сумматоре 3 и во втором регистре 5. сдвига, могут выполняться одновременно. С выхода второго регистра 5 сдвига код чисел, соответствующих парным, произведени ям кода выборки на четные коэффициенты, записывается через второй блок 6 элементов И во второй блок 7 памяти. В первом

и втором блоках 10 и 7 памяти -накаплива.ются парные произведения входных выборок на коэффициенты фильтрации. При помощи блока 11 синхронизации осуществляется считывание парных произведений из первого и второго блоков 10 и 7 памяти через второй мультиплексор 8 в первый накапливающий сумматор 9, в котором осуществляется суммирование парных произведений для получения очередного отсчета свертки. Для повторной фильтрации одной и той же реализации входного сигнала не требуется выполнение дополнительных операций умножения, необходимо лищь изменить при помощи первого и второго таймеров 13 и 14 режимы управления первым и вторым блокамй 10 и 7 памяти.

Первый и второй таймеры 13 и 14 осуществляют также согласование во времени процедур вычисления (формирования) парных произведений и перезаписи парных произведений из второго накапливающего сумматора 3 во второй регистр сдвига 5.

В известном фильтре повыщение быстродействия достигается лищь за счет того, что устраняется избыточность при повторных умножениях одного значении выборки (числа) на одинаковые значению коэффициенты, то в предлагаемом устройстве повыщение быстродействия достигается и за счет устранения избыточности при выполнении операции умножения - произведение, полученное в предыдущем такте, используется как исходное число для формирования произведения в настоящем такте. Кроме того, предусматривается возможность одновременного формирования двух произведений (произведения на нечетный и четный коэффициенты).

На формирование N произведений входного отсчета на массив коэффициентов требуется

NtyM 0,5Nt5,-f 0,5NtcR, где iytt - время, требуемое на выполнение операции умножения;

ts -время, требуемое на выполнение

операции суммирования; tcfl.- время, требуемое на выполнение

операции сдвига

при последовательном формировании произведений, а при параллельном

NtvH - 0,5N (ty,,, или в среднем на одну операцию умножения

ty 0,5(t +tejt) И

tyM 0,5 max {ty,,, tcgjl

соответственно.

Практически, как показали испытания, среднее время на выполнение операции умножения определяется

0,5 (tg+ tce),5max{t,t

Таким образом, по сравнению с известным фильтром операции умножения (как наиболее трудоемкие) заменяются в два раза меньшим количеством более быстродействующих операций суммирования и таким же количеством сверхбыстродействующих (особенно при использовании приборов с зарядовой связью) операций сдвига по разрядной сетке. Кроме того, устройство позволяет совмещать во времени выполнение этих операций. При использовании данного устройства в системах многоканальной фильтрации, получаемые устройством коды путем соответствующих накоплений можно использовать для осуществления многополосовой

фильтрации. Промежуточные результаты с выхода фильтра могут регистрироваться в любых устройствах памяти с произвольным доступом к информации. Дополнительная эффективность от использования в многоканальных устройствах фильтрации прямо пропорциональна количеству каналов.

Использование предлагаемого устройства позволяет существенно повысить быстродействие цифровых фильтров без ограничения, накладываемого на вид частотной характеристики.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Цифровой фильтр | 1985 |

|

SU1302296A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Адаптивный цифровой фильтр | 1982 |

|

SU1080245A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Цифровой фильтр | 1985 |

|

SU1327281A1 |

1. ЦИФРОВОЙ ФИЛЬТР, содержащий первый накапливающий сумматор, первый блок памяти, блок синхронизации и последовательно соединенные первый регистр сдвига, первый мультиплексор и второй накапливающий сумматор, отличающийся тем, что, с целью увеличения быстродействия, в него введены последовательно соединенные и включенные между выходами второго и входами первого накапливающих сумматоров первый блок элементов И, второй регистр сдвига, второй блок элементов И, второй блок памяти и второй мультиплексор, вторые информационные входы которого подключены к выходам первого блока памяти, вторые информационные входы первого мультиплексора объединены с его п рвыми информационными входами, причем информационный вход, соответствующий i-му (i 1,2, ...,п) разряду первых информационных входов, соединен с информационным вхо дом, соответствующим (i-Ь 1)-му разряду вторых информационных входов, первый информационный вход которого, соответствующий младшему разряду, соединен с общей щиной, информационные входы первого блока памяти соединены с выходами первого блока элементов И, с первого по шестой выходы блока синхронизации подключены к входу управления первого мультиплексора, к входу управления второго накапливающего сумматора, к объединенным входам управления первого блока элементов И и первого блока памяти, к входу управления второго регистра сдвига, к объединенным входам управления второго блока элементов И и второго блока памяти и к входу управления второго мультиплексора соответственно, при этом входь первого регистра сдвига являются входами, а выходы перkn вого накапливающего сумматора - выходами цифрового фильтра. 2. Фильтр по п. 1, отличающийся тем, что блок синхронизации содержит генератор импульсов, первый и второй таймеры, первый, второй, третий и четвертый делители частоты, входы которых соединены с выхо- , дом генератора импульсов, выхрй первого делителя частоты является первьш выходом блока синхронизации, выход .второго делиО5 теля частоты подключен к входам первого и второго таймеров и является вторым выхо ;о дом блока синхронизации, а выходы перво00 го , третьего делителя частоты, второго таймера и четвертого делителя частоты являются третьим, четвертым, пятым и щестым выходами блока синхронизации соответственно.

l.

bi

hi

Ihi

I

f

5Xi ... (K-;;Xt .

гЧх..- zfe-i xt..

2-5Щ.. Z4lK-i))(L..

/5xt...2(.-.

.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Антонью А | |||

| Цифровые фильтры | |||

| М., «Радио и связь, 1983, с | |||

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПОДАЧИ УГЛЯ К ТОПКАМ | 1920 |

|

SU297A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-23—Публикация

1983-09-27—Подача