Изобрвте1ше относится к втлчисли- ;тельной технике и технике связи и ко- ет быть использовано длк передачи речевь5х сообщений.

Цель изобретения - повышение точ- :ности преобразования за счет сниже- 1ния уровня шумов квантования„

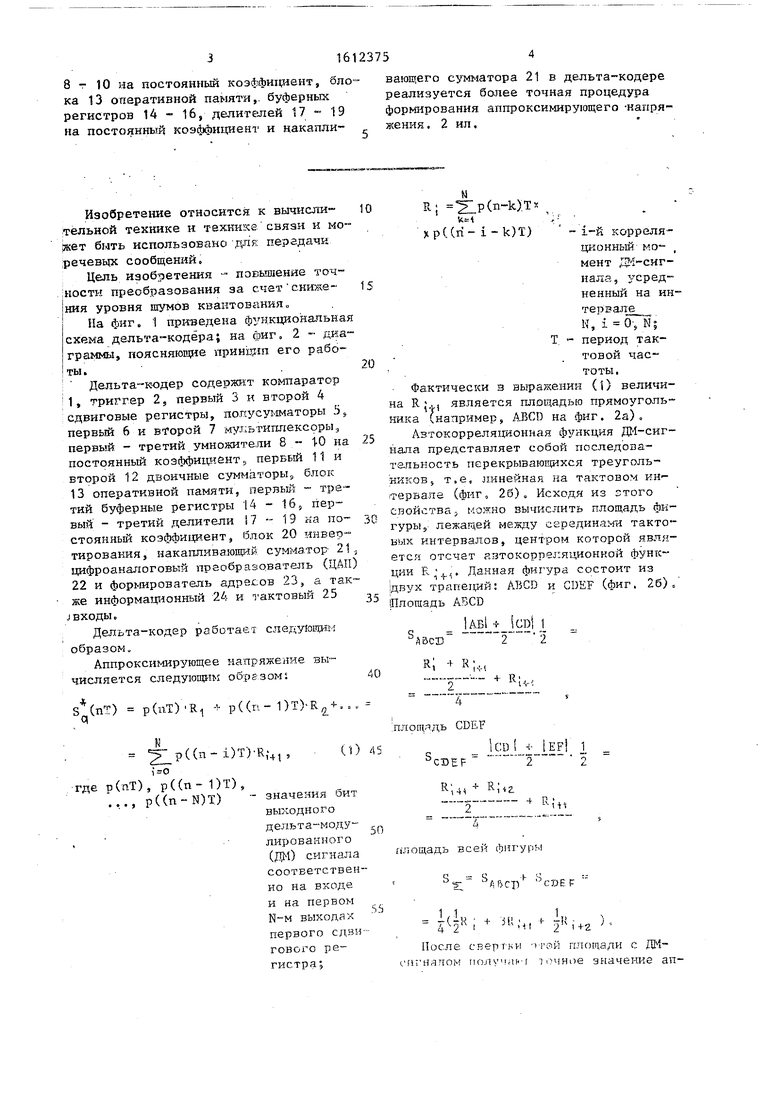

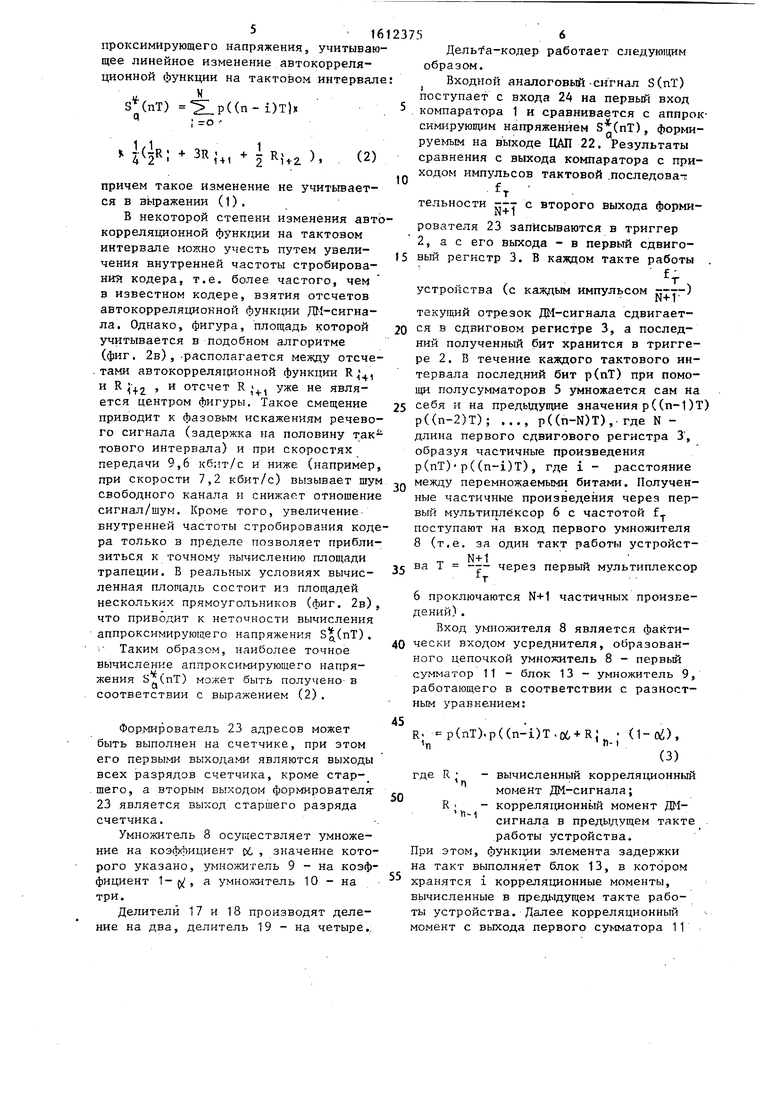

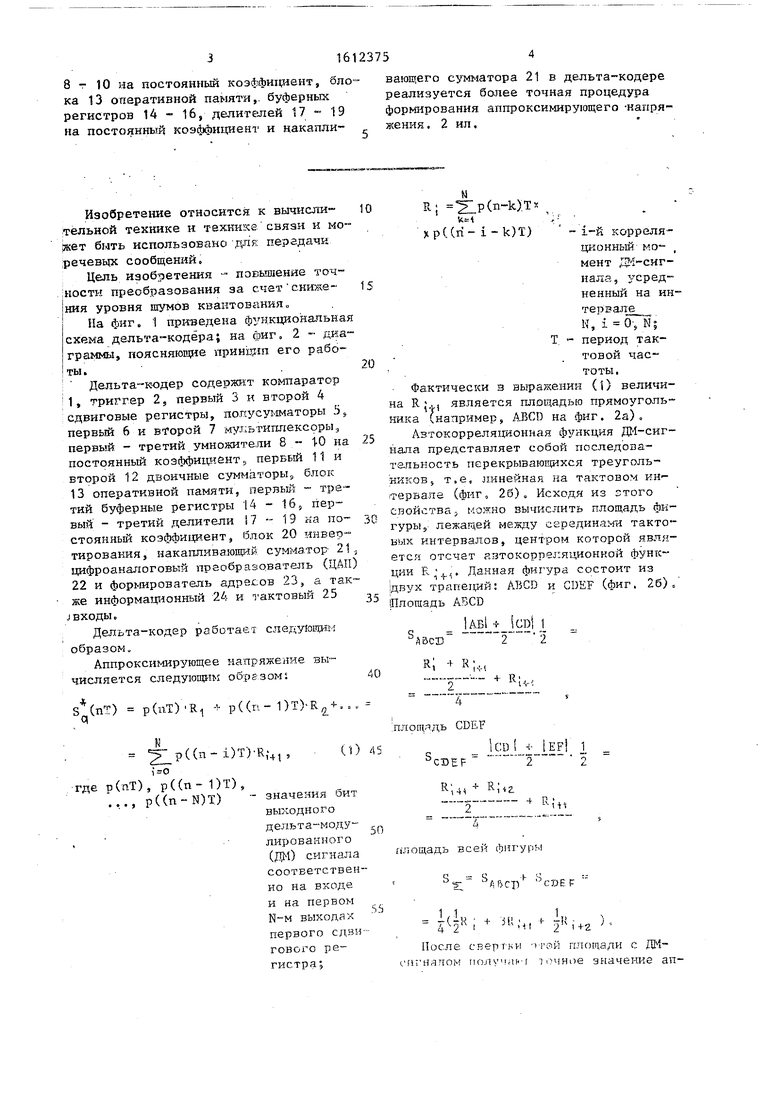

На фиг. 1 приведена функциональная схема дельта-кодера; на фиг, 2 - диаграммы, поясняющие принщш его работы.

Дельта-кодер содержит компаратор 1, триггер 2, первый 3 и второй 4 сдвиговые регистры, полусу1-1маторы Ь первый 6 к второй 7 мультиппексоры, первый - третий умножители 8 - 1-0 на постоянный коэффшщент,, первый 11 и второй 12 двоичные сумматоры, блок 13 оперативной памяти, первый - третий буферные регистры 14 - 16, первый - третий делители Г7 - 19 ка по- стоянный коэффи1 рент, блок 20 инвертирования , накапливающий сумматор 21 цифроаналоговый преобразователь (ДАН 22 и формирователь адресов 23, а также информационный 24 и тактовый 25 Jвходы.

Дельта-кодер работает следующим

образом.

Аппроксимирующее напряжение вычисляется следующим обрезом:

S(nT) p(iiT) Ri -5- р((п- 1)T) R2/

К

p((n-i)T) R,-4,,

(1) 45

РЧ i:p(n-k):Tx .

,,

XpC(ri-i-k)T) i-й корреляционный. МО- , мент Д 1-сиг- нала, усредненный на ин- тервал1е K, i 0-, N; Т. - период тактовой частоты.

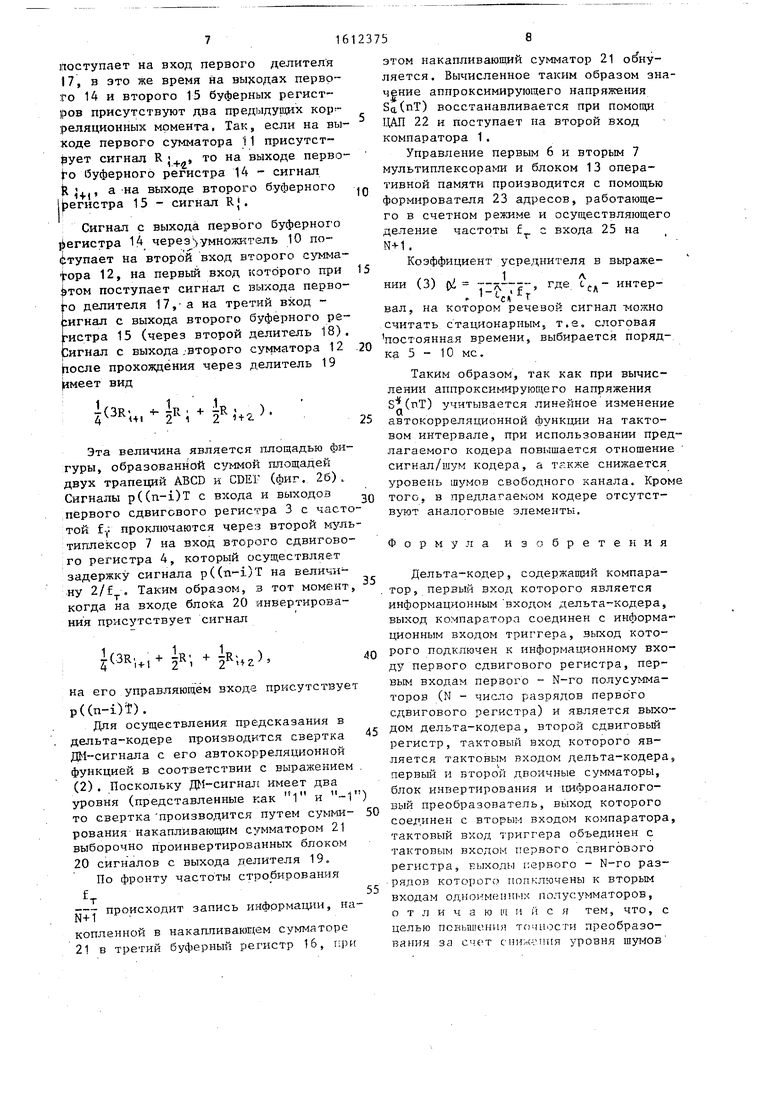

Фактически з выражении (1) величина R ,, является площадью прямоугольника (например, ABCD на фиг. 2а),

Автокорреляционная функция Д1-1-сиг- нала представляет собой последовательность псрекрываюшд хся треугольников, т.е. линейная на тактовом ин- тервале (фиг, 26). Исходя из этого свойства 5 можно вычислить площадь фигуры,: лежащей между еерадина: га такто- B«jix интервалов, центром которой является отсчет азтокорре1:яционной функции В. ;.,. Данная фигура состоит из |двух т рапеций: ABCD и GDEF (фиг. 26). Илощадь ABCD

UB 1 Аасв 2 2

R; - к;.и.

.

/Г

9

ллощя.дь CDEF

ICD IEF 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство конференц-связи с дельта-модуляцией | 1989 |

|

SU1660202A1 |

| Дельта-модулятор | 1987 |

|

SU1444953A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Адаптивный телевизионный дельта-кодер | 1989 |

|

SU1690199A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Адаптивный дельта-кодер | 1988 |

|

SU1658384A1 |

| Дельта-модулятор | 1988 |

|

SU1658383A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование для передачи речевых сообщений позволяет повысить точность преобразования за счет снижения уровня шумов квантования. Дельта-кодер содержит компаратор 1, триггер 2, сдвиговые регистры 3, 4, полусуматоры 5.1 - 5.N, двоичные сумматоры 11, 12, блок 20 инвертирования и цифроаналоговый преобразователь 22. Благодаря введению полусумматора 5. (N + 1), мультиплексоров 6, 7, умножителей 8 - 10 на постоянный коэффициент, блока 13 оперативной памяти, буферных регистров 14 - 16, делителей 17 - 19 на постоянный коэффициент и накапливающего сумматора 21 в дельта-кодере реализуется более точная процедура формирования аппроксимирующего напряжения. 2 ил.

1 v

де р(пТ), р((п- 1)Т), ,..., p((n-N)T)

значения бит выходного дельта-моду лированного (Д1Ч) сигнала соответственно на входе и на первом N-M выходах первого сдвигового регистра;

RU - „......„4 R;,

площадь всей фигуры

т Alicp crjEF

55

Ч

11 и. 1,+2

После CBepTKV чтэй площади с ДМ- с 8гналом ПОЛУ ,- точноб эначенив аи 1612375

проксимирующего напряжения, учитывающее линейное изменение автокорреляционной еЬункции на тактовом интервале: V

p((n-i)T)x

; о

S(nT) q

+ 3R

1-И

+ I Rl42

),

причем такое изменение не учитьгаает- ся в выражении (1),

В некоторой степени изменения автокорреляционной функции на тактовом интервале можно учесть путем увеличения внутренней частоты стробирова- ния кодера, т.е. более частого, чем в известном кодере, взятия отсчетов автокорреляционной функгщи ДМ-сигна- ла. Однако, фигура, площадь которой учитывается в подобном алгоритме (фиг, 2в), -располагается между отсче- . тами автокоррелящюнной функции , и R . и отсчет R уже не является центром фигуры. Такое смещение приводит к фазовым искажениям речевого сигнала (задержка на половину так тового интервала) и при скоростях передачи 9,6 кбит/с и ниже (например.

10

Входной аналоговый-сигнал 8(пТ) поступает с входа 24 на первый вход компаратора 1 и сравнивается с аппрок симирующим напряжением S(nT), формируемым на выходе ЦАП 22. Результаты сравнения с выхода компаратора с приходом импульсов тактовой последоваfr

тельности --- с второго выхода формирователя 23 записываются в триггер 2, а с его выхода - в первый сдвиго- 15 вый регистр 3. В каждом такте работы

fr устройства (с каждым импульсом гттт)

текущий отрезок ДМ-сигнала сдвигает- 20 ся в сдвиговом регистре 3, а последний полученный бит хранится в триггере 2. В течение каждого тактового интервала последний бит р(пТ) при помощи полусумматоров 5 умножается сам на 25 себя и на предыдущие значения р((п-1)Т р((п-2)Т); ..., р((п-Ы)Т),-где N - длина первого сдвигового регистра 3, образуя частичные произведения

р(пТ) p((n-i)T), где i - расстояние при скорости 7,2 кбит/с) вызывает шум между перемножаемыми битами. Получен- свободного канала и снижает отношение ные частичные произведения через пер- сигнал/шум. Кроме того, увеличение- внутренней частоты стробирования кодера только в пределе позволяет приблизиться к точному вычислению площади трапеции. В реальных условиях вычисленная площадь состоит из нескольких прямоугольников (фиг. 2в)J что приводит к неточности вычисления аппроксимирующего напряжения 5(пТ).

вый мультиплексор 6 с частотой f. поступают на вход первого умножите-ля 8 (т.е, за один такт работы устройст35

ва

N+1

через первый мультиплексор

Таким образом, наиболее точное вычисление аппроксимирующего напряжения Sjj(nT) может быть получено- в соответствии с выражением (2),

Фор.мирователь 23 адресов может быть выполнен на счетчике, при этом его первыми выходами являются выходы всех разрядов счетчика, кроме стар- ,шего, а вторым выходом формирователя- 23 является выход старшего разряда счетчика.

Умножитель 8 осуществляет умножение на коэффициент , значение которого указано, умножитель 9 - на коэффициент 1-(), а умножитель 10 - на три.

Делители 17 и 18 производят деление на два, делитель 19 - на четыре..

6 проключаются N+1 частичных произведений) .

Вход умножителя 8 является факти- 40 чески входом усреднителя, образованного цепочкой умножитель 8 - первый сумматор 11 - блок 13 - умножитель 9, работающего в соответствии с разностным уравнением:

45

л

П-1

R. -p(nT).p((n-i)T.o6 + R, ; (1-oi),

(3)

где R50

R

ИМ

55

вычисленный кoppeляlц oнный момент ДМ-сигнала; корреля1Ц1оннь1й момент ДМ- сигнала в предыдущем такте работы устройства.

При этом, функдаи элемента задержки на такт выполняет блок 13, в котором хранятся i корреляционные моменты, вычисленные в предыдущем такте работы устройства. Далее корреляционный момент с выхода первого сумматора 11

:

10

Дeльfa-кoдep работает следу101цим образом.

Входной аналоговый-сигнал 8(пТ) поступает с входа 24 на первый вход компаратора 1 и сравнивается с аппроксимирующим напряжением S(nT), формируемым на выходе ЦАП 22. Результаты сравнения с выхода компаратора с приходом импульсов тактовой последоваfr

тельности --- с второго выхода формирователя 23 записываются в триггер 2, а с его выхода - в первый сдвиго- 15 вый регистр 3. В каждом такте работы

fr устройства (с каждым импульсом гттт)

текущий отрезок ДМ-сигнала сдвигает- 20 ся в сдвиговом регистре 3, а последний полученный бит хранится в триггере 2. В течение каждого тактового интервала последний бит р(пТ) при помощи полусумматоров 5 умножается сам на 25 себя и на предыдущие значения р((п-1)Т) р((п-2)Т); ..., р((п-Ы)Т),-где N - длина первого сдвигового регистра 3, образуя частичные произведения

р(пТ) p((n-i)T), где i - расстояние между перемножаемыми битами. Получен- ные частичные произведения через пер-

вый мультиплексор 6 с частотой f. поступают на вход первого умножите-ля 8 (т.е, за один такт работы устройстр(пТ) p((n-i)T), где i - расстояние между перемножаемыми битами. Получен- ные частичные произведения через пер-

35

ва

N+1

через первый мультиплексор

р(пТ) p((n-i)T), где i - расстояние между перемножаемыми битами. Получен- ные частичные произведения через пер-

6 проключаются N+1 частичных произведений) .

Вход умножителя 8 является факти- 40 чески входом усреднителя, образованного цепочкой умножитель 8 - первый сумматор 11 - блок 13 - умножитель 9, работающего в соответствии с разностным уравнением:

5

л

П-1

R. -p(nT).p((n-i)T.o6 + R, ; (1-oi),

(3)

где R0

R

ИМ

5

вычисленный кoppeляlц oнный момент ДМ-сигнала; корреля1Ц1оннь1й момент ДМ- сигнала в предыдущем такте работы устройства.

При этом, функдаи элемента задержки на такт выполняет блок 13, в котором хранятся i корреляционные моменты, вычисленные в предыдущем такте работы устройства. Далее корреляционный момент с выхода первого сумматора 11

поступает на вход первого делителя 17, в это же время на вьцсодах первого 14 и второго 15 буферных регистров присутствуют два предыдущих кор - реляционных момента. Так, если на вы- коде первого сумматора 11 присутст- ует сигнал R;+-. то на выходе первого буферного регистра 14 - сигнал

Ui

а -на выходе второго буферного

IjjerHCTpa 15 - сигнал R .

Сигнал с выхода первого буферного 1)егистра 14 через умножитель Ю по- (Ьтупает на второй вход второго сумма- Тора 12, на первый вход которого при этом поступает сигнал с выхода первого делителя 17,-а на третий вход - |;игнал с выхода второго буферного регистра 15 (через второй делитель 18). Сигнал с выхода .-второго сумматора 12 Ьосле прохождения через делитель 19 меет вид

|(3R;, ).

Эта величина является площадью фигуры, образованной сг ммой площадей двух трапеций ABCD и СБЕГ (фиг. 26). Сигналы p((n-i)T с входа и выходов 0 первого сдвигового регистра 3 с частотой ff проключаются через второй типлексор 7 на вход второго сдвигового регистра 4, который осуществляет задержку сигнала p((n-i.)T на величи - -ну 2/f . Таким образом, в тот момент, когда на входе блока 20 инвертирования присутствует сигнал

35

5(3R;,+

2 и.

),

. присутствует

на его управляющем вход

p((n-i)).

Для осуществления предсказания в дельта-кодере производится свертка ДМ-сигнала с его автокорреляционной функцией в соответствии с выражением (2). Поскольку ДМ-сигнал имеет два уровня (представленные как 1 и -1 то свертка производится путем сумми- рования накапливающим сумматором 21 выборочно проинвертированных блоком

20сигн алов с выхода делителя 19. По фронту частоты стробирования

f

происходит запись информации, наN+1

копленной в накапливающем сумматоре

21в третий буферный регистр 16, при

0

этом накапливающий сумматор 21 обнуляется. Вычисленное таким образом значение аппроксимирующего напряжения Sa(nT) восстанавливается при помощи Щ1 22 и поступает на второй вход компаратора 1.

Управление первым 6 и вторым 7 мультиплексорами и блоком 13 оперативной памяти производится с помощью формирователя 23 адресов, работающего в счетном режиме и осуществляющего деление частоты f г входа 25 на N-t-1

15

Коэффициент усреднителя в вьфажел

где (-сд- интер1

20

25

НИИ (3) oi -

.

вал, на котором речевой сигнал молсно .считать стационарным, т.е, слоговая постоянная времени, выбирается поряд-. ка 5 - 10 мс.

Таким образом, так как при вычислении aппpoкcи нpyющeгo напряжения

1

st(ri.T) учитывается линейное изменение

0

35

40

45

. ) 50

55

автокорреляционной функции на тактовом интервале, при использовании предлагаемого кодера повышается отношение сигнал/шум кодера, а также снижается уровень шумов свободного канала. Кроме того, в предлагаемом кодере отсутствуют аналоговые элементы.

Формула изобретения

Дельта-кодер, содержащий компаратор, первый вход которого является информационньш входом дельта-кодера, выход компаратора соединен с информационным входом триггера, выход которого подключен к информационному входу первого сдвигового регистра, первым входам первох о - N-ro полусумматоров (N - число разрядов перво го сдвигового регистра) и является выходом дельта-кодера, второй сдвиговый регистр, тактовый вход которого является тактовым входом дельта-кодера, первый и второй двоичные сумматоры, блок инвертирования и цифроаналого- вый преобразователь, выход которого соединен с вторым входом компаратора, тактовый вход триггера обьединен с тактовым входом первого сдвигового регистра, ЕЫХОДЫ первого - N-ro разрядов которого попключены к вторым входам одноименных полусумматоров, отличаю щ м и с я тем, что, с целью повьпиения точности преобразования за счет снилселия уровня шут-юв

квантования, в дельта-кодер введены формирователь адресов, первый и второй мультиплексоры, блок оперативной памяти, первый - третий умножители на постоянный коэффициент, первый - третий делители на постоянный коэффициент, первый - третий буферные регистры, накапливающий сумматор и (Кн-1)-й полусумматор, первый и второй входы которого объединены первым информационным входом второго мультиплексора и подключены к выходу триг- гера, второй - (Ы+1)й иНформацион161237510

рого умножителей на постоянный коэф фициент, выходы которых соединены с первыми и вторыми входами первого двоичного сумматора, выходы которог подключены к.входам первого делител на постоянный коэффициент и информа ционным входам блока оперативной па мяти и первого беферного регистра, выходы которого соединены с входами третьего умножителя на постоянный к эф4) и информационными входами второго буферного регистра, выходы которого подключены к входам второг

10

ные входы второго мультиплексора под- j делителя на постоянный коэффициент,

КЛЮЧеНЫ к ВЫХППЯМ ГП.ТтРТ ТЧЗОиил Т А-П PMVnTrr.l ГТС1Т ТЗ - Г t

ключены к выходам соответственно первого - N-ro разрядов первого сдвигового регистра, тактовые входы первого и второго буферных регистров объединены с входом формирователя адресов и подключены к тактовому входу дельта-кодера, первыб выходы формирователя адресов соединены с адресными входами первого и второго мультиплексоров и блока оперативной памяти, второй выход формирователя адресов подключен к тактовым входам триггера, накапливающего сумматора и третьего буфер.- ного регистра, выходы (N+D-ro, первого - N-ro полусумматоров соединены соответственно с первым - (Ы+1)-м информационными входами первого мультиплексора, выход fcoToporc и выходы блока оперативной памяти подключены к входам соответственно первого и вто20

25

30

Г

35

выходы первого и второго делителей на постоянный коэффи11(иент и третьег умножителя на постоянный коэффициен соединены с ервыми - третьими входами второгь двоичного сумматора, в ходы которого через третий делитель на ПОСТОЯННЕЙ коэффициент подключены к информационным входам блока инвертирования, выход второго мультиплексора соединен с информационным входом второго сдвигового регистра, выход которого подключен к управляющем входу блока инвертирования, выходы к торого соединены с информационными входами накапливающего сумматора, вы ходы которого подключены к информационным входам третьего буферного ре гистра , выходы которого соединены с входак0{ цифроаналогового преобразователя.

а

О

Яб

7510

рого умножителей на постоянный коэффициент, выходы которых соединены с первыми и вторыми входами первого двоичного сумматора, выходы которого подключены к.входам первого делителя на постоянный коэффициент и информационным входам блока оперативной памяти и первого беферного регистра, выходы которого соединены с входами третьего умножителя на постоянный ко- эф4) и информационными входами второго буферного регистра, выходы которого подключены к входам второго

делителя на постоянный коэффициент,

j делителя на постоянный коэффициент,

PMVnTrr.l ГТС1Т ТЗ - Г t

20

5

0

5

выходы первого и второго делителей на постоянный коэффи11(иент и третьего умножителя на постоянный коэффициент соединены с ервыми - третьими входами второгь двоичного сумматора, выходы которого через третий делитель на ПОСТОЯННЕЙ коэффициент подключены к информационным входам блока инвер.. тирования, выход второго мультиплексора соединен с информационным входом второго сдвигового регистра, выход которого подключен к управляющему входу блока инвертирования, выходы которого соединены с информационными входами накапливающего сумматора, выходы которого подключены к информационным входам третьего буферного регистра , выходы которого соединены с входак0{ цифроаналогового преобразователя.

L А Li-T D L+2

В С F

| Низкоскоростной дельта-модулятор | 1984 |

|

SU1203706A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Величкин А.И, Передача аналоговых сообщений по цифровым каналам связи | |||

| М.: Радио и связь, 1983, с | |||

| Складная решетчатая мачта | 1919 |

|

SU198A1 |

| Дельта-модулятор | 1987 |

|

SU1444953A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| .() ЛЕЛЬТА-КОДЕР i | |||

Авторы

Даты

1990-12-07—Публикация

1989-01-26—Подача