входы первого и второго суммирующих усилителей соответственно через пятый и шестой резисторы соединены с четвертымвходом вычислительной ячейки, а через седьмой и восьмой резисторы - с пятым входом вычислительной ячейки, неинвертирующий вход первого и инвертирующийвход второго суммирующих усилителей соответственно через девятый и десяты

резисторы соединены с шестым входом вычислительной ячейки, а через одиннадцатый и двенадцатый резисторы - с седьмым входом вычислительной ячейки, а неинвертирующие входы первого и второго суммирующих усилителей соответственно через тринадцатый и четырнадцатый резисторы соединены с восьмым входом вычислительной ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для спектрального анализа | 1987 |

|

SU1670619A2 |

| АНАЛИЗАТОР ФУНКЦИЙ УОЛША | 2000 |

|

RU2203504C2 |

| Дискретно-аналоговый анализатор спектра | 1978 |

|

SU734578A1 |

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

| Рекурсивное вычислительное устройство | 1988 |

|

SU1522264A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Преобразователь координат | 1986 |

|

SU1328827A1 |

| Устройство для спектрального анализа | 1973 |

|

SU484528A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

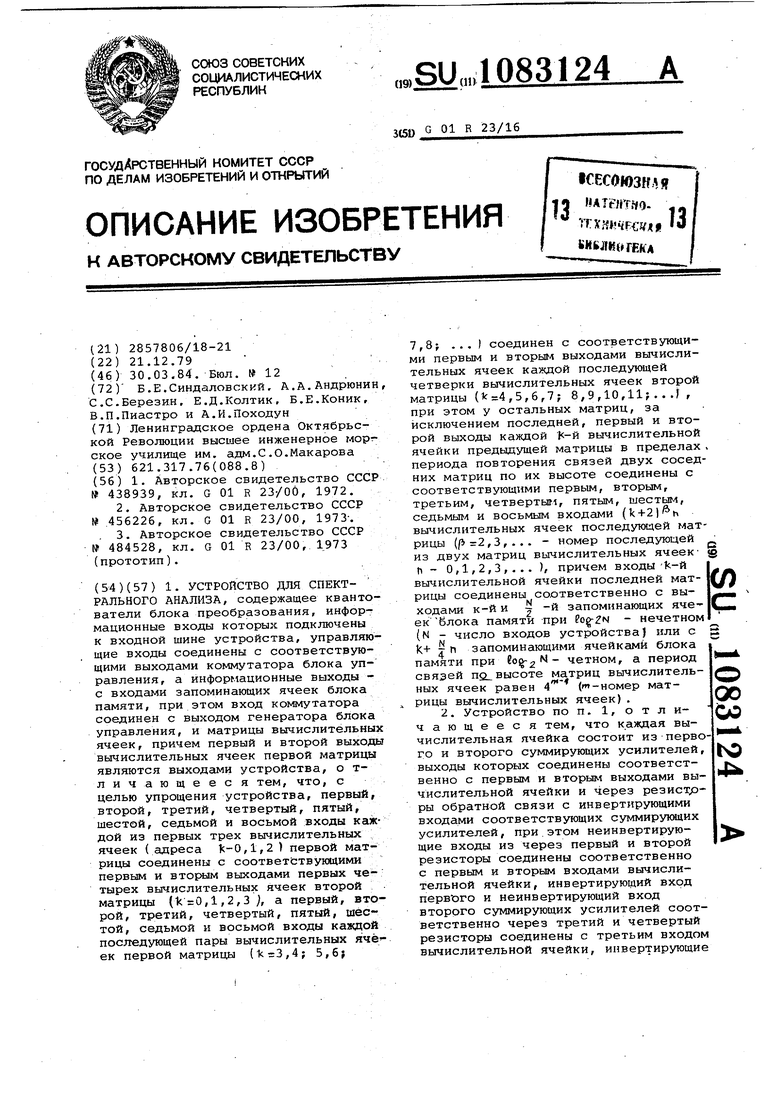

1. УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА, содержащее квантователи блока преобразования, информационные входы которых подключены к входной шине устройства, управляющие входы соединены с соответствующими выходами коммутатора блока управления, а информационные выходы с входами запоминающих ячеек блока памяти, при этом вход коммутатора соединен с выходом генератора блока управления, и матрицы вычислительных ячеек, причем первый и второй выходы вычислительных ячеек первой матрицы являются выходг1МИ устройства, о тличающеес я тем, что, с целью упрощения устройства, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы каждой из первых трех вычислительных ячеек (адреса 1(-0,1,2 ) первой матрицы соединены с соответствующими первым и вторым выходами первых четырех вычислительных ячеек второй матрицы (k 0,1,2,3 ), а первый, второй, третий, четвертый, пятый, шёс той, седьмой и восьмой входы каждой последующей пары вычислительных ячёек первой матрицы (,4; 5,6; 7 ,В; ... I соединен с соответствующими первым и вторым выходами вычислительных ячеек каждой последующей четверки вычислительных ячеек второй матрицы (,5,6,7f 8,9,10,11;...), при этом у остальных матриц, за исключением последней, первый и второй выходы каждой К-й вычислительной ячейки предыдущей матрицы в пределах , периода повторения связей двух соседних матриц по их высоте соединены с соответствующими первым, вторым, третьим, четвертым, пятым, шестым, седьмы и восьмым входами (k+2)t вычислительных ячеек последующей матрицы (р 2,3,... - номер последующей i из двух матриц вычислительных ячеек П - 0,1,2,3,... ), причем входы -й (Л вычислительной ячейки последней матрицы соединены соответственно с выходами к-й и -и запоминающих ячеек блока памяти при Pog-2N - нечетном (N - число входов устройства) или с k+ тп запоминающими ячейками блока памяти при четном, а период связей па высоте матриц вычислительных ячеек равен (т-номер матСХ) рицы вычислительных ячеек) . to к 2. Устройство по п. 1, о т л ичающееся тем, что каждая вычислительная ячейка состоит из первого и второго суммирующих усилителей, выходы которых соединены соответст4 венно с первым и вторым выходами вычислительной ячейки и через резистрры обратной связи с инвертирующими входами соответствующих суммирукяцих усилителей, при.этом неинвертирующие входы из через первый и второй резисторы соединены соответственно с первым и вторым входами вычислительной ячейки, инвертирующий вход первъго и неинвертирующий вход второго суммирующих усилителей соответственно через третий и четвертый резисторы соединены с третьим входом вычислительной ячейки, инвертирующие

Изобретение относится к специализированным средствам аналоговой вычислительной техники, предназначенной для спектрального анализа широкополосных детерминированных и случайных сигналов.

Известно устройство аналогового определения ортогональной составляющей спектра финитных сигналов, содержащее согласующий и инвертирующий каскады, выходы которых через блок периодической выборки мгновенных значений исследуемого сигнала, управляемый генератором импульсов, соединены с сумматором, выполненным в виде RC -интегратора с взвешивающими резисторами Cll.

Недостатком устройства является невысокая точность за счет расхождения значений коэффициентов передачи согласующего и инвертирующего каскадов,а также за счет погрешности, ВНОСИМОЙ RC-интегратором сумматора.

Известен анализатор ортогоналзьных составляющих спектра электрических сигналов, содержащий устройство выборки мгновенны: значений исследуемого сигнала, многоканальный KOMNiyтатор последовательного действия, наборы взвешивающих резисторов, суммирующие устройства, вьшолненные в виде интегрирующих усилителей, и генератор периодической последовательности управляющих импульсов, в котором устройство выборки мгновенных з-нач.ений исследуемого сигнала соединено с входом многоканального коммутатора последовательного.действия, а каждый из выходов последнего связан с входами одного из наборов взвешивающих резисторов, причем один резиг стор из каждого набора вз,0ешиваю1цих резисторов своим выходом присоединен к одному из входов суммирующего устройства С 23 .

Однако устройство характеризуется невысокой точностью,обусловленной погрешностью, вносимой интегрирующими усилителями.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для спектрального анализа, содержа, щее квантователи блока преобразования, информационные входы которых подключень к входной шине устройст- . ва, управляющие входы соединены с соответствующими выходами коммутатора блока управления, а информационУ ные выходы - с входами запоминающих ячеек блока памяти, при этом в;ход коммутатора соединен с выходом генератора блока управления, и матрицы вычислительных ячеек, причем первый

15 и второй выходы вычислительных ячеек первой матрицы являются выходами устройства З.

Недостатком устройства является его сложность, обусловленная необ0 ходимостью использования большого числа вычислительных ячеек, состоящих из инверторов и трехвходовых суммирующих усилителей.

Цель изобретения - упрощение уст5 ройства.

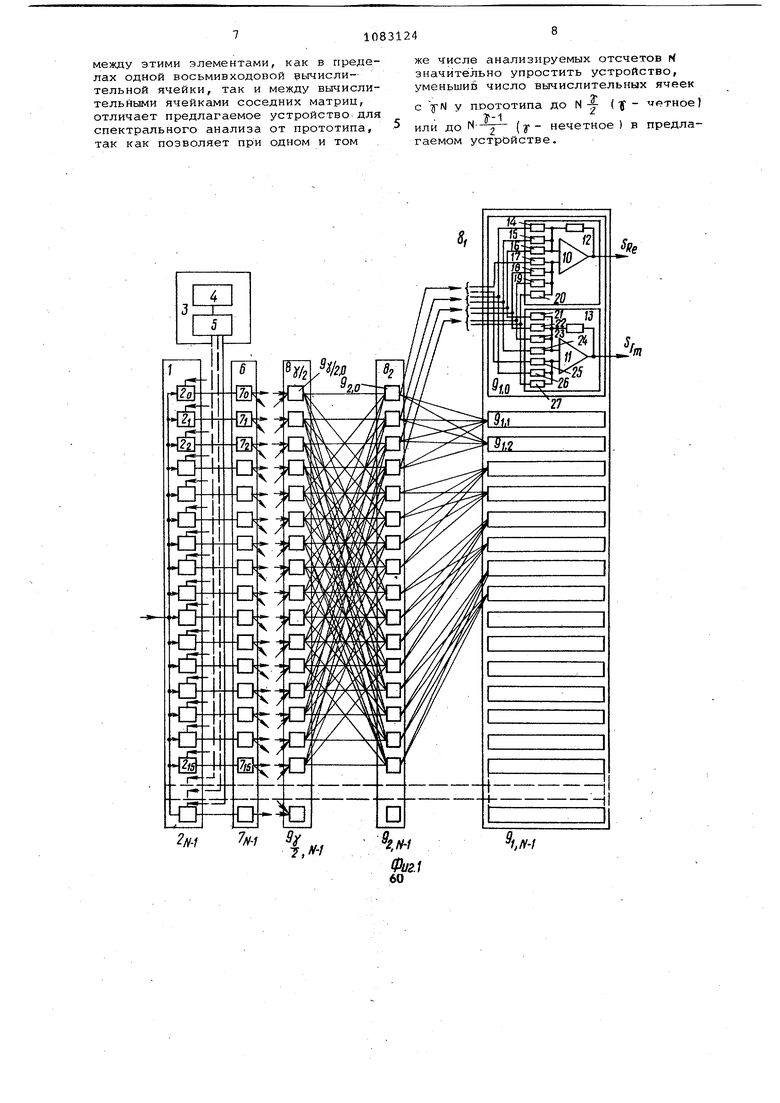

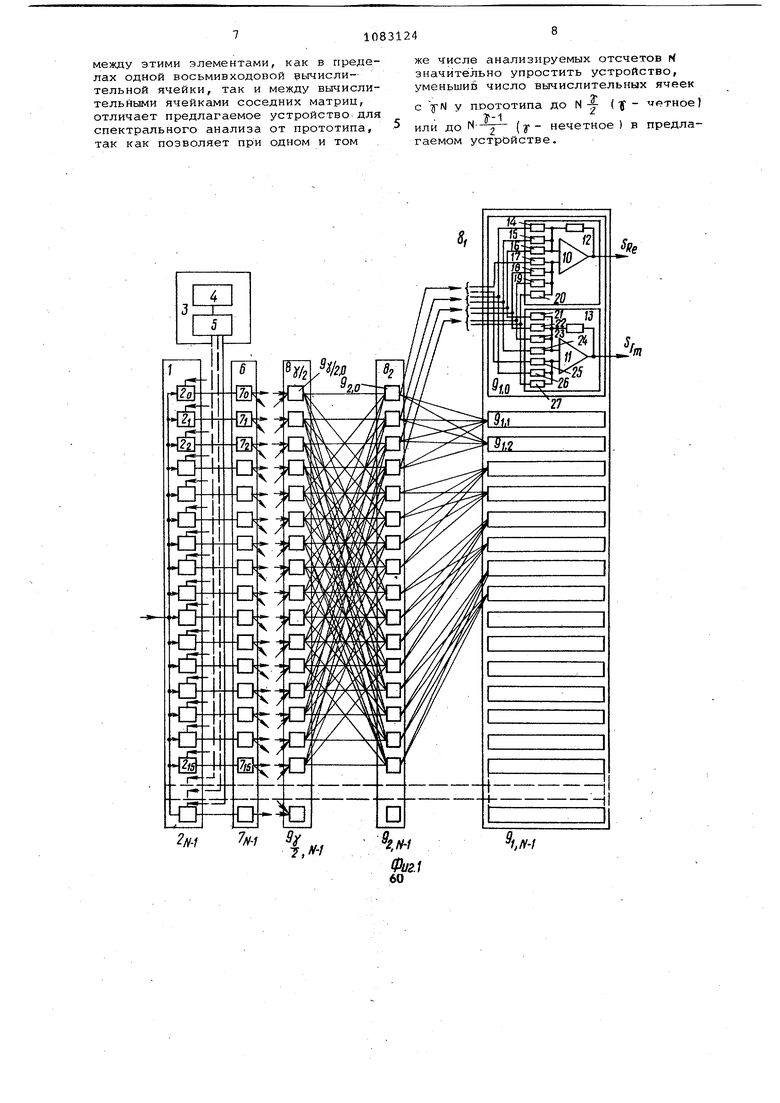

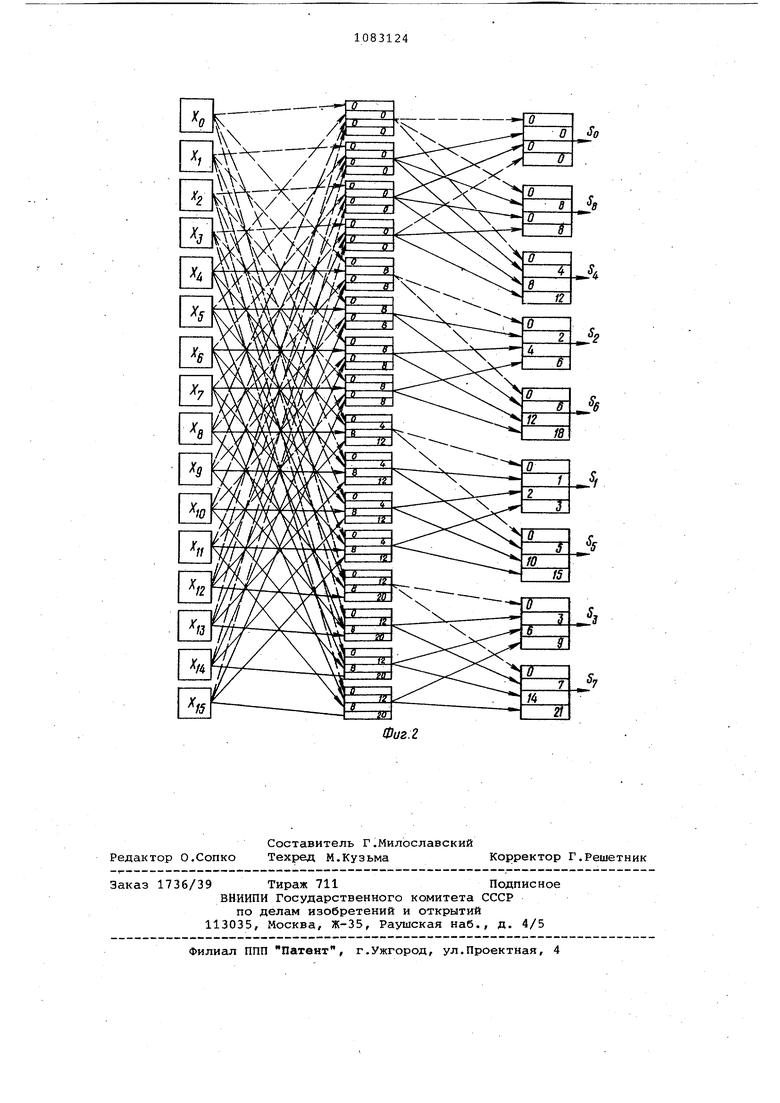

Поставленная цель достигается тем, что в устройствЬ для спектрального анализа, содержащем квантователи блока преобразования, информа0 ционные входы которых подключены к входной шине устройства, управляющие входы соединены с соответствующими выходами коммутатора блока управления, а информационные выходы 5 с входами запоминающих ячеек блока памяти, при этом вход коммутатора соединен с выходом генератора блока управления, и матрицы вычислительных ячеек, причем первый и второй выхоQ ды вычислительных ячеек первой матрицы являются выходами устройства, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы каждой из первых трех вычислительных ячеек (адреса k-0,1,2) пер5 вой матрицы соединены с соответствующими первым и вторым выходами первых четырех вычислительных ячеек второй матрицы (,1,2,3), а первый второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы каждой последующей пары вычислительных ячеек первой матрицы ( 3 , 4 ; 5,6; 7,0: ...I соединены с соответствующими первьм и вторым выходами вычислительных ячеек каждой последующей четверки вычислительных ячеек второй матрицы (,5,6.7; 8,9,10,11;...) при этом у остальных матриц., за исключением последней, первый и ВТОРОЙ выходы каждой вычислительной ячейки предыдущей матрицы в пределах периода повторения связей двух соседних Матриц по их высоте соединены с соответствующими первым,, вторым, третьим, четвертьпч, пятым, шестым, седьмым и восьмым входами (1с+2)и вычислительных ячеек последующей матрицы., (р 2,3, ... - номер последующей из двух матриц вычислительных ячеек;п 0,1,2,3,...| причем входы k-й вычислительной ячей ки последней матрицы соединены COOTIB етственно с выходами и j -и запоминающих ячеек блока памяти при нечетном (N- число входов устройства ) или с К+ т запоминающими ячейками блока памяти при четном, а период связей по высоте матриц вычислительных ячеек равен (т - номер матрицы вычислительных ячеек ). Причем каждая вычислительная -ячей ка состоит из первого и второго суммирующих усилителей, выходы которых соединены соответственно с первым и вторым выходами вычислительной ячейки и через резисторы обратной связи с инвертирующими входами соответствующих суммирующих усилителей, при Ьтом неинвертирующие входы их через первый и второй резисторы соединены соответственно с первым и Входами вычислительной ячейки, инвер тирующий вход первого и неинвертирую щий вход второго суммирующих усилителей соответственно через третий и четвертый резисторы соединены с третьим входом вычислительной ячейки, инвертирующие входы первого и второго суммирующих усилителей / соот ветственно через пятый и шестой резисторы соединены с четвертым входом вычислительной ячейки, а через седьмой и восьмой резисторы - с пятым входом вычислительной ячейки, неинвертирующий вход первого и инвертирующий вход второго суммирующих усилителей соответственно через девятый и десятый резисторы соединены с шестым входом вычислительной ячейки, а через одиннадцатый и двенадцатый резисторы - с седьмым входом вычислительной ячейки, а неинвертирующие .входы первого и второго суммирующих усилителей соответственно через тринадцатый и четырнадцатый резисторы соединены с восьмым входом вычислительной ячейки. На фиг. 1 представлена блок-схема предлагаемого устройства на фиг.2связи между запоминающими ячейками блока памяти и вычислительньоми ячейками . Устройство спектрального анализа содержит блок 1 преобразования, включающий в себя квантователи 2) , 2...2|vj, блок 3 управления с последовательно соединенныг и генератором 4 импульсов и коммутатором 5, €лок 6 памяти, включающий в себя запоминающие ячейки 7, 7, ... 7( , матрицы 8 Yf 2 3/ (-j- четное ) или 8fj,..f)/(r- нечетное) вычислительных ячеек, состоящих из вычислительных ячеек 9, | ( пп - номер матрицы вычислительных Ачеек, к -номер вычислительной ячейки в матрице . Каждая из вычислительных ячеек восьмивходовая и выполнена в виде двух семивходовых суммирующих усилителей 10 и 11 с резисторами 12 и 13 обратной связи и резисторов 14-27, включенных между первым, вторым, третьим, четверть, пятым, шестым, седьмым и восьмым входами вычислительной ячейки, неинвертирующими и инвертирующими входами суммирующих усилителей 10 и 11. Информационные входы всех квантователей 2 блока 1 преобразования соединены с входами устройства, их управляющие входы связаны с выходами коммутатора 5, а информационные выходы - с входами запоминающих ячеек 7 блока 6 памяти. Сигналы, пропорциональные амплитудам ортогональных составляющих комплексного спектра, снимаются с вычислительных ячеек 9 , 9 ., , ..., 9 1 первой от выхода матрицы 8 . Каждая из первых трех вычислительных ячеек 9 матрицы 8 связана с четырьмя первыми вычислительными ячейками 92,о 21 22 2,3 второй матрицы 8, акаждая последующая пара вычислительных ячеек , 9-| if Тбматрицы 8 связана со всеми вычислительными ячейками последующей четверки ячеек 92,4f 9 2,5 г 2,(, 2,1 28 2,Э 2-10 211 матрицы 8 , одновременно у остальных матриц вычислительных ячеек каждая 1с-я вычис лительная ячейка предыдущей матрицы, в пределах периода повторения связей двух соседних матриц по их высоте, соединена с(1с+2)п вычислительными ячейКс1МИ последующей матрицы (р 2,3 ... - номер той из рассматриваемых двух матриц, которая ближе к выходу устройства; rirO,l,2 ...), причем k-я вычислительная ячейка последней матрицы связана с V. и K+N/2 запоминающими ячейками блока 6 памяти при N - нечетном и с К+ п запоминаю щими ячейками блока 6 памяти при Eog-jN- четном, а период повторения связей по высоте матрицы равен 4 (w - номер вычислительных ячеек. В основе устройства лежит вычислительная ячейка, которая выполняет операции вида ,2ехр( Р h%lV Pb) гдеД.,А А А - комплексные числа, характеризующие сигналы, подводимые к ячейке; Д - комплексное число, характеризующее результа вычислений; Чу ,4L,44 поворотов А2 , А А4 соответственно. Семивходовые суммирующие усилите ли 10 и 11 вычисляют величины вещес венной и мнимой частей комплексного числа Д. Истинные знаки весовых коэ фициентов учитываются за счет подкл чения взвешивающих резисторов и ин.вертирующему или неинвертирующему входам суммирующего усилителя. Углы поворота векторов 3 . Ча , t связаны с числом диск ретных отсчетов исследуемого сигнала N соотношением TS . где ,1, ...,N-1 - число, характеризующее рассматриваемую вершину графа. Устройство содержит |Ы вычислительных ячеек, которые объединены в 2 матриц по N вычислительных ячеек в каждой матрице, если у - четное число, и М вычислительных ячеек, которые объединены в-1Ц матриц по N вычислительных ячеек в каждой матрице, если -нечетное число ( N - число дискретных отсчетов исследуемого сигнала, ИгЗ-т). Предлагаемое ,устройство для спект рального анализа реализует модифицированный алгоритм быстрого преобразования Фурье (БПФ). Устройство работает следующим образом. Аналоговый входной сигнал поступа ет На информационные входы квантователей 2 блока 1 преобразования. Импульсы с генератора 4 импульсов чере коммутатор 5 поочередно прикладывают ся на управляющие входы квантователей 2, открывая их. Величины входног сигнала, выбранные с частотой следот вания импульсов генератора 4 импульсов , последовательно подаются на запоминающие ячейки 7 блока 6 памяти, где они запоминаются на время, необходимое для ввода информации. Выходные напряжения запоминающих ячеек 7. поступают на входы вычислительных ячеек 9 матрицы 8 -у/2 ()/2| . С помощью семивходовых суммирующих усилителей 10 и 11 и резисторов 14-27, входящих в йычислительную ячейку 9, выполняются операции по вычислению напряжений, пропорциональных вещественной и мнимой частям комплексного числа, соответствующего входной величине данной вычислительной ячейки. Напряжения, пропорциональные вещественной и мнимой частям результата вьлчисления, формируются на первом и втором выходах вычислительной ячейки путем взвешенного суммирования вещественных и мнимых частей входных комплексных чисел. При этом знак весового коэффициента вводится за счет подключения соответствующего сигнала на инвертирующие и неинвертирующие входы усилителя. Выходные сигналы вычислительных ячеек матрицы (8(-у-)/г1- поступают на входы вычислительных ячеек матрицы 8j. {8(y., где входные сигналы разлагаются на ортогональные составляющие. В последующих матрицах вычислительных ячеек операции разложения входных напряжений вычислительными ячейками повторяются. С выхода вычислительных ячеек первой {от выхода устройства / матрицы 8 снимаются сигналы, пропорциональные амплитудам ортогональных составляющих комплексного спектра. В качестве примера на фиг. 2 представлены связи между запоминающими ячейками 7 и вычислительньоми ячейками устройства cN 16. Слева условно изображены запоминающие ячейки с массивом исходных данных Хд, Х, ... , X j ( индексы характеризуют адреса запоминающих ячеек). Устройство содержит две- матрицы вычислительных ячеек. Пунктирные линии обозначают перенос входного сигнала с весом 1, а сплошные - перенос с k J(- весом W :е), , где К - число, .записанное в прямоугольнике, к которому направлена линия. Устройство вычисляет ортогональные составляющие гармоник порядка 0,1, .. ., 8. Ортогональные составляющие гармоник порядка 9,10, ..., 15 определяются по данным измерений, поскольку векторы, характеризующие гармоники 1и9, 2 и 10 и т.д., - комплексносопряженные . Использование семивходовых суммирующих усилителей и новых связей

между этими элементами, как в пределах одной восьмивходовой рычисли- тельной ячейки, так и между вычислительными ячейками соседних матриц, отличает предлагаемое устройство для спектрального анализа от прототипа, так как позволяет при одном и том

же числе анализируемых отсчетов (Ч значительно упростить устройство, уменьши } число вычислительных ячеек

с yN у прототипа до N (f - четное)

1

ИЛИ до (у- нечетное ) в предлаNгаемом устройстве.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство аналогового определения ортогональной составляющей спектра финитных сигналов | 1972 |

|

SU438939A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-03-30—Публикация

1979-12-21—Подача