Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах отображения графической информации, а также в системах числового программного управления.

Цель изобретения - повышение надежности устройства за счет организации контроля процесса интерполирования.

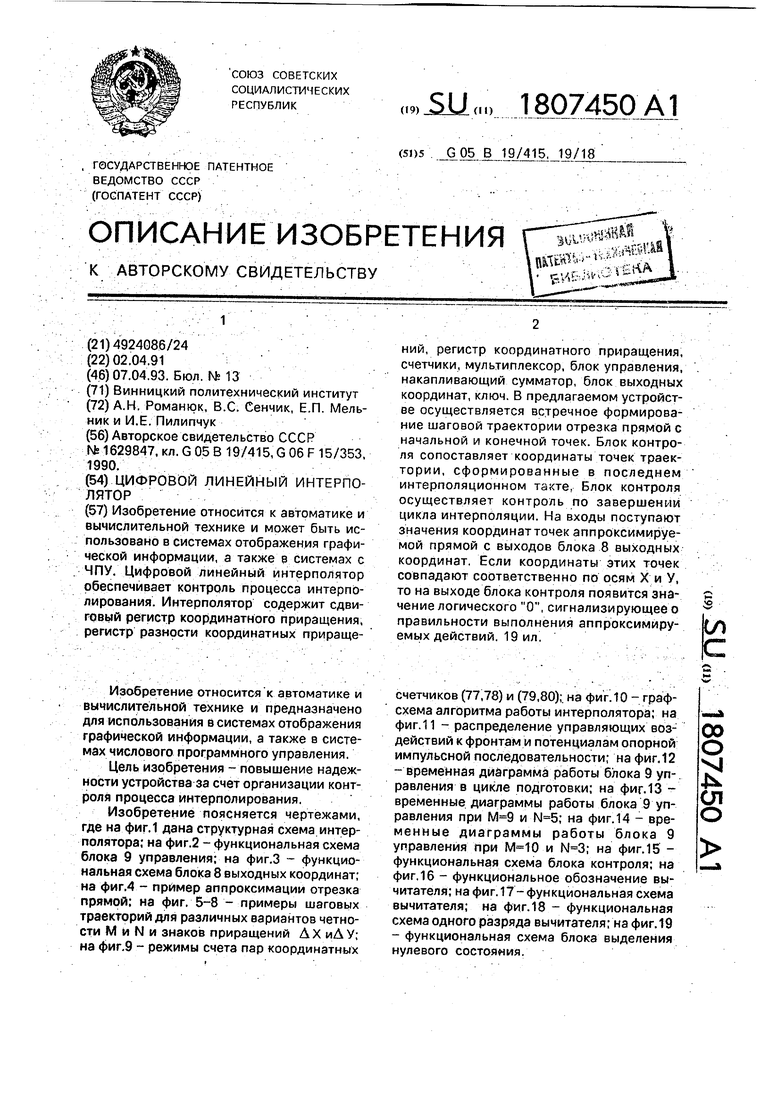

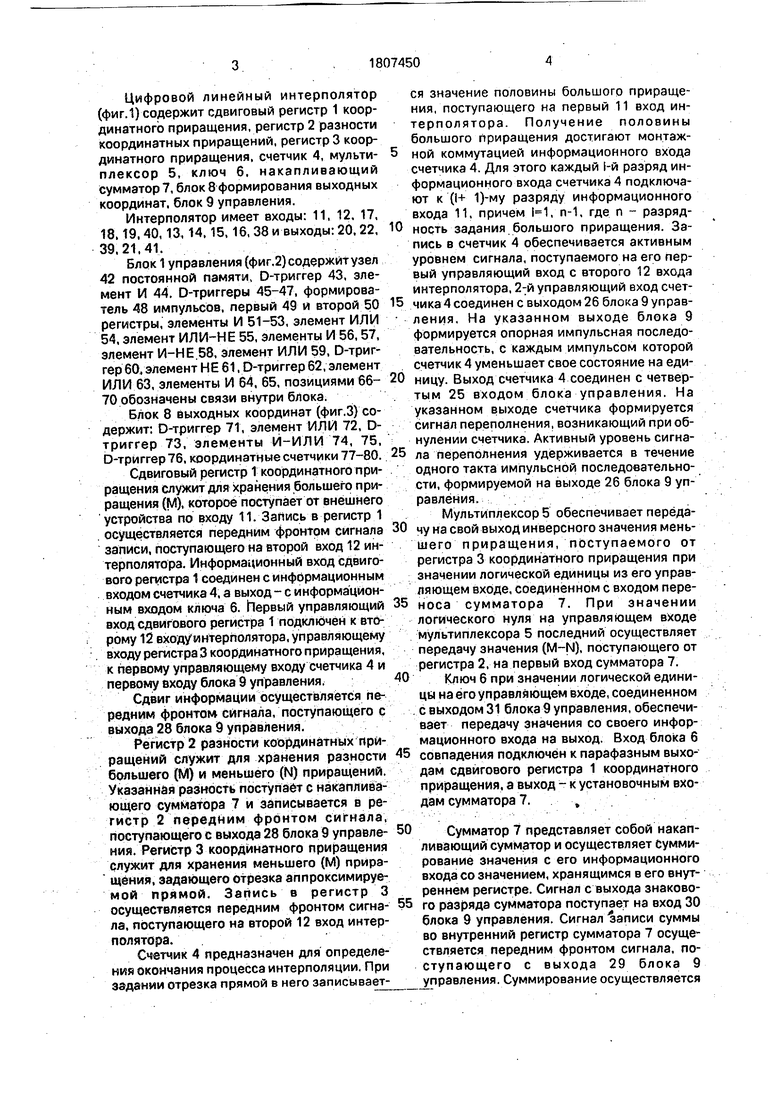

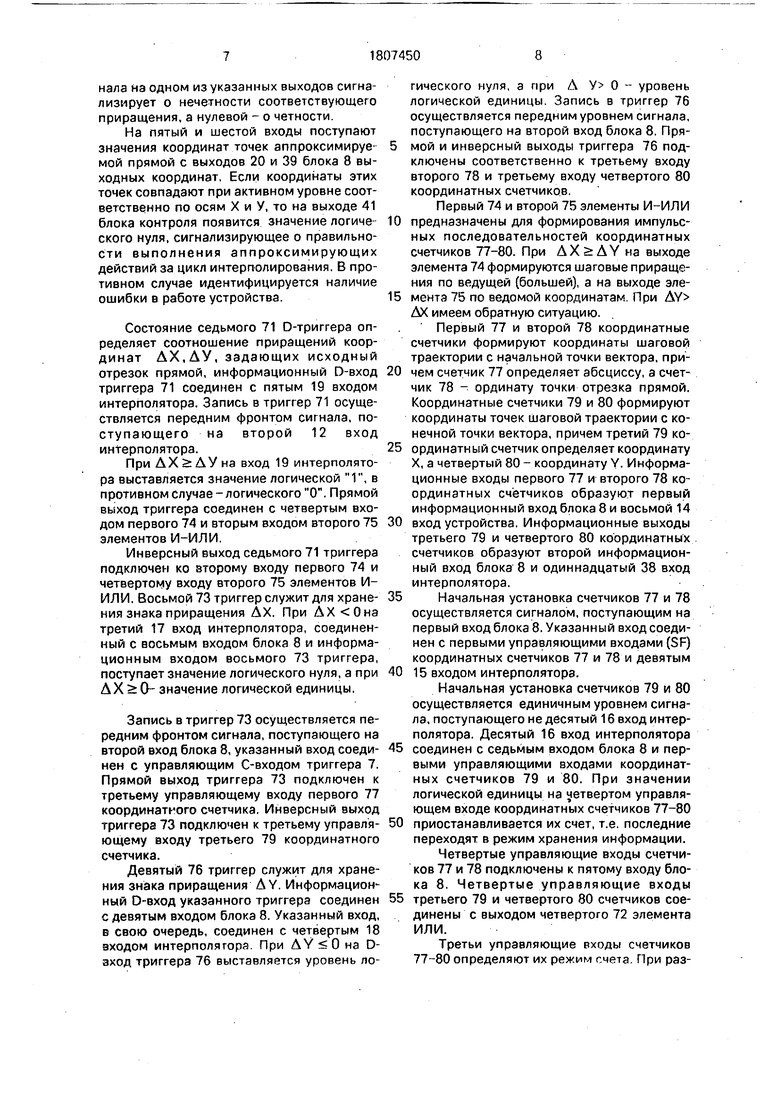

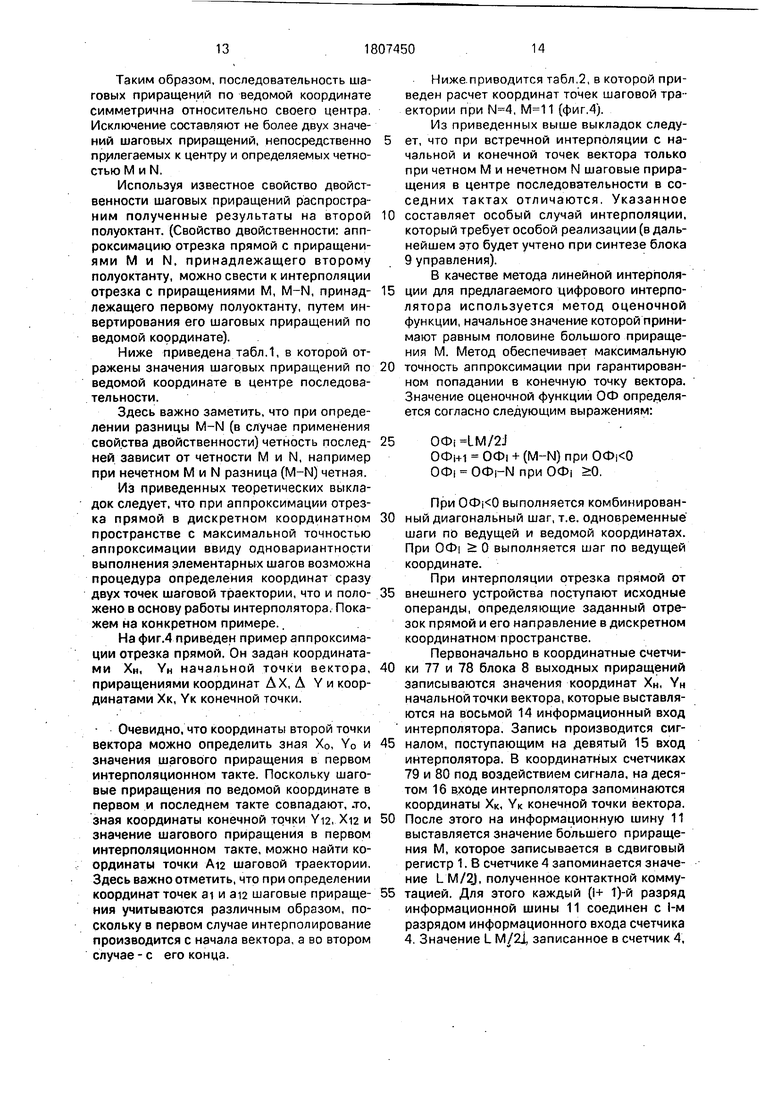

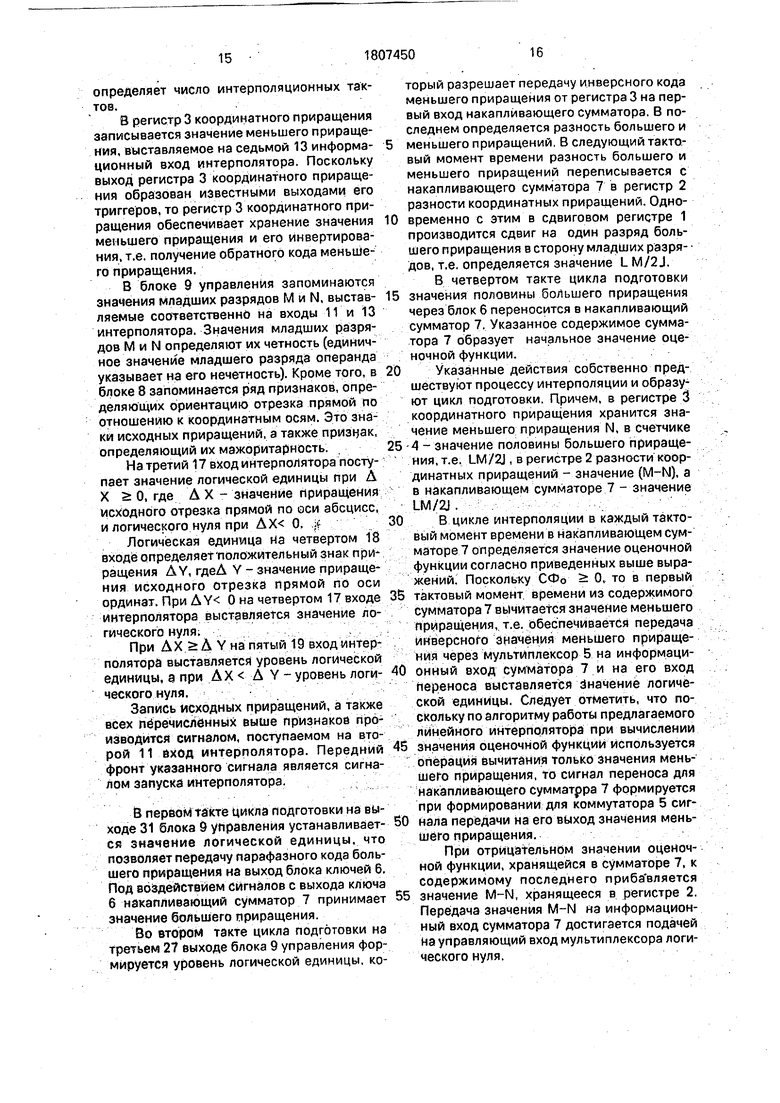

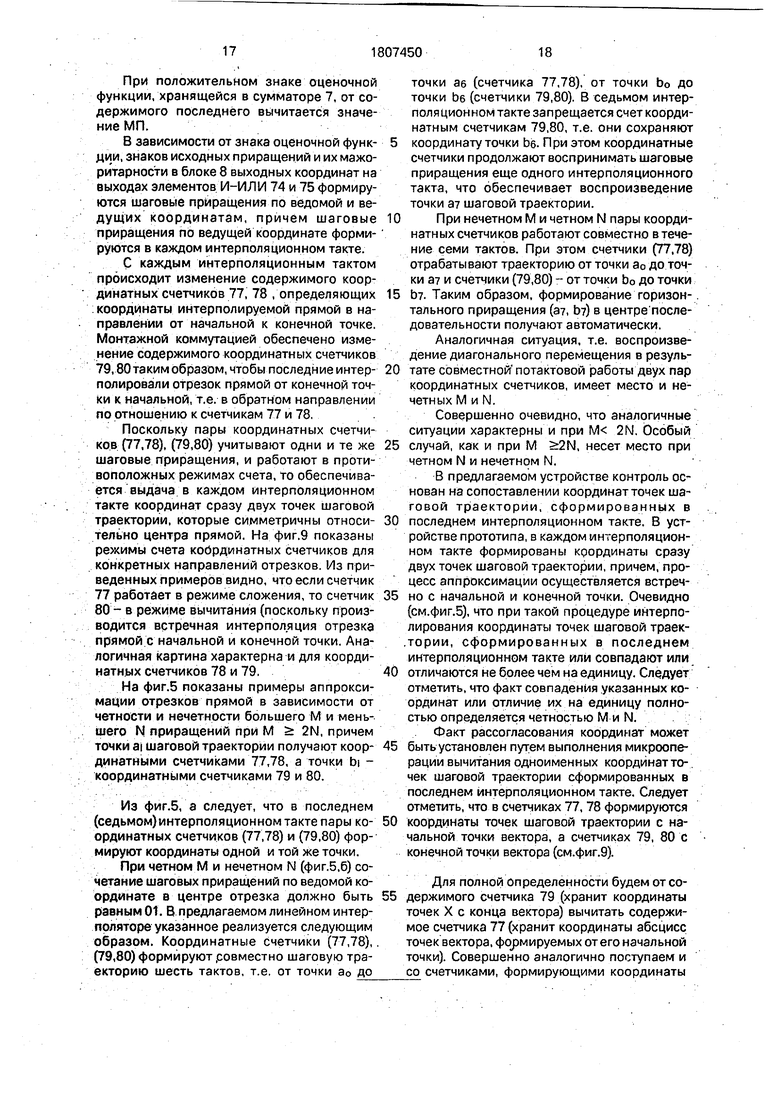

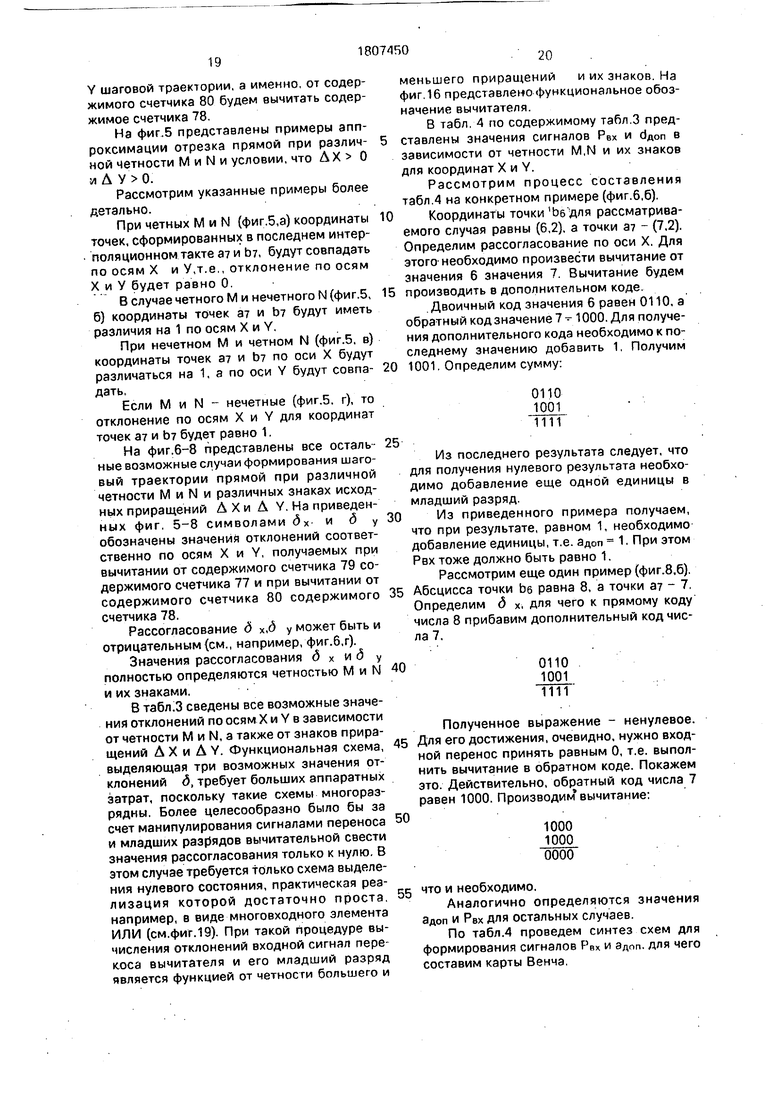

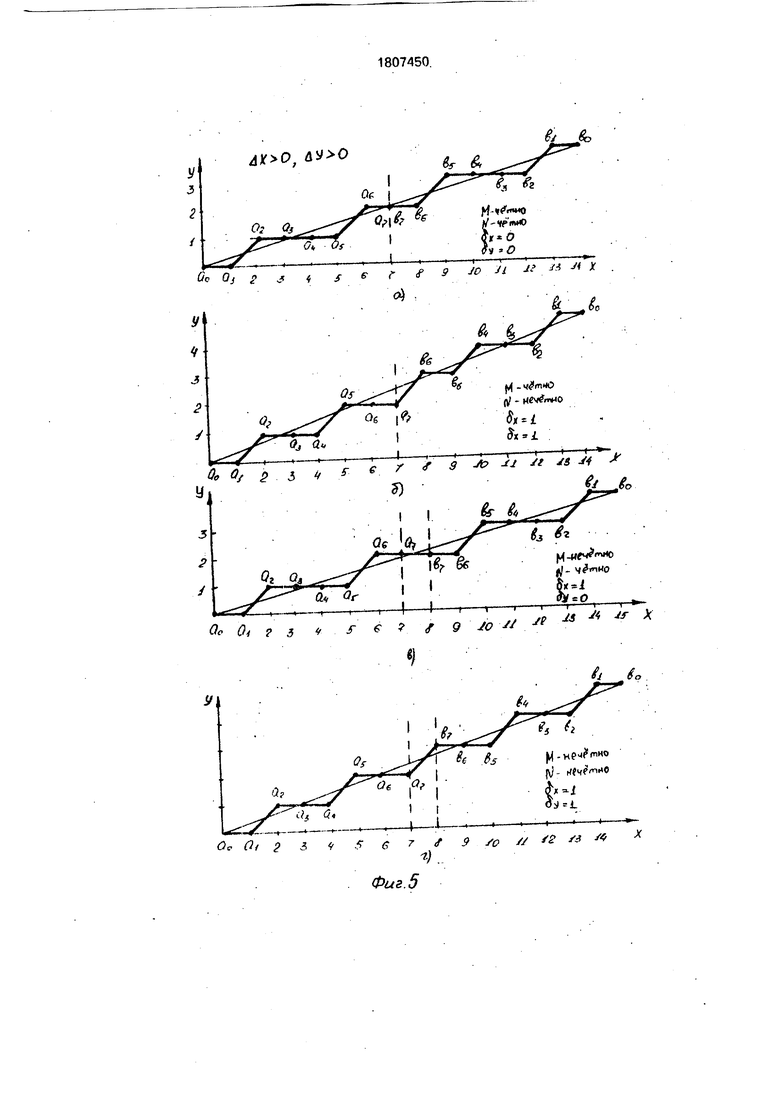

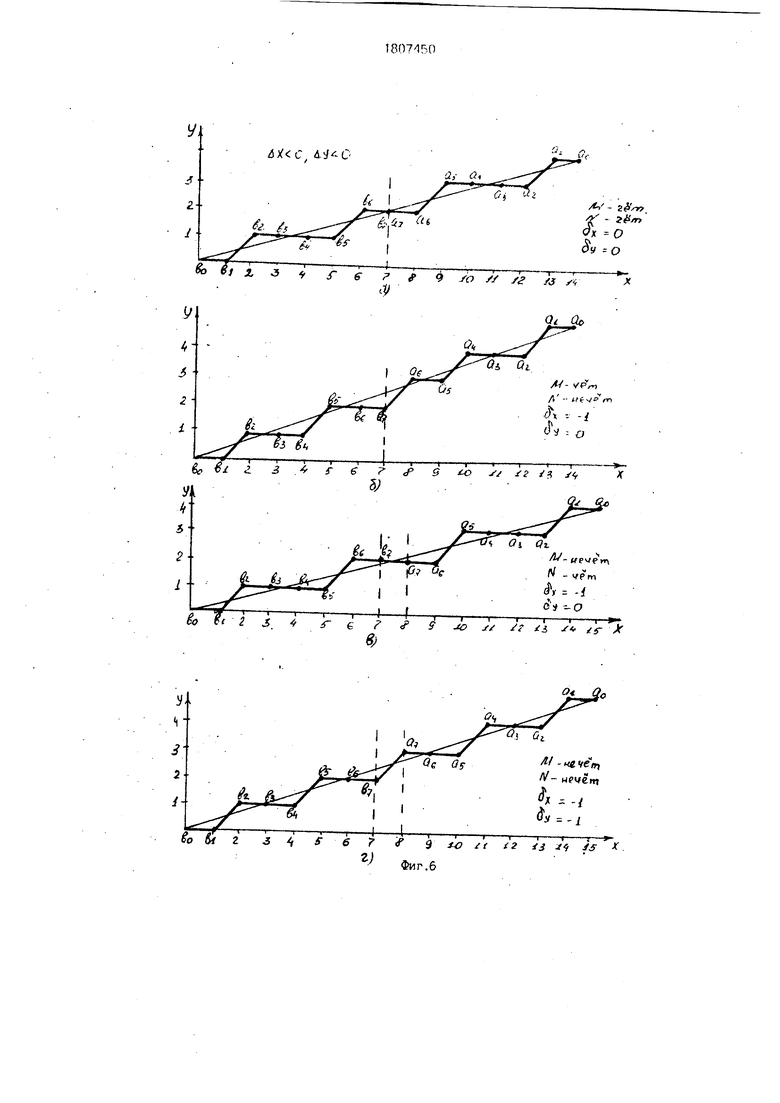

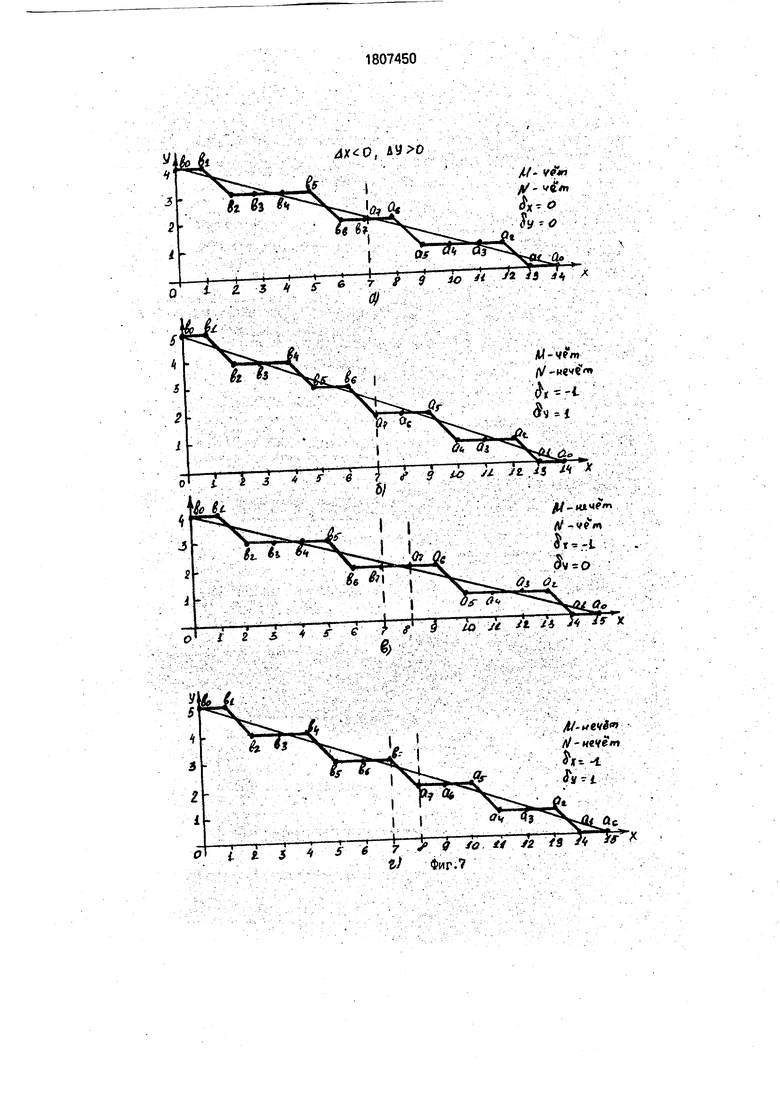

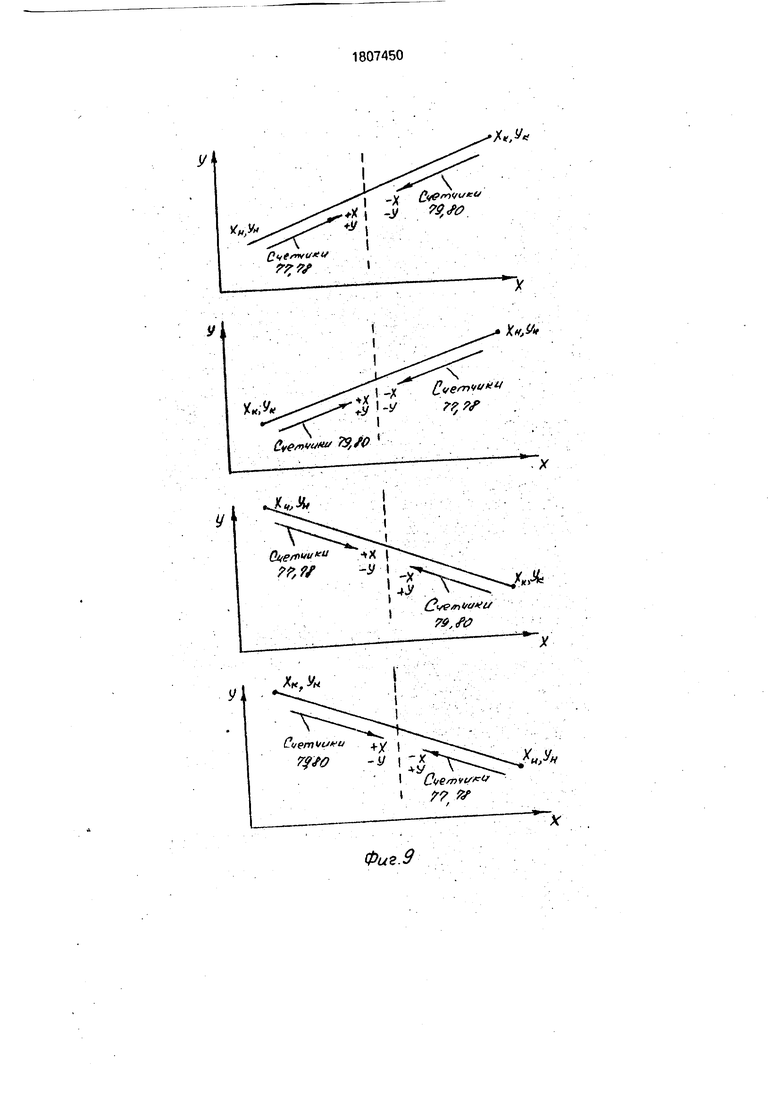

Изобретение поясняется чертежами, где на фиг. 1 дана структурная схема интер- полятора; на фиг.2 - функциональная схема блока 9 управления; на фиг.З - функциональная схема блока 8 выходных координат; на фиг.4 - пример аппроксимации отрезка прямой; на фиг. 5-8 - примеры шаговых траекторий для различных вариантов четности М и N и знаков приращений ДХ иДУ; на фиг.9 - режимы счета пар координатных

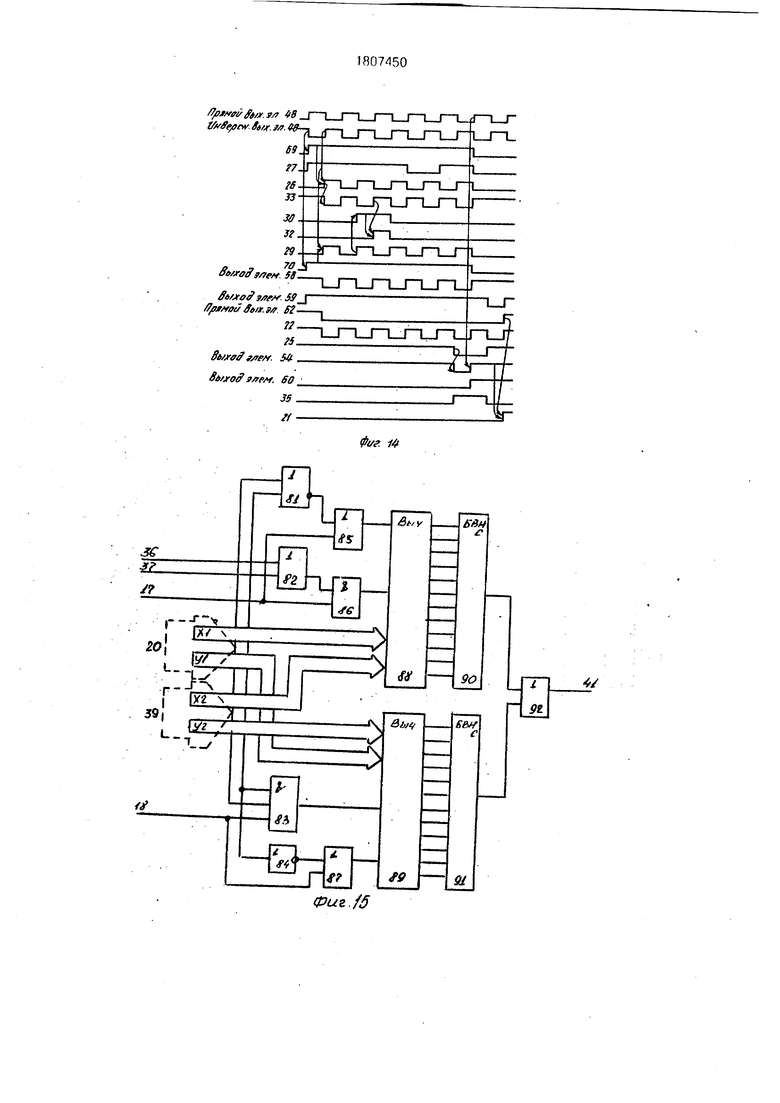

счетчиков (77,78) и (79,80);. на фиг. 10 - граф- схема алгоритма работы интерполятора; на фиг.11 - распределение управляющих воз- действий к фронтам и потенциалам опорной импульсной последовательности; на фиг.12

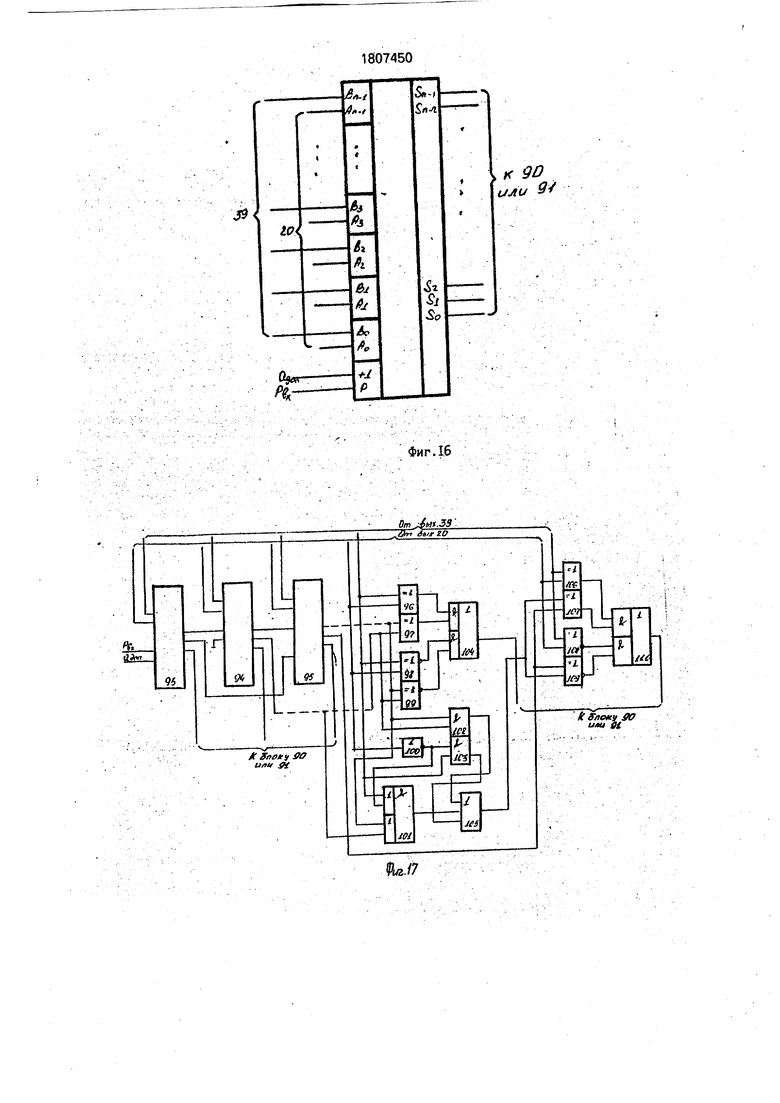

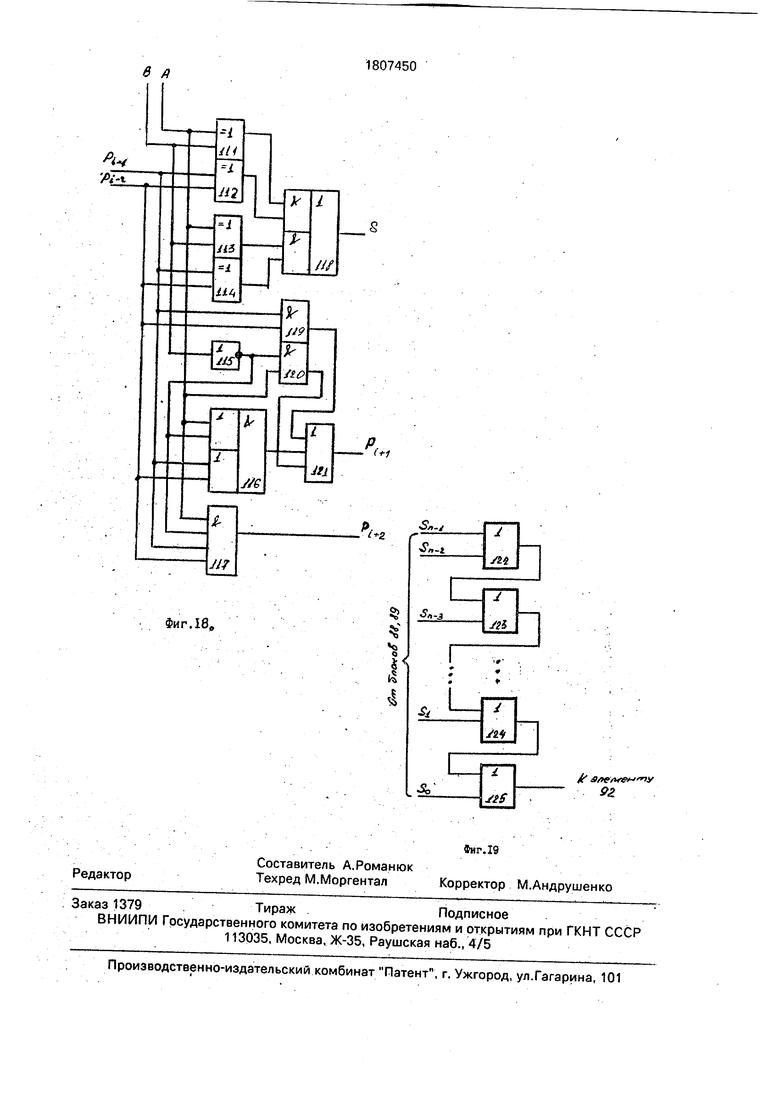

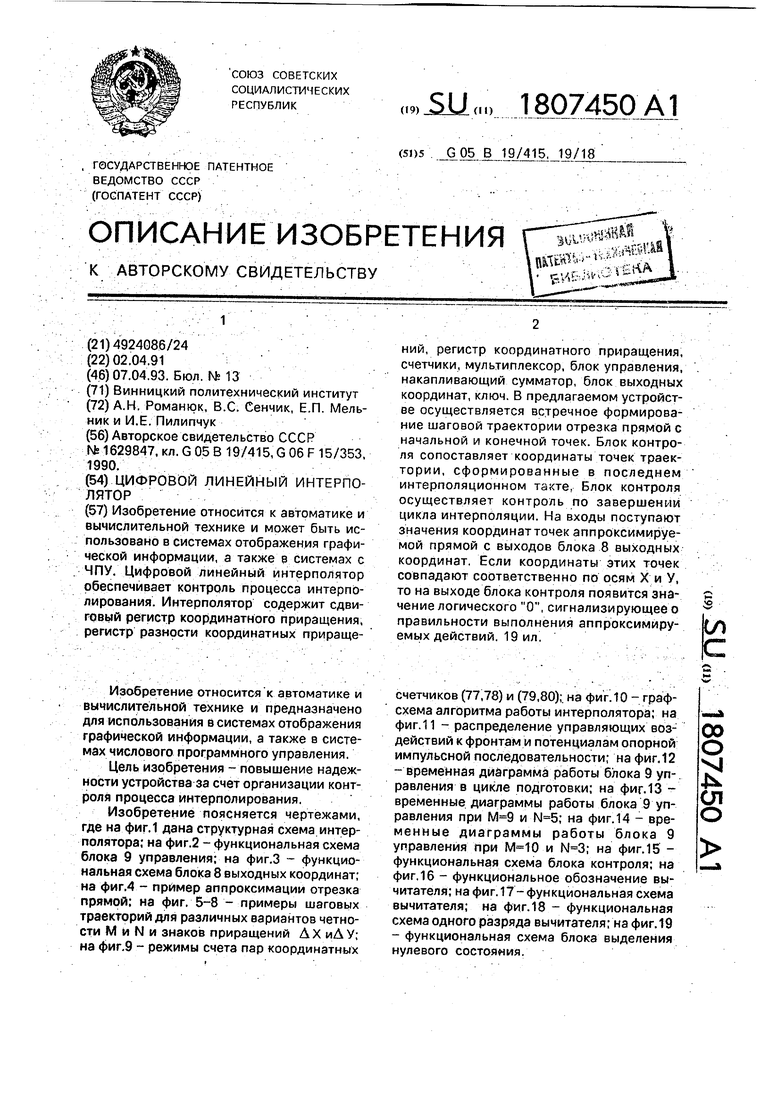

- временная диаграмма работы блока 9 уп-. равления в цикле подготовки; на фиг.13 - временные диаграммы работы блока 9 управления при и на фиг. 14 - временные диаграммы работы блока 9 управления при и на фиг.15 - функциональная схема блока контроля; на фиг. 16 - функциональное обозначение вычитателя; на фиг. 17-функциональная схема вычитателя; на фиг.18 - функциональная схема одного разряда вычитателя; на фиг. 19

- функциональная схема блока выделения нулевого состояния.

00

о

2

СП

о

Цифровой линейный интерполятор (фиг.1) содержит сдвиговый регистр 1 координатного приращения, регистр 2 разности координатных приращений, регистр 3 координатного приращения, счетчик 4, мультиплексор 5, ключ 6, накапливающий сумматор 7, блок 8 формирования выходных координат, блок 9 управления.

Интерполятор имеет входы: 11, 12. 17, 18.19.40,13,14,15,16, 38 и выходы: 20.22, 39.21.41.

Блок 1 управления (фиг,2) содержит узел 42 постоянной памяти, D-триггер 43, элемент И 44, D-триггеры 45-47, формирователь 48 импульсов, первый 49 и второй 50 регистры, элементы И 51-53, элемент ИЛИ 54, элемент ИЛИ-НЕ 55, элементы И 56,57, элемент И-НЕ.58, элемент ИЛИ 59, D-триггер 60, элемент НЕ 61, D-триггер 62, элемент ИЛИ 63, элементы И 64, 65, позициями 66- 70 обозначены связи внутри блока.

Блок 8 выходных координат (фиг.З) содержит: D-триггер 71, элемент ИЛИ 72, D- триггер 73, элементы Й-ИЛИ 74, 75, D-триггер 76, координатные счетчики 77-80.

Сдвиговый регистр 1 координатного приращения служит для хранения большего приращения (М), которое поступает от внешнего устройства по входу 11. Запись в регистр 1 . осуществляется передним фронтом сигнала записи, поступающего на второй вход 12 ин- терполятора. Информационный вход сдвигового регистра 1 соединен с информационным входом счетчика 4, а выход - с информационным входом ключа 6. Первый управляющий вход сдвигового регистра 1 подключён к второму 12 входуинтерполятора, управляющему входу регистра 3 координатного приращения, к первому управляющему входу счетчика 4 и первому входу блока 9 управления.

Сдвиг информации осуществляется передним фронтом сигнала, поступающего с выхода 28 блока 9 управления.

Регистр 2 разности координатных приращений служит для хранения разности большего (М) и меньшего (N) приращений. Указанная разность поступает с накапливающего сумматора 7 и записывается в регистр 2 передним фронтом сигнала, поступающего с выхода 28 блока 9 управления. Регистр 3 координатного приращения служит для хранения меньшего (М) приращения, задающего of резка аппроксимируемой прямой. Запись в регистр 3 осуществляется передним фронтом сигнала, поступающего на второй 12 вход интер- полятора.

Счетчик 4 предназначен для определения окончания процесса интерполяции. При задании отрезка прямой в него записывается значение половины большого приращения, поступающего на первый 11 вход ин- терполятора. Получение половины большого приращения достигают монтажной коммутацией информационного входа счетчика 4. Для этого каждый 1-й разряд информационного входа счетчика 4 подключают к (1+ 1)-му разряду информационного входа 11, причем , п-1, где п - разрядность задания большого приращения. Запись в счетчик 4 обеспечивается активным уровнем сигнала, поступаемого на его первый управляющий вход с второго 12 входа интерполятора, 2-й управляющий вход счетчика 4 соединен с выходом 26 блока 9 управ- ления. На указанном выходе блока 9 формируется опорная импульсная последовательность, с каждым импульсом которой счетчик 4 уменьшает свое состояние на единицу. Выход счетчика 4 соединен с четвертым 25 входом блока управления. На указанном выходе счетчика формируется сигнал переполнения, возникающий при обнулении счетчика. Активный уровень сигнала переполнения удерживается в течение одного такта импульсной последовательности, формируемой на выходе 26 блока 9 управления.

Мультиплексор 5 обеспечивает перёдачу на свой выход инверсного значения меньшего приращения, пйступаемого от регистра 3 координатного приращения при значении логической единицы из его управляющем входе, соединённом с входом переноса сумматора 7. При значении логического нуля на управляющем входе мультиплексора 5 последний осуществляет передачу значения (M-N), поступающего от регистра 2, на первый вход сумматора 7.

Ключ 6 при значении логической единицы на его управляющем входе, соединенном с выходом 31 блока 9 управления, обеспечивает передачу значения со своего информационного входа на выход. Вход блока 6

совпадения подключён к парафазным выходам сдвигового регистра 1 координатного приращения, а выход - к установочным входам сумматора 7.,

Сумматор 7 представляет собой накапливающий сумматор и осуществляет Суммирование значения с его информационного входа со значением, хранящимся в его внутреннем регистре. Сигнал с выхода знакового разряда сумматора поступает на вход 30 блока 9 управления. Сигнал записи суммы во внутренний регистр сумматора 7 осуществляется передним фронтом сигнала, поступающего с выхода 29 блока 9 управления. Суммирование осуществляется

за время действия нулевого уровня сигнала на выходе 29 блока 9.

Блок 8 выходных координат предназначен для формирования координат сразу двух точек шаговой траектории. На выходе 20,первые п разрядов задают координату Xi первой из точек шаговой траектории, а вторые п разрядов - координату Ут первой из точек шаговой траектории, формируемой в данный момент времени. Первые п разрядов выхода 39 определяют координату Х2, а вторые п разрядов - координату Y2 второй из точек шаговой траектории, формируемой в данный момент времени,

Первый управляющий и первый информационный входы блока 8 предназначены для выполнения операции позиционирования начальной точки вектора, т.е. занесения в блок 8 координат Xn, Yn начальной точки вектора. Первый управляющий и первый ин- формационный входы блока 8 соединены соответственное входами 15 и 14 интерпо- лятора; Управляющие входы блока 8 соединены соответственно с выходами 32-35 блока 9 управления. Второй информационный и седьмой управляющий входы блока 8 соединены соответственно с 38 и 16 входами интерполятора.

Указанные входы предназначены для за- поминания в блоке 8 координат Хк и Ук конечной точки вектора. На третий 17 вход интерполятора от внешнего устройства поступает информация о знаке приращения АХ. При значение сигнала на входе 17 интерполятора, соединенном с входом блока 8 выходных координат, равно 1, а при ДХ О - нулю. Совершенно аналогично определяется и знак приращения Y. При А У 0 на четвертый вход интерполятора, соединенный с девятым входом блока 8 выходных координат, выставляется значение логической единицы, в противном случае - значение логического нуля,

: Пятый 19 вход интерполятора соединен с десятым входом блока 8 координатных приращений. Сигнал на указанном входе определяет преобладание одного приращения над другим. При АХ Д Y на вход 19 интерполятора выставляется значение ло- гической 1, в противном случае - логического 0я.

Запись признаков, поступающих на входы 17-19, происходит сигналом, поступающим от внешнего устройства на вход 12 интерполятора. Указанный вход подключен к входу 12 блока 8 выходных координат.

Сигналы, формируемые на 34 и 35 выходах блока 9 управления, предназначены для

управления выдачей координатных точек шаговой траектории. На седьмом 33 выходе формируется опорная импульсная последовательность, под воздействием которой осуществляется выдача координат шаговой траектории по ведущей координате, а на выходе 32 блока 9 управления формируется последовательность импульсов, предназначенных для выдачи координат шаговой траектории по ведомой координате.

Блок 9 управления осуществляет управление операционными узлами интерполятора в соответствии с алгоритмом работы. По второму 12 входу интерполятора происходит запуск интерполятора передним фронтом. Второй 12 вход интерполятора подключен к первому входу блока 9 управления. Единичное значение младшего разряда шины 11 указывает о нечетном значении большего приращения (М), а единичное значение младшего разряда шины нечетном значении меньшего приращения (N). Младший разряд входа 11 интерполятора подключен к третьему входу 23 /блока 9 управления. Младший разряд входа 13 интерполятора подключен к пятому входу 24 блока 9 управления. Вход 40 интерполятора подключен к шестому входу блока 9. По шестому входу происходит начальная установка интерполятора.

На выходе 21 интерполятора формируется сигнал конец интерполирования. Значение логического нуля на выходе 21 сигнализирует об интерполяции отрезка в заданный момент времени, т.е. о занятости интерполятора. При значении логической единицы на выходе 21 интерполятор готов к принятию исходного задания отрезка прямой.

Под воздействием сигнала, формируемого на выходе 22 интерполятора, осуществляется запись выходных координат, формируемых на выходах 20, 39, во внешнюю память. Запись происходит задним фронтом сигнала.

Блок 10 контроля предназначен для определения по формируемым координатам точек шаговой траектории правильности работы интерполятора. Блок 10 контроля начинает свою работу по завершении цикла интерполяции. Первый и второй входы блока подключены соответственно к третьему 17 и четвертому 18 входам интерполятора, третий и четвертый - соответственно к младшим разрядам значении большего и меньшего приращений..

На выходах 36,37 триггеров 45,46 блока 9 формируются признаки, определяющие четность соответственно большего и мень шего приращений. Единичный уровень сигнала на одном из указанных выходов сигнализирует о нечетности соответствующего приращения, а нулевой - о четности.

На пятый и шестой входы поступают значения координат точек аппроксимируемой прямой с выходов 20 и 39 блока 8 выходных координат, Если координаты этих точек совпадают при активном уровне соответственно по осям X и У, то на выходе 41 блока контроля появится значение логиче ского нуля, сигнализирующее о правильности выполнения аппроксимирующих действий за цикл интерполирования. В противном случае идентифицируется наличие ошибки в работе устройства.

Состояние седьмого 71 D-триггера определяет соотношение приращений координат АХ.АУ, задающих исходный отрезок прямой, информационный D-вход триггера 71 соединен с пятым 19 входом интерполятора. Запись в триггер 71 осуществляется передним фронтом сигнала, поступающего на второй 12 вход интерполятора.

При на вход 19 интерполятора выставляется значение логической 1, в противном случае-логического О. Прямой выход триггера соединен с четвертым входом первого 74 и вторым входом второго 75 элементов И-ИЛИ.

Инверсный выход седьмого 71 триггера подключен ко второму входу первого 74 и четвертому входу второго 75 элементов И- ИЛИ. Восьмой 73 триггер служит для хранения знака приращения АХ. При АХ 0 на третий 17 вход интерполятора, соединенный с восьмым входом блока 8 и информационным входом восьмого 73 триггера, поступает значение логического нуля, а при ДХ 0- значение логической единицы.

Запись в триггер 73 осуществляется передним фронтом сигнала, поступающего на второй вход блока 8, указанный вход соединен с управляющим С-входом триггера 7. Прямой выход триггера 73 подключен к третьему управляющему входу первого 77 координатного счетчика. Инверсный выход триггера 73 подключен к третьему управляющему входу третьего 79 координатного счетчика.

Девятый 76 триггер служит для хранения знака приращения A Y. Информационный D-вход указанного триггера соединен с девятым входом блока 8. Указанный вход, в свою очередь, соединен с четвертым 18 входом интерполягора. При на D- зход триггера 76 выставляется уровень логического нуля, а при А У 0 - уровень логической единицы. Запись в триггер 76 осуществляется передним уровнем сигнала, поступающего на второй вход блока 8. Прямой и инверсный выходы триггера 76 подключены соответственно к третьему входу второго 78 и третьему входу четвертого 80 координатных счетчиков.

Первый 74 и второй 75 элементы И-ИЛИ

предназначены для формирования импульсных последовательностей координатных счетчиков 77-80. При на выходе элемента 74 формируются шаговые приращения по ведущей (большей), а на выходе элементэ 75 по ведомой координатам. При AY ДХ имеем обратную ситуацию.

Первый 77 и второй 78 координатные счетчики формируют координаты шаговой траектории с начальной точки вектора, причем счетчик 77 определяет абсциссу, а счетчик 78 - ординату точки отрезка прямой. Координатные счетчики 79 и 80 формируют координаты точек шаговой траектории с конечной точки вектора, причем третий 79 координатный счетчик определяет координату X, а четвертый 80 - координату Y. Информационные входы первого 77 и второго 78 координатных счётчиков образуют первый информационный вход блока 8 и восьмой 14

вход устройства. Информационные выходы третьего 79 и четвертого 80 координатных счетчиков образуют второй информационный вход блока 8 и одиннадцатый 38 вход интерполятора.

Начальная установка счетчиков 77 и 78 осуществляется сигналом, поступающим на первый вход блока 8. Указанный вход соединен с первыми управляющими входами (SF) координатных счетчиков 77 и 78 и девятым

15 входом интерполятора.

Начальная установка счетчиков 79 и 80 осуществляется единичным уровнем сигнала, поступающего не десятый 16 вход интерполятора. Десятый 16 вход интерполятора

соединен с седьмым входом блока 8 и первыми управляющими входами координатных счетчиков 79 и 80. При значении логической единицы на четвертом управляющем входе координатных счетчиков 77-80

приостанавливается их счет, т.е. последние переходят в режим хранения информации. Четвертые управляющие входы счетчиков 77 и 78 подключены к пятому входу блока 8. Четвертые управляющие входы

третьего 79 и четвертого 80 счетчиков соединены с выходом четвертого 72 элемента ИЛИ.

Третьи управляющие входы счетчиков 77-80 определяют их режим счета. При разрешении .счета единичный уровень сигнала на указанном входе определяет счет в прямом направлении, т.е. в режиме сложения, а при значении логического нуля - в обратном направлении, т.е. в режиме вычитания.

Вторые управляющие входы счетчиков 77-80 являются их входами счета. При поступлении переднего фронта сигнала на указанном входе происходит инкрементное изменение содержимого счетчика. Вторые управляющие входы первого 77 и третьего 79 координатных счетчиков соединены с выходом первого 74 элемента И-ИЛИ; Вторые управляющие входы второго 78 и четвертого 80 координатных счетчиков подключены к выходу второго 75 элемента И-ИЛИ. .

Выходы первого 77 и второго 78 координатных счетчиков образуют первую группу 20 информационных выходов блока 8, а выходы третьего 79 и четвертого 80 координат- ных счетчиков образуют вторую информационную группу выходов 39 блока 8.

Первый вход четвертого элемента 72 подключен к пятому входу блока 8, а второй вход - к шестому входу блока 8.

Узел 42 постоянной памяти предназначен для хранения микрокоманд/определяющих выполнение требуемых операций. Первый, второй и третий входы узла 42 памяти подключены к выходам второго регистра, а четвертый вход - к пятому входу блока управления. С первого по четвертый входы узла 42 памяти определяют адрес микрокоманды. Первые пять выходов узла 42 памяти соединены с информационным входом первого 49 регистра, предназначенного для хранения микрокоманды, поступаемой с блока 42. Сигналы на шестом, седьмом и восьмом выходах узла 42 памяти совместно со значением сигнала переполнения сумматора 7 образуют адрес микрокоманды, которая будет выполняться в следующем такте. С шестого по восьмой выходы узлов 42 памяти соединены соответственно с первым, вторым и третьим входами второго 50 регистра. С первого по третий выходы первого 49 регистра подключены соответственно к пятому 31, третьему 27 и первому 28 выходам блока управления. Четвертый 69 выход регистра 49 соединен с первыми входами элементов 56, 59, 58. Пятый 70 выход регистра 49 соединен с первым входом элемента 57.

Управляющие R-входы регистров 49 и 50 подключены к выходу первого 44 элемента И и R-входам первого 43 и четвертого 47 D-триггеров. На выходе элемента 44 формируется сигнал установки в начальное состояние регистров 49, 50 и триггеров 43 и 47. Управляющие С-входы первого 49 и второго 50 регистров подключены соответственно к выходам второго 51 и третьего 52 элементов. 5 И. Триггеры 43 и 47 предназначены для синхронизированного начала работы интерполя- тора с первым импульсом, вырабатываемым формирователем импульсов 48, после поступления сигнала Пуск на первый вход бло0 ка 9 управления. Информационный D-вход триггера 43 соединен с выходом логической единицы, а управляющий С-вход - с входом 12 блока 9 управления, С-входами 45 и 46 D-триггеров с входом элемента И 53.

5 Выход триггера 43 подключен к информационному D-входу триггера 47, управляющий С-вход которого соединен с прямым выходом формирователя импульсов 48, вторым входом второго элемента 51 и вторыми

0 входами элементов 54, 59, 63 ИЛИ.

Прямой выход триггера 47 подключен к первому входу первого 51 и второго 52 элементов И. Инверсный выход формирователя 48 импульсов подключен к входам элемен5 тов И 52, 56, 57, входу элемента И 58 И-НЕ, Выход шестого 57 элемента И соединен с четвертым 29 выходом блока 9 управления.

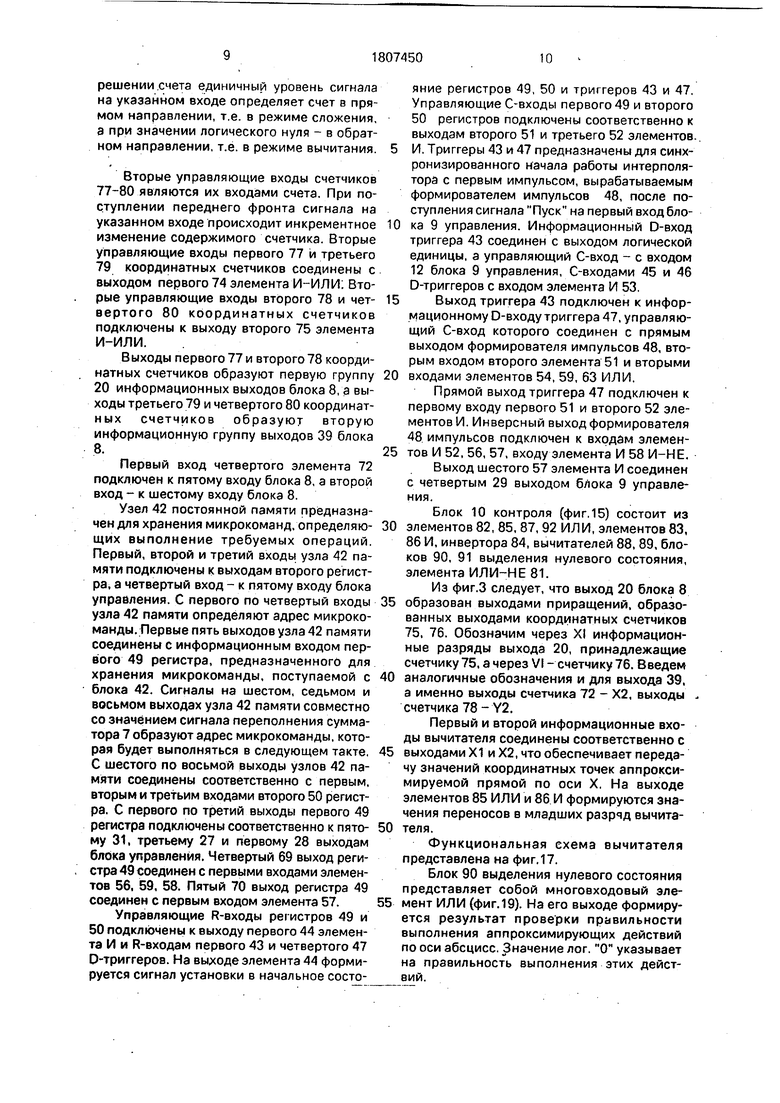

Блок 10 контроля (фиг. 15) состоит из

0 элементов 82, 85,87, 92 ИЛИ, элементов 83, 86 И, инвертора 84, вычитателей 88, 89, блоков 90, 91 выделения нулевого состояния, элемента ИЛИ-НЕ 81.

Из фиг.З следует, что выход 20 блока 8

5 образован выходами приращений, образованных выходами координатных счетчиков 75, 76. Обозначим через XI информационные разряды выхода 20, принадлежащие счетчику 75, а через VI - счетчику 76. Введем

0 аналогичные обозначения и для выхода 39, а именно выходы счетчика 72 - Х2, выходы счетчика 78 - Y2.

Первый и второй информационные входы вычитателя соединены соответственно с

5 выходами Х1 и Х2, что обеспечивает передачу значений координатных точек аппроксимируемой прямой по оси X. На выходе элементов 85 ИЛИ и 86 И формируются значения переносов в младших разряд вычита0 теля.

Функциональная схема вычитателя представлена на фиг. 17.

Блок 90 выделения нулевого состояния представляет собой многовходовый эле5 мент ИЛИ (фиг. 19). На его выходе формируется результат проверки правильности выполнения аппроксимирующих действий по оси абсцисс. Значение лог. О указывает на правильность выполнения этих действий.

По аналогии построена схема контроля по оси У. Первый и второй информационные входы вычитателя соединены соответственно с входами У1 и У2, что обеспечивает передачу значений координат точек аппроксимируемой прямой по оси Y. На выходе элементов 83 И 87 ИЛИ формируются значения переносов в младший разряд вычитателя. Функциональная схема вычитателя по оси Y идентична схеме вычитателя по оси X. На выходе блока 91 выделения нулевого состояния формируется результат проверки правильности работы интерполятора по оси ординат. На выходе 41 элемента 92 ИЛИ формируется результат работы блока 10 контроля в целом.

Рассмотрим работу линейного интерполятора. Для этого докажем, что последовательность шаговых приращений по ведомой координате при аппроксимации отрезка прямой с максимальной точностью симметрична относительно своего центра, за исключением не более двух ближайших к нему значений приращения,

Пусть аппроксимируемый отрезок пря- мой задан меньшим N и большим М приращения, причем М 2N.

Отклонение идеальной прямой от-ближайшего ординатного уровня решетки в точке равно:.

d(D)l-jJJ-D-0,5jNМ

D

где L -J - оператор выделения целой части 35 числа.

В точке X M-D

N

d(M-D) L(M-D)-gj-+0,5J (М -D) ,5J +

Л

М

Отсюда следует, что. d(D) (M-D).

Поскольку отклонение идеальной прямой от ближайших точек решетки совпадает по модулю при значениях абсцисс, равных

D, (M-D) ( ), то ввиду одновариантностм выполнения элементарных шагов при аппроксимации вектора с максимальной точностью заключаем, что последовательность шаговых приращений по ведомой координате симметрична относительно своего центра.

5

0

5

0

Определим значения шаговых приращений по ведомой координате, которые являются ближайшими к центру последовательности, поскольку их значения могут отличаться ввиду различного числа единичных приращений за первый и второй полуциклы.

Если М и N - четные, то точка (N/2, М/2) идеальной прямой совпадает с точкой решетки, а числа единичных шаговых приращений по ведомой координате за первый и второй полуциклы совпадают. Отсюда следует, что при четных М и N свойство симметричности шаговых приращений по ведомой координате выполняется для всех ,М/2,

Для обозначения четкости и нечеткости N и М введем вспомогательные параметры

, си LN/2J nZi LM/2J- При четном М и нечетном N N

(ЧЙ-ЈН

л;

2а + 1 2-Zi

h

ZiM.5

25

30

35

40

45

В данном случае в М/2 такте по ведомой координате можно выполнять как нулевой, так и единичный элементарный шаг, поскольку точность аппроксимации в обоих случаях не превышает половины шага дискретизации. Для первого полуоктанта наличие двух единичных шаговых приращений по ведомой координате в смежные тактовые моменты времени невозможно. Отсюда следует, что если при четном Ми нечетном N в М/2 такте выполняется единичное шаговое приращение по ведомой координате, то в (М/2+1)-м такте значение шагового приращения по ведомой координате нулевое, и наоборот.

При нечетном М и четном N ордината идеальной прямой в точке М/2 равна а 1. Отклонение точки (Zi, a i) решетки от указанного ординатного уровня равно:

2«1

2Zi +1

«- Zi

а

2Zi + 1

а точки (Zi+ 1, а 1) -a i(2Zi+ 1). Учитывая, что указанные отклонения меньше по модулю 0,5, а также их знаки, заключаем, что в такте (Zi+ 1) по ведомой координате шаговое приращение не формируют, т.е. в указанном такте выполняют горизонтальное перемещение.

Совершенно аналогично можно показать, что при нечетном значении М и N в такте (Zi+ 1) по ведомой координате выполняются единичное шаговое приращение.

Таким образом, последовательность шаговых приращений по ведомой координате симметрична относительно своего центра. Исключение составляют не более двух значений шаговых приращений, непосредственно прилагаемых к центру и определяемых четностью М и N.

Используя известное свойство двойственности шаговых приращений распространим полученные результаты на второй полуоктант. (Свойство двойственности: аппроксимацию отрезка прямой с приращениями М и N, принадлежащего второму полуоктанту, можно свести к интерполяции отрезка с приращениями М, M-N, принад- лежащего первому полуоктанту, путем инвертирования его шаговых приращений по ведомой координате).

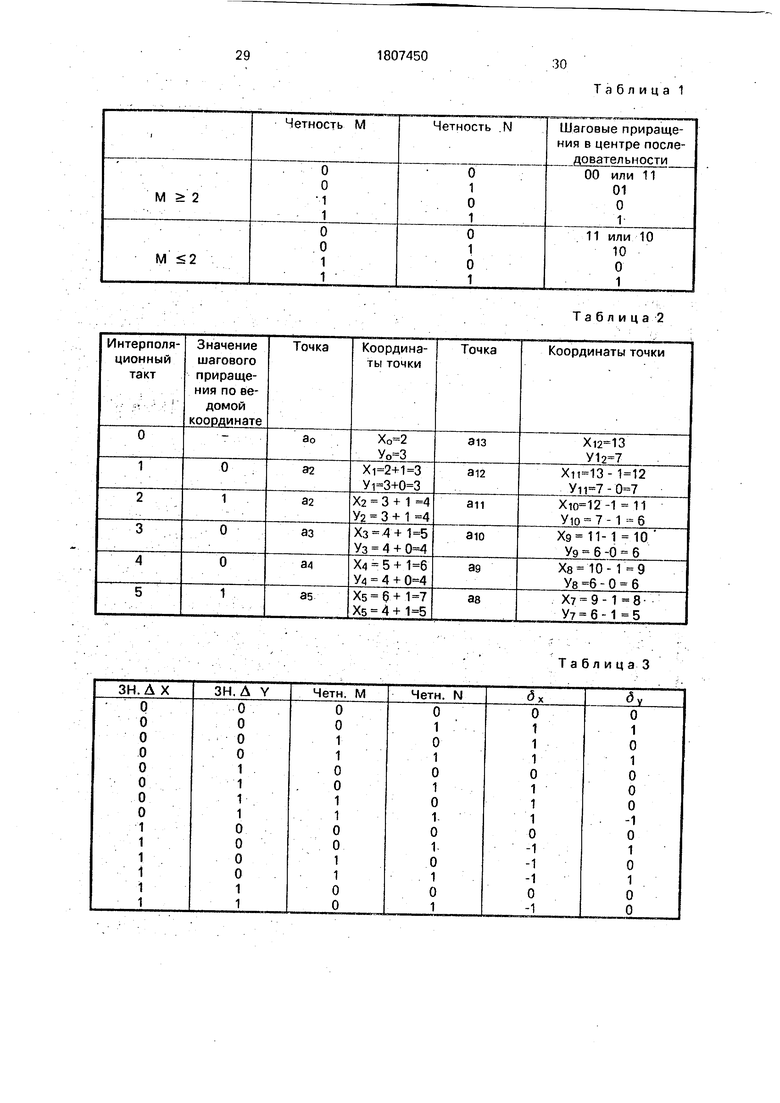

Ниже приведена табл.1, в которой отражены значения шаговых приращений по ведомой координате в центре последовательности.

Здесь важно заметить, что при определении разницы M-N (в случае применения свойства двойственности) четность послед- ней зависит от четности М и N, например при нечетном М и N разница (M-N) четная.

Из приведенных теоретических выкладок следует, что при аппроксимации отрезка прямой в дискретном координатном пространстве с максимальной точностью аппроксимации ввиду одновариантности выполнения элементарных шагов возможна процедура определения координат сразу двух точек шаговой траектории, что и поло- жено в основу работы интерполятора. Покажем на конкретном примере.

На фиг.4 приведен пример аппроксимации отрезка прямой. Он задан координатами Хи, Ун начальной точки вектора, приращениями координат АХ, Л Y и координатами Хк, YK конечной точки.

Очевидно, что координаты второй точки вектора можно определить зная Х0, Y0 и значения шагового приращения в первом интерполяционном такте. Поскольку шаговые приращения по ведомой координате в первом и последнем такте совпадают, .то, зная координаты конечной точки Yi2, Xia и значение шагового приращения в первом интерполяционном такте, можно найти координаты точки Ai2 шаговой траектории, Здесь важно отметить, что при определении координат точек ai и aia шаговые прираще- ния учитываются различным образом, поскольку в первом случае интерполирование производится с начала вектора, а во втором случае - с его конца.

Ниже.приводится табл.2, в которой приведен расчет координат точек шаговой траектории при , (фиг.4).

Из приведенных выше выкладок следует, что при встречной интерполяции с начальной и конечной точек вектора только при четном М и нечетном N шаговые приращения в центре последовательности в соседних тактах отличаются. Указанное составляет особый случай интерполяции, который требует особой реализации (в дальнейшем это будет учтено при синтезе блока 9 управления).

В качестве метода линейной интерполяции для предлагаемого цифрового интерполятора используется метод оценочной функции, начальное значение которой принимают равным половине большого приращения М. Метод обеспечивает максимальную точность аппроксимации при гарантированном попадании в конечную точку вектора. Значение оценочной функции ОФ определяется согласно следующим выражениям:

OOi lM/2J

ОФн-1 ОФ| + (M-N) при

ОФ| ОФ|ЧМ при ОФ1 0.

При выполняется комбинированный диагональный шаг, т.е. одновременные шаги по ведущей и ведомой координатах. При ОФ| S 0 выполняется шаг по ведущей координате.

При интерполяции отрезка прямой от внешнего устройства поступают исходные операнды, определяющие заданный отрезок прямой и его направление в дискретном координатном пространстве.

Первоначально в координатные счетчики 77 и 78 блока 8 выходных приращений записываются значения координат Хн, YH начальной точки вектора, которые выставляются на восьмой 14 информационный вход интерполятора. Запись производится сигналом, поступающим на девятый 15 вход интерполятора. В координатных счетчиках 79 и 80 под воздействием сигнала, на десятом 16 входе интерполятора запоминаются координаты Хк, YK конечной точки вектора. После этого на информационную шину 11 выставляется значение большего приращения М, которое записывается в сдвиговый регистр 1. В счетчике 4 запоминается значение L M/2J, полученное контактной коммутацией. Для этого каждый (i+ 1)-й разряд информационной шины 11 соединен с 1-м разрядом информационного входа счетчика 4. Значение L M/2J, записанное в счетчик 4,

определяет число интерполяционных тактов.

В регистр 3 координатного приращения записывается значение меньшего приращения, выставляемое на седьмой 13 информационный вход интерполятора. Поскольку выход регистра 3 координатного приращения образован известными выходами его триггеров, то регистр 3 координатного приращения обеспечивает хранение значения меньшего приращения и его инвертирования, т.е. получение обратного кода меньшего приращения,

В блоке 9 управления запоминаются значения младших разрядов М и N, выставляемые соответственно на входы 11 и 13 интерполятора. Значения младших разрядов М и N определяют их четность (единичное значение младшего разряда операнда указывает на его нечетность). Кроме того, в блоке 8 запоминается ряд признаков, определяющих ориентацию отрезка прямой по отношению к координатным осям. Это знаки исходных приращений, а также признак, определяющий их мажоритарность.

На третий 17 вход интерполятора поступает значение логической единицы при А X S 0, где АХ- значение Приращения исходного отрезка прямой по оси абсцисс, и логического нуля при А Х 0, if

Логическая единица на четвертом 18 входе определяет положительный знак при ращения A Y, гдеА V - значение приращения исходного отрезка прямой по оси ординат. При A Y 0 на четвертом 17 входе интерполятора выставляется значение логического нуля;,

При АХ.& A Y на пятый 19 вход интерполятора выставляется уровень логической единицы, а. при АХ A Y - уровень логического нуля.

Запись исходных приращений, а также всех перечисленных выше признаков производится сигналом, поступаемом на второй 11 вход интерполятора. Передний фронт указанного сигнала является сигналом запуска интерполятора.

В первом такте цикла подготовки на выходе 31 блока 9 управления устанавливается значение логической единицы, что позволяет передачу парафазного кода большего приращения на выход блока ключей 6, Под воздействием сигналов с выхода ключа 6 накапливающий сумматор 7 принимает значение большего приращения.

Во втором такте цикла подготовки на третьем 27 выходе блока 9 управления формируется уровень логической единицы, который разрешает передачу инверсного кода меньшего приращения от регистра 3 на первый вход накапливающего сумматора. В последнем определяется разность большего и

меньшего приращений, В следующий тактовый момент времени разность большего и меньшего приращений переписывается с накапливающего сумматора 7 в регистр 2 разности координатных приращений. Одно- временно с этим в сдвиговом регистре 1 производится сдвиг на один разряд большего приращения в сторону младших разря- дов, т.е. определяется значение L M/2J. В четвертом такте цикла подготовки

значения половины большего приращения через блок 6 переносится в накапливающий сумматор 7. Указанное содержимое сумматора 7 образует начальное значение оценочной функции.

Указанные действия собственно предшествуют процессу интерполяции и образуют цикл подготовки. Причем, в регистре 3 координатного приращения хранится значение меньшего приращения N, в счетчике

-А - значение половины большего приращения, т.е. LM/2J , в регистре 2 разности координатных приращений - значение (M-N), а в накапливающем сумматоре 7 - значение LM/2J. ..:.:.;

В цикле интерполяции в каждый тактовый момент времени в накапливающем сумматоре 7 определяется значение оценочной функции согласно приведенных выше выражений. Поскольку СФо 2: 0, то в первый

тактовый момент времени из содержимого сумматора 7 вычитается значение меньшего Приращения, т.е. обеспечивается передача инверсного значения меньшего приращения через мультиплексор 5 на информационный вход сумматора 7 и на его вход переноса выставляется Значение логической единицы. Следует отметить, что поскольку по алгоритму работы предлагаемого линейного интерполятора при вычислении

значения оценочной функций используется операция вычитания только значения меньшего приращения, то сигнал переноса для накапливающего сумматрра 7 формируется при формировании для коммутатора 5 сигНала передачи на его выход значения меньшего приращения.

При отрицательном значении оценочной функции, хранящейся в сумматоре 7, к содержимому последнего прибавляется

значение M-N, хранящееся в регистре 2. Передача значения M-N на информационный вход сумматора 7 достигается подачей на управляющий вход мультиплексора логического нуля.

При положительном знаке оценочной функции, хранящейся в сумматоре 7, от содержимого последнего вычитается значение МП.

В зависимости от знака оценочной функ- дии, знаков исходных приращений и их мажо- ритарности в блоке 8 выходных координат на выходах элементов И-И Л И 74 и 75 формируются шаговые приращения по ведомой и ведущих координатам, причем шаговые приращения по ведущей координате формируются в каждом интерполяционном такте.

С каждым интерполяционным тактом происходит изменение содержимого координатных счетчиков 77, 78 .определяющих : координаты интерполируемой прямой в направлении от начальной к конечной точке. Монтажной коммутацией обеспечено изменение содержимого координатных счетчиков 79, ВОтакимобразом, чтобы последние интер- полировали отрезок прямой от конечной точки к начальной, т.е. в обратном направлении по отношению к счетчикам 77 и 78.

Поскольку пары координатных счетчиков (77,78), (79,80) учитывают одни и те же шаговые приращения, и работают в противоположных режимах счета, то обеспечивается выдача в каждом интерполяционном такте координат сразу двух точек шаговой траектории, которые симметричны относи- тельно центра прямой. На фиг.9 показаны режимы счета кобрдинатных счетчиков для конкретных направлений отрезков. Из приведенных примеров видно, что ее л и счетчик 77 работает в режиме сложения, то счетчик 80 - в режиме вычитания (поскольку производится встречная интерполяция отрезка прямой с начальной и конечной точки. Аналогичная картина характерна и для координатных счетчиков 78 и 79.

На фиг.5 показаны примеры аппроксимации отрезков прямой в зависимости от четности и нечетности большего М и меньшего N приращений при М 2N, причем точки а| шаговой траектории получают коор- дикатными счетчиками 77,78, а точки bi - координатными счетчиками 79 и 80.

Из фиг.5, а следует, что в последнем (седьмом)интерполяционном такте пары ко- ординатных счетчиков (77,78) и (79,80) формируют координаты одной и той же точки.

При четном М и нечетном N (фиг.5,6) сочетание шаговых приращений по ведомой координате в центре отрезка должно быть равным ОТ. В предлагаемом линейном интер- прляторе указанное реализуется следующим образом. Координатные счетчики (77,78), (79,80) формируют .совместно шаговую траекторию шесть тактов, т.е. от точки ао до

точки ае (счетчика 77,78), от точки Ь0 до точки be (счетчики 79,80). В седьмом интерполяционном такте запрещается счет координатным счетчикам 79,80, т.е. они сохраняют координату точки be. При этом координатные счетчики продолжают воспринимать шаговые приращения еще одного интерполяционного такта, что обеспечивает воспроизведение точки ау шаговой траектории.

При нечетном М и четном N пары координатных счетчиков работают совместно в течение семи тактов. При этом счетчики (77.78) отрабатывают траекторию от точки а0 до точки а и счетчики (79,80) - от точки Ь0 до точки Ь. Таким образом, формирование горизонтального приращения (а, Ь) в центре после- довательности получают автоматически.

Аналогичная ситуация, т.е. воспроизведение диагонального перемещения в результате совместной потактовой работы двух пар координатных счетчиков, имеет место и нечетных М и N.

Совершенно очевидно, что аналогичные ситуации характерны и при М 2N, Особый случай, как и при М 2N, несет место при четном N и нечетном N.

В предлагаемом устройстве контроль основан на сопоставлении координат точек шаговой траектории, сформированных в последнем интерполяционном такте, В устройстве прототипа, в каждом интерполяционном такте формированы координаты сразу двух точек шаговой траектории, причем, процесс аппроксимации осуществляется встречно с начальной и конечной точки. Очевидно (см.фиг.5), что при такой процедуре интерполирования координаты точек шаговой траек- .тории, сформированных в последнем интерполяционном такте или совпадают или отличаются не более чем на единицу. Следует отметить, что факт совпадения указанных координат или отличие их на единицу полностью определяется четностью Ми N.

Факт рассогласования координат может быть установлен путем выполнения микрооперации вычитания одноименных координат точек шаговой траектории сформированных в последнем интерполяционном такте. Следует отметить, что в счетчиках 77, 78 формируются координаты точек шаговой траектории с начальной точки вектора, а счетчиках 79, 80 с конечной точки вектора (см.фиг.9).

Для полной определенности будем от содержимого счетчика 79 (хранит координаты точек X с конца вектора) вычитать содержимое счетчика 77 (хранит координаты абсцисс точек вектора, формируемых отего начальной точки). Совершенно аналогично поступаем и со счетчиками, формирующими координаты

Y шаговой траектории, а именно, от содержимого счетчика 80 будем вычитать содержимое счетчика 78.

На фиг,5 представлены примеры аппроксимации отрезка прямой при различной четности М и N и условии, что ЛХ О и Д У 0.

Рассмотрим указанные примеры более детально.

При четных М и N (фиг.5,а) координаты точек, сформированных в последнем интерполяционном такте а и Ь, будут совпадать по осям X и У,т.е., отклонение по осям X и У будет равно 0.

В случае четного М и нечетного N (фиг.5, б) координаты точек а и Ь будут иметь различия на 1 по осям X и Y,

При нечетном М и четном N (фиг.5, в) координаты точек а и Ь по оси X будут различаться на 1, а по оси Y будут совпадать,

Если М и N - нечетные (фиг.5. г), то отклонение по осям X и Y для координат точек а и Ь будет равно 1.

На фиг.6-8 представлены все остальные возможные случаи формирования шаговый траектории прямой при различной четности М и N и различных знаках исходных приращений Д X и Л Y. На приведенных фиг. 5-8 символами 3х и б у обозначены значения отклонений соответственно по осям X и Y, получаемых при вычитании от содержимого счетчика 79 содержимого счетчика 77 и при вычитании от содержимого счетчика 80 содержимого счетчика 78.

Рассогласование d х,3 y может быть и отрицательным (см., например, фиг.6,г).

Значения рассогласования д х и б у полностью определяются четностью М и N и их знаками.

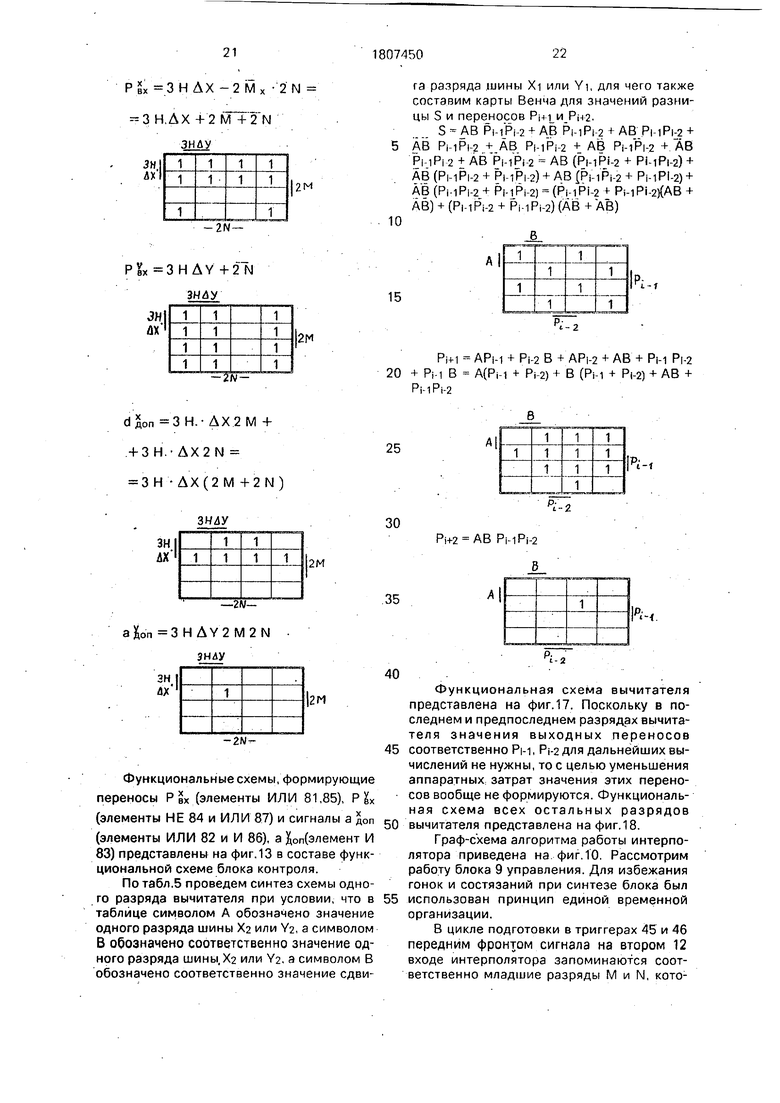

В табл.3 сведены все возможные значения отклонений по осям X и Y в зависимости от четности М и N, а также от знаков приращений Д X и Д Y. Функциональная схема, выделяющая три возможных значения отклонений 3, требует больших аппаратных затрат, поскольку такие схемы многоразрядны. Более целесообразно было бы за счет манипулирования сигналами переноса и младших разрядов вычитательной свести значения рассогласования только к нулю. В этом случае требуется только схема выделения нулевого состояния, практическая реализация которой достаточно проста, например, в виде многовходного элемента ИЛИ (см.фиг.19). При такой процедуре вычисления отклонений входной сигнал перекоса вычитателя и его младший разряд является функцией от четности большего и

меньшего приращений и их знаков. На фиг. 16 представлено функциональное обозначение вычитателя.

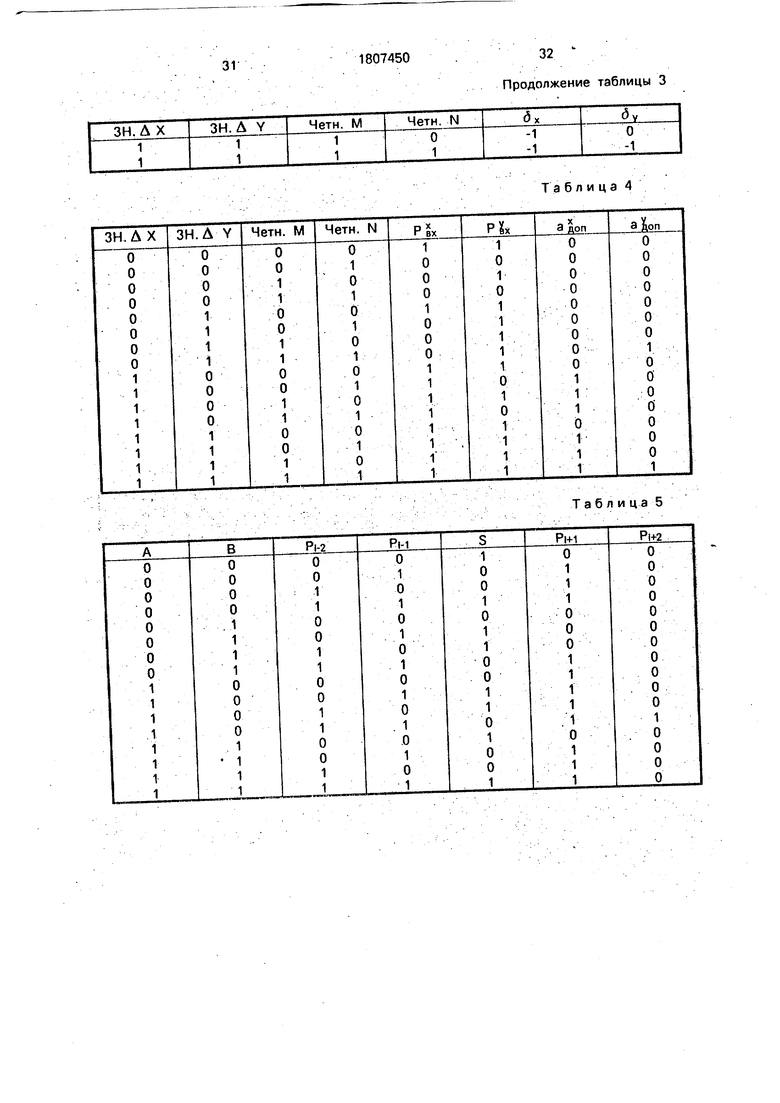

В табл. 4 по содержимому табл.3 представлены значения сигналов РВх и dAon в зависимости от четности M,N и их знаков для координат X и Y.

Рассмотрим процесс составления табл.4 на конкретном примере (фиг.6,б).

Координаты точки be для рассматриваемого случая равны (6,2), а точки а - (7,2). Определим рассогласование по оси X. Для этого необходимо произвести вычитание от значения 6 значения 7. Вычитание будем

производить в дополнительном коде.

.Двоичный код значения 6 равен 0110, а обратный код значение 7 - 1000. Для получения дополнительного кода необходимо к последнему значению добавить 1, Получим

1001, Определим сумму:

0110

1001

1111

25

Из последнего результата следует, что для получения нулевого результата необходимо добавление еще одной единицы в младший разряд.

Из приведенного примера получаем, что при результате, равном 1, необходимо добавление единицы, т.е. адол 1. При этом Рвх тоже должно быть равно 1,

Рассмотрим еще один пример (фиг.8,6).

Абсцисса точки be равна 8, а точки а - 7, Определим д х, для чего к прямому коду числа 8 прибавим дополнительный код числа 7,

40

0110

1001

1111

Полученное выражение - ненулевое. Для его достижения, очевидно, нужно входной перенос принять равным 0, т.е. выполнить вычитание в обратном коде. Покажем это. Действительно, обратный код числа 7 равен 1000. Производим вычитание:

1000

1000

0000

что и необходимо.

Аналогично определяются значения адоп и Рвх для остальных случаев.

По табл.4 проведем синтез схем для формирования сигналов РВх и адоп. для чего составим карты Венча.

Pgx 3 Н ДХ -2 Мх - 2 N

ЗН,ДХ+2МТ 2 М ЗНДУ

3 ЛХ

2М

-2N-

0

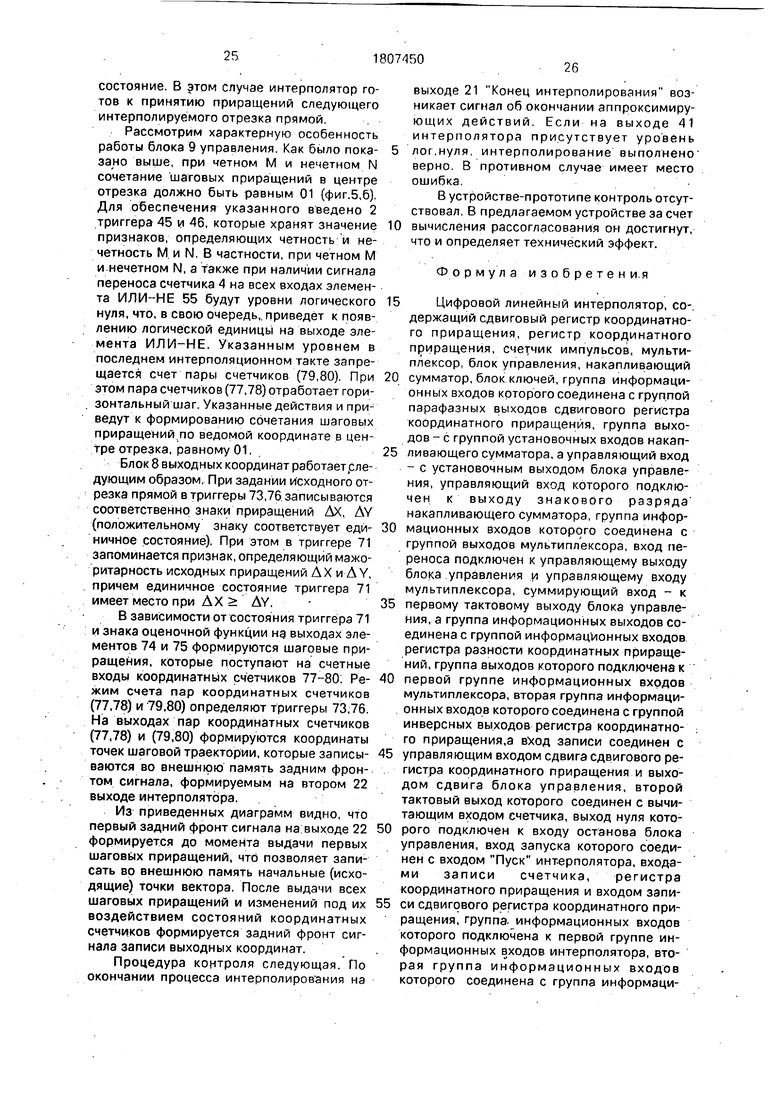

га разряда шины Xi или YI, для чего также составим карты Венча для значений разницы S и переносов .

S - АВ Pt-iPi-2 + АВ РиР|-2 + АВ .Pi-iPi-2 + АВ Pi-iPi-2 + АВ Pi-iPi-2 + АВ Р|-ГР|-2 + АВ Pl-lPl 2 + AB P|-lPi-2 АВ (РмР1-2 + PI-lPl-2) + АВ (P|-lPl-2 + Pl-lPl-2) + АВ (Pi-iPi-2 + Pi-tPI-2) + АВ (Pj- |Pi-2 + Pi-1 Pi-2) (Pi-lPi-2 + Pi-lPi-2)(AB + AB) + (Pi-iP i-2 + РмРк) (АВ + АВ)

6

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах отображения графической информации, а также в системах с ЧПУ. Цифровой линейный интерполятор обеспечивает контроль процесса интерполирования. Интерполятор содержит сдвиговый регистр координатного приращения, регистр разности координатных приращений, регистр координатного приращения, счетчики, мультиплексор, блок управления, накапливающий сумматор, блок выходных координат, ключ. В предлагаемом устройстве осуществляется встречное формирование шаговой траектории отрезка прямой с начальной и конечной точек. Блок контроля сопоставляет координаты точек траектории, сформированные в последнем интерполяционном такте, Блок контроля осуществляет контроль по завершений цикла интерполяции. На входы поступают значения координат точек аппроксимируемой прямой с выходов блока 8 выходных координат. Если координаты этих точек совпадают соответственно по осям X и У, то на выходе блока контроля появится значение логического О, сигнализирующее о правильности выполнения аппроксимируемых действий. 19 ил.

Pgx 3HAV+2 N

ЗНДУ

ЗН ДХ

I2M

- 2N -

dЈon 3 Н.- ДХ2 М +

+ 3 Н.- ДХ2 N

ЗН ДХ(2 М +2N)

ЗНДУ

-2W- ajjon 3 Н AY2M2N ЗНДУ

ЗН

|гм

-ал/Функциональные схемы, формирующие переносы Р gx (элементы ИЛИ 81,85), Р Јх (элементы НЕ 84 и ИЛИ 87) и сигналы а доп

(элементы ИЛИ 82 и И 86), а &0п(элемент И 83) представлены на фиг. 13 в составе функциональной схеме блока контроля.

По табл.5 проведем синтез схемы одного разряда вычитателя при условии, что в таблице символом А обозначено значение одного разряда шины Х2 или Y2, а символом В обозначено соответственно значение одного разряда шины.Хг или Y2. а символом В обозначено соответственно значение сдви15

A К-,

Pi+1 APi-1 + Pi-2 В + APi-2 + АВ + РЫ Pi-2 20 + Pi-i В А(Ри + Pi 2) + В (Pi-1 + Pi-2) + AB + Pi-1 Pi-2

В

25

A

ft-i

35

Л|

рн

pi-2

Функциональная схема вычитателя представлена на фиг. 17. Поскольку в последнем и предпоследнем разрядах вычитателя значения выходных переносов

5 соответственно Рм, Pi-2 для дальнейших вычислений не нужны, то с целью уменьшения аппаратных: затрат значения этих переносов вообще не формируются. Функциональная схема всех остальных разрядов

0 вычитателя представлена на фиг. 18.

Граф-схема алгоритма работы интерпо- лятора приведена на. фиг. 10. Рассмотрим работу блока 9 управления. Для избежания гонок и состязаний при синтезе блока был

5 использован принцип единой временной организации.

В цикле подготовки в триггерах 45 и 46 передним фронтом сигнала на втором 12 входе интерполятора запоминаются соответственно младшие разряды М и N, которые указывают об четности и нечетности исходных приращений. Нулевым уровнем сигнала на втором 12 входе интерполятора устанавливается в единичное состояние триггер fife, что .запрещает в цикле подготовки работу координатных счетчиков 77-80. Последнее исключает возможные срабатывания указанных счетчиков, например, при переходе триггера 62 из нулевого в единичное состояние. Единичное состояние триггера 62 запрещает прохождение синхроимпульсов.записи выходных координат во внешнюю память, формируемых на выходе элемента 63.

Нулевой уровень сигнала на втором 12 входе интерполятора переводит триггер 60 в нулевое состояние, что приводит к нулевому уровню сигнала на выходе элемента 64. Указанный сигнал является сигнэлом.Конец интерполяции. Передним фронтом сигнала на входе 12 интерполятора (указанным фронтом сигнала разрешается работа интерполятора) устанавливается в единичное состояние триггер43. При появлении после этого переднего фронта сигнала на выходе формирователя импульсов 48 устанавливается в единичное состояние триггер 47, что разрешает прохождение импульсной последовательности от формирователя 48 на выходы элементов 51 и 52, Указанные действия по запуску интерполятора обеспечивают присинхронизирован- ную его работу к переднему фронту импульса от формирователя .48 после поступления сигнала Пуск (передний фронт сигнала на входе 12 интерполятора).

В интерполяторе не предусмотрена начальная установка знакового разряда накапливающего сумматора 7. Карта прошивки узла 42 ПЗУ, приведенная в табл.2., составлена таким образом, чтобы обеспечить правильную работу интерполятора до момента обнуления знакового разряда накапливающего сумматора 7.

Поскольку исходное состояние второго 50 регистра нулевое, то с приходом через элемент 51 первого импульса от формирователя 48 в регистре 49 запомнится первая микрокоманда, имеющая адрес 0000 или 1000 в зависимости от значения знакового разряда сумматора 7. Микрокоманды по указанным адресам идентичны и имеют один и тот же адресный переход (содержимое регистра 50) - 001. Во втором такте, следовательно, будут выполняться микрокоманды с адресами 1001 или 0001, которые также идентичны и имеют адресный переход 010. Во втором такте цикла подготовки из большего приращения вычитается меньшее и, следовательно, знаковый разряд сумматора принимает нулевое состояние.

Дальнейшие переходы производятся всоот-. ветствии с таблицей, представленной на фиг.9, узла 42 постоянной памяти.

Временная работа блока 9 управления.

5 По окончании цикла подготовки (см. граф-схе. му алгоритма работы интерполятора карту

прошивки блока 42 и временную диаграмму

работы интерполятора в цикле подготовки

(фиг. 12) на выходах 69 и 70 регистра 49 уста0 навливается уровень логической единицы, который разрешает прохождение ;импульса на счетчик 4 через элемент 56, на накапливаю- . щий сумматор 7 через элемент 37.

Единичный уровень сигнала на выходе

5 69 первого регистра 49 при единичном уров- - не сигнала на инверсном выходе формирователя импульсов 48 приводит к установке триггера 62 в нулевое состояние. Последнее разрешает прохождение импульсов от фор0 мирователя 48 через элемент ИЛИ 63. Под воздействием импульсной, последовательности на выходе элемента ИЛИ 63 происходит запись выходных координат во . внешнюю память. : .;

С каждым импульсом, формируемым на

0 выходе элемента И 56, содержимое счетчика 4 уменьшается на единицу. После поступления на вычитающий вход счётчика 1м/2.1им- пульсов на его выходе формируется сигнал переноса, который поступает на четвертый

5 25 вход блока 9 управления. При наличии сигнала переноса счетчика (нулевой уровень сигнала) и появлении переднего фронта сигнала на прямом выходе формирователя импульсов 48 триггер 60 ус0 танавливается в состояние логической единицы, что в свою очередь приводит к переводу триггеров 43 и 47 в нулевое.состо- яние, а также обнулению регистров 49 и 50. Нулевое состояние триггера 47 запрещает

5 прохождение импульсов через логические элементы 51 и 52, а нулевое состояние регистра 49 приводит к прекращению передачи импульсных последовательностей через элементы 56,57,58. Про цесс интерполяции

0 отрезка прямой закончен, однако для обеспечения записи последних выходных приращений во внешнюю память предусмотрена установка триггера 62. В единичное состоят ние только передним фронтом следующего

5 синхроимпульса от формирователя импульсов 48. Процесс интерполяции и запись выходных приращений закончены. Об этом .сигнализирует единичный уровень сигнала на выходе элемента 64 И, который появляется при установке триггера 60 и 62 в единичное

состояние. В этом случае интерполятор готов к принятию приращений следующего интерполируемого отрезка прямой.

Рассмотрим характерную особенность работы блока 9 управления. Как было показано выше, при четном М и нечетном N сочетание шаговых приращений в центре отрезка должно быть равным 01 (фиг.5,6). Для обеспечения указанного введено 2 триггера 45 и 46, которые хранят значение признаков, определяющих четность; и нечетность М. и N. В частности, при четном М и.нечетном N, а также при наличии сигнала переноса счетчика 4 на всех входах элемента ИЛИ-НЕ 55 будут уровни логического нуля, что, в свою очередь,, приведет к появлению логической единицы на выходе элемента ИЛИ-НЕ. Указанным уровнем в последнем интерполяционном такте запрещается счет пары счетчиков (79,80). При этом пара счетчиков (77,78) отработает горизонтальный шаг. Указанные действия и приведут к формированию сочетания шаговых приращений по ведомой координате в центре отрезка, равному 01.

Блок 8 выходных координат работаетрле- дующим образом. При задании исходного отрезка прямой в триггеры 73,76.записываются соответственно знаки приращений ДХ, AY (положительному знаку соответствует единичное состояние). При этом в триггере 71 запоминается признак, определяющий мажо- ритарность исходных приращений АХ и Л Y, причем единичное состояние триггера 71 имеет место при АХ AY.

В зависимости от состояния триггера 71 и знака оценочной функции на выходах элементов 74 и 75 формируются шаговые приращения, которые поступают на счетные входы координатных счетчиков 77-80; Режим счета пар координатных счетчиков (77,78) и 79,80) определяют триггеры 73,76. На выходах пар координатных счетчиков (77,78) и (79,80) формируются координаты точек шаговой траектории, которые записываются во внешнюю память задним фронтом сигнала, формируемым на втором 22 выходе интерполятора.

Из приведенных диаграмм видно, что первый задний фронт сигнала на: выходе 22 формируется до момента выдачи первых шаговых приращений, что позволяет записать во внешнюю память начальные (исходящие) точки вектора. После выдачи всех шаговых приращений и изменений под их воздействием состояний координатных счетчиков формируется задний фронт сигнала записи выходных координат.

Процедура контроля следующая. По окончании процесса интерполирования на

выходе 21 Конец интерполирования возникает сигнал об окончании аппроксимирующих действий. Если на выходе 41 интерполятора присутствует уровень

лог.нуля, интерполирование выполнено верно. В противном случае имеет место ошибка. В устройстве-прототипе контроль отсутствовал. В предлагаемом устройстве за счет

вычисления рассогласования он достигнут, что и определяет технический эффект.

Формула изо брете ни.я

Цифровой линейный интерполятор, со-, держащий сдвиговый регистр координатного приращения, регистр координатного приращения, счетчик импульсов, мультиплексор, блок управления, накапливающий

сумматор, блок ключей, группа информационных входов которого соединена с группой парафазных выходов сдвигового регистра координатного приращения, группа выходов - с группой установочных входов накапливающего сумматора, а управляющий вход - с установочным выходом блока управления, управляющий вход которого подключен к выходу знакового разряда накапливающего сумматора, группа информационных входов которого соединена с группой выходов мультиплексора, вход переноса подключен к управляющему выходу блока .управления и управляющему входу мультиплексора, суммирующий вход - к

первому тактовому выходу блока управления, а группа информационных выходов соединена с группой информационных входов, регистра разности координатных приращений, группа выходов которого подключена к

первой группе информационных входов мультиплексора, вторая группа информационных входов которого соединена с группой инверсных выходов регистра координатного приращения.а записи соединен с

управляющим входом сдвига сдвигового регистра координатного приращения и выходом сдвига блока управления, второй тактовый выход которого соединен с вычитающим входом счетчика, выход нуля которого подключен к входу останова блока управления, вход запуска которого соединен с входом Пуск интерполятора, входами записи счетчика, регистра координатного приращения и входом записи сдвигового регистра координатного приращения, группа, информационных входов которого подключена к первой группе информационных входов интерполятора, вторая группа информационных входов которого соединена с группа информационных входов регистра координатного приращения, вход начальной установки блока управления является входом начальной установки интерполятора, а также блок формирования выходных координат, первый и второй знаковые входы и управляющий вход которого являются соответственно, первым, вторым знаковыми и управляющим входами интерполятора, первая и вторая группы информационных выходов блока формирования выходных координат является первой и второй группами информационных выходов интерпо- лятора.первый и второй тактовые входы которого соединены, соответственно, с третьим и четвертым тактовыми выходами блока управления, первый и второй входы запрета соединены соответственно с первым и вторым выходами запрета блока управления, выход Конец интерполирования и выход записи которого являются, соответственно выходом Конец интерполирования и стробирующим выходом интерполятора, третья и четвертая группы информационных входов интерполятора подключены соответственно к первой и второй группам информационных входов блока формирования выходных координат, первый и второй установочные входы которого являются, соответственно первым и вторым установочными входами интерполятора, а вход записи соединение входом Пуск интерполятора, первый и второй информационные входы блока управления подключены, соответственно к младшим разрядам первой и второй групп информационных входов интерполятора, (при этом, i -и разряд(, п-1) группы инфор- йационных входов счетчика соединен с ( разрядом первой группы информационных входов интерполятора, где п - разрядность этой группы, отличающийся тем, что, с целью повышения надежности интерполятора путем организации контроля, в него введен блок контроля, выход которого подключен к пятому выходу интерполятора, третий и четвертый входы которого соединены, соответственно, с первым и вторым входами блока контроля, третий и четвертый входы которого подключены соответственно, к выходу четности и нечётности исходных приращений блока управления, первая и вторая

группы входов блока контроля соединены, соответственно, с первой и второй группами информационных выходов блока формирования выходных координат, при этом блок

контроля содержит четыре элемента ИЛИ, два элемента И, инвертор, элемент ИЛИ- НЕ, первый и второй вычитатели, первый и второй блоки выделения нулевого состояния, выходы которых подключены соответственно, к первому и второму входам первого элемента ИЛИ, выход которого соединен с выходом блока контроля, первый вход которого подключен к вторым входам второго элемента ИЛИ, первого элемента И,

выход которого соединен с дополнительным входом младшего разряда первого вы- читатёля, выходы которого подключены, соответственно, к входам первого блока вы- деления нулевого состояния, второй вход

блока контроля соединен с третьим входом второго элемента И и с вторым входом третьего элемента ИЛИ, выход которого подключен к входу переноса второго вычитателя, выходы которого соединены, соответственно с входами второго блока выделения нулевого состояния, первая и вторая группы информационных входов второго вычитателя подключены соответственно к группе входов первой и второй

групп входов блока, дополнительный вход младшего разряда вычитателя соединен,с выходом второго элемента И, второй вход которого подключен к третьему входу блока контроля, первому входу элемента ИЛИНЕ, первому входу четвертого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, четвертый вход блока контроля подключен к второму входу элемента ИЛИ-НЕ, второму входу четвертого элемента ИЛИ, первому входу второго элемента И, входу инвертора, выход которого соединен с первым входом третьего элемента ИЛИ, вход переноса первого вычитателя подключен к выходу второго

элемента ИЛИ, первый вход которого соединен с выходом элемента ИЛИ-НЕ, первая и вторая группы информационных входов первого вычитателя подключены соответственно к группе входов первой и второй

групп входов блока контроля.

Таблица 1

Та б л и ц а 2

ТаблицаЗ

Продолжение таблицы 3

Та блица 4

Т а б л и ц а 5

У/i

Fl

/

/t м tfJti9

51 JTf

i.

г

2Г

JO

№ Л

зе

зг

33

34

sf

35Г

39

A

4J

SI

Zi

Фс/г.

Ш

Л

Э С

ъ с

О

I

t,x

4

& 44

G- 4f

Г

25

г

k5

C D

Фчг г

/

ь

35

2e

Xr

f

23

T

#ar..f

jftS .

m

еь

II

т

&Г..Г

3S

V C

во

.

fl/ 3 , 7 / J // Л

..

Фиг.5

6 Jo

b 6c

±f is

( |)|- Лч

Ф ,

S4

fyeaw 79,/С

Фиг. 9

Фиг.18в

%

Ч

ъ

и

4

| Способ прогнозирования течения послеоперационных гнойно-воспалительных осложнений | 1988 |

|

SU1629847A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-04-07—Публикация

1991-04-02—Подача