ОС

00 со

О)

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1272271A1 |

| Преобразователь переменного напряжения в цифровой код | 1977 |

|

SU741452A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Аналого-цифровой Фурье-преобразователь | 1980 |

|

SU966886A1 |

| Автоматический регулятор компенсирующего устройства | 1990 |

|

SU1704145A1 |

| Формирователь импульсов | 1981 |

|

SU1030963A1 |

| Аналого-цифровой Фурье-преобразователь | 1980 |

|

SU938391A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Частотный дискриминатор | 1984 |

|

SU1241142A1 |

ФАЗОЧУВСТВИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД, содержащий . измерительный частотный прео6разова тель, реверсивный счетчик импульсов и блок управления, отличающийся тем, что, с целью упрощения конструкции и увеличения чувствительности, в него введены постоянный запоминающий блок и цифровой сумматор, выходы которого соединены с входами реверсивного счетчика импульсов, причем выход измерительного частотного преобразователя соединен с входной клеммой запуска цифрового , информационные входы которого соединены с выходами постоянного запоминающего блока, а блок управления соединен своими выходами с цифровым сумматором и постоянным запоминаюпдам блоком. (Л С

tf. 7

Изобретение относится к электрлческим измерениям в диапазонах :1Нфранизких и звуковых частот, предназначено для преобразования в цифровой код составляющей переменного напряжения, синфазной первой гармонике опорного сигнала, и может быть использовано при экспериментальном определении амплитудно-фазовых частотных характеристик четырехполюсников, при акустических измерениях, исследованиях в области систем автоматического управления и регулирования, в геофизике, биофизике, океанологии и т.д.

Известен цифровой анализатор, в котором используется преобразование Фурье для определения интегральных характеристик низкочастотных сигналов, в частности их квадратурных ком .понент t ОНедостатком указанного устройства является сложность его функциональны узлов.

Метрологические характеристики анализатора приемлемы, если его умножитель оперирует с 50-разрядными двоичными числами. Построение подобного цифрового умножителя для экономи-;лого полевого прибора трудно осу|цествить даже при использовании современной микроэлектрониой базы. Усложняет устройство также и наличие в его составе высокоточного аналогоцифрового преобразователя.

Известен фазочувствительный преобразователь напряжение - код, в котором осуществляется промежуточное прев)ащение входного сигнала в частоно-модулированную импульсную после-Q довательность, содержащий измерительный частотный преобразователь, реверсивный счетчик импульсов, блок управления, отсчетное устройство, делитепь частоты, включенный между измерительным частотным преобразователем и реверсивным счетчиком импульсов, блок управления, содержащий элемент ИЛИ, элементы совпадений и соединенные последовательно триггерные ячейки, выходы которых соединены с элементами совпаденийj причем один из входов какдого элемента совпадения соединен .с соответствующим выходом делителя частоты а выходы элементов совпадения - с элементом ИЛИ, выход которого соединен со счетным входом реверсивного счетчика импульсов, вход управления последнего соединен с выходом последней триггерной ячейки узла управления.

Преобразователь вырабатывает цифровой код, пропорциональный скалярному произведению векторов входного напряжения и опорного сигнала. Вектор коммутации R(Sii| устройства кусочно-постоянная нечетная функция времени.

G помощью данного преобразователя можно выбирать длительности интервалов постоянства ) и относительные величины ее ступеней для уничтожения паразитных полос пропускания системы на частотах заданных гармоник преобразуемого напряжения 23.

Однако известное устройство отличается сложностью и малой чувствительностью.Усложняет устройство наличие в нем делителя частоты с переменным коэффициентом деления, который относительно различных выходов должен равняться 2, 8794; 1, 5321; 1, 1371 и 1,0000. При этом делитель частоты должен содержать наряду с собственно делителями еще и широкодиапазонные умножители частоты, что усложняет преобразователь в целом.

Малая чувствительность устройства проявляется при исключении из делителя частоты умножителей частоты. В этом случае коэффициенты пересчета делителя могут быть 9, 5 и А. Система с подобным делителем частоты имеет чувствительность в 4 раза меньшую потенциальной чувствительности, определяемой крутизной модуляционной характеристики используемого в устройстве измерительного частотного преобразователя.

Цель изобретения - упрощение конструкции и увеличение чувствитель-,: ности.

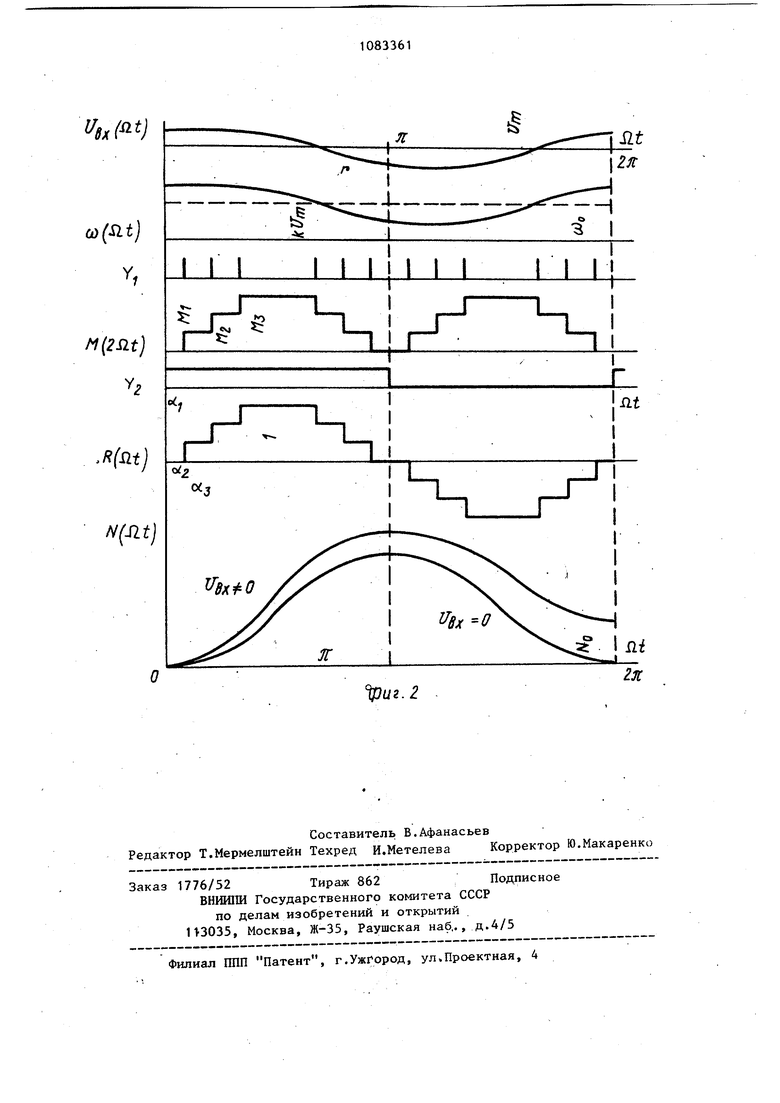

Поставленная цель достигается тем, что в фазочувствительный преобразователь напряжение-код, содержащий измерительный частотный преобразователь, реверсивный счетчик импульсов и блок управления, введены постоянный запоминающий блок и цифровой сумматор, выходы которого соединены с входами реверсивного счетчика импульсов, причем выход измерительного частотного преобразователя соединен входной клеммой запуска цифрового умматора, информационные входы коорого соединены с выходами постоян-, ого запоминакнцего блока, а блок управления соединен своими выходами с сумматором и постоянным запоминающим блоком. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 временные диаграммы его работы. Устройство .содержит входную клемму 1 обрабатываемого сигнала, клемму 2 сброса, измерительный частотный преобразователь 3, постоянный запоминающий блок 4, блок 5 памяти с последовательной выборкой, регистр 6, цифровой сумматор 7, входную клем му 8 запуска цифрового сумматора, входную информационную клемму 9 сумматора,.входную управляющую клемму 10 сумматора, блок 11 управления, ре версивньй счетчик 12 импульсов и выходную клемму 13-. Входная клемма 1 соединена с входом измерительного частотного преобразователя 3, выход которого соединен с клеммой 8 сумматора. Клемма 2 сброса соединена с входами сброса 1щфрового сумматора 7, реверсивного счетчика 12 и блока 11 управления. Первый вь1ход блока 11 управления соединен с входом блока 5 памяти выход которого соединен с входом регистра 6, выходом соединенного с входной информационной клеммой 9 сумматора 7. Второй выход блока 11 соединен с входной управляющей клеммой 10 сумматора. Выход переполнения сумматора 7 соединен с входом суммиг рования реверсивного счетчика 12, а выход заема - с входом вычитания. Источник обрабатываемого напряжения (не показан) через: измерительный частотный преобразователь 3 соединен с входом Запуск цифрового сумматора 7, информационные клеммы 9 которо го через регистр 6 подключены к блоку 5. Выходы сумматора 7 подсоединен к входам счетчика 12. Блок 11 управления потенциалами Y и 2 своих выходов задает режимы работы блока 4 и сумматора 7. Перед началом цикла преобразования (при ) производится сброс счетчика 12, сумматора 7 и счетчиков блока 11 в нулевое состояние. В это время на клемме 1 присутствует обрабатываемое напряжение (ftt+ где и„. и Я - соответственно амплитуда и круговая частота, а f - сдви фазы этого напряжения относительно первой гармоники сигнала У (фиг.2) вырабатываемого блоком 11. С помощью 1 1 преобразователя 3 входное напряжение преобразуется в последовательность импульсов с частотой w(52t) uiot U 5in{5 4 4). где Юр и k - соответственно центральная частота и крутизна модуляционной характеристики измерительного частотного преобразователя (фиг.2). На вход блока 5 памяти подводится сигнал управления Y (фиг.2). По каждому импульсу из блока 5 выводится очередной операнд М., который запоминается в регистре 6 на интервал времени, заканчивающийся с приходом следующего импульса Y, . Временная зависимость кода М (2Sli ), подаваемого на информационные входы сумматора 7, иллюстрируется соответствующей эпюрой (фиг.2). На графике функции M(2flt) символами М., М- и М обозначены относительные величины ее ступенек. Фазовые углы ai , об, и cL отвечают моментам скачкоЬ этой функции. Для одной из модификаций преобразователя ,4450; М 0,8019; Мэ 1,0000 и об, 5-, 0,. 5-, 5,, 5Л/14. . V3 В качестве сумматора 7 используется реверсивный цифровой сумматор накапливающего типа. По каждому Импульсу, генерируемому преобразователем 3 и поступающему на вход Запуск сумматора 7, последний производит алгебраическое суммирование кода, присутствующего на его информационных входах, с собственным содержимым, накопленным к этому моменту времени. Режимы работы сумматора 7 задаются потенциалом Y (фиг.2) блока 11. При Y2 логическая 1 цифровой сумматор работает в режиме суммирования, а при Y2 логический О - в режиме вычитания. Импульсы переполнения сумматора 7, возникающие на одном из его выходов при суммировании, подводятся к входу суммирования счетчика 12. Импульсы переполнения сумматора 7, работающего в режиме вычитания, поступают на аналогичный вход счетчика 12, свыхода которого снимается код, пропорциональный искомой компоненте входного напряжения, синфазной первой гармонике управляющего потенциала .Y/ или первой гармонике вектора коммутации R(()/(Y2-Y2) преобразователя, где Y2 - продукт

, $10833616

инверсии сигнала Yj . Эпюра R( преобразуется мнимая составляющая представлена на фиг,2.входного сигнала N (0,508/Й )«

Содержимое N(Sli I счетчика 12 . Ч .

изменяется в соответствии Таким образом, предлагаемая систес интегралом i 5 ма осуществляет фазочувствительное

N( u(flt|ft(SJt . преобразование переменного напряжения в цифровой код. Введение в ее состав

При оговоренных вьше значениях М -М тора позволяет упростить фазочувстви ступеней функции M 2Sl-t) и величинах О тельный преобразователь и увеличить углов dL.o( разложение в ряд Фурье ; его чувствительность по сравненшб с вектора коммутации имеет следукяций прототипом. Упрощение достигается завид: меной уникального, сложного и громоздR(Slt) «1,0176inS t- TS Sin 13Sli- TC переменным козффициентом деления . . подходящим типовым ци(|фовым сумматол S1 г IJ лет т # I,,, ,

„.ром из ряда ЦС, выпускаемых в виде

В этих условиях результат фазочув-g,. Запоминаю;ее устройство реалиствнтельного преобразования первой например, на нескольких корпугармоники входного сигнала мультиплексоров - переключателей

2f/flСИС и не усложняет систему в целом.

N М/ Э4-1/+- /О ГУказанные отличия позволяют уве0 1« l/t-/ /ii r , I jtWjj+ Uj sinitяичить чувствительность преобрааова Отеля, так как величину, например,

/СЭ4. ш1 сэ JA 0508 . (фиг. 2) можно всегда положить

x iiCt+fJJsinSZtdtz- kOj COSV . ,равной единице и свободно задать треВысшие гармоники обрабатываемого на-функции M(2Si) без учета ограничений,

пряжений с но1«ерами 3-11, 17-25 икоторые накладывает структура делитеТ.Д., которые могут присутствовать в золя частоты прототипа. Для модификасоставе Ugx(.t) . не создают погреш-ции известного устройства, делитель

нести преобраэования, так как соот частоты которого имеет коэффициенты

ветствующие спектральные компонентыпересчета 9,5 и А, величина М сос разложении дпя ,,R(Slt) равнытавляёт лишь 1/4, что приводит к

нулю.- J,уменьшению его чувствительности в

При сдвиге функции М(2ЯО и потен-4 раза по сравнению с предлагаемым

V2 на время 7f/2 S2 в код N устройством.

запоминающего блока и цифрового сумма. кого нестандартного делителя частоты

значения-других ступеней Us,(t) a)(t) I Г I 11 Li I НГ -LJr,. f1(2Sit) H ./(litj /(Slt) Xft(7 Ч. / 1 1 Ill I J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смеляков В.Б., Гартштейн Б.Н | |||

| Шевченко А.В | |||

| Вероятнея оценка интегральных характеристик периодического сигнала | |||

| - Приборы и систеWI управления, 1981, № 11, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ФАЗОЧУВСТВИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД | 0 |

|

SU409366A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-03-30—Публикация

1982-10-25—Подача