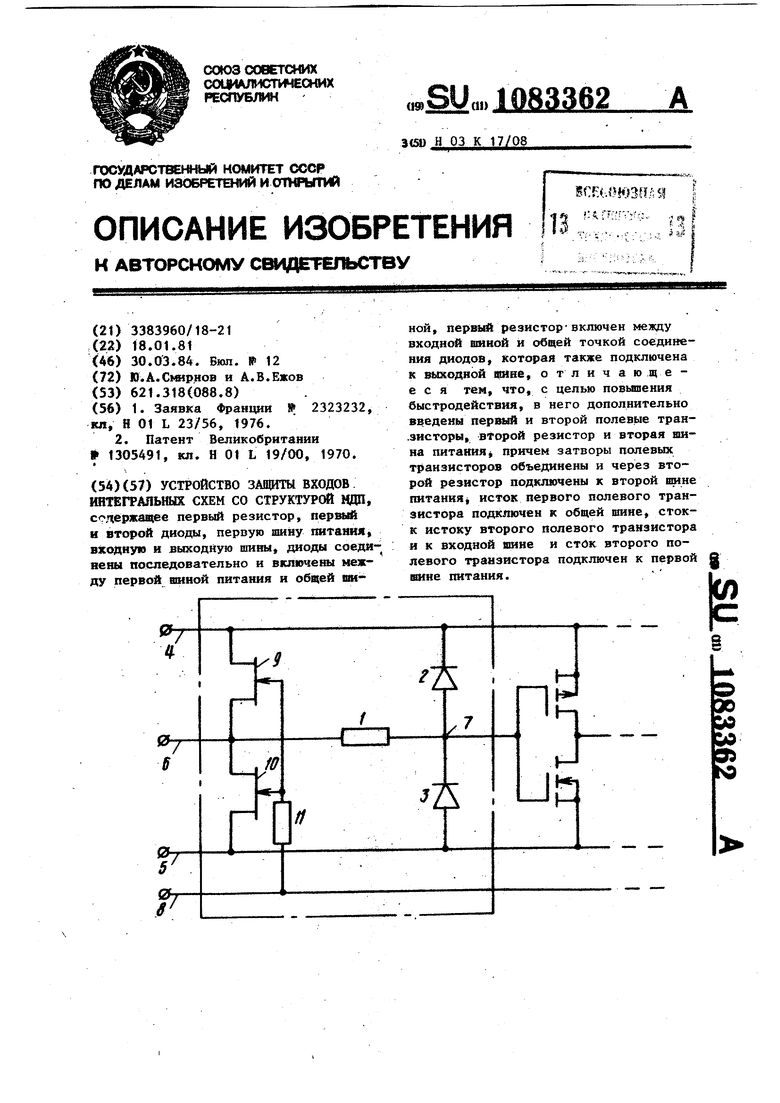

Изобретение относится к полупроводниковой электроникп, в частности к интегральным схемам на ЦДЛ-структу рах, и может быть использовано для защиты их входов от перенапряжения. Известно устройство защиты входов МДП ИС от перенапряжения, состоящее из двух каскадов. Первый содержит две шунтирующие цепи лля различных величин входного напряжения и дополнительный резистор с большим сопротивлением, второй каскад содержит шунтирующую цепь в виде МДП-транзистора с толстым окислом и дополнитель ный резистор с большим сопротивлениемОднако в связи с тем, что устройство имеет на входе резисторы большо го номинала, его функциональные возможности ограничены областью примене ния для микросхем низкого быстродействия. Известно устройство защиты входов МДП интегральных схем от перенапряже ния, включающее резистор, соединенны с двумя последовательно соединенными диодами, которые соединены один - с первой шиной питания, а второй - с общей шиной, свободный конец резисто ра соединен с входной шиной. Устройство может применяться для быстродей ствующих микросхем С 2. Однако известная схема обладает инерционностью, в результате чего при попадании на вход интегральной схеме высокого потенциала статического электричества вероятность пробо подзатворного окисла резко увеличива ется. Цель изобретения - повьш1ение быстродействия устройства. Поставленная цель достигается тем, что в устройство защиты входов интегральных схем со структурой МДП, содержащее первый резистор, первый и второй диоды, первую шину питания, входную и выходную шины, причем диоды соединены последовательно и включены между первой шиной питания и об щей шиной, первый резистор включен между входной шиной и общей точкой соединения диодов, которая также под ключена к выходной шине, дополнитель но введены первый и второй полевые транзисторы, второй резистор и вторая шина питания, причем затворы полевых транзисторов объединены и через второй резистор подкгючрчы к второй шине питания, исток первого полевого транзистора подключен к общей шине, сток - к истоку второго полевого транзистора н к входной шине и сток второго полевого транзистора подключен к первой шине питания. На чертеже приведена Схема устройства. Устройство содержит первый резистор 1, соединенный с двумя последовательно соединенными диодами 2 и 3. Первый диод 2 соединен с первой шиной питания 4, второй диод 3 с общей шиной 5. Один вывод первого резистора 1 соединен с входной шиной 6, а второй - с выходной шиной 7. В устройстве предусмотрена вторая шина питания 8, два полевых транзистора 9 и 10, Исток первого транзистора 9 соединен со стоком второго транзистора 10 и с входной шиной 6. Сток транзистора 9 соединен с первой шиной питания 4, а исток транзистора 10 соединен с общей шиной 5. Затворы транзисторов 9 и 10 соединены между собой и с второй шиной питания 8 через второй резистор 11. Устройство работает следующим образом. В исходном состоянии полевые транзисторы 9 и 10 открыты. При возникновении положительного напряжения статического электричества на шине 4 по отношению к шине 6 транзисторы 9 и 10 открыты. Таким образом, между этими шинами возникает проводимость через открытый канал полевого транзистора 9 и запертый диод 2. Ток разряда определяется в основном сопротивлением открытого канала полевого транзистора 9 до момента в емени, когда наступит пробой диода 2, после чего ток разряда будет определяться сопротивлением открытого транзистора 9 и сопротивлением первого резистора 1. Так как эти сопротивления одного порядка, ток разряда через цепь резистора 1 и транзистор 9 также Одного порядка до момента времени, когда напряжение статического электричества не станет равным пробивному напряжению; тогда диод запирается и ток разряда протекает только через сопротивление отк-. крытого канала полевого транзистора 9. При возникновении отрицательного напряжения статического электричества на шине 4 по отношению к шине 6 транзисторы 9 и 10 также отпираются таким

образом, что между этими шинами возникает проводящая цепь через транзистор 9, открытый диод 2 и первый резистор 1. Таким..образом, ток разряда определяется сопротивлением открытого j канала транзистора; 9 до момента времени,, когда начнет проводить диод 2 (откроется в прямом направлении), тогда ток перераспределится и будет определяться цепочкой из параллельно ю включенных сопротивлений, составленных

из последовательных сопротивлений резистора и открытого диода, и сопротивлением открытого канала.

При перенапряжениях, возникающих на входной шине 6 относительно общей шины 5, аналогично работают полевой транзистор 10 и диод 3.

Второй резистор 11 служит для ограничения тока разряда через полевые транзисторы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ ИНТЕГРАЛЬНЫХ СХЕМ СО СТРУКТУРОЙ МДП ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2005 |

|

RU2308146C2 |

| ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2014 |

|

RU2560822C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КНС (КРЕМНИЙ НА САПФИРЕ), КНИ (КРЕМНИЙ НА ИЗОЛЯТОРЕ) СТРУКТУРАХ | 2011 |

|

RU2467431C1 |

| Устройство автоматического смещения | 1981 |

|

SU995673A1 |

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ МИКРОСХЕМЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2012 |

|

RU2523115C1 |

| СХЕМА УПРАВЛЕНИЯ ПОСЛЕДОВАТЕЛЬНЫМ КЛЮЧОМ НА МДП-ТРАНЗИСТОРЕ | 2006 |

|

RU2312456C1 |

| ОДНОТАКТНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2009604C1 |

| Триггер с раздельными входами | 1978 |

|

SU746874A1 |

| Высоковольтный электронный ключ | 2024 |

|

RU2837267C1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

УСТРОЙСТВО ЗАВИТЫ ВХОДОВ. ИНТЕГРАЛЬНЫХ СХЕМ СО СТРУКТУР(Ш НДП, содержащее первый резистор, первьй и второй диоды, первую шину питания« вх(едиую и выходную шины, даюды соединены последовательно и включет между первой яшной питания и общей ittiной, первь резистор-включен между входн шиной и общей точкой соединения диодов, которая также подключена к выходной щиве, отличающееся тем, что, с целью пов1лоения быстродействия, в него дополнительно введены первый и второй полевые тран.зисторы, второй резистор и вторая шина питания причем затворы полевых транзисторов объединены и через второй резистор подключены к второй вшне питания исток первого полевого транзистора подключен к общей шине, стокк истоку второго полевого транзистора и к входной огане и сток второго полевого транзистора подключен к первой шине питания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УДАРОПРОЧНАЯ МОРОЗОСТОЙКАЯ КОМПОЗИЦИЯ ПОЛИПРОПИЛЕНА | 2006 |

|

RU2323232C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ газообеспечения объекта с неравномерным потреблением хладагента и устройство для его осуществления | 1985 |

|

SU1305491A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-03-30—Публикация

1981-01-18—Подача