(54) ТРИГГЕР С РАЗДЕЛЬНЫМИ ВХОДАМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер на мдп-транзисторах | 1977 |

|

SU641633A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| @ - @ -Триггер | 1982 |

|

SU1034154A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

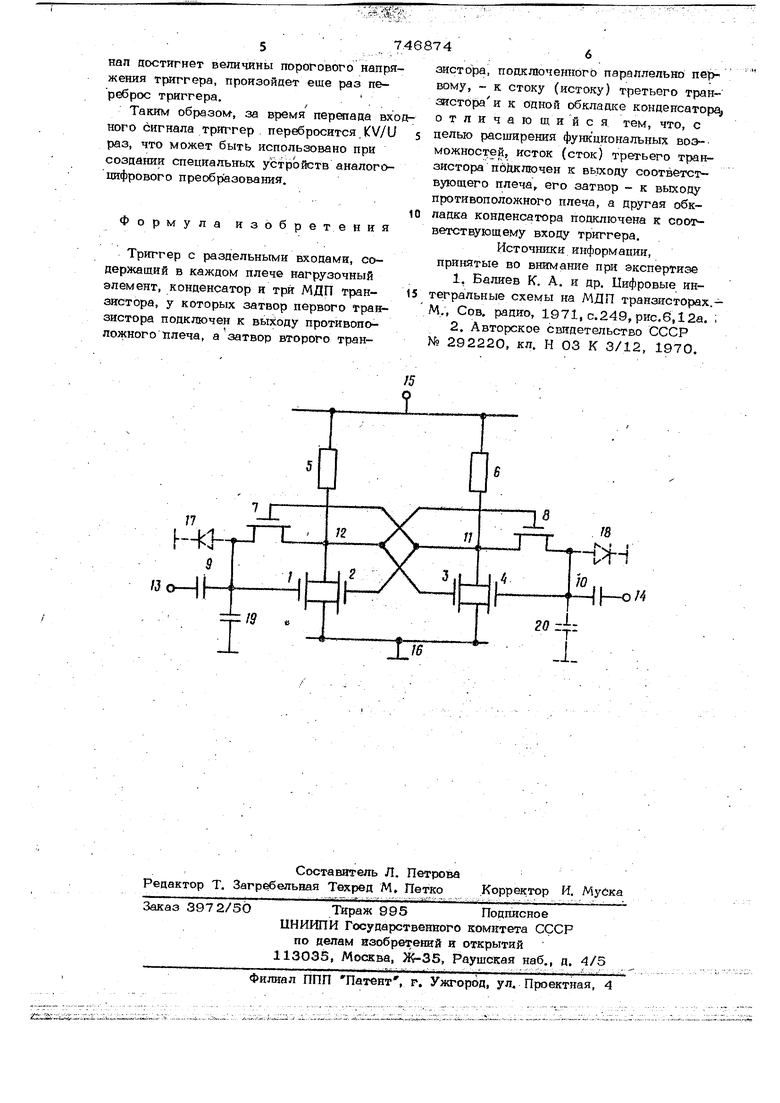

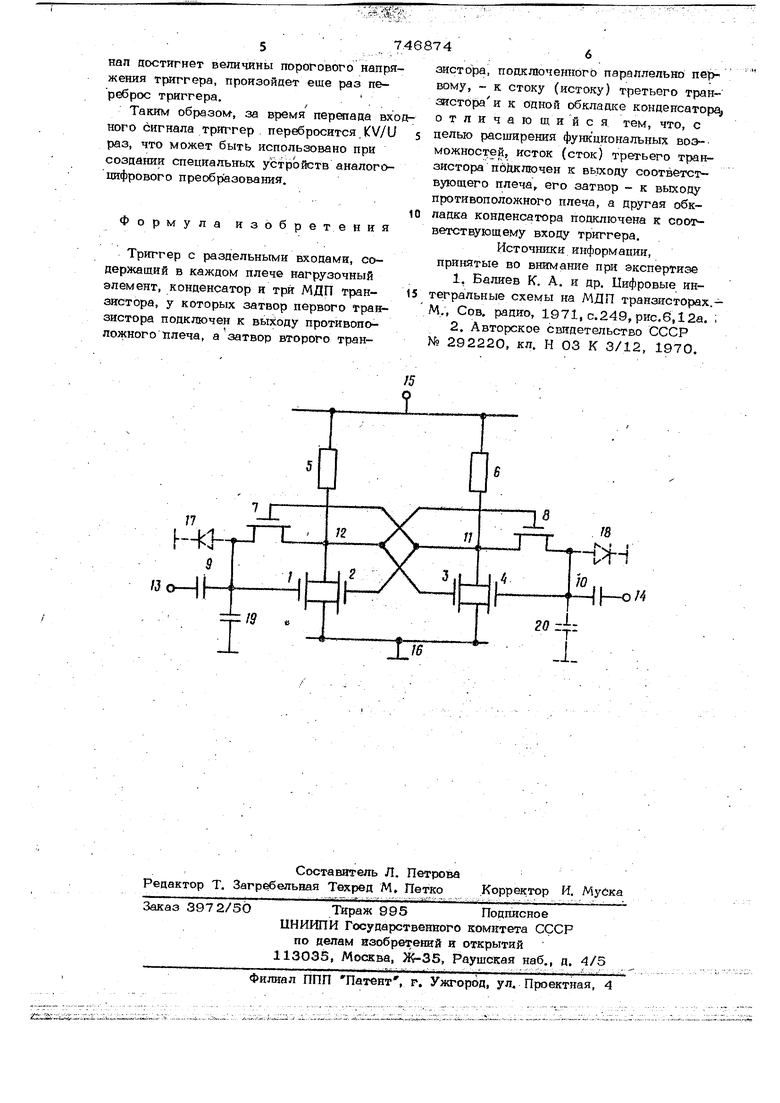

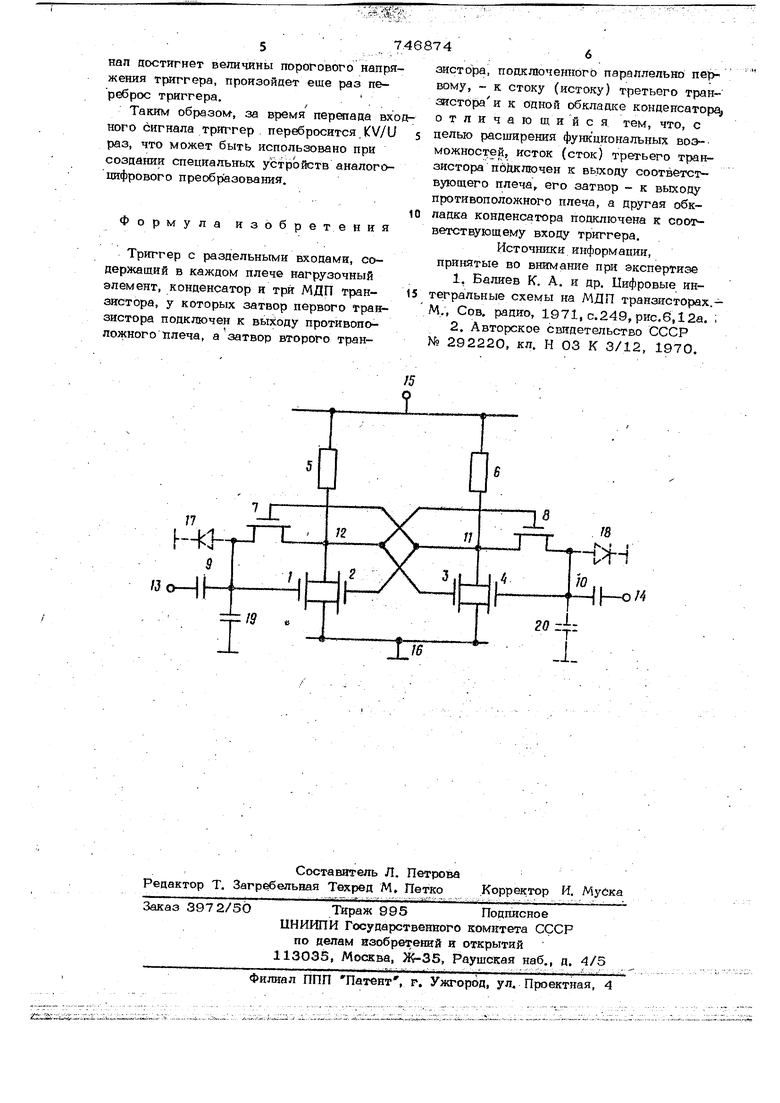

. -. . ,Г, Изобретение относится к области вычяспйтепьной техника и может быть и6йопьзовано при построении элементов и узлов на интегральных МДП микросхемах для ш1фровЬ1х вычкспительных машин Известен триггер на полевых МДП транзисторах с индуцированным каналом, содержащий в каждом плече два параллельно соединенных переключающих МДП транзистора и нагрузочный МДП транзистор 1 , Недостаток такого устройства - ограниченные функциональные возможности, что при построении бистабильных схем (счетчиков, регистров и т. д.) на ос- : нове триггера с раздельными входами пр водят к значительному усложнению схемы за счет увеличения количества элементов, необходимых для реализации соответ стщющих функций возбуждения триггера, увеличению мощности за счет потребления тока в этих цепях. Наиболее близким к предложенному Триггеру является триггер в раздельныМИ входами, содержащий в каждом плече нагрузочный элемент, конденсатор и три МДП транзистора, затвор одного из транзисторов подключен 1C Ыз1ходу противоположного плеча; затвор второго транзистора, подключенного параллельно первому;к стоку (истоку) третьего транзистора и к одной обкладке конденсатора. Исток (сток) третьего транзистора подключен к общей шине, его затвор - к соответствующему логическому входу схемы. Другая обкладка, конденсатора подключена к другому логическому входу триггера 2. Недостаток этого триггера - ограниченные функциональные возможности, свя-. занные с требованием обязательного разделения во времени входных сигналов, подаваемых на каждый из входов триггера. Цель изобретения - расширение функциональных возможностей триггера. Для достижения этого в триггере с раздельн 1ми входами, содержащем в каждом плече нагрузочный элемент, конденсатор и три МДП транзистора, у которых 3„.7 затвор первого транзистора подключен к выходу противоположного плеча, а затвор второго транзистора, подключенного параллельно первому - к стоку (истоку) третьего транзистора и к одной обкладке конденсатора, истозк (сток) третьего Tpai . погшлючен к выходу сбйт1вётствую .щаО плеча, его затвор - if выходу противоположного плеча, а другая обкладка кон денсатора подключена к соответствующему Входу триггера. На чертеже представлена электрическая принципиальная схема триггера с раз дельными входами, В каждом плече триггера имеется двух ахоДовый НЕ-ИЛИ, образованн:ь1й двумя параллельно включенными транзисторами 1 и 2 (3 и 4)и последовательно вклзвэченным нагрузочным элементом 5 (6 Затвор транзистора 1(4) подключен к стоку (истоку) третьего транзистора 7(8 и одной обкладке конденсатора 9 (10), Затворы транзисторов 2(3) н 7(8) пощсл tjeHbi к выходу 11(12) противоположного плеча триггера. Исток (сток) транзистора 7(8) подключен к вьисоду 12(11) соот- ветствующего плеча триггера. Другая о6кМдка конденсатора 9(10) п 9дЙШчена к входу 13(14) триггера. Нагрузочный элемент 5(6) подключен к шине питания 15,истоки транзис оров 1 и 2 (3 и 4) подключены к общей щине 16. ПоМйией 17(18) обозначен диод стокового (истокового) перехода транзистора 7 (8), а позицией 19(20) - узловая емкость входа плеча триггера относительно общей шины -16.;.-- --V-:-.Г . .,.. ..- ..:... Триггер работает следующим образом. Предположим, что висходном состоягши на в ыходе 12 уровеньнапряжения с6от |Е 6т :твуёт уровйю напряжения логической; единицы, на выходе 11 - урбвшоЖН|®жения логическогону ля, йа входы 13 и 14 триггера и на затворы транзистск ров 1 и 4 поступает напряжение, соответствующее напряжению логического «trjTCT , . . . njr 4ДЛ,, .. .,, ..,-. -.,. -.--;..l. .,--.-1. посту(плении на вход 13 триггера напряжения логической бдйнйцырнб через емкостный делитель (конденсатор 9, емкость 19) передается на затвор транадстора 1. Если уровень напряжешш на затворе транзистора 1 окажется .болыие порога срабатывания триггера, произойдет переброс Tpurrispa в другое состояние, при котором на выходе 1 i ус.тайовится состояние логической единицы iijpa этом транзистор 7 откроется, и че- , 74 рез опсрытые транзисторы 7 и 2 емкость 19 разрядится. Поэтому после завершения переходных процессов на затворах транзисторов 1 и 4 установится нулевей уровень напряжения, .даже в том случае, если входной сигнал на входе 13 останется равным напряжению логичес- кой единицы. При поступлении навход 14 напряжения логической единицы аналогично описанному произойдет переброс триггера висходное состояние, при этом обе емкости 19 и 20 разрядятся. Поскольку в интегральном исполнении параллельно узловым емкостям 19 и 20 включены диоды 17, 18 стоковых (иотоковых) переходов транзисторов 7 и 8 соответственно, обратный перепад напряжения вх одного сигнала при нулевых У{э6ёНЯх напряжения на этих емкостях не приводит к появлению уровней напряжения противоположной полярности в указайных точках. . Таким образом, триггер срабатывает от перепада уровней напряжения входного сигнала напряжение логическрго нуля напряжение логической единицы и не требует разделения во времени входных уровней напряжения. Обозначим перепад напряжений входного сигнала - V , коэффициент емкостных делителей (конденсатор 9, 19 и конденсатор 10, емкость 20) и порог срабатывания транзистора 1(4) -U . Тогда при KV и данная схема выполняет функции триггера с раздельными входами, срабатывающего от перепада входного сигнала и не имеощего запретной комбинаций входных сигналов. Кроме того, при объединении входов 13 и 14 и вьтолнении условия схема вьшолняет функции счетного триггёр/а.-, -- : . Предположим, что триггер установлен в исходное состояние. Так как транзисторы 8 и 3 открыты, то при иэменегши входного сигнала от уровня, соответстуюшегО уровню напряжения логического уля, до уровня, соответствующего уровю напряжения логической единицы, сохраяется нулевой уровень напряжения на атворе транзистора 4 и увеличивается ровень напряжения на затворе транзисора 1. После переброса триггера происодит разряд узловой емкости 19 через ткрывшиеся транзисторы 7 и 2. Поэтому ри дальнейшем изменении входного сигала будет сохраняться нулевой уровень апряжения уже на затворе транзистора . и когда на затворе т|эанзистора 4 сигнал достигнет величины порогового напря жения триггера, произойдет еше раз переброс триггера.. Таким образом-, за время переттада вхо ного сигнала триггер перебросится KV/U раз, что может быть использовано при создании специальных устройств аналого-цифрового преобразования. Формула изобретения Триггер с раздельными входами, содержащий в каждом плече нагрузочный элемент, конденсатор и три МДП транзистора, у которых затвор первого транзистора подключен к выходу противоположного плеча, а затвор второго тран6зистора, подключенного параллельно первому, - к стоку (истоку) третьего транзистора и к одной обклаш е конденсатора, о т л и ч а го 1Д и и с я тем, что, с целью расширения функцяональных воэможностей, исток (сток) третьего транзистора пЬйкпючен к вьтходу соответствующего плеча, его затвор - к выходу противоположного плеча, а другая обкладка конденсатора подключена к соответствующему входу триггера. Источники информации, принятые во внимание при экспертизе 1.Балиев К. А. и др. Цифровые интбГральные схемы на МДП транзисторах,- М;, Сов. радио, 1971, 0.249, рИс.6,12а. ; 2.Авторское свидетельство СССР № 292220, кл. Н 03 К 3/12, 1970.

Авторы

Даты

1980-07-05—Публикация

1978-01-04—Подача