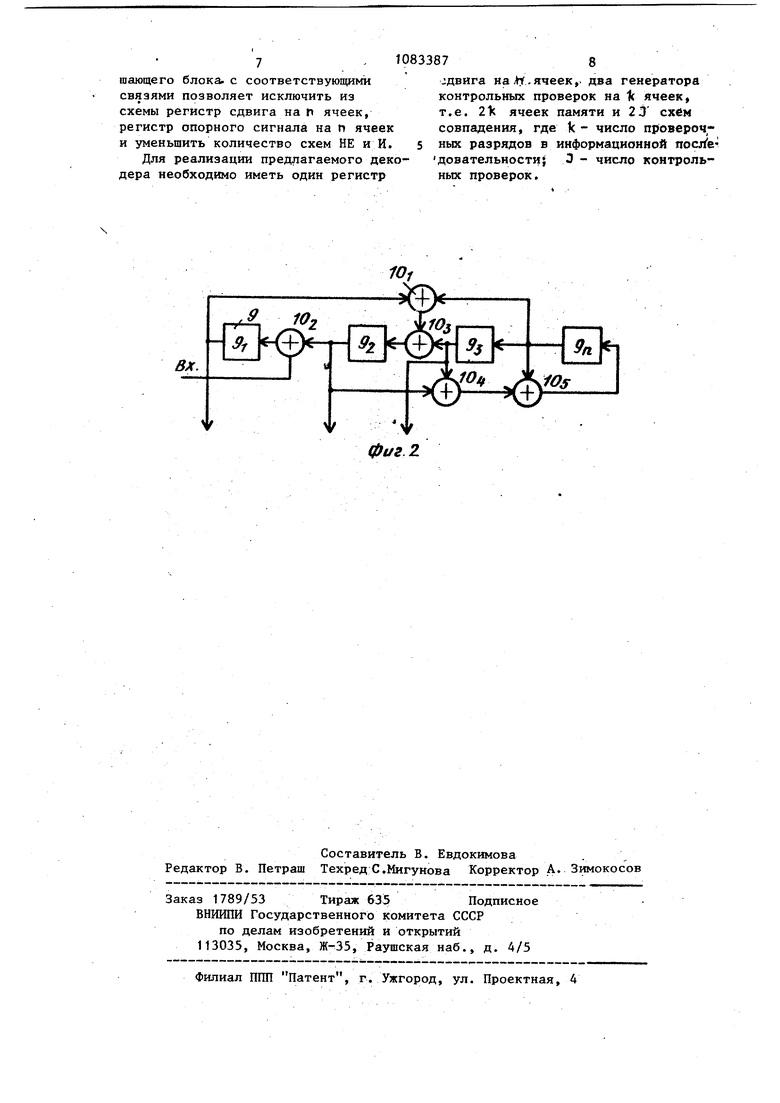

2 РУ Изобретение о тйосится к радиотех нике и может использоваться в аппар туре передачи данных по каналу с по хами. Известен декодер циклического кода с исправлением стираний, содержащий регистры, информационными и стираний с цепями об ратной связи, блок кодирования-корректйрующегокрд сумматор, по модулю 2, элементы Запрет, рекуррентный датчик и выходной регистр сдвига, подключенный к одному из входов элемента И, к BTQpofty входу которого и к входу датчика разрешающего импульса подключен триггер, кроме того, между входами информационного регистра и блока кодирования коррекТирукицего кода и входами сумматора по модулю 2 включены элементы Запрет, а между вйходами сумматора по модул 2 и входом триггера включены последовательно соединенный дополнитепьн триггер и элемент И, причем к вторы входам элементов Запрет подключен регистр стираний, а к выходам блока кодирования корректирующего кода и выходного регистра сдвига подключ , рекуррентный датчик через дополните ный регистр сдвига 1 3Недостатком данного устройства является сложность регистров, кодирующего блока и рекуррентного датчика, входящих в состав устт ройства. Наиболее близким к предлагаемому является декодер для циклического кода с исправлением ошибок и стираНИИ, содержащий блок разделения комбинаций, первый выход которого подключен к входу регистра сдвига, а также мажоритарные блоки, кольцевой регистр сдвига, элементы НЕ, выходы разрядов регистра сдвига, соответствующие нулевым позициям опорньк комбинаций кодовых колец, соединены с первыми входами первых элементов И, а выходы разрядов регистра сдвига, соответствующих единичным позициям опорных комбинаций, соединены с первыми входами первых элементов И через элементы Н выходы разрядов кольцевого регист; ра; сдвига соединены с вторыми входами первых элементов И, выходы первьк элементов И соединены с входами пороговых элементов 23 Недостатком известного устройства является сложность реализации кольцевых регистров сдвига. Цель изобретения - упрощение feeкодера путем исключения кольцевьк регистров сдвига. Для достижения поставленной цели в декодер циклического кода с исправлением ошибок и стираний, содержащий блок разделения комбинаций, первый выход которого подключен к входу регистра сдвига, а также мажоритарные блоки, введены генератор контрольных проверок Стирание, генератор контрольных проверок Ошибка, Сумматор по модулю два и решающий блок, при этом первый и второй выходы блока разделения комбинаций подключены соответственно к входам генератора контрольных проверок Ош1Йбка и генератора контрольных проверок Стирание, выходы разрядов которых подключены к соответствующим входам решающего блока, выхода которого через первый мажоритарный блок подключены к одному из входов сумматора по модулю два, к ДРУ7 гому входу которого подключен выход регистра сдвига, причем выходы разрядов генератора контрольных проверок Стирание через вТорой мажоритарный блок подключены к управляющему входу решакш его блока. Йа фиг.1 представлена электрическая схема декодера циклического кода с исправлением ошибок и стираний на фиг.2 - вариант реализации генератора контрольных проверок. Декодер циклического кода содержит регистр 1 сдвига, блок 2 разделения комбинаций, генератор 3 контрольных проверок Ошибка, генератор 4 контрольных проверок Стирание, первый и второй мажоритарные блоки 5 и -6, решающий блок 7 и сумматор 8 по модулю два. Генераторы 3 и 4 контрольных проверок Ошибка и Стирание для циклического (7,4) с порождающим полиномом 1- состоят из регистра 9 сдвига, число разрядов которого определяется количеством проверочных разрядов и сумматоров lOj по модулю два. Декодер работает следующим образом. Информационная последовательность, закодированная в циклическом коде, поступает на вход блока 2 разделения комбинаций. Работу, декодера разбита на два цикла.В первом цикле происходит запись информации, на втором ее декодирование. При помощи решающего блока 7 осуществляется разделе ние приходящей из линии связи комби нации на две: комбинацию символов 1 и комбинацию ошибок стираний. Решающий блок 7 реализован на двух пороговых элементах. Принятая после довательность записьгоается в регист 1 сдвига, в генератор 3 контрольных проверок Ошибка и в генератор 4 контрольных проверок Стирание , причем в регистр 1 сдвига и в генератор 3 контрольных проверок Ошибк записывается комбинация, у которой стертые позиции заменены нулями, а в генератор 4 контрольных проверо Стирание записывается последовательность, у которой единицы стоят на стертых позициях. После приема информации осуществляется ее декоди рование . С соответствующих выходов генератора 4 контрольных проверок Стирание комбинация поступает на вход второго мажоритарного блока 6 и на входы решающего блока 7. Второй мажоритарный блок 6 выдает единицу на такте, соответствующем стертой позиции. Порог срабатьгоания второго мажоритарного блока 6 определяется исходя из корректирующей способности кода по формуле n , (1) число контрольных провегде 3 рок кода-, число ошибок. О - максимальное число проверо нарушаемых ошибками кратности 5-1. Решающий блок 7 работает следующим образом. . Сигналом управления, определяющим режимы работы решающего блока 7, является сигнал, поступающий на его управляющий вход с выхода второ мажоритарного блока 6. Если второй мажоритарный блок 6 выдает на выход 1, то это означает, что на данной позиции символ кодового елова стерт и требуется его коррекция. В этом режиме решающий блок 7 запрещает подключение контрольных проверок от генератора 4 контрольных проверок Стирание к первому мажоритарному блоку 5 и разрешает подключение контрольных проверок от генератора 3 контрольных проверок Ошибка к первому мажоритарному блоку 5, по которым определяется значение стертого блока. Если.второй мажоритарный блок 6 вьщает на выход О, то это означает, что на данной позиции стирание символа не произошло, и решающий блок 7 осуществляет операцию логического умножения разрядов контрольных проверок генератора 4 контрольных проверок Стирание с соответствующими инверсными разрядами г енератора 3 контрольных проверок Ошибка и подает результат логического умножения к входам первого мажоритарного блока 5. Появление единицы на вькоде первого мажоритарного.блока 5. определяет наличие ошибки на данном такте. Порог срабатывания перво-го мажоритарного блока 5 определяется по формуле n«3-j -e , (2) где 2 -максимальное число проверок, в ; которые входят стёртые символы. .Затем кодовая комбинация, за- писанная в регистре 1 сдвига, складывается по модулю два в сумматоре 8 по модулю два с кодовой последовательностью, поступающей с выхода первого мажоритарного блока. Рассмотрим процесс декодирования принятой ошибочной комбинации на примере. Допустим, что передается комбинздня...0011101 (порождающий полином 1,). Для данного порождающего полинома используется, например, .генератор 3 (4) контрольных проверок, представленный на фиг.2. В процессе передачи кодовой последовательности по каналу с помехами происходит ее искажение. Допустим, первый символ трансформируется из О в 1, а третий символ стирается. В этом случае на вход декодера поступает следующая информационная последовательность 1001101. Тогда на вход генератора 3 контрольных проверок Ошибка, на вход регистра 1 сдвига поступает комбинация 1001101, а на вход генератора 4 контрольных проверок Стирание - 0010000.. Исходя из формул (1) и (2) выбирается порог срабатывания первого и второго мажоритарных блоков 5 и 6 В данном случае порог срабатывания первого мажоритарного блока равен 2, а второго 3, т.е. первый мажоритар$1083387

ный блок 5 выдаес на выходе единичный; а второй мажоритарный блок-6 - при сигнал, если на его входах будут трех единицах. Процесс декодирования присутствовать две и более единиц, представлен в виде таблицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Декодер линейных кодов,исправляющий стирания | 1982 |

|

SU1112554A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2008 |

|

RU2379841C1 |

| Мажоритарное декодирующее устройство | 1975 |

|

SU538502A1 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХ ПАКЕТОВ ОШИБОК | 1965 |

|

SU174207A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1984 |

|

SU1246380A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| СИСТЕМА ИСПРАВЛЕНИЯ СТИРАНИЙ С ЗАЩИТОЙ НОМЕРА КЛАСТЕРА | 2012 |

|

RU2485702C1 |

ДЕКОДЕР ЦИКЛИЧЕСКОГО КОДА С ИСПРАВЛЕНИЕМ ОЙМБОК И СТИРАНИЙ, содер:жащий блок разделения комбинаций, первый выход которого подключен к входу регистра сдвига, а также мажо-. ритарные блоки, отличающи йс я тем, что, с целью упрощения путем исключения кольцевых регистров сдвига, в него введены генератор контрольных проверок Стирание, генератор контрольных проверок Ошибка, сумматор по модулю два и решающий блок, при этом первый и.второй выходы блока разделения комбинаций подключены соответственно к входам генератора контрольных проверок Ошибка и генератора контрольных проверок Стирание, выходы разрядов которых подключены к соответствующим входам решанщего блока, выходы которого через первый мажоритарный блок подключены к одному из входов сумматора по модулю два, к другому входу которого подключен выход регистра сдвига, причем выходы раз- рядов генератора контрольных проверок Стирание через второй мажоритарный блок подключены к управляющему входу решгшщего блока.

Из таблищ) видно, как определяе ся вектор ошибок трансформаций и стираний. Первый мажоритарный блок 5 срабатывает от двух единиц, пост пающих с генератора 3 контрольных проверок Ошибка на 7-sJM такте, тем самым указывая, что на первой позиции присутствует ошибка трансф мации. Второй мажоритарный блок 6 срабатывает от трех единиц, поступающих с генератора 4 контрольных проверок Стирание на 9-.м такте тем самым указывая, что на 3-й позиции присутствует ошибка Стирание , а ее значение определяется по состоянию генератора 3 контроль ных проверок Ошибка. В данном случае на третьей позиции происходит стирание 1. Полученный вектор ошибок складывается по модулю два при помощи сумматора 8 по модулю два с записанной в регистр 1 сдвига кодовой последовательностью. 1001101 +1010000 0011101, На выходе сумматора 8 по модулю два комбинация полностью соответствует передаваемой. Таким образом, декодер осуществляет коррекцию одиночной ошибки трансформации и одиночной ошибки стирания. Включение в схему декодера циклического кода с исправлением ошибок и стираний двух генераторов проверок, сумматора по 1 одулю два, ретающего блока с соответствующими связями позволяет исключить из схемы регистр сдвига на п ячеек, регистр опорного сигнала на п ячеек и уменьшить количество схем НЕ и И. Для реализации предлагаемого Д1еко дера необходимо иметь один регистр 878 сдвига на t.ячеек,, два генератора контрольных проверок на tc ячеек, т.е. 21 ячеек памяти и 23 схим совпадения, где k - число проверочных разрядов в информационной nocjlie довательности; J - число контрольных проверок.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ИСПРАВЛЕНИЯ СТИРАНИЙ | 0 |

|

SU396826A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ДЕШИФРАТОР ЦИКЛИЧЕСКОГО КОДА С ИСПРАВЛЕНИЕМ ОШИБОК И СТИРАИИИ | 0 |

|

SU323778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1980-05-16—Подача