Изобретение относится к технике связи, а именно к устройствам передачи информации с помощью использования циклических кодов.

Целью изобретения является повыше- ние достоверности обрабатываемой информации.

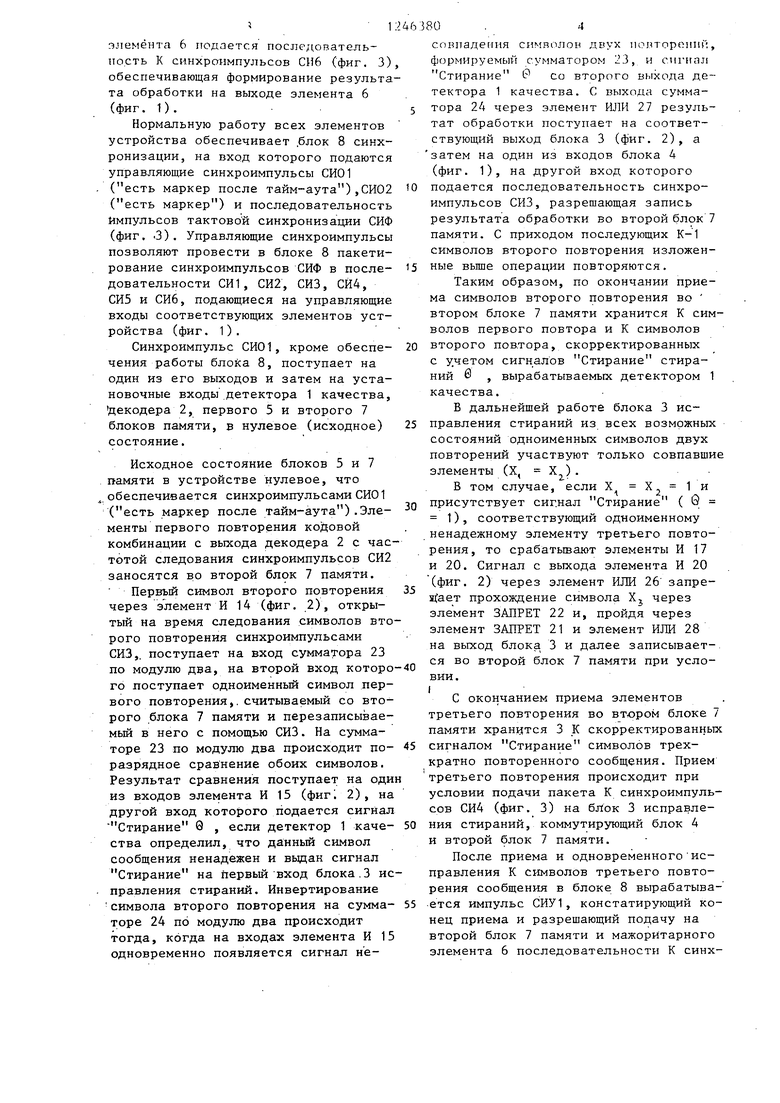

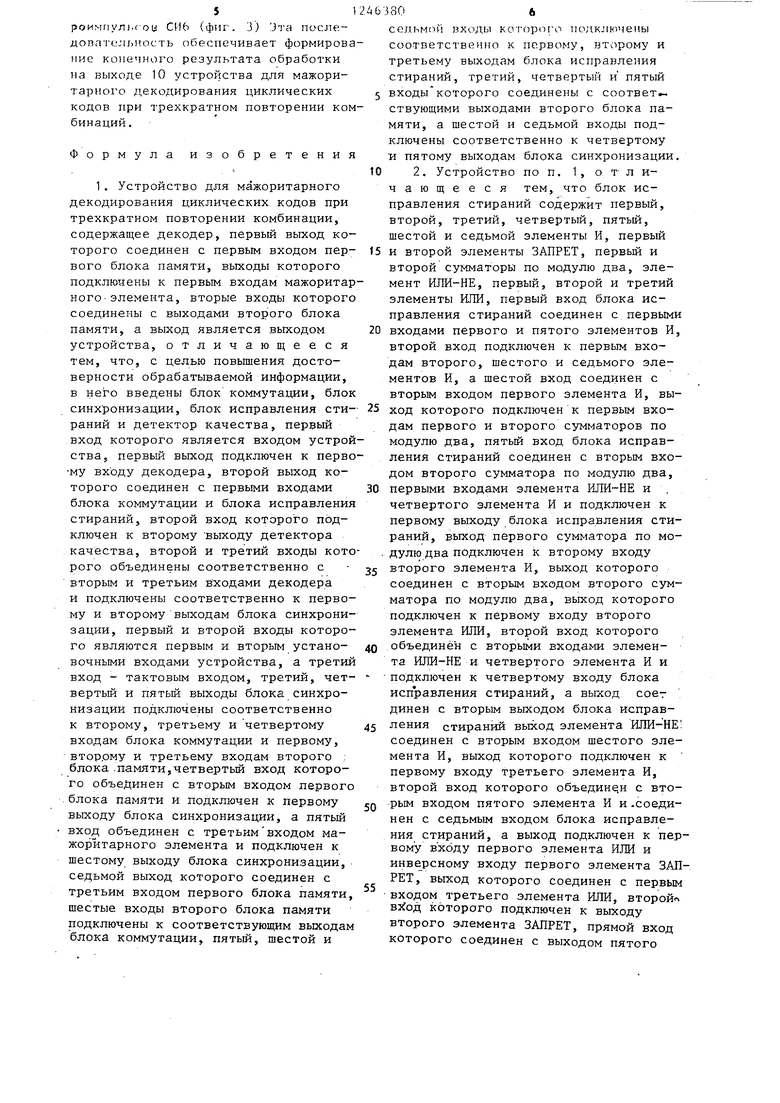

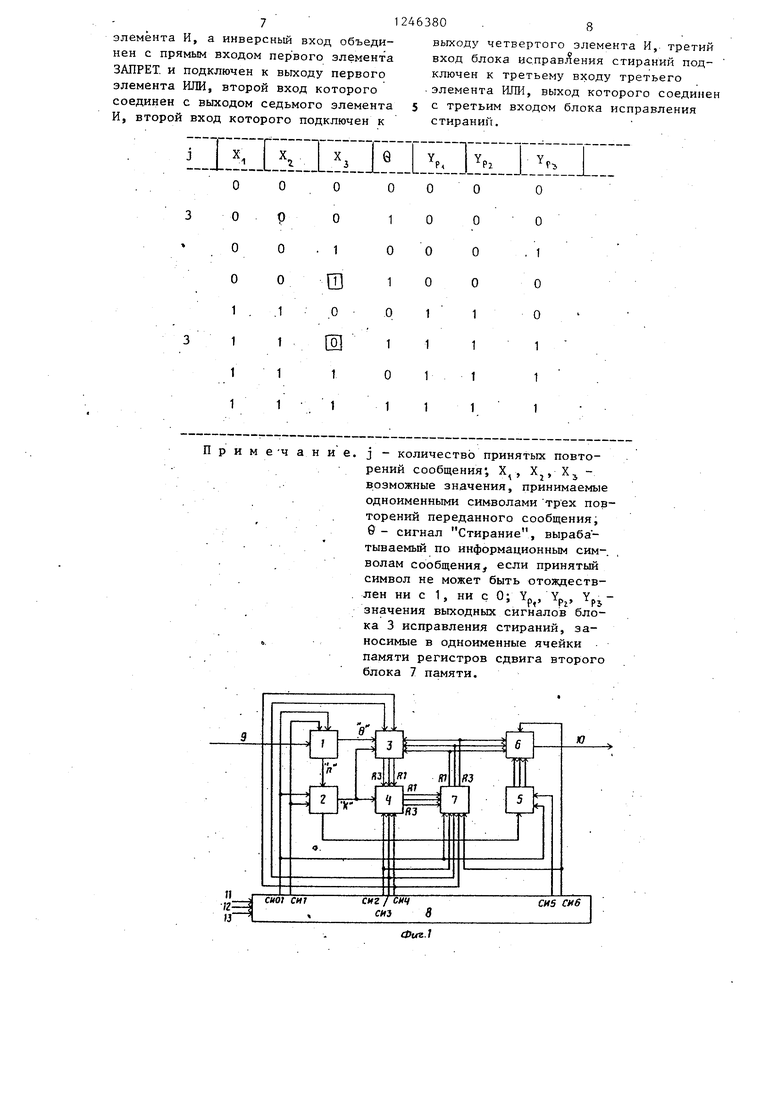

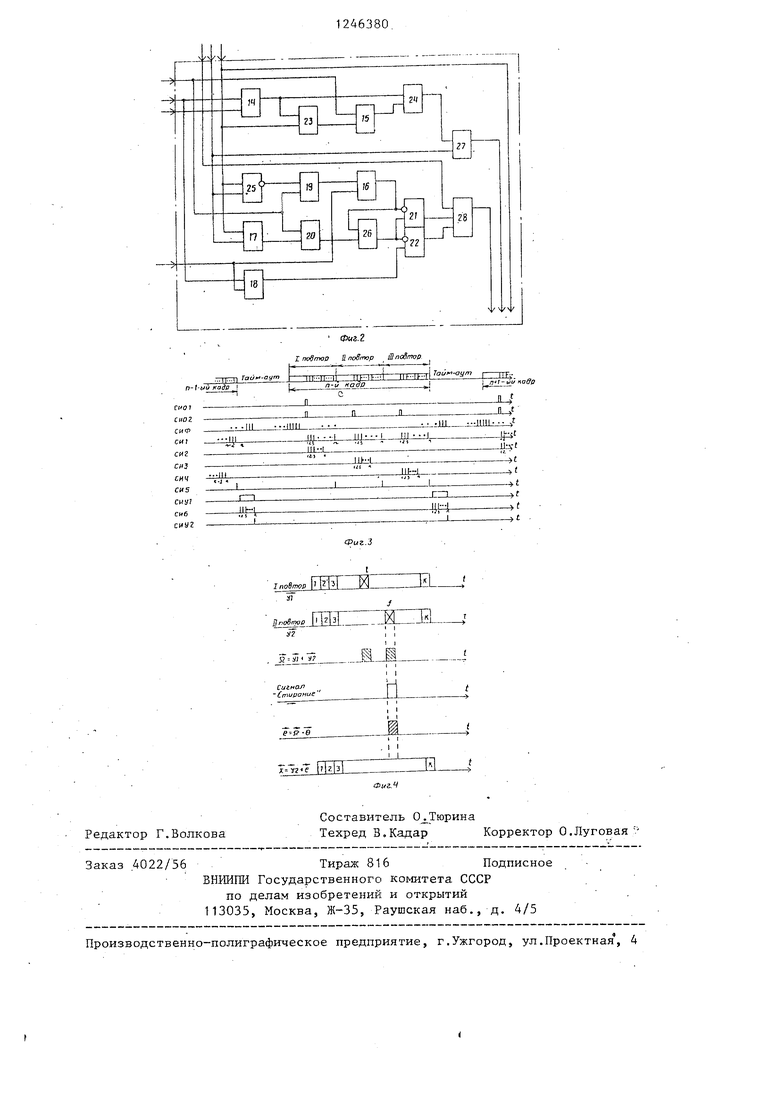

-На фиг. 1 приведена структурная электрическая схема устройства для мажоритарного декодировд.ния циклических кодов при трехкратном повторении комбинации, на фиг. 2 -. функциональная схема блока исправления стираний; на фиг. 3 - временная диаграмма работы устройства, на фиг. 4 - временная диаграмма исправления ошибок во втором повторении при использовании сигналов стир ания.

Устройство содержит детектор 1 качества, декодер 2, блок 3 исправления стираний, коммутирующий блок 4, первый блок 5 памяти, мажоритарный элемент ,6, второй блок 7 памяти, блок 8 синхронизации, вход 9 устройства, выход 10 устройства, первый 11 и вто- ,- рой 12 установочные входы устройства и тактовый вход 13.

Блок 3 исправления стираний содержит семь элементов И 14-20, два элемента ЗАПРЕТ 21 и 22, два сумматора 23 и 24 по модулю два, элемент ИЛИ- НЕ 25, три элемента ИЛИ 26-28.

Детектор 1 качества .предназначен для анализа ка вдого принимаемого (до п включительно) символа кодовой комбинации и вырабатывания сигнала Стирание (0) в том-случае, если принятый символ не может быть отождествлен ни с 1, ни с О,

Работа блока 3 обеспечивается последовательностями синхроимпульсов СИ01 и СИ1 ,(фиг. 3): СИ01 - маркер

после тайм-аут.а является импульсом установки устройства в .исходное состояние.. Он позволяет обнулить все блоки 5 и 7 памяти устройства и разрешает прохождение импульсов тактовой синхронизации (СИФ) на управляющие входы элементов устройства, которые в виде пачек определенной длины, формиру;емых блоком 8, обеспечивают нормальное функционирование.устрой-. ства..

При приеме первого и второго повторения в блоке 3 производится сравнение одноименных символов. При этом учитывается сигнал стирания для соответствующего символа второго повто- ,

рения сообщения, который указывает на искажение данного символа, что позволяет инвертировать искаженный символ во втором повторении (фиг. 4).

При обнар жении ошибки в первом повторении (искаженный символ обозначается крестом) его запоминает (YI). При приеме второго повторения (Y2) фиксируются соответствующие ему стирания О и определяется результат

сложения по модулю два (S ) одноименных символов кодовых векторов Y1 и Y2 . Резуль т ат логического перемножения б с определенной вероятностью указывает на искаженные символы второго повторения, которые инвертируются в соответствии с f. Cкoppeктиpoвaнj aя-комбинация имеет вид X Y2 ® I. Указанные операции над сигналами (фиг. 4) позволяют ос-уществить исправление некоторой доли ошибок во втором повторении сообщения,, закодированного циклическим кодом.

При приеме третьего повторения КОДОЕ1ОЙ комбинации- корректирующая работа блока 3 исправления стираний может быть задана соответствующей таблицей. При этом исправление ошибок в третьем повторении кодовой комбинации производится, если есть сигнал Стирание и предше ствующие одноименные символы двух повторений имеют максимальный код числа еди.ниц или кулевой код.

Мажоритарный элемент 6 работает в одном из следующим режимов, кото- рьй задается кодовой комбинацией результатов декодирования, поступающей с первого блока 5 памяти..

Первый режим работы: если декодер 2 не обнаружил ошибок во всех трех принятых кодовЬк комбинациях, или обнаружил ошибки только в одной кодовой комбинации или во всех трех кодовых комбинациях, то на выходе мажоритарного элемента 6 двоичные символы являются результатом голосования по большинству, на одноименных позициях всех повторений.

Второй режим работы: если декодер 2 обнаружил ошибки в двух кодовых комбинациях, то на выходе мажоритарного элемента 6 появляются символы той комбинации, в которой не обнару- .жен о ошибок.

После приема всех трех повторений сообщений на управляющие входы второ- .го блока 7 памяти и мажоритарного

элемента 6 подается последовательность К синхроимпульсов СИ6 (фиг. 3) обеспечивающая формирование результата обработки на выходе элемента 6 (фиг. 1).

Нормальную работу всех элементов устройства обеспечивает блок 8 синхронизации, на вход которого подаются управляющие синхроимпульсы СИ01 (есть маркер после тайм-аута),СИ02 (есть маркер) и последовательность Импульсов тактовой синхронизации СИФ (фиг. .3). Управляющие синхроимпульсы позволяют провести в блоке 8 пакетирование синхроимпульсов СИФ в после- довательности СИ1, СИ2, СИЗ, СЙ4, СИ5 и СИб, подающиеся на управляющие входы соответствующих элементов устройства (фиг. 1).

Синхроимпульс СИ01, кроме обеспе- чения работы блока 8, поступает на один из его выходов и затем на установочные входы детектора 1 качества, декодера 2, первого 5 и второго 7 блоков памяти, в нулевое (исходное) состояние.

Исходное состояние блоков 5 и 7 памяти в устройстве нулевое, что обеспечивается синхроимпульсами СИ01 (есть маркер после тайм-аута) .Эле- менты первого повторения кодовой комбинации с выхода декодера 2 с частотой следования синхроимпульсов СИ2 заносятся во второй блок 7 памяти.

Первъм символ второго повторения через элемент И 14 (фиг. 2), открытый на время следования символов второго повторения синхроимпульсами СИЗ,, поступает на вход сумматора 23 по модулю два, на второй вход которо го поступает одноименный символ первого повторения,. считываемый со второго блока 7 памяти и перезаписывае- мьш в него с помощью СИЗ. На сумматоре 23 по модулю два происходит по- разрядное сравнение обоих символов. Результат сравнения поступает на оди из входов элемента И 15 (фиг 2), на другой вход которого подается сигнал Стирание 9 , если детектор 1 каче- ства определил, что данный символ сообщения ненадежен и выдан сигнал Стирание на первый вход блока.3 исправления стираний. Инвертирование символа второго повторения на сумма- торе 24 по модулю два происходит тогда, когда на входах элемента И 15 одновременно появляется сигнал несовпадения символен двух понтороиий, формируемый сумматором 23, и сигнал Стирание Р со второго выхода детектора 1 качества. С выхода сумматора 24 через элемент ИЛИ 27 результат обработки поступает на соответствующий выход блока 3 (фиг. 2), а затем на один из входов блока 4 (фиг. 1), на другой вход которого подается последовательность синхроимпульсов СИЗ, разрешающая запись результата обработки во второй блок 7 памяти. С приходом последующих К-1 символов второго повторения изложенные выше операции повторяются.

Таким образом, по окончании приема символов второго повторения во втором блоке 7 памяти хранится К символов первого повтора и К символов второго повтора, скорректированных с учетом сигналов Стирание стираний 0 , вырабатываемых детектором 1 качества.

В дальнейщей работе блока 3 исправления стираний из всех возможных состояний одноименных символов двух повторений участвуют только совпавши элементы (X, X ).

В том случае, если X Х 1 и присутствует сиг.нал Стирание ( Q 1), соответствующий одноименному ненадежному элементу третьего повторения, то срабатьтают элементы И 17 и 20. Сигнал с выхода элемента И 20 (фиг. 2) через элемент РШИ 26 запре- прохождение символа Х через элемент ЗАПРЕТ 22 и, пройдя через элемент ЗАПРЕТ 21 и элемент ИЛИ 28 на выход блока 3 и далее записывается во второй блок 7 памяти при условии.

С окончанием приема элементов третьего повторения во втором блоке памяти хранится 3 К скорректированны сигналом Стирание символов трехкратно повторенного сообщения. Прием третьего повторения происходит при условии подачи пакета К синхроимпульсов СИ4 (фиг. 3) на блок 3 исправления стираний, коммутирующий блок 4 и второй блок 7 памяти.

После приема и одновременного исправления К символов третьего повторения сообщения в блоке 8 вырабатыва ется импульс СИУ1, констатирующий конец приема и разрешающий подачу на второй блок 7 памяти и мажоритарного элемента 6 последовательности К синх$1246

1 оимг|ул).гои СИ6 (фиг . 3) .Зга после- )И(:)сть обеспечивает формирование конечного результата обработки на гзыходе 10 устройства для мажоритарного декодирования циклических кодов при трехкратном повторении комбинаций.

Формула изобретения

1. Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации, содержащее декодер, первый выход которого соединен с первым входом пер- вого блока памяти, выходы которого подключены к первым входам мажоритарного- элемента, вторые входы которого соединены с выходами второго блока памяти, а выход является выходом устройства, отличающееся тем, что, с целью повьшения достоверности обрабатываемой информации, в него введены блок коммутации, блок синхронизации, блок исправления сти- раний и детектор качества, первый вход которого является входом устройства, первый выход подключен к перво му входу декодера, второй выход которого соединен с первыми входами блока коммутации и блока исправления стираний, второй вход которого подключен к второму ВЫХОДУ детектора качества, второй и третий входы которого объединены соответственно с - вторым и третьим в ходами декодера и подключены соответственно к первому и второму выходам блока синхронизации, первый и второй входы которого являются первым и вторым устано- вочными входами устройства, а третий вход - тактовым входом, третий, чет- вертьй и пятый выходы блока синхронизации подключены соответственно к второму, третьему и четвертому входам блока коммутации и первому,

втор.ому и третьему входам второго ; блока.памяти,четвертый вход которого объединен с вторым входом первого блока памяти и подключен к первому выходу блока синхронизации, а пятый вход объединен с третьим входом мажоритарного элемента и подключен к шестому выходу блока синхронизации, седьмой выход которого соединен с третьим входом первого блока памяти, шестые входы второго блока памяти подключены к соответствующим выходам блока коммутации, пятый, шестой и

to

15 20 25 ЗО jj 0 - 5

,„

5

3306

ceitbMOvi ВХОД) кот орого подключены соответственно к первому, второму и третьему выходам блока исправления стираний, третий, четвертый и пятый входы которого соединены с соответ ствующими выходами второго блока памяти, а шестой и седьмой входы подключены соответственно к четвертому и пятому выходам блока синхронизации.

2. Устройство по п. 1, отличающееся тем, что блок исправления стираний содержит первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, первый и второй элементы ЗАПРЕТ, первый и второй сумматоры по модулю два, элемент ИЛИ-НЕ, первый, второй и третий элементы РШИ, первый вход блока исправления стираний соединен с первыми входами первого и пятого элементов И, второй вход подключен к первьм входам второго, шестого и седьмого элементов И, а шестой вход соединен с вторым входом первого элемента И, выход которого подключен к первым входам первого и второго сумматоров по модулю два, пятый вход блока исправления стираний соединен с вторым входом второго сумматора по модулю два, первыми входами элемента и . четвертого элемента И и подключен к первому выходу блока исправления стираний, выход первого сумматора по мо- дулш два подключен к второму входу второго элемента И, выход которого соединен с вторым входом второго сумматора по модулю два, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого объединён с вторыми входами элемента ИЛИ-НЕ и четвертого элемента И и

подключен к четвертому входу блока исп равления стираний, а выход соет динен с вторым выходом блока исправления стираний выход элемента ИЛИ-НЕ соединен с вторым входом шестого элемента И, выход которого подключен к первому входу третьего элемента И, второй вход которого объединен с вторым входом пятого элемента И и .соединен с седьмым входом блока исправления стираний, а выход подключен к первому входу первого элемента ИЛИ и инверсному входу первого элемента ЗАПРЕТ, выход которого соединен с первым

входом третьего элемента ИЛИ, второй вХоД которого подключен к выходу второго элемента ЗАПРЕТ, прямой вход которого соединен с выходом пятого

7 1246380 .8

элемента И, а инверсный вход объеди-выходу четвертого элемента И, третий

иен с прямым входом пер вого элементавход блока исправления стираний под-

ЗАПРЕТ, и подключен к выходу первогоключей к третьему входу третьего

элемента ИЛИ, второй вход которогоэлемента ИЛИ, выход которого соединен

соединен с выходом седьмого элемента5 третьим входом блока исправления

И, второй вход которого подключен кстираний.

11П1-11 Е 1А

П р и м е Ч а н и е.

j - количество принятых повторений сообщения; Х, Х, Х - возможные значения, принимаемые одноименными символами трех повторений переданного сообщения; 0 - сигнал Стирание, вырабатываемый по информационным сим-, волам сообщения, если принятый символ не может быть отождествлен ни с 1, ни с 0; Yp, Yp, значения выходных сигналов блока 3 исправления стираний, заносимые в одноименные ячейки памяти регистров сдвига второго блока 7 памяти.

Фиг.г

Г rjodfnoff и повтор iS подлюр.

-tTFTpif-пглтг -TTFTFT ° п-у кадр

С

11П

mil

.IH

L

ЯЬ

I f 29/wJlIl0LZHZZZI Jil

Ж

; 1

t I

Ж. ЛI

-оут

/7 r-bJt/ р t

-JUf

1Ь,- (

ч J

. (

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| СПОСОБ ОБРАБОТКИ И ПРИЕМНИК СООБЩЕНИЙ ЦИРКУЛЯРНЫХ ОДНОСТОРОННИХ СЕТЕЙ ПЕРЕДАЧИ ДАННЫХ С ПОВТОРЕНИЯМИ | 2016 |

|

RU2643441C2 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

Изобретение oтнocиtcя к технике связи и позволяет по.выеить достоверность обрабатываемой информации. Устройство содержит детектор качества, декодер, блок исправления стираний, коммутирующий блок, первый и второй блоки памяти, мажоритарный элемент, блок синхронизации, вход и выход устройства, первый и второй установочные входы устройства -и тактовый вход. . Блок исправления стираний содержит семь элементов И, два элемента ЗАПРЕТ, два сумматора по модулю два, элемент ИЛИ-НЕ, три элемента ИЛИ. 1 3 . п. ф плы, 4 ил. ю СЛ

Редактор Г.Волкова

Составитель О Тюрина

Техред В.Кадар Корректор 0.Луговая

Заказ 4022/56Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная , 4

| Шварцман B.C | |||

| и Емельянов А.Е | |||

| Теория передачи дискретной информации, -М.: Связь, 1979, с | |||

| Самоцентрирующийся лабиринтовый сальник | 1925 |

|

SU423A1 |

| Гуров B.C., Емельянов А.Е., Етру- хин И.Н | |||

| и Осипов В.Г. | |||

| Передача дискретной информации и телеграфия | |||

| - М.: Связь, 1974, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Аппарат для получения газа под высоким давлением для работы в поршневом или турбинном двигателе | 1922 |

|

SU387A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1978 |

|

SU677123A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-23—Публикация

1984-11-19—Подача