f4i

эо

J

х

00

fS

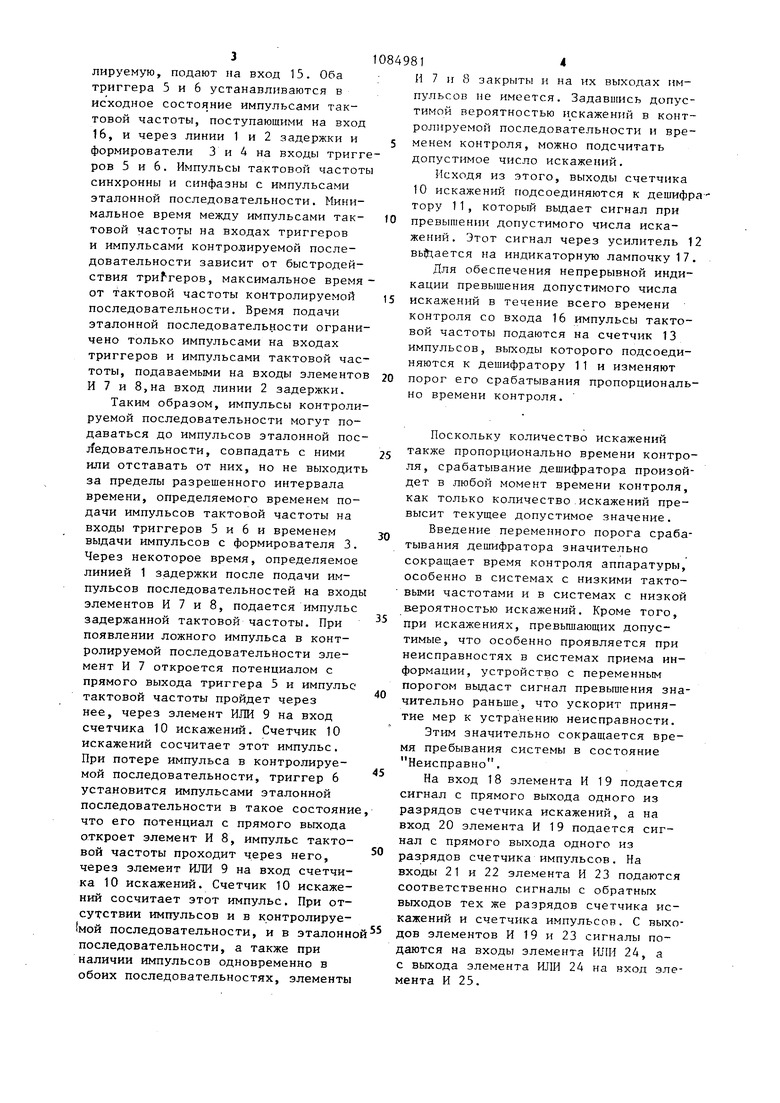

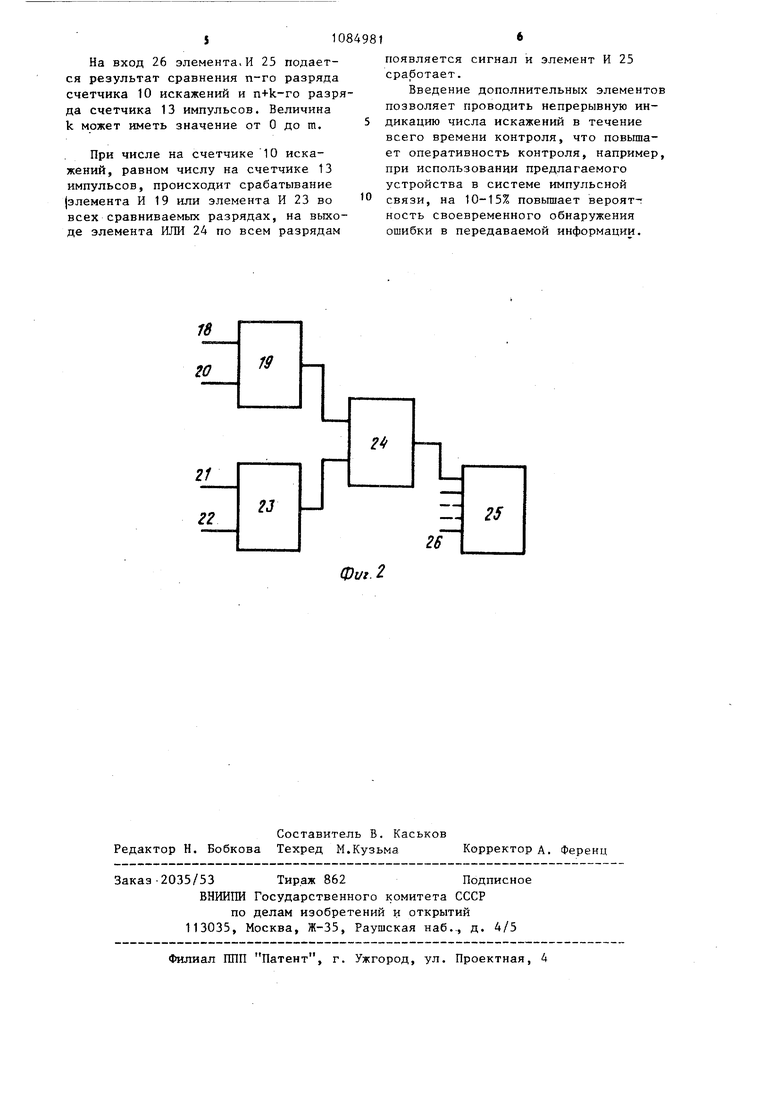

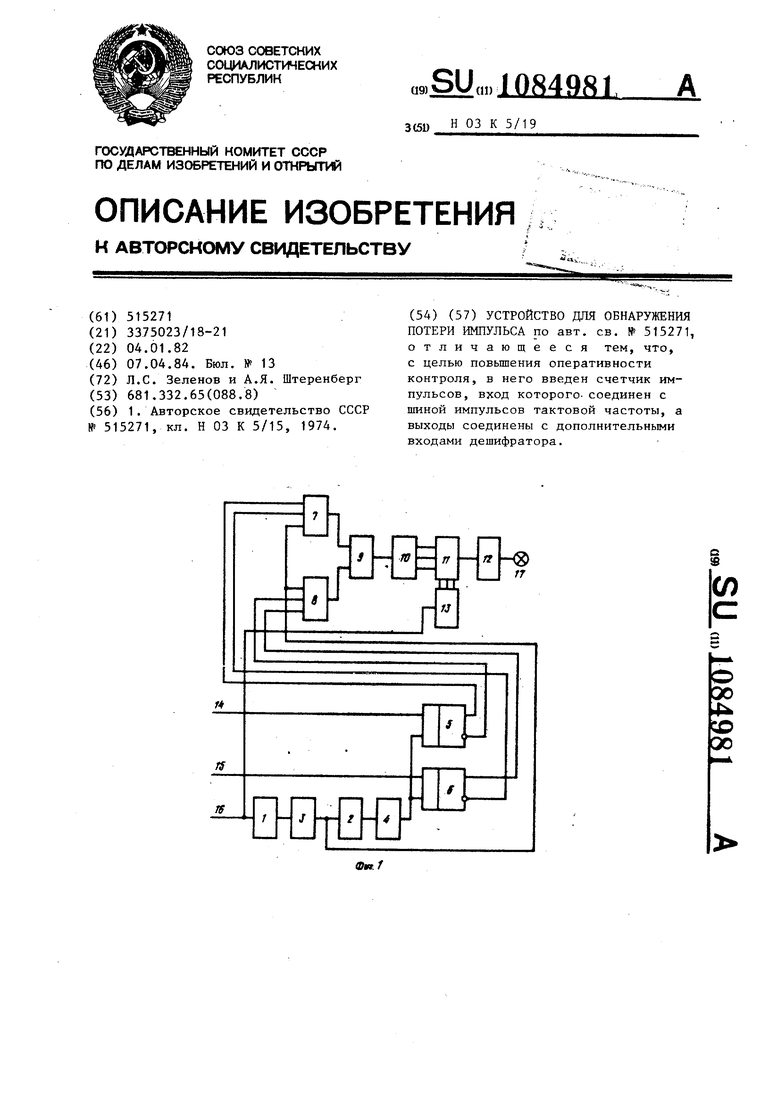

JS Изобретение относится к импульснон технике, а именно к устройствам контроля импульсных последовательностей. По основному авт. св. № 515271 известно устройство для обнаружения потери импульса, содержащее триггер один из входов которого соединен с выходом второго формирователя, а выходы триггера подключены к одним входам логических элементов И, вторые входы которых подключены к выходу первого формирователя, выходы логических элементов И соединены с входами логического элемента ИЛИ, усилитель, две линии задержки, дополнительный триггер, счетчик искажений и дешифратор, причем одна лини задержки подключена к входу первого формирователя, вторая линия задержки включена между первым и вторым форм рователями, один вход дополнительно го триггера подключен к выходу втор го формирователя, на его второй вход подан входной сигнал, а выходы допол нительного триггера соединены с соо ветствующими входами логических эле ментов И, при этом счетчик искажени и дешифратор соединены последовател но и включены меЖДу выходами логиче кого элемента ИЛИ и входом усилителя 1. Однако известное устройство не обеспечивает непрерывную индикадию превышения допустимого числа искажений в течение времени контроля, что ведет к весьма длительному врем пульсной последовательности. Целью изобретения является повышение оперативности контроля. Поставленная цель достигается тем, что в устройство для обнаруя ения потери импульса, содержащее триггер, один из входов которого соединен с выходом второго формирователя, а выходы триггера подключены к одним входам логических эле ментов И, вторые входы которых подключены к выходу первого формироват ля, выходы логических элементов И соединень с входами логического эле мента ИЛИ, усилитель, две линии задержки, дополнительный триггер, счетчик искажений и дешифратор, при чем одна линия задержки подключена входу первого формирователя, вторая линия задержки включена между первы и вторым формирователями, один вход дополнительного триггера подключен к выходу второго формирователя, на его второй вход подан входной сигнал, а выходы дополнительного триггера соединены с соответствующими входами логических элементов И, при этом счетчик искажений и дешифратор соединены последовательно и включены между выходами логического элементаТШИ и входом усилителя, введен счетчик импульсов, вход которого соединен с шиной импульсов тактовой частоты, а выходы соединены с дополнительными входами дешифратора. На фиг. 1 представлена электрическая структурная схема предлагаемого устройства; на фиг. 2 - структурная схема управления порогом срабатывания дешифратора для одного разряда. Устройство содержит линии 1 и 2 задержки, формирователи 3 и 4, триггеры 5 и 6, логические элементы И 7 и 8, логический элемент ИЛИ 9, счетчик 10 искажений, дешифратор 11, усилитель 12, счетчик 13 импульсов. При этом одни из входов триггеров 5 и 6 подсоединены к выходу второго формирователя 4, выходы - к одним входам логических элементов И 7 и 8 соответственно, вторые входы которых подключены к выходу первого формирователя 3, выходы логических элементов И 7 и 8 соединены с входами логического элемента ИЛИ 9, первая линия 1 задержки подключена к входу первого формирователя 3, вторая линия 2 задержки включена между первым 3 и вторым 4 формирователями, счетчик 10 искажений и дешифратор 11 соединены последовательно и включены между выходом логического элемента ИЛИ 9 и входом усилителя 12, счетный вход счетчика 13 импульсов подключен к шине импульсов тактовой частоты, которая подключена к входу первой линии 1 задержки, а выходы счетчика 13 соединены с дополнительными входами дешифратора 11, при этом Второй вход триггера 5 подсоединен к шине контролируемой, а второй вход триггера 6 - к щине эталонных импульсных последовательностей. Устройство работает следуклцим образом. Контролируемую импульсную последовательность подают на вход 14, а эталонную импульсную последовательность, с которой сравнивают контролируемую, подают на вход 15. Оба триггера 5 и 6 устанавливаются в исходное состояние импульсами тактовой частоты, поступающими на вход 16, и через линии 1 и 2 задержки и формирователи 3 и 4 на входы тригг ров 5 и 6. Импульсы тактовой частот синхронны и синфазны с импульсами эталонной последовательности. Минимальное время между импульсами такТОБОЙ частоты на входах триггеров и импульсами контролируемой последовательности зависит от быстродействия тpи гepoв, максимальное время от тактовой частоты контролируемой последовательности. Время подачи эталонной последовательности ограни чено только импульсами на входах триггеров и импульсами тактовой час тоты, подаваемыми на входы элементо И 7 и 8,на вход линии 2 задержки. Таким образом, импульсы контроли руемой последовательности могут подаваться до импульсов эталонной пос Ледовательности, совпадать с ними или отставать от них, но не выходит за пределы разрешенного интервала времени, определяемого временем подачи импульсов тактовой частоты на входы триггеров 5 и 6 и временем выдачи импульсов с формирователя 3. Через некоторое время, определяемое линией 1 задержки после подачи импульсов последовательностей на вход элементов И 7 и 8, подается импульс задержанной тактовой частоты. При появлении ложного импульса в контролируемой последовательности элемент И 7 откроется потенциалом с прямого выхода триггера 5 и импульс тактовой частоты пройдет через нее, через элемент ИЛИ 9 на вход счетчика 10 искажений. Счетчик 10 искажений сосчитает этот импульс. При потере импульса в контролируемой последовательности, триггер 6 установится импульсами эталонной последовательности в такое состояни что его потенциал с прямого выхода откроет элемент И 8, импульс тактовой частоты проходит через него, через элемент ИЛИ 9 на вход счетчика 10 искажений. Счетчик 10 искажений сосчитает этот импульс. При отсутствии импульсов и в контролируе мой последовательности, и в эталонн последовательности, а также при наличии импульсов одновременно в обоих последовательностях, элементы И 7 и 8 закрыты и на их выходах импульсов не имеется. Задавшись допустимой вероятностью искажений в контролируемой последовательности и временем контроля, можно подсчитать допустимое число искажений. Исходя из этого, выходы счетчика 10 искажений подсоединяются к дешифратору 11, который выдает сигнал при превышении допустимого числа искажений. Этот сигнал через усилитель 12 BbifiaercH на индикаторную лампочку 17, Для обеспечения непрерывной индикации превышения допустимого числа искажений в течение всего времени контроля со входа 16 импульсы тактовой частоты подаются на счетчик 13 импульсов, выходы которого подсоединяются к дешифратору 11 и изменяют порог его срабатывания пропорционально времени контроля. Поскольку количество искажений также пропорционально времени контроля, срабатывание дешифратора произойдет в любой момент времени контроля, как только количество искажений превысит текущее допустимое значение. Введение переменного порога срабатывания дешифратора значительно сокращает время контроля аппаратуры, особенно в системах с низкими тактовыми частотами и в системах с низкой вероятностью искажений. Кроме того, при искажениях, превьш1ающих допустимые, что особенно проявляется при неисправностях в системах приема информации, устройство с переменным порогом вьщаст сигнал превьшгения значительно раньше, что ускорит принятие мер к устранению неисправности. Этим значительно сокращается время пребывания системы в состояние Неисправно. На вход 18 элемента И 19 подается сигнал с прямого выхода одного из разрядов счетчика искажений, а на вход 20 элемента И 19 подается сигнал с прямого выхода одного из разрядов счетчика импульсов. На входы 21 и 22 элемента И 23 подаются соответственно сигналы с обратных выходов тех же разрядов счетчика искажений и счетчика импульсов. С выходов элементов И 19 и 23 сигналы подаются на входы элемента ИЛИ 24, а с выхода элемента ИЛИ 24 на вход элемента И 25. 10 На вход 26 элемента.И 25 подается результат сравнения п-го разряда счетчика 10 искажений и n+k-ro разря да счетчика 13 импульсов. Величина k может иметь значение от О до т. При числе на счетчике 10 искажений, равном числу на счетчике 13 импульсов, происходит срабатывание |злемента И 19 или элемента И 23 во всех сравниваемых разрядах, на выходе элемента ИЛИ 24 по всем разрядам появляется сигнал и элемент И 25 сработает. Введение дополнительных элементов позволяет проводить непрерывную индикацию числа искажений в течение всего времени контроля, что повышает оперативность контроля, например, при использовании предлагаемого устройства в системе импульсной связи, на 10-15% повышает вероят-г ность своевременного обнаружения ошибки в передаваемой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потери импульса | 1974 |

|

SU515271A1 |

| Устройство для обнаружения искажений в последовательности импульсов | 1977 |

|

SU743184A1 |

| Устройство для обнаружения искажений в последовательности импульсов | 1980 |

|

SU911715A1 |

| Устройство для контроля работоспособности приемника цифровой информации | 1987 |

|

SU1494236A1 |

| Устройство для контроля фазовых искажений сигнала воспроизведения | 1987 |

|

SU1413673A1 |

| Дискретный демодулятор сигналов частотной телеграфии | 1977 |

|

SU734895A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля фазовыхиСКАжЕНий СигНАлА ВОСпРОизВЕдЕНия | 1979 |

|

SU853671A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПОТЕРИ ИМПУЛЬСА по авт. св. № 515271, отличающееся тем, что, с целью повышения оперативности контроля, в него введен счетчик импульсов, вкод которого- соединен с шиной импульсов тактовой частоты, а выходы соединены с дополнительными входами дешифратора. Н2 It 17 (Л

18

«яоие

19

20

2Г 22

23

Фиг. 2

25

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения потери импульса | 1974 |

|

SU515271A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-07—Публикация

1982-01-04—Подача