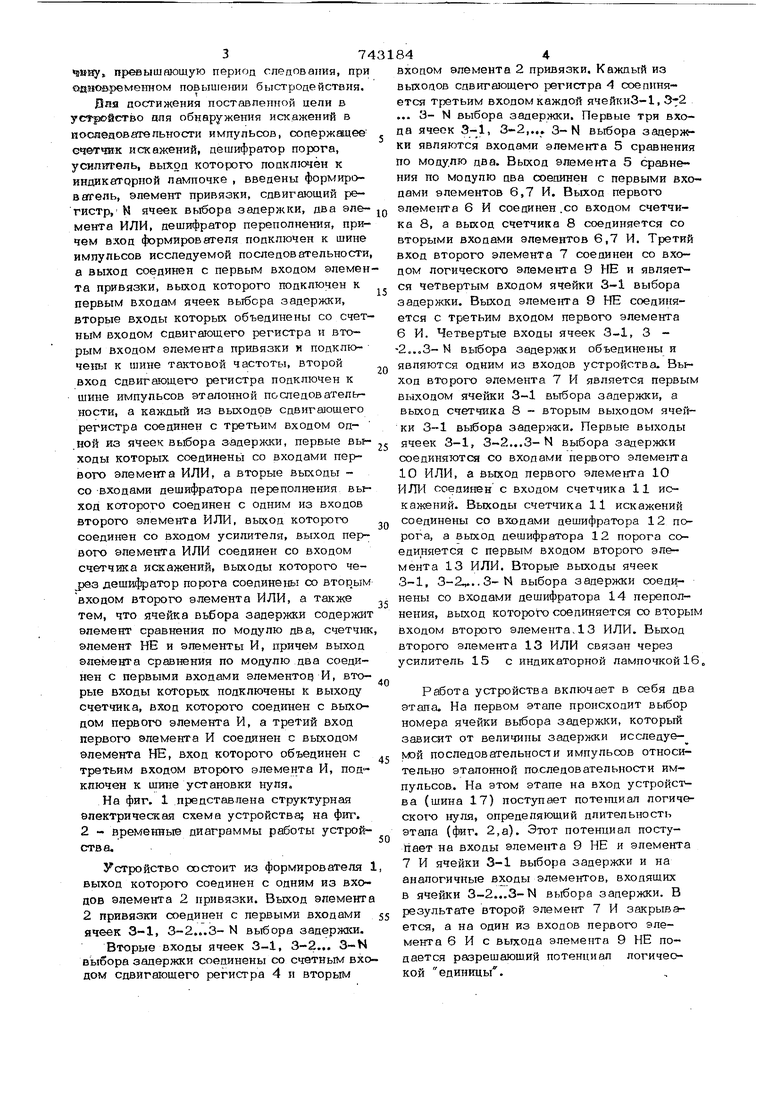

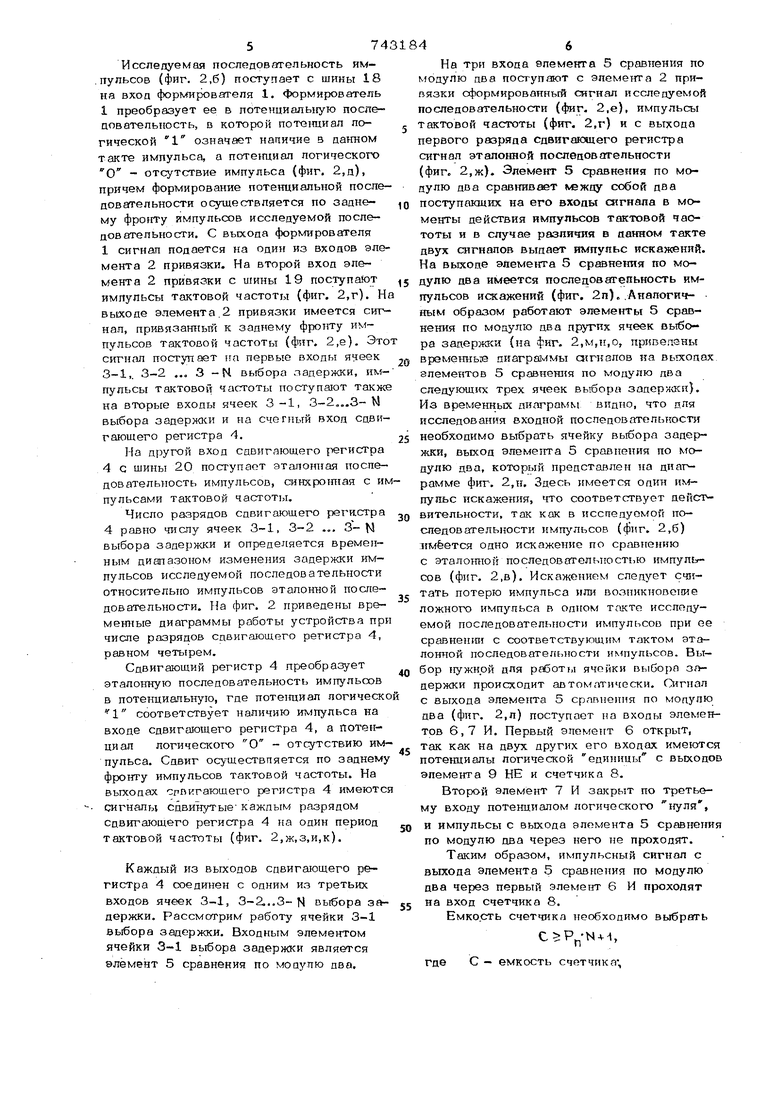

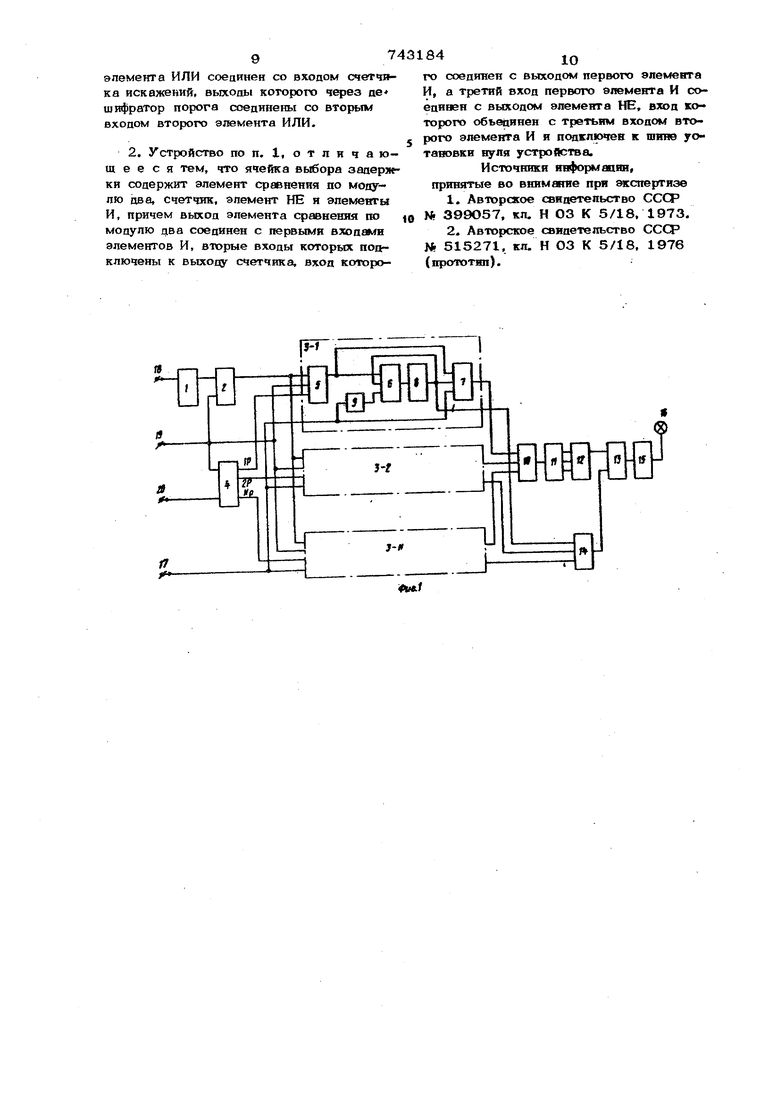

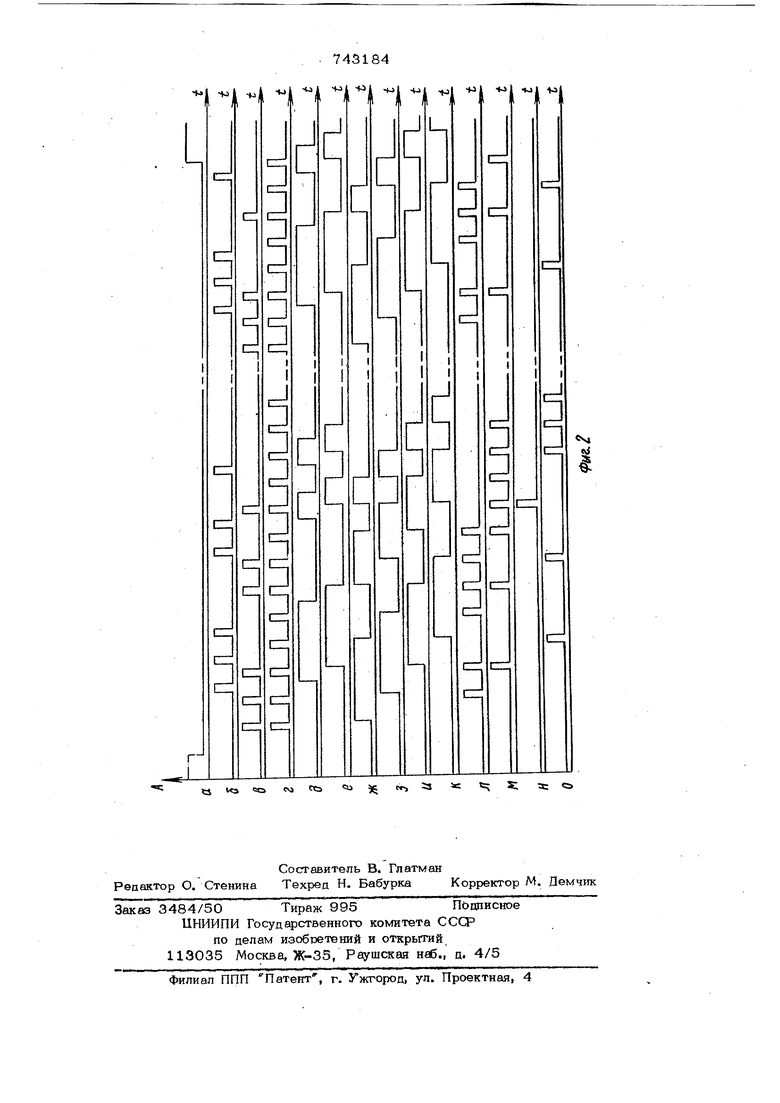

Изобретение относится к импульсной технике, а более конкретно к устройствам осуществляющим контроль входной ПОСЛ&повательно(7гй импульсов с помощью сравнения ее с эталонной последовательностью импульсов. Известно устройство для обнаружения потери импульса, содержащее триггер, один из входов которого соединен с выходом формирователя, а выходы триггера подключены к одним входам логических элементов И, вторые входы которьк подключены к выходу первого формирователя, выходы логических элементов И соединены со входами логического элемента Однако данное устройство не обеспечивает достаточной точности определения временного положения проверяемых импульсов и не позволяет обнаружить появление ложных импульсов. Прототипом предлагаемого устройства является устройство для обнаружения потери импульса, содержащее две линии задержки, два ({юрмирователя, пва триггера. логические элементы И, ИЛИ, счетчик искажений, деши(1)ратор, усилитель 2 . Данное устройство позволяет обнаруживать потерю импульса и наличие ложных импульсов, а также осуществлять контроль временного положения импульсов. Однако известное устройство не обеспечивает обнаружение искажений при временном попожении импульсов исследуемой последовательности, отличающемся от временного положения импульсов эталонной последовательности, больше чем на один период следования импульсов, или дает ложные результаты. Кроме того, быстродействие известного устройства ограничивает время, нео&ходимое для установки в исходное состояние триггеров и опроса логических элементов И. Цель изобретения - обеспечить жение искажений при времетшом положении импульсов исследуемой последовательности, отличном от времен гого положения импульгсов эталонной поспецовательности на вели«вйну, превышающую периоц следования, при ,ременном повышении быстродействия. Дая постижения поставленной цепи в yct « ScTBO апя обнаружения искажений в йоовещовеггельности импупьсов, сопержацее счетчик искажений, дешифратор порога, усипитепь, выхоа которого поаключен к индикаторной лампочке , введены формироваггель, элемент привязки, сдвигающий регистр,- N ячеек выбора задержки, два элемента ИЛИ, дешифратор переполнения, причем вход формирователя подключен к шине импупьсов исследуемой последовательности а выход соединен с первым входом элемен та привязки, выход которого подключен к первым входам ячеек выбора задержки, вторые входы которых объединены со счет ным входом Сдвигающего регистра и вторым входом элемента привязки и подключены к шине тактовой частоты, второй вход Сдвигающего регистра подключен к шине импупьсов эталонной последовательности, а каждый из выходов сдвигающего регистра соединен с третьим входом одной из ячеек выбора з-адерхжи, первые выходы которых соединены со входами первого эпеменга ИЛИ, а вторые выходы со -входами дешифратора переполнения выход которого соединен с одним из входов второго элемента ИЛИ, выход которого соединен со входом усилителя, выход первого элемента ИЛИ соединен со входом счетчика искажений, выходы которого чеjyea дешифратор порога соединены со вторым входом второго элемента ИЛИ, а также тем, что ячейка вьбора задержки содержит элемент сравнения по модулю два, счетчик элемент НЕ и эгаэменты И, причем выход элемента сравнения по модулю два соединен с первыми входами элементов И, вторые входы которых подключены к выходу счетчика, вход которого соедггаен с выходом первого элемента И, а третий вход первого элемента И соединен с выходом элемента НЕ, вход которого объединен с третьим входом второго элемента И, подключен к шине установки нуля. На фиг, 1 представлена структурная эпектрическая схема устройства; на фиг. 2 - временные диаграммы работы устройства. Устройство состоит из формирователя выход которого соединен с одним из входов элемента 2 привязки. Выход эпеменга 2 привязки соединен с первыми входами ячеек 3-1, 3-2...3- N выбора задерж1си. Вторые входы ячеек 3-1, 3-2... 3-N выбора задержки соединены со счетным вхо дом Сдвигающего регистра 4 и вторым ВХОДОМ элемента 2 привязки. Каждый из выходов сдвигающего регистра 4 соединяется третьим входом каждой ячейкиЗ-1, 3-2 ... 3- N выбора задержки. Первые три входа ячеек , 3-2,.... 3-N выбора задеря ки являются входами элемента 5 сравнения по модулю два. Вьосод элемента 5 сравнения по модулю два соединен с первыми входами элементов 6,7 И. Выход первого элемента 6 И соединен .со входом счетчика 8, а выход счетчика 8 соединяется со вторыми входами элементов 6,7 И. Третий вход второго элемента 7 соединен со входом логического элемента 9 FfE и является четвертым входом ячейки 3-1 выбора задержки. Выход элемента 9 НЕ соединяется с третьим входом первого элемента 6И. Четвертые входы ячеек 3-1, 3 -2.оЗ- N выбора задержки объединены и являются Одним из входов устройства. Выход второго элемента 7 И является первым выходом ячейки 3-1 выбора задержки, а выход счетчика 8 - вторым выходом ячейки 3-1 выбора задержки. Первые выходы ячеек 3-1, 3-2...3-N выбора задержки соединяются со входами первого элемента 10 ИЛИ, а выход первого элемента 10 ИЛИ соединен с входом счетчика 11 искажений. Выходы счетчика 11 искажений соединены со входами дешифратора 12 порога, а выход дешифратора 12 порога соединяется с первым входом второго элемента 13 ИЛИ. Вторые выходы ячеек 3-1, 3-2.,...3-N выбора задержки соединены со входами дешифратора 14 переполнения, выход KOTopotxi соединяется со вторым входом второго элемента, 13 ИЛИ. Выход второго элемента 13 ИЛИ связан через усилитель 15 с индикаторной лампочкой 16„ Работа устройства включает в себя два этапа. На первом этапе происходит выбор номера ячейки выбора задержки, который зависит от величины задержки исследуемой последовательности импульсов относительно эталонной последовательности импульсов. На этом этапе на вход устройст ва (шина 17) поступает поте1шиал логического нуля, определяющий длительность этапа (фиг. 2,а). Этот потенциал поступает на входы элемента 9 НЕ и элемента 7И ячейки 3-1 выбора задержки и на аналогичные входы элементов, входящих в ячейки 3-2...3-N выбора задержки. В результате второй элемент 7 И закрывается, а на один из входов первого элемента 6 И с выхода элемента 9 НЕ подается разрешающий потенциал логической единицы. Исследуемая последовательность ям.пульсов (фиг. 2,6) поступает с шины 18 на вход форкедрюваггеля 1. Формирователь 1 преобразует ее в потенциальную поспе- цователыюсть, в которой потенциал логической 1 означает наличие в данном такте импульса, а потетхиал логического О - отсутствие импульса {фиг. 2,д), причем формирование потенциальной после довательности осуществляется по заднему фронту импульсов исследуемой последовательности. С выхода формирователя 1 сигнал подается на один из входов эле мента 2 привязки. На второй вход элемента 2 привязки с шины 19 поступают импульсы тактовой частоты (фиг. 2,г). Н вьЕХОде элемента.2 привязки имеется сит нал, привязанньш к заднему фронту импульсов тактовой частоты (фиг. 2,е). Эт сигнал поступает на первые входы ячеек 3-1,, 3-2 ... 3 -М выбора задержки, импульсы тактовой частоты поступают такж на вторые входы ячеек 3-1, 3-2,,.3- М выбора задермси и на счетный вход сдвигающего регистра 4. Иа другой вход сдвигающего регистра 4 с шины 20 поступает эталонная последовательность импульсов, синхрютшая с и пульсами тактовой частоты. Число разрядов сдвигающего регистра 4 равно числу ячеек 3-1, 3-2 ... 3выбора задержки и определяется временным диапазоном изменения задержки импульсов исследуемой последовательности относительно импульсов эталонной последовательности. На фиг. 2 приведены времеьшые диаграммы работы устройства пр числе разрядов сдвигающего регистра 4, равном четырем. Сдвигающий регистр 4 преобразует эталонную последовательность импульсов в потенциальную, где потенциал логическ соответствует наличию импульса на входе Сдвигающего регистра 4, а потенциал логического О - отсутствию импульса. Сдвиг осуществпяется по заднему фронту импульсов тактовой частоты. На выходах срвкгающего регистра 4 имеютс сигналы сдвинутые каждым разрядом Сдвигающего регистра 4 на один период тактовой частоты (фиг. 2,ж,з,и,к). Каждый из выходов сдвигшощего регистра 4 соединен с одним из третьих входов ячеек 3-1, 3-2...3-N выбора задержки. Рассмотрим работу ячейки 3-1 выбора задержки. Входным элементом ячейки 3-1 выбора задержки является элемент 5 сравнения по модулю два. На три входа элемента 5 сравнения по модулю два поступают с элемента 2 привязки сформированный снгнал исследуемой послеповательности (фиг. 2,е), импульсы тактовой частоты (фиг. 2,г) и с выхода первого разряда сдвигающего регистра сигнал эталонной поспвповательности (фиг. 2,ж). Элемент 5 сравнения по мопупю два кежцу собой два поступакщих на его входы сигнала в моменты действия импульсов тактовой частоты и в случае различия в данном такте двух сигналов выдает иктупьс искажений. На выходе элемента 5 сравнения по модулю два имеется последовагепьность импульсов иосажений (фиг. 2п). .Аналогичным образом работают элемет-ы 5 сравнения по модулю два других ячеек вь бора задержки (на фиг. 2,м,н,о, привеааны враметагые пиаграЗх;(мы сигналов на выходах, элементов 5 сравнения по модулю два следующие трех ячеек выбора задернжп), Из временных диаграмм видно, что для исследования входной последовательности необходимо выбрать ячейку выбора задержки, выход элеметга 5 сравнения по модулю два, который представлен па диат рамме фиг-. 2,н. Здесь имеется один импупьс искажения, что соответствует дейст вительности, так как в иссггедуомой последовательности импульсов (фиг. 2,6) имеется одно искажение по сравнению с эталотюй последовательностью импул тсов (фиг. 2,в). Искажением следует сч15тать потерю импульса или возникновение ложного импульса в одном такте исследуемой последовательности импульсов при ее сравненш с соответствующим тактом эталонной последовательности импульсов. Выбор нужной для работы ячейки выбора ЗсТдержки происходит автоматически. Сигнал с выхода элемента 5 сравнения по модулю два (фиг. 2,л) поступает на входы элементов 6,7 И. Первый элемент 6 открыт, так как на пвул других его входах имеются потенциалы логической едишшы с выходов элемента 9 НЕ и счетчика 8. Второй элемент 7 И закрыт по третьему входу потегщиалом логического нуля, и импульсы с выхода элемента 5 сравнения по модулю два через него не проходят. Таким образом, импульсный сигнал с выхода элемента 5 сравнения по модулю два через первый элеметгг 6 И проходят на вход счетчика 8. Емкость счетчика необходимо вьлбрать , где С - емкость счетчика

вероятность искажения однотх) , имнульса и появления ложного

импульса в интервале времени,

необхоцимом для выбора нуишой

пля работы ячейки выбора зацержки;М - число анализируемых тактов,

умещающихся в интервале времени, необходимом для выбора

нужной для работы ячейки выбора задержки.

Величина интервала времени, необходимого для выбора нужной для работы ячей ки выбора задержки, зависит от характера шжледуемой импул ьсной последовател ьности изменяется пропорционапьно автокорреляци онной функции исследуемого и этало1гаого сигнапов.

Из временных диаграмм фиг, 2, л, м, н, о, виано, что нужная для работы ячейка выбора задержки, в которой элемент сравнения 5 по модулю два выдает сигнал, показа1гаый на фиг, 2,н, Элементы 5 сравнения по модулю два остальных ячеек выбор задержки выдают большее число искажений, и счетчики этих ячеек, если их емкость выбрана по указанной формуле, переполняются. По окончании этапа выбора нужной для работы ячейки вь1бора задержки: на входах элемента 9 НЕ и третьем входе второго элемента 7 И появится потенциал логической епишщы, В результате будет открыт второй элемент И только в той ячейке выбора задермси, где не переполнился счетчик. Выход вторых элементов И ячеек 3-1, 3-2,„3-N выбора задержки соединен. со входами первого элемеггга 10 ИЛИ.

На следующем этапе обнаружения искажений в исследуемой последовательности импульсов устройство работает следующим образом.

На один из входов первого элемента 10 ИЛИ с выбраетюй для работы ячейки выбора задержки поступают импульсы искажений исследуемой последовательности импульсов, которые поступают па вход счетчика 11 искажений. Зная допустимую вероятность искажений в контролируемой последовательности импульсов и время контроля, можно подсчитать допустимое за это время число искажений. Исходя из этого, выходы счетчика 11 искажений, под соединяются к дешифратору 12 порога, который выдает сигнал при превышении допуо тимого числа искажений. Этот сигнал через второй элемент 13 ИЛИ и усилитель 15 выдается на индикаторную лампочку 16 Если же на этапе выбора нужной для работы ячейки выбора задержки в контролируемой последовательности число искажений будет превышать допустимое, то все счетчики ячеек выбора задержки переполняются. Выходы всех счетчиков соединены со входами дешифратора 14 переполнения, и при переполнении всех счетчиков дешифратор 14 выдает сигнал, который через второй элемент 13 ИЛИ и усилитель 15 поступит на индикаторную лампочку 16,

Устройство для обнаружения искажений а последовательности импульсов обеспечивает обнаружение искажений при временном положении импульсов исследуемой последовательности, отличающемся от временного положения импульсов эталонной последовательности на величину, превышающую период следования импульсов.

Формула изобретения

1, Устройство для обнаружения искажений в последовательности импульсов, содержащее счетчик искажений, дешифратор порога, усилитель, выход которого подключен к индикаторной лампочке, отличающееся тем, что, с целью обеспечения обнаружения искажений при временном положении импульсов исследуемой последовательности, отличном от временного положения импульсов эталонной последовательности на величину, превышающую период следования импульсов, при одновременном повышении быстродействия, в него введены формирователь, элемент привязки, сдвигающий регистр, N ячеек выбора задержки, элементы ИЛИ и дешифратор переполнения, причем вход формирователя подключен к шине импульсов исследуемой последовательности, а выход соединен с первым входом элемента привязки, выход которого подключен к первым входам ячеек выбора задержки,, вторые входы которых рбъединены со счетным входом сдвигающего регистра и аторым входом элемента привязки и подключены к щине тактовой частоты, второй вход сдвигающего регистра подключен к: шине импульсов эталонной последовательности, а каждый из выходов сдвигающего регистра соединен с третьим входом одной из ячеек вьбора задержки, первые выходы которых соединены со входами первого элемента ИЛИ, а вторые выходы - со входами дешифратора переполнетш, выход которого соединен с одггим из входов второго элемента ИЛИ, выход котоуюго соединен со входом усилителя, выход первого

элемента ИЛИ соецинен со вхоаом счетчика искажений, вьпсоцы которого через ае шифратор порога соепинены со вторым вхопом второго элемента ИЛИ.

2. Устройство по п. 1, о т п и ч а ющ е е с я тем, что ячейка выбора задержки содержит элемент сравнения по модулю цв а, счетчик, элемент НЕ и элемевты И, причем выхоа элемента сре невяя по модулю два соединен с первыми входами элементов И, вторые входы которых подключены к выходу счетчика, вход которого соединен с выходом первого элемента И, а третий вход первого элемента И соединен с выходом элемента НЕ, которого объединен с третьим входом второго элемента И и подключен к шине уотановки нуля устройства.

Источники информапии, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 1 399О57, кл. Н ОЗ К 5/18, 1973.

2.Авторское свидетельство СССР № 515271, кл. Н ОЗ К 5/18, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения искажений в последовательности импульсов | 1980 |

|

SU911715A1 |

| Устройство для обнаружения искажений в последовательности импульсов | 1986 |

|

SU1367144A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Запоминающее устройство | 1981 |

|

SU1018150A1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| Устройство синхронизации кодовой последовательности | 1988 |

|

SU1555893A1 |

| УСТРОЙСТВО АВТОМАТИЗИРОВАННОГО ФОРМИРОВАНИЯ ЭТАЛОННОЙ ИНФОРМАЦИИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 2012 |

|

RU2520386C1 |

| Устройство для измерения защищенности сигналов от помех | 1989 |

|

SU1658399A1 |

| УСТРОЙСТВО ДЛЯ КОМПЕНСАЦИИ АМПЛИТУДНО-ЧАСТОТНЫХ ИСКАЖЕНИЙ В ЛИНЕЙНЫХ ТРАКТАХ С ИСПОЛЬЗОВАНИЕМ ДВУХМЕРНЫХ МЕТРИЧЕСКИХ ПРОСТРАНСТВ | 2006 |

|

RU2342781C2 |

| Устройство для обнаружения потери импульса | 1982 |

|

SU1084981A2 |

Авторы

Даты

1980-06-25—Публикация

1977-12-01—Подача