Изобретение относится к вычислительной технике и может быть использовано для контроля функционирования и хода вычислительного процесса в автоматизированных системах управления (АСУ), построенных на основе однокристальных микропроцессорных БИС и программно реализующих различные алгоритмы логического управления, задаваемые в виде бинарных граф схем .алгоритмов (БГСА) .

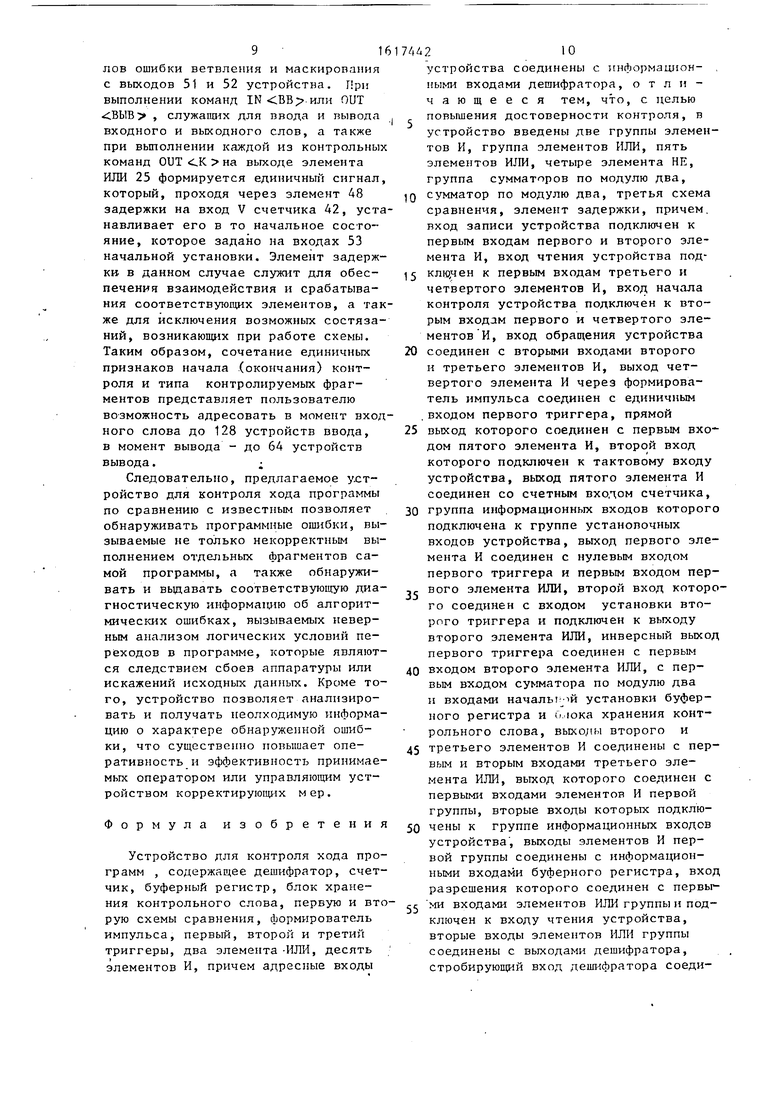

Цель изобретения - повьш1ение достоверности контроля. ; На фиг. 1 приведена функциональная схема устройства для контроля

хода программ, на фиг. 3 - временные диаграммы работы устройства для контроля хода программ.

Устройство для контроля хода программ содержит тактовый вход 1 устройства, вход 2 обращения, вход 3 чтения, вход 4 записи, входы 5, 6 признака последовательности условных модулей, вход 7 эталонного сигнала, адресные входы 8, информационные входы 9, вход 10 признака выдачи выходного слова, вход 11 начала-окончания контроля, элементы И 12-16, группы 17 и 18 элементов И, элементы И 19-23, группу элементов ИЛИ 24,

элементы ИЛИ 25-31, элементы НЕ 32- 35, сумматор 36 по модулю два, групп 37 сумматоров по модулю два, триггеры 38-40, блок 41 хранения контрольного слова, счетчик 42, дешифратор

43,буферный регистр 44, схемы 45-47 сравнения, элемент 48 задержки, фор- мироватепь 49 и тульса, выходы 50-52 ошибки устройства и входы 53 уста- ьськк устройстна.

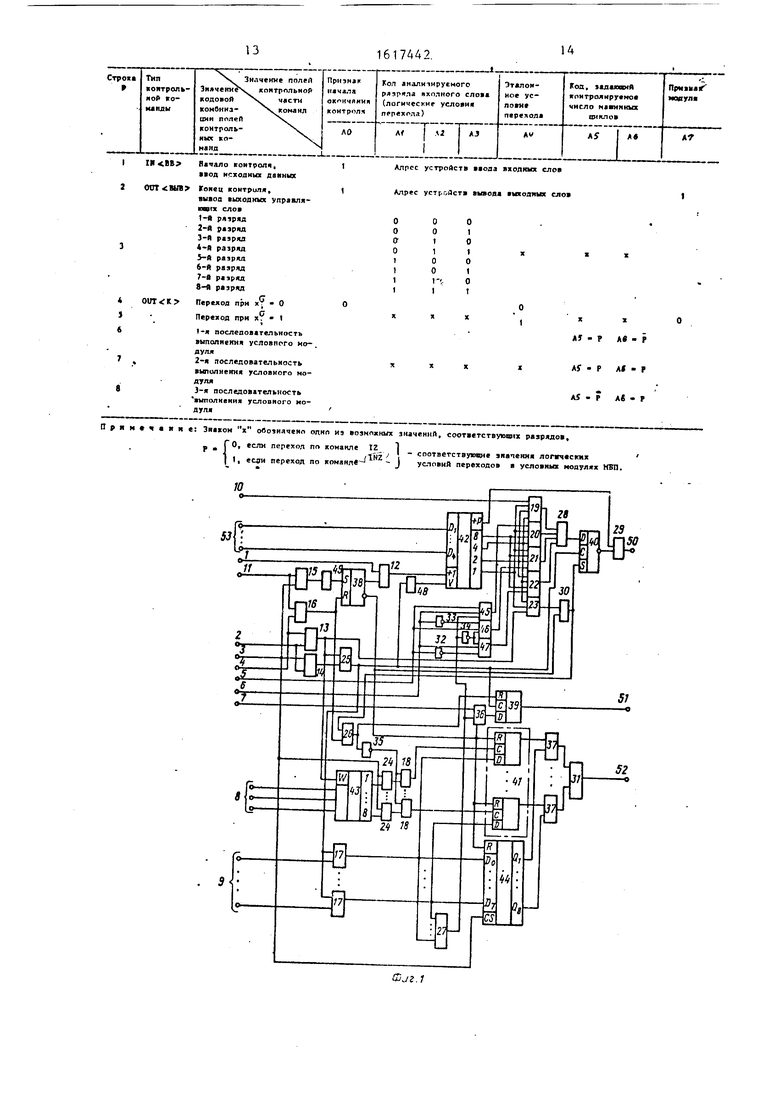

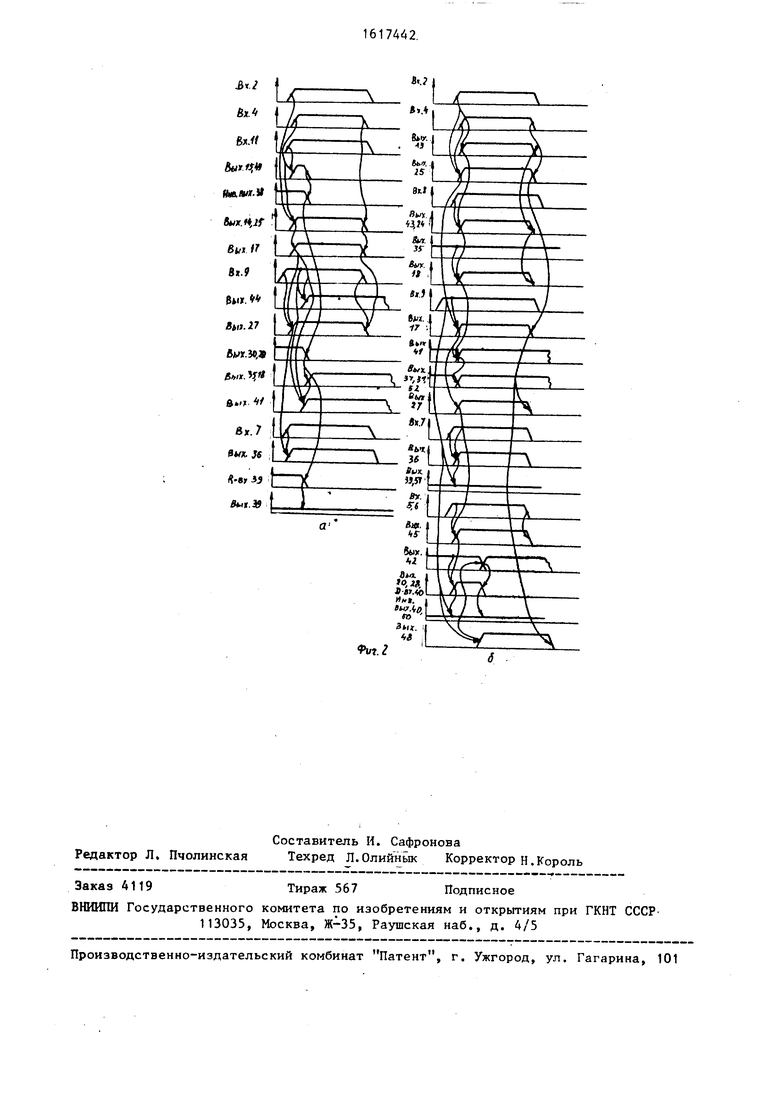

На фиг.2а представлена временная диаграмма работы устройства для контроля хода программы на последнем машинном т.и кле выполнения команды вво- да входного слова в буферный регистр

44,блока 41 хранения контрольного слова; на фиг.2б - временная диаграм ма работы устройства на последнем машинном цикле выполнения контрольной команды типа OUT К при условии совпадения числа машинных циклов, заданного значениями адресных линий А1-АЗ) с числом, сформированным на выходах счетчика 43 при отработке соответствующего фрагмента, а также

при совпадении эталонного значения перехода (разряд. А4) и результата промежуточных вычислений.

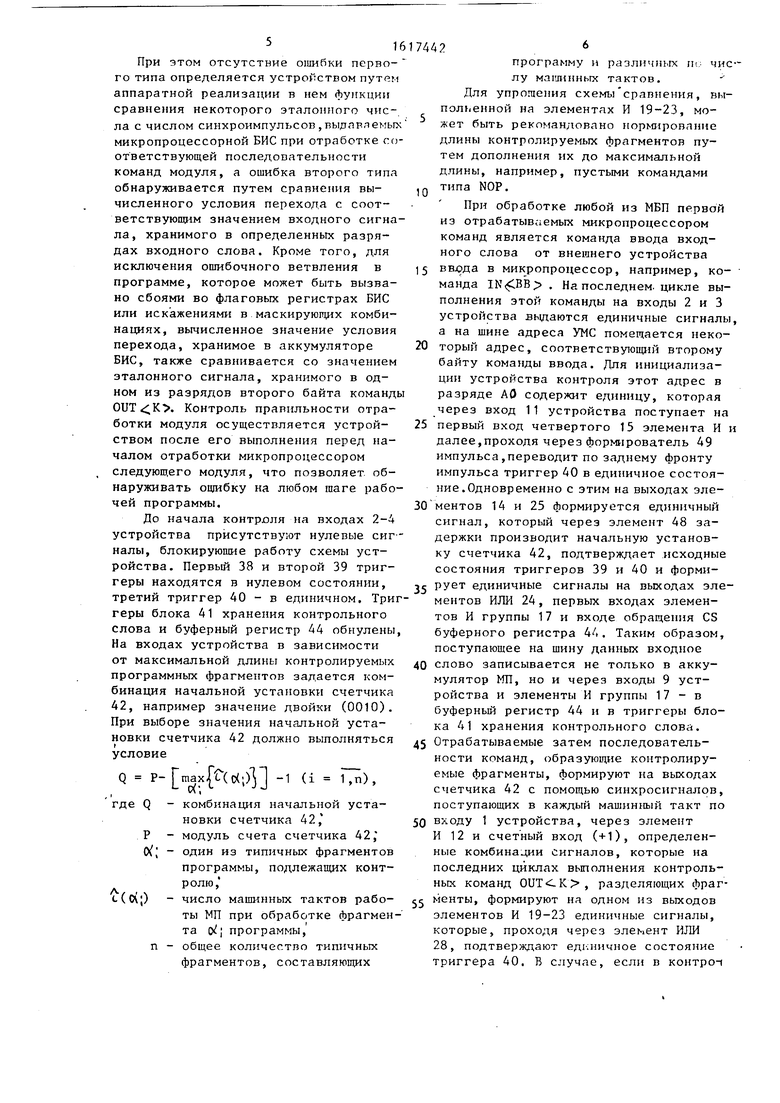

В строке 1 таблицы кодирования второго байта соответствую0щх контрольных команд представлен порядок кодирования второго байта команды ввода входного слова (); в строке 2 - порядок кодирования второго байта команды вывода выходного управляющего слова (), в строке 3 - пЬрядок кодирования адресных разрядов А1-АЗ, в строках 4 и 5 - порядок кодирования разряда А4 задающего на вход 7 устройства эталонное значение условия перехода, которое определяется по бинарным графам схем алгоритмов в зависимости от того, по какому ребру (нулевому или единичному) осуществлен переход к вьтолнению следующего программного .фрагмента, реализующего соответствующую ему вершину БГСА; в строках 6-8 - порядок кодирования разрядов А5 и А6 при выполнении соответственно первой, второй и третьей последовательностей команд в программных фрагмантах с условными переходами.

Любой алгоритм логического управления, заданный системой булевых функций, может быть представлен БГСА, осуществляющим выбор выходных управляющих слов, в качестве которых мо

)о

15

20 25

,« .Q r

35

50

5

гут выступать определенные комбинации значений управляюпщх сигналов. При этом, реализующая этот алгоритм микропроцессорная бинарная программа может быть составлена как некоторая последовательность повторяющихся фрагментов программы, образующих типовые программные модули, ориентирование как на обработку однобайтных наборов входных сигналов, хранящихся в регистрах общего назначения микропроцессорной БИС, так и на выдачу из определенных массивов памяти управляющих выходньк слон. Заметим, что в общем случае все фрагменты можно разделить на условные программные модули, служащие для проверки логических условий переходов по ветвям алгоритма, и лиейные программные модули, служащие для формирования или выдачи выходных управляющих слов, причем контролируемое число машинных циклов в условных программных модулях зависит от значения логического условия перехода. Следовательно, ход вьшолнения такой программы можно считать правильным, если на любом из допустимых наборов входных переменных переход от выполнения предыдущего программного модуля к последующему не приводит к искажению реализуемого алгоритма. Для выделения программных модулей и организации ввода исходных данных, своевременной выдачи и обработки контрольной и управляющей информации эти модули разделены контрольными командами, несущими для устройства контроля ряд эталонных и управляющих сигналов. В качестве таких команд используются команды обмена микропроцессора с внешними устройства типа IN В2 и OUT :В2(где В2 - второй байт команды, порядок кодирования которого в зависимости от назначения команды представлен в таблице. Таким образом, условием безошибочного выполнения того или иного программного модуля может служить отсутствие ошибок типа:

-пропадание необходимой или появление ложной команды в каком-либо программном модулеJ

-неверное получение .в ходе вычислений значения входной переменной (или логического условия перехода), определяемого порядок отработки ветвей алгоритма.

1

При этом отсутствие ошибки перво- го типа определяется устройством путем аппаратной реализации в нем функции сравнения некоторого эталонного числа с числом синхроимпульсов , выдав л емых микропроцессорной БИС при отработке соответствующей последовательности команд модуля, а ошибка второго типа обнаруживается путем сравнения вычисленного условия перехода с соответствующим значением входного сигнала, хранимого в определенных разрядах входного слова. Кроме того, для исключения ошибочного ветвления в программе, которое может быть вызвано сбоями во флаговых регистрах БИС или искажениями в маскирующих комбинациях, вычисленное значение условия перехода, хранимое в аккумуляторе БИС, также сравнивается со значением эталонного сигнала, хранимого в одном из разрядов второго байта команд . Контроль правильности отработки модуля осуществляется устройством после его выполнения перед началом отработки микропроцессором следующего модуля, что позволяет, обнаруживать ошибку на любом шаге рабочей программы.

До начала контроля на входах 2-4 устройства присутствуют нулевые сигналы, блокирующие работу схемы устройства. Первьй 38 и второй 39 триггеры находятся в нулевом состоянии, третий триггер 40 - в единичном. Триггеры блока 41 хранения контрольного слова и буферный регистр 44 обнулены На входах устройства в зависимости от максимальной длины контролируемых программных фрагментов задается комбинация начальной установки счетчика 42, например значение двойки (0010). При выборе значения начальной установки счетчика 42 должно выполняться условие

Q (о(1) 5 -1 (i Г) ,

где Q - комбинация начальной установки счетчика 42, Р - модуль счета счетчика 42, - один из типичных фрагментов программы, подлежащих контролю,

1.(о(;) - число машинных тактов работы МП при обработке фрагмента ( программы, п - общее количество типичных фрагментов, составляющих

174426

программу и различных ш; числу манинных тактов. Для упрощения схемы сравнения, вы- польенной на элементах И 19-23, может быть рекомандовано норьо1рование длины контролируемых фрагментов путем дополнения их до максимальной длины, например, пустыми командами

10

типа NOP.

При обработке любой из МБП первой из отрабатываемых микропроцессором команд является команда ввода входного слова от внешнего устройства 15 ввода в микропроцессор, например, команда . На последнем, цикле выполнения этой команды на входы 2 и 3 устройства выдаются единичные сигналы а на шине адреса УМС помещается неко- 20 торый адрес, соответствующей второму байту команды ввода. Для инициализации устройства контроля этот адрес в разряде АО содержит единицу, которая через вход 11 устройства поступает на 25 первый вход четвертого 15 элемента И далее,проходя через формирователь 49 импульса,переводит по заднему фронту импульса триггер 40 в единичное состояние. Одновременно с этим на выходах эле- 30 ментов 14 и 25 формируется единичный сигнал, который через элемент 48 задержки производит начальную установку счетчика 42, подтверждает исходные состояния триггеров 39 и 40 и форми- 35 РУет единичные сигналы на выходах элементов ИЛИ 24, первых входах элементов И группы 17 и входе обращения CS буферного регистра 44. Таким образом, поступающее на шину данных входное 40 слово записывается не только в аккумулятор МП, но и через входы 9 устройства и элементы И группы 17 - в буферный регистр 44 и в триггеры блока 41 хранения контрольного слова. 45 Отрабатываемые затем последовательности команд, образующие контролируемые фрагменты, формируют на выходах счетчика 42 с помощью синхросигналов, поступающих в каждый машинный такт по 50 входу 1 устройства, через элемент И 12 и счетный вход (+1), определенные комбинации Сигналов, которые на последних циклах выполнения контрольных команд ОиТ СК, разделяющих фраг- JJ менты, формируют на одном из вькодов элементов И 19-23 единичные сигналы, которые, проходя через элемент ИЛИ 28, подтверждают ед1-;ничное состояние триггера 40. В случае, если в контро-i

лируемом фрагменте не выполняется какая-либо команда или появляется ложная, то на выходе 50 устройства появляется сигнал ошибки, которьй формируется либо по выходу (+Р) счет чика 42, либо на последнем машинном цикле контрольной команды OUT.K, так как на выходах элементов И 19-23 нет значения единицы и, следовательно, триггер 40 переносится в нулевое состояние. В случае, если в соответствии с бинарным графом реализуемого алгоритма к тому или иному фрагменту программы предусмотрен переход по нескольким путям вычисления, то перед этим фрагментом программы ставится соответствующее количество контрольных команд , каждая из которых имеет определенное значение второго байта команды. Для-того, чтобы эти контрольные команды не воспринимались как ложные, на заключительном машинном цикле их выполнения с помощью счетчика 42, элементов И 18, ИЛИ 26 и 30 на входы начальной установки триггеров 39 и 40 и блока 41 подается сигнал, исключающий выдачу ложного сигнала ошибки на выходах 50-52 устройства.

Для исключения алгоритмических ошбок ветвления, возникающих вследстви неверного анализа микропроцессором входных переменных (логических условий переходов) после отработки каждого из модулей условного перехода при выполнении контрольных команд OUT .К устройством проверятся соответствие .значения логического условия перех.р- да, полученного маскированием в аккумуляторе микропроцессора, значению соответствующей существенной переменной х, хранящейся в буферном регистре 44 устройства контроля. При этом в последнем цикле вьтолнения соответствующей контрольной команды с линий шины адреса на входы 8 устройства поступает код выбираемого триггера из блока 41 хранения контрольного слова, в который с помощью дешифратора 43, элементов И 18, ИЛИ 24 и соответствующих управляющих сигналов записи и обращения записывается вычисленное микропроцессором зна- логического условия перехода, поступающего в это же время из аккумулятора МП через шину данных, входы 9 устройства и элементы И 17 на В-ьход соответствующего триггера

0

5

0

5

0

5

0

5

0

5

блока 41. Если при этом значение, вычисленное в аккумуляторе микропроцес- ора, оказывается неверным и соответствующий триггер блока 41 изменяет свое состояние на противоположное, то на выходе одного из су маторов по модулю два группы 37 появится единица, что возникает вследствие расхождения значений, поступающих с соответ- ствутощего выхода триггера блока 41 и соответствующего выхода Q буферного регистра 44 на первый и второй входы этого сумматора по модулю дна. Единица, проходя через элемент ИЛИ 31, вьщает на выходе 52 сигнал ошибки ветвления. Кроме того, в случае, если значение переменной вычислено верно и на выходе 52 отсутствует сигнал ошибки, а переход в программе осуществлен все же по другому значению, что является следствием искажения значения флагового регистра или маски, служащей для определения значений переменных х , то на выходе элемента ИЛИ 27 появляется значение, отличное от значения, поступающего с шины адреса на вход 7 устройства и на первый вход сумматора 36 по модулю два. В результате этого второй триггер 39 перебрасьшается в единицу, а на выходе 51 устройства выдается сигнал ошибки маски. При отработке микропроцессором заключительного на каждом пути вычисления реализуемого алгоритма фрагмента вьщачи выходного управляющего слова на третьем цикле выполнения команды соответствующий пход 10 признака выдачи выходного слова устройства поступает значение единицы, которая в сочетании с сигналами, полученными на выходах счетчика 42, формирует при верной отработке этого модуля на выходах элементов И 19 и ИЛИ 28 единичный сигнал, подтверждающий единичное состояние третьего триггера 40 и отсутствие ошибки. Кроме того, единичный признак ЛО 1 окончания контроля, поступивший при выполнении команды вывода вход 11 устройства, в сочетании с сигналами записи и обращения переводит через входы 2 и 4 устройства первый триггер 38 в нулевое состояние, а единичный сигнал с выхода элемента И 16, поступая через элемент ИЛИ 26 на R-вход второго триггера 39 и первые входы элементов И 24, запрещает выдачу ложных сигна91

лов ошибки ветвления и маскирования с выходов 51 и 52 устройства. При выполнении команд IN ВВ или OUT ВЫВ , служащих для ввода и вывода входного и выходного слов, а также при вьшолнении каждой из контрольных команд OUT выходе элемента ИЛИ 25 формируется единичный сигнал, который, проходя через элемент 48 задержки на вход V счетчика 42, устанавливает его в то начальное состояние, которое задано на входах 53 начальной установки. Элемент задержки в данном случае служит для обеспечения взаимодействия и срабатывания соответствующих элементов, а также для исключения возможных состязаний, возникающих при работе схемы. Таким образом, сочетание единичных признаков начала .(окончания) контроля и типа контролируемых фрагментов представляет пользователю возможность адресовать в момент входного слова до 128 устройств ввода, в момент вывода - до 64 устройств вывода.;

Следовательно, предлагаемое устройство для контроля хода программы по сравнению с известным позволяет обнаруживать программные ошибки, вызываемые не только некорректным выполнением отдельных фрагментов самой программы, а также обнаруживать и выдавать соответствующую диагностическую информа1щю об алгоритмических ошибках, вызываемых неверным анализом логических условий пе- р1еходов в программе, которые являются следствием сбоев аппаратуры или искажений исходных данных. Кроме того, устройство позволяет анализировать и получать неолходимую информацию о характере обнаруженной ошибки, что существенно повышает оперативность и эффективность принимаемых оператором или управляюш м устройством корректирующих мер.

Формула изобретения

Устройство для контроля хода программ , содержащее дешифратор, счетчик, буферный регистр, блок хранения контрольного слова, первую и вторую схемы сравнения, формирователь импульса, первый, второй и третий триггеры, два элемента -ИЛИ, десять элементов И, причем адресные входы

210

устройства соединены с информашюн- . ными входами дешифратора, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены две группы элементов И, группа элементов ИЛИ, пять элементов ИЛИ, четыре элемента НЕ, группа сумматоров по модулю два,

сумматор по модулю два, третья схема сравнения, элемент задержки, причем, вход записи устройства подключен к первым входам первого и второго элемента И, вход чтения устройства подклщчен к первым входам третьего и четвертого элементов И, вход начала контроля устройства подключен к вторым входам первого и четвертого элементов И, вход обращения устройства

соединен с вторыми входами второго и третьего элементов И, выход четвертого элемента И через формирователь импульса соединен с единичным входом первого триггера, прямой

выход которого соединен с первым входом пятого элемента И, второй вход которого подключен к тактовому входу устройства, выход пятого элемента И соединен со счетным входом счетчика,

группа информационных входов которого подключена к группе установочных входов устройства, выход первого элемента И соединен с нулевым входом первого триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с входом установки второго триггера и подключен к выходу второго элемента ИЛИ, инверсный выход первого триггера соединен с первым

входом второго элемента ИЛИ, с первым входом сумматора по модулю два и входами началь -1Й установки буферного регистра и олока хранения контрольного слова, выходы второго и

третьего элементов И соединены с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с первыми входами элементов И первой группы, вторые входы которых подключены к группе информационных входов устройства, выходы элементов И первой группы соединены с информационными входами буферного регистра, вход разрешения которого соединен с первыми входами элементов ИЛИ группы и подключен к входу чтения устройства, вторые входы элементов ИЛИ группы соединены с выходами дешифратора, стробирующий вход дешифратора соединен с выходом второго элемента И, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И второй группы, выход первого элемента ИЛИ соединен с нулевым входом третьего триггера и через первый элемент НЕ - с вторыми входами элементов И второй группы, выходы которых подключены к синхровходам блока хранения контрольного слова, выходы элементов И первой группы соединены с входами четвертого элемента ИЛИ и информационными входами блока хранения контрольного слова, выходы буферного регистра соединены с первыми входами соответствующих сумматоров по МОДУЛЮ два группы, вторые входы которых соединены с выходами блока хранения контрольного слова, выходы сумматоров по модулю два группы соединены с входами пятого элемента ИЛИ, выход которого является первым выходом ошибки устройства, прямой выход третьего триггера является вторым выходом ошибки устройства, выход третьего элемента ИЛИ соединен с син- хровходами второго и третьего триггеров и через элемент задержки - с входом разрешения записи счетчика, выход переполнения которого соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с инверсным выходом второго триггера, выход которого является третьим выходом ошибки устройства, выход первого разряда счетчика соединен с первыми входами элементов И с шестого по девятый, выход второго разряда счетчика соединен с вторыми входами седьмого, девятого элементов И и первым входом десятого элемента И, выход третьего разряда счетчика

соединен с вторыми входами шестого, восьмого, десятого элементов И и третьим входом девятого элемента И, выход четвертого разряда счетчика соединен с третьими входами седь- мого, восьмого и десятого элементов И, выходы схем сравнения с первой по третью соединены с четвертыми входаQ ми соответственно восьмого, седьмого и десятого элементов И, выход второго элемента И соединен с третьим шестого элемента И, выходы элементов И с седьмого по десятый сот

5 единены с входами шестого элемента ИЛИ, выход которого соединен с инфор мационным входом второго триггера, первый вход признака последовательности условных модулей устройства

0 соединен с первыми входами первой и второй схем сравнения и через второй элемент НЕ - с первым входом третьей схемы сравнения, второй вход признака последовательности условных

5 модулей устройства соединен с вторыми входами первой и третьей схем сравнения и через третий элемент НЕ - с вторым входом второй схемы сравнения, выход четвертого элемента ИЛИ

0 соединен с вторым входом сумматора по модулю два, с третьим входом первой схемы сравнения и через четвертый элемент НЕ - с третьими входами второй и третьей схем сравнения, третий вход сумматора по модулю два подключен к входу эталона устройства, а выход - к информационному входу третьего триггера, выход шестого элемента И соединен с вторым входом второго

о элемента ИЛИ, четвертый вход девятого элемента И подключен к входу приз-, нака выдачи выходного слова устройства.

5

Кол зналивирусного ряэрхла вхолного словж (логические условия

перехода)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для контроля хода программы | 1983 |

|

SU1236487A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1605239A1 |

| Устройство для контроля программ | 1988 |

|

SU1509906A2 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для контроля программ | 1987 |

|

SU1418719A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля хода вычислительного процесса в автоматизированных системах управления, построенных на однокристальных микропроцессорных БИС, программно-реализующих различные алгоритмы логического управления, задаваемые в виде бинарных граф-схем алгоритмов. Целью изобретения является повышение достоверности контроля. Устройство дополнительно содержит две группы элементов И, группу элементов ИЛИ, элементы НЕ, сумматоры по модулю два, элемент задержки, третью схему сравнения. Устройство позволяет обнаруживать алгоритмические ошибки и оперативно выдавать соответствующую диагностическую информацию о характере этой ошибки. Кроме того, реализованный в устройстве вывод контрольной информации, использующий часть адресного пространства, позволяет совместить ряд рабочих и установочных операций, что уменьшает вводимую в рабочую программу временную избыточность. 3 ил.

-я послеповательностъ выполиекня условпого модуля

2-я последовательность вылилнення условного модуля

3-я последовательность выполнения условного модуля

Ирин, ,,«„,. знаком х ово,н««но опнп иэ возможных значеннЛ. соотвётствувшх разрядов

1

- соответст

fO, если переход по комаиле IZ 1 I .г™ „.п«ft NZ 1 соответствуввие знапення лоппсских

J. если переход ло J условий переходов в условных модулях МВП.

Af

Т

М УАЗ

Алрсс устройств явода входных слов Адрес устройств вывоаа Btnojimn слов

о 1

о t о I

о I

X

Ав

Af - Р А( AS - Р А .

Л/т. г

| Анцупов С.А | |||

| и др | |||

| Диагностирование управляющих устройств по схемам алгоритмов | |||

| - Автоматика и телемеха;ника, 1986, № 10, с.132, рис.5 | |||

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-19—Подача