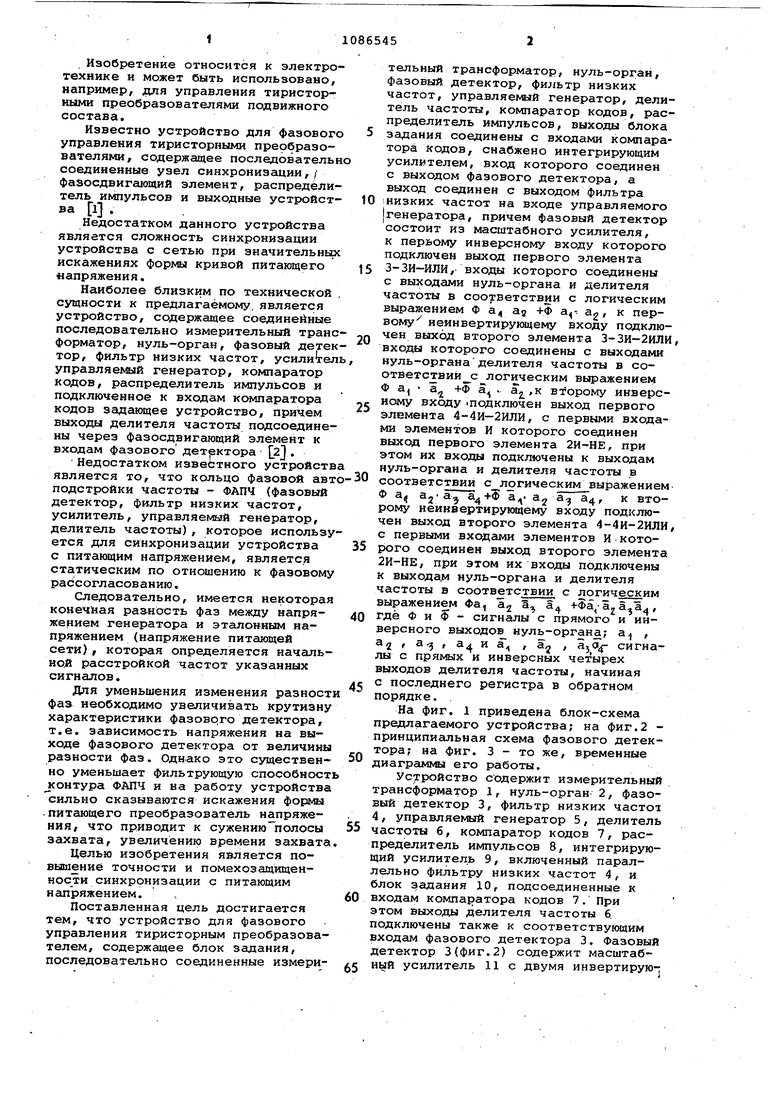

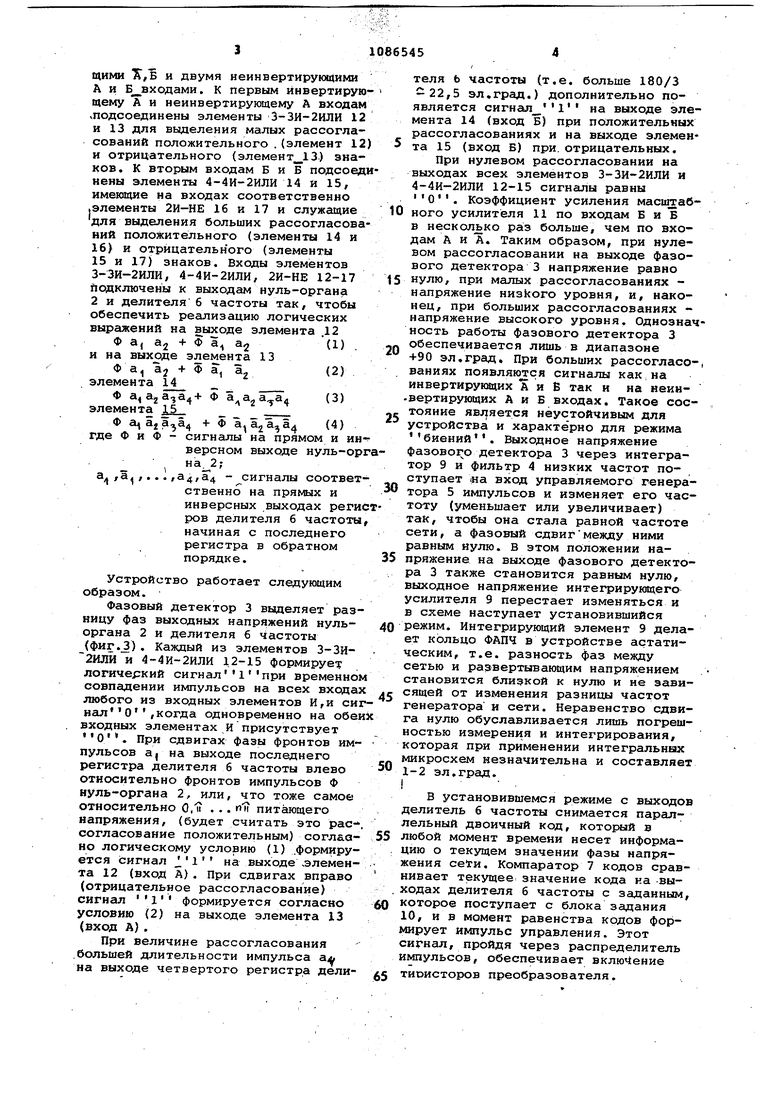

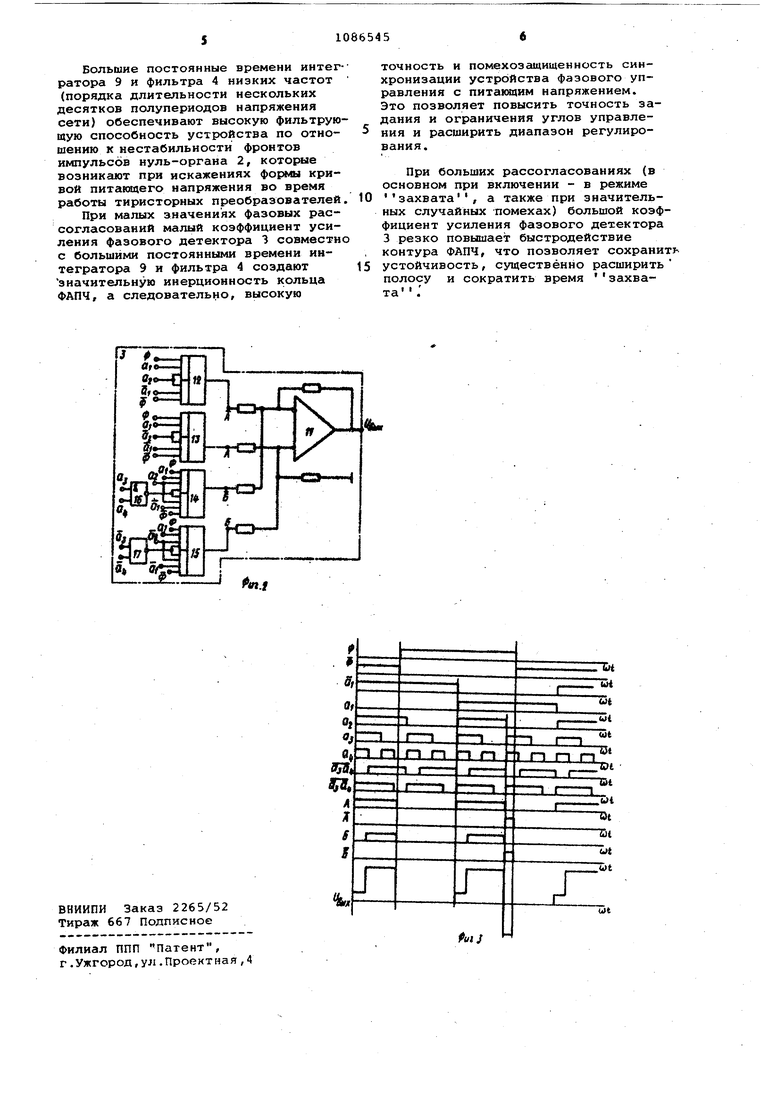

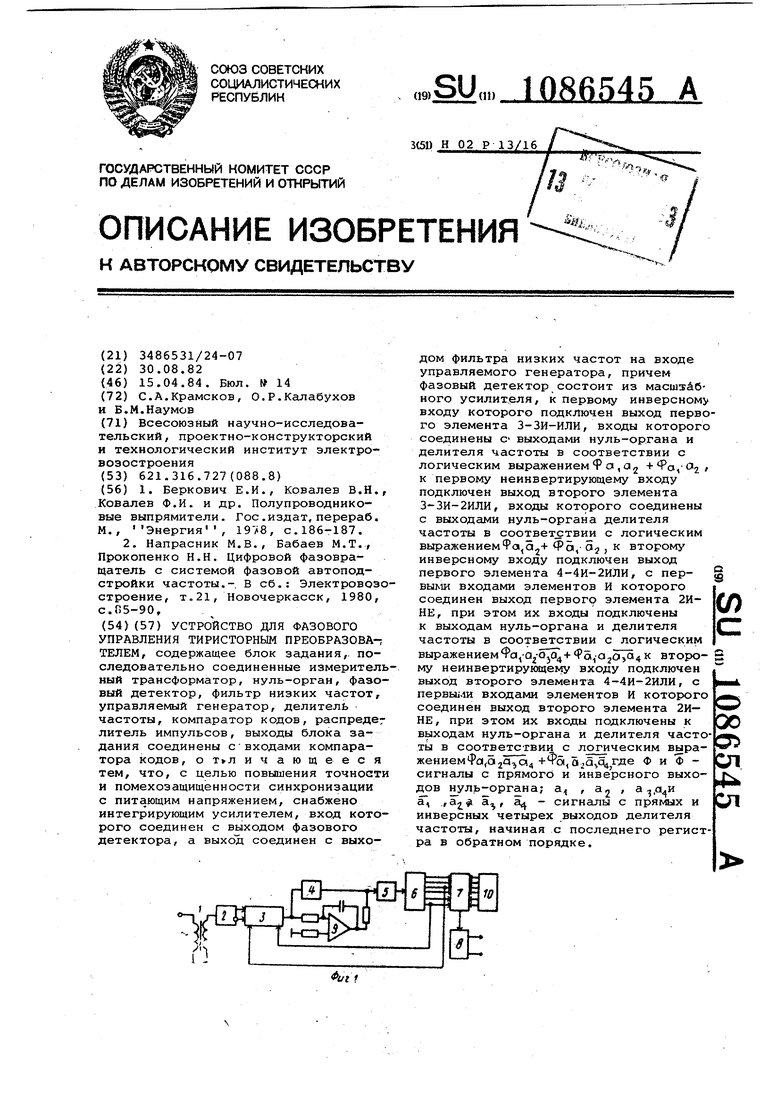

Изобретение относится к электро технике и может быть использоваво, например, для управления тиристоркыми преобразователями подвижного состава. Известно устройство для фазовог управления тиристорными прербразователями, содержащее последователь соединенные узел синхронизации, / фазосдвигающий элемент, распредели тель импульсов и выходные устройст ва l . . Недостатком данного устройства является сложность синхронизации устройства с сетью при значительнш искажениях формы кривой питающего напряжения. Наиболее близким по технической сущности к предлагаемому, является устройство, содержащее соединейные последовательно измерительный транс форматор, нуль-орган, фазовый детек тор, фильтр низких частот, усилител управляемый генератор, компаратор кодов, распределитель импульсов и подключенное к входам компаратора кодов зад «ощее устройство, причем выходы делителя частоты подсоединены через фазосдвигающий элемент к входам фазового детектора 2. Недостатком известного устройств является то, что кольцо фазовой авт подстройки частоты - ФАПЧ (фазовый детектор, фильтр низких частот, усилитель, управляемый генератор, делитель частоты), которое использу ется для синхронизации устройства с питакяцим напряжением, является статическим по отношению к фазовому рассогласованию. Следовательно, имеется некоторая конечная раз-ность фаз между напряжением генератора и эталонным напряжением (напряжение питающей сети), которая определяется начальной расстройкой частот указанных сигналов. Для уменьшения изменения разност фаз необходимо увеличивать крутизну характеристики фазового детектора, т.е. зависимость напряжения на выходе фазового детектора от величины разности фаз. Однако это существенно уменьшает фильтрующую способност контура ФАПЧ и на работу устройства сильно сказываются искажения формы .питающего преобразователь напряжения, что приводит к сужению полосы захвата, увеличению времени захвата Целью изобретения является повышение точности и помехозащищенности синхронизации с питающим напряжением. Поставленная цель достигается тем, что устройство для фазового управления тиристорным преобразователем, содержащее блок задания, последовательно соединенные измерительный трансформатор, нуль-орган, фазовый детектор, фильтр низких частот, управляемый генератор, делитель частоты, компаратор кодов, распределитель импульсов, выходы блока задания соединены с входами компаратора кодов, снабжено интегрирующим усилителем, вход которого соединен с выходом фазового детектора, а выход соединен с выходом фильтра iнизких частот на входе управляемого генератора, причем Фазовый детектор состоит из масштабного усилителя, к первому инверсному входу которого подключен выход первого элемента 3-ЗИ-ИЛИ, входы которого соединены с выходами нуль-органа и делителя частоты в соответствии с логическим выражением Ф а,| аз +Ф ag, к первому неинвертирукнцему входу подключен выход второго элемента 3-ЗИ-2ИЛИ, входы которого соединены с выходами нуль-органаделителя частоты в соответствий с логическим выражением Ф а, а +Ф а . 2. второму инверсному входу «подключен выход первого элемента 4-4И-2ИЛИ, с первыми входами элементов И которого соединен выход первого элемента 2И-НЕ, при этом их входы подключены к выходам нуль-органа и делителя частоты в соответствий с логическим вы эажениеМ а а, Ф а., ак второму неинвертирующему входу подключен выход второго элемента 4-4И-2ИЛИ, с первыми входами элементов И которого соединен выход второго элемента 2И-НЕ, при этом их входы подключены к выходам нуль-органа и делителя частоты в соответствии с логическим выражением Фа, aj а, а , где Ф и Ф - сигналы с прямого и инверсного выходов нуль-органа; а , aj , а , а и а , , сигналы с прямых и инверсных четырех выходов делителя частоты, начиная с последнего регистра в обратном порядке. , На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2 принципиальная схема фазового детектора; на фиг. 3 - то же, временные диаграммы его работы. Устройство содержит измерительный трансформатор 1, нуль-орган 2, фазовый детектор 3, фильтр низких часто 4, управляемый генератор 5, делитель частоты б, компаратор кодов 7, распределитель импульсов 8, интегрирующий усилитель 9, включенный параллельно фильтру низких частот 4, и блок задания 10, подсоединенные к входам компаратора кодов 7. При этом выходы делителя частоты 6. подключены также к соответствующим входам фазового детектора 3. Фазовый детектор 3(фиг.2) содержит масштабный усилитель 11 с двумя инвертирующими ,в и двумя неинвертирующими А и Б входами. К первым инвертирую щему А и неинвертирующему А входам чподсоединены элементы 3-ЗИ-2ИЛИ 12 и 13 для выделения малых рассогласований положительного . (элемент 12 и отрицательного (элемент 13) знаков. К вторым входам Б и Б подсоед нены элементы 4-4И-2ИЛИ 14 и 15, имеющие на входах соответственно .элементы 2И-НЕ 16 и 17 и служащие для выделения больших рассогласова ний положительного (элементы 14 и 16) и отрицательного (элементы 15 и 17) знаков. Входы элементов 3-ЗИ-2ИЛИ, 4-4И-2ИЛИ, 2И-НЕ 12-17 Подключены к выходам нуль-органа 2 и делителя6 частоты так, чтобы обеспечить реализацию логических выражений на выходе элемента .12 Ф а, aj + Ф а и на выходе элемента 13 Ф а aj + Ф а, а элемента 14 Ф а а,, Ф , элемента ,5 Ф а а + Ф а, где Ф и Ф - сигналына прямом и ин вареном выходе нуль-ор а. ,а,..,а4/а4 - сигналы соответ ственно на прямых и инверсных выходах реги ров делителя 6 частоты начиная с последнего регистра в обратном порядке. Устройство работает следующим образом. Фаэовый детектор 3 выделяет раз ницу фаз выходных напряжений нульоргана 2 и делителя 6 частоты (фиг.). Каждый из элементов 3-ЗИ 2ИЛИ и 4-4И-2ИЛИ 12-15 формирует логичеркий сигналiпри временно совпадении И1 1пульсов на всех входа любого из входных элементов И,и си нал О ,когда одновременно на обе входных элементах И присутствует О. При сдвигах фазы фронтов им пульсов aj на выходе последнего регистра делителя б частоты влево относительно фронтов импульсов Ф нуль-органа 2, или, что тоже самое относительно О, ... и питающего напряжения, (будет считать это рассогласование положительным) соглаоно логическому условию (1) .формируется сигнал на выходе -элемента 12 (вход А). При сдвигах вправо (отрицательное рассогласование) сигнал 1 формируется согласно условию (2) на выходе элемента 13 (вход А), При величине рассогласования большей длительности импульса ау на выходе четвертого регистра делителя Ь частоты (т.е. больше 180/3 - 22,5 эл.град.) дополнительно появляется сигнал 1 на выходе элемента 14 (вход Б) при положительных рассогласованиях и на выходе элемента 15 (вход Б) при. отрицательных. При нулевом рассогласовании на выходах всех элементов 3-ЗИ-2ИЛИ и 4-4И-2ИЛИ 12-15 сигналы равны О. Коэффициент усиления масштабного усилителя 11 по входам Б и Б в несколько раз больше, чем по входам А и А. Таким образом, при нулевом рассогласовании на выходе фазового детектора 3 напряжение равно нулю, при малых рассогласованиях напряжение низКого уровня, и, наконец, при больших рассогласованиях - напряжение высокого уровня. Однозначность работы фазового детектора 3 обеспечивается лишь в диапазоне +90 эл.град. При больших рассогласо-, ваниях появляются сигналы как;на инвертирующих А и В так и на неинвертирующих А и Б входах. Такое состояние является неустойчивым для устройства и характерно для режима биений Выходное напряжение фазово1го детектора 3 через интегратор 9 и фильтр 4 низких частот поступает «а вход управляемого генератора 5 импульсов и изменяет его частоту (уменьшает или увеличивает) так, чтобы она стала равной частоте сети, а фазовый сдвигмежду ними равным нулю. В этом положении напряжение на выходе фазового детектора 3 также становится равным нулю, выходное напряжение интегрирующего усилителя 9 перестает изменяться и в схеме наступает установившийся режим. Интегрирующий элемент 9 делает кольцо ФАПЧ в устройстве астатическим, т.е. разность фаз между сетью и развертывающим напряжением становится близкой к нулю и не зависящей от изменения разницы частот генератора и сети. Неравенство сдвига нулю обуславливается лишь погрешностью измерения и интегрирования, которая при применении интегральнеис микросхем незначительна и составляет 1-2 эл.град. I . В установившемся режиме с выходов делитель 6 частоты снимается параллельный двоичный код, который в любой момент времени несет информацию о текущем значении фазы напряжения сети. Компаратор 7 кодов сравнивает текущее значение кода на выходах делителя б частоты с заданным, которое поступает с блока задания 10, и в момент равенства кодов формирует импульс управления. Этот сигнал, пройдя через распределитель импульсов, обеспечивает включ1ение тиоисторов преобразователя.

Большие постоянные времени интегратора 9 и фильтра 4 низких частот (порядка длительности нескольких песятков полупериодов напряжения сети) обеспечивают высокую фильтрующую способность устройства по отношению к нестабильности ФРО« ° импульсов нуль-органа 2, которые в никают при искажениях Форм кривой питающего напряжения во время

работы тиристорных nP«°JP ° f ПРИ малых значениях фазовых рас согласований малый коэффициент усиле ия фазового детектора 3 совместн с большими постоянными времени интегратора 9 и фильтра 4 создают значительную инерционность кольца ФАПЧ, а следовательно, высокую

точность н помехозащищенность синхронизации устройства фазового управления с питающим напряжением. Это позволяет повысить точность задания и ограничения углов управления и расширить диапазон регулирования.

При больших рассогласованиях (в основном при включении - в режиме

захвата, а также при значительных случайных помехах) большой коэффициент усиления фазового детектора 3 резко повышает быстродействие контура ФАПЧ, что позволяет сохранить

устойчивость, существенно расширить полосу и сократить время захвата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Вибрационный источник сейсмических сигналов | 1985 |

|

SU1277034A1 |

| Устройство для управления положением исполнительных элементов | 1983 |

|

SU1226413A2 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО К БАЛАНСИРОВОЧНОМУ СТАНКУ | 1992 |

|

RU2054644C1 |

| Устройство для дуплексной цифровой связи | 1986 |

|

SU1408537A1 |

УСТРОЙСТВО ДЛЯ ФАЗОВОГО УПРАВЛЕНИЯ ТИРИСТОРНЫМ ПРЕОБРАЗОВА-; ТЕЛЕМ, содержащее блок задания, последовательно соединенные измерительный трансформатор, нуль-орган, фазовый детектор, фильтр низких частот, управляемый генератор, делитель частоты, компаратор кодов, распредег литель импульсов, выходы блока задания соединены свходами компаратора кодов, о ичающееся тем, что, с целью повышения точноети и помехозащищенности синхронизации с питающим напряжением, снабжено интегрирующим усилителем, вход которого соединен с выходом фазового детектора, а выхбд соединен с выходом фильтра низких частот на входе управляемого генератора, причем фазовый детектор состоит из масшзё1бного усилителя, к первому инверсному входу которого подключен выход перво го элемента 3-ЗИ-ИЛИ, входы которого соединены С выходами нуль-органа и делителя частоты в соответствии с логическим выражением ф а ,02 +Ра,-О2, к первому неинвертирующему входу подключен выход второго элемента 3-ЗИ-2ИЛИ, входы которого соединены с выходами нуль-органа делителя частоты в соответствии с логическим выражениемФа а -ь Фа, а , к второму инверсному входу подключен выход о S первого элемента 4-4И-2ИЛИ, с первыкш входами элементов И которого (Л соединен выход первого элемента 2ИНЕ, при этом их входы подключены к выходам нуль-органа и делител я частоты в соответствии с логическим выражениемРа, 5 второму неинвертирующему входу подключен выход второго элемента 4-4И-2ИЛИ, с первьи.ш входами элементов И которого соединен выход второго элемента 2И- эо 01 сл НЕ, при этом их входы подключены к выходам нуль-органа и делителя частоты в соответствии с логическим выражением Фс1,а257о|4 ,,rfle Ф и Ф сигналы с прямого и инверсного выходов нуль-орга.на; а , а , а , а, ,, а - сигналы с прямых и инверсных четырех выходов делителя частоты, начиная с последнего регистра в обратном порядке.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Беркович Е.И., Ковалев В.Н., Ковалев Ф.И | |||

| и др | |||

| Полупроводниковые выпрямители | |||

| Гос.издат, перераб | |||

| М., Энергия, 1978, с.186-187 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Напрасник М.В., Бабаев М.Т., Прокопенко Н.Н | |||

| Цифровой фазовращатель с системой фазовой автоподстройки частоты.- | |||

| В сб.: Электровозостроение, т,21, Новочеркасск, 1980, с.П5-90, | |||

Авторы

Даты

1984-04-15—Публикация

1982-08-30—Подача