сх ел

00

: Изобретение относится к электро- 4вязи и может быть использовано для Передачи информации.

Цель изобретения - повышение даль Йости передачи и повьшение помехоус- т ойчивости при мультипликативной по- NJexe.

j На фиг.1 изображена структурная электрическая схема предлагаемого у1стройства; на фиг.2 - структурная электрическая схема входного согласующего блока; на фиг.З - структурная электрическая схема восстанови- Т|еля линейного сигнала; на фиг.4 - временная диаграмма.

Устройство.для дуплексной цифрово сЬязи содержит регенератор 1, а на калздой стороне - решающий блок 2, т;риггер 3, генератор 4 импульсов,

п

;редатчик 5,, компенсатор 6, приемни

, формирователь 8 импульсов, элемен 9 и счетчик 10.

Передатчик содержит формирователь 1 линейного сигнала, элемент 2И-ИЛИ lit, делитель 13 частоты на два, пре- о разователь 14 параллельного кода в последовательный.

Приемник содержит сумматор 15 по модулю два, усилитель-ограничитель 16, входной согласующий блок 17, де- 18 и счетный триггер 19.

Компенсатор содержит операционный усилитель 20, первьш, второй, третий четвертый резисторы 21-24 соответственно.

I Регенератор содержит первьй 25 и в11орой 26 компенсаторы и первьй 27, втюрой 28 восстановители линейного сигнала.

Входной согласующий блок содержит суйматор 29, фиксатор 30 управляющего сигнала, усилитель 31 с автоматической регулировкой усиления, дифференциатор 32 и фазовый фильтр 33,

Восстановитель линейного сигнала содержит формирователь 34 линейного си нада, формирователь 35 импульсов, усилитель-ограничитель 36 и входной согласующий блок 37.

Устройство работает следующим об- ра$ом.

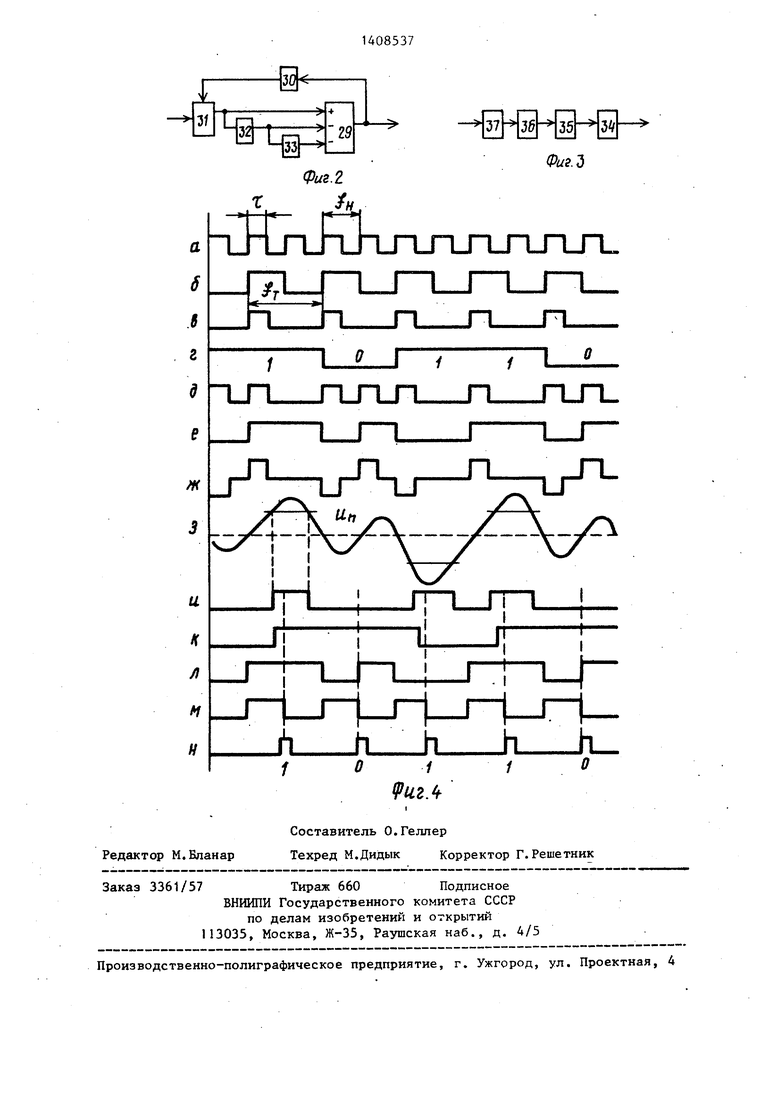

На одной стороне цифровая инфор- ма1|1ия по байтам в параллельном коде заносится в преобразователь 14 парал леЛьного кода в последовательный и считывается в последовательном коде (фИг.4г) по тактам сигнала (фиг.46) с выхода делителя 13 тактовой часто

5

0

5

0

5

0

5

5

0

ты на два. В элементе 2И-ИЛИ 12 осуществляется цифровая МОДУЛЯ1ЩЯ, т.е. формируется последовательность импульсов заданной длительности i с дискретной скважностью (фиг.4д). Генератор 4 импульсов формирует несущую частоту ц (фиг.4а). Эта частота задает скорость передачи (модуляции) цифрового сигнала. В формирователе 11 линейного сигнала последовательность импульсов преобразуется в цифровой линейный сигнал (фиг.4ж), спектр которого согласован с характеристикой канала конкретной линии связи. Сформированный линейный сигнал через резистор 22 согласования компенсатора 6 поступает в линию связи.

С линии на вход компенсатора 6 приходит сигнал, сформированньй передатчиком 5 другой стороны, который в линии претерпел изменения по уровню и по форме в соответствии с характеристикой используемого канала.

В компенсаторе 6 операционный усилитель 20 выполнен с дифференциальным каскадом на входе. Благодаря этсму он усиливает разностные выходные над-, ряжения и ослабляет синфазные. Сигнал с передатчика 5, воздействующий на инвертирующий вход операционного усилителя 20 компенсатора 6 и на неинвертирующий вход его же через резистор 22 согласования, является синфазным напряжением для обоих входов. Поэтому на выходе компенсатора 6 сигнал передатчика 5 подавлен (практически подавление может составить 90 дБ и более в зависимости от характеристик операционного усилителя 20). Приходящий сигнал с линии, сформированньй передатчиком другой стороны, воздействует только на неинвертирую- дций вход операционного усилителя 20, так как выходное сопротивление передатчика 5 близко к нулю и инвертирующий вход операционного усилителя 20 для сигнала другой стороны имеет нулевой потенциал. В результате на выходе компенсатора 6 присутствует только усиленный сигнал, приходящий

с другой стороны. I

С выхода компенсатора 6 сигнал

поступает на вход приемника 7, в ко- . тором во входном согласующем блоке 17 восстанавливаются потери в линии (усилителем 31) и устраняются фазовые искажения схемами дифференциатора 32, фазового фильтра 33 и сумматора 29.

15

25

30

Усилитель 31 выполнен по схеме с АРУ, управляющем сигналом которого является сигнал, сформированный фиксатором 30 управляющего сигнала. Суммарная передаточная характеристика канала и входного согласующего блока 17 представляет фильтр нияэ5их частот с линейной фазовой характеристикой в используемой для передачи частотной полосе. Поэтому на выходе входного согласующего блока 17 формируется сигнал (фиг.4з), огибающая которого имеет ус тойчивую нулевую линию с признаками тактовой частоты и с признаками информа1щонных символов по уровню амплитуд сигнала.

Детектор 18 выделяет импульсы при переходе сигналом установленного порогового уровня Uf, (фиг.4и), а счет- 20 ный триггер 1.9 по переднему фронту этих .импульсов меняет свое состояние (на выходе единичное или нулевое) (фиг.4к). С выхода входного согласующего блока 17 сигнал поступает также на вход усилителя-ограничителя 16, в котором формируется сигнал с крутым фронтом при переходе через нулевой уровень (фиг,4л) и далее этот сигнал в сумматоре 15 по модулю Два суммируется.с сигналом счетного триггера 19. На выходе сумматора 15 по модулю два формируется сигнал такто- вой частоты (фиг.4м), который пос- тзшает на вход формирователя 8 (коротких) импульсов. Последний по заднему фронту сигнала тактовой частоты формирует короткие импульсы (фиг.4н), которые поступают на второй вход элемента И 9. Информационный сигнал (фиг.4и) приемника 7 подключен к входу решающего блока 2 и к входу триггера 3. .

В передатчике 5 каждый байт (слово) цифровой информации сопровождается отличительным признаком (например, перед началом информационного байта посылается дополнительный единичный бит),который используется для байтовой синхронизации при передаче. По биту отличительного признака триггер 3 устанавливается в. единичное состояние, и элемент И 9 пропускает импульсы тактовой синхронизации на вход решающего блока 2 и на вход счетчика 10. По тактовьм импульсам решающего блока 2 фиксируют О или 1 из информационного сигнала (фиг.4и,н) и преобразует последовательный код в

g

10

45

35

40

50

55

5

5

0

0

параллельный по байтам. Счетчик 10 формирует импульс окончания информа- ционного байта, по которому триггер

3 сбрасывается в нулевое состояние. На инверсном выходе триггера 3 формируется синхронизируюпщй импульс, по которому в решающем блоке 2 переписывается сформированный байт в буферную (накопительную) память. По очередному отличительному биту триггер 3 устанавливается в единичное состояние и процесс приема цифровой информации повторяется.

В регенераторе 1 оба его входа являются одновременно выходами восстановленного цифрового линейного сигнала. На выходах компенсаторов 25 и 26 получают принимаемый сигнап с линии соответствующего направления (разностный сигнал), так как воста- новленный сигнал (синфазный) компенсируется. В восстановителях 27 и 28 сигнал обрабатывается во входном согласующем блоке 37, на выходе которого получают сигнал (фиг.4з). Усилительно граничитель 36 формирует сигнал (фиг.4л) с крутыми фронтами при переходе через нулевой уровень. Формирователь 35 импульсов по заднему и переднему фронтам сигнала (фиг,4л,е) формирует импульсы эталонной длительности Т, которые соответствуют длительности импульсов несущей частоты fn передатчика 5 (фиг.5д). Формирователь 34 формирует цифровой линейный сигнал (фиг.4ж)5 спектр которого согласован с характеристикой канала конкретной линии связи.

Таким образом, регенератор 1 является двусторонним ретранслятором цифрового сигнала по одной физической паре, что позволяет использовать его -в линейных трактах для передачи циф- 5 ровой информации на любые расстояния в двухпроводной системе связи. При этом скорости передачи сигналов каж-, дои стороны могут не совпадать, что не влияет на помехоустойчивость устройства и не требуется сложных адаптивных устройств ФАПЧ, так как передатчик 5 и приемник 7 не имеют допол- связей, креме информацион5

0

0

нительных ных.

55

Формула изобретения

1. З стройство для дуплексной цифровой связи, содержащее на каждой

стороне генератор импульсов, выход которого соединен с тактовым входом передатчика, выход которого подключен к входу компенсатора, выход которого соединен с входом приемника, первьй выход которого соединен с входом формирователя импульсов, и триггер, о т- личагощее ся тем, что, с повышения дальности передачи и повышения псмехоустойчивости при мультрг- пликативной помехе, введены регенератор, а на каждой стороне - решающий: блок, счетчик и элемент И, выход которого соединен с первым входом решающего блока и входом счетчика, выход которого подключен к первому входу триггера, инверсный выход которого соединен с вторым входом решающего

10

15

жит сумматор по модулю два, счетн триггер, детектор, усгатитель-огра читель и входной согласующий блок выход которого соединен с входом лителя-ограничителя и с входом де тора, выход которого соединен с з дом счетного триггера, выход кото подключен к первому входу суммато по модулю два, второй вход которо подключен к выходу усипителя-огра чителя, при этом вход входного со ласующего блока является входом п емника, первым и вторым выходами торого являются соответстенно вых сумматора по.модулю два и выход д тектора.

4, Устройство по п.1, о т л и |блока, первый вход которого подключен 20 ю щ е.е с я тем. что компенсатор

к второму выходу приемника, и к второму входу триггера, единичный выход (Которого соединен с первьм входом |элемента И, второй вход которого поддержит четыре резистора и операционный усилитель, единичный вход которого соединен с первым выводом первого резистора и первым выводом второго

ючен к выходу формирователя импуль- 25 резистора, второй вывод которого сое

жит сумматор по модулю два, счетньш триггер, детектор, усгатитель-ограни читель и входной согласующий блок, выход которого соединен с входом усилителя-ограничителя и с входом детектора, выход которого соединен с зхо- . дом счетного триггера, выход которого подключен к первому входу сумматора по модулю два, второй вход которого , подключен к выходу усипителя-ограни- чителя, при этом вход входного согласующего блока является входом приемника, первым и вторым выходами которого являются соответстенно выход сумматора по.модулю два и выход детектора.

4, Устройство по п.1, о т л и ю щ е.е с я тем. что компенсатор

ч а- содержит четыре резистора и операционный усилитель, единичный вход которого соединен с первым выводом первого резистора и первым выводом второго

резистора, второй вывод которого сое

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с двухпроводной линией приемопередатчика данных | 1986 |

|

SU1394447A1 |

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| Регенератор многоканальной цифровой системы связи | 1978 |

|

SU720756A1 |

| ЦИФРОВОЙ КАНАЛ СВЯЗИ ТЕЛЕМЕТРИЧЕСКОЙ СЕЙСМОРЕГИСТРИРУЮЩЕЙ АППАРАТУРЫ | 2000 |

|

RU2189058C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

| Приемник цифрового биполярного сигнала | 1985 |

|

SU1305889A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для дистанционного контроля линейных регенераторов | 1987 |

|

SU1418915A1 |

| Система адаптивного управления электрогидравлическим следящим приводом с контролем | 2015 |

|

RU2610851C1 |

Изобретение относится к электросвязи. Цель изобретения - ловьшение дальности передачи-и повышение помехоустойчивости при мультипликативной помехе. Устр-во содержит регенератор 1,а на каждой стороне: решающий блок 2,триггер 3, генератор 4 импульсов, передатчик 5, компенсатор 6, приемник 7, формирователь 8 импульсов, эл-т И 9 и счетчик 10. В устр-ве регенератор 1 является двусторонним ретранслятором цифрового сигнала по одной физической паре, что позволяет использовать его в линейных трактах для передачи цифровой информации на любые расстояния в двухпроводной системе связи. При зтом скорости передачи сигналов каждой стороны могут не совпадать, что не влияет на помехоустойчивость устр-ва, а также не требуется сложных адаптивных устр-в фазовой автоподстройки частоты, т.к. передатчик 5 и приемник 7 не имеют дополнительных связей, кроме информационных. Цель достигается введением регенератора 1, решающего блока 2, генератора 4 и приемника 7. Устр- во по пп.2-5 ф-лы отличается выполнением передатчика 5, приемника 7, компенсатора 6 и регенератора 1. 4 з.п. ф-ль1, 4 ил. (Л

I.

jCOB, при этом регенератор соединен JC компенсатором.

резистора второй вывод которого соединен с выходом операционного усилителя j, второй вывод, первого резистора подключен к нулевой шине, при этом выход операционного усилителя является выходом компенсатора, входом которого является второй вывод второго резистора, первый вывод которого является входом-выходом компенсатора. 5. Устройство по п. 1, о т л и ч.аю Щ е е с я тем, что регенератор содержит два восстановителя линейноТ о сигнала, первый компенсатор и второй компенсатор, выход которого соединен через второй восстановитель линейного сигнала с входом первого компенсатора, выход которого соединен с входом первого восстановителя линейного сигнала, вькод которого подключен к входу второго компенсатора, при этом входы-выходы первого и второго компенсаторов являются входами-выходами регенератора.

3f

29

Фиг.2 ///

Фиг.Ъ

.

.

иУЧ,

и

н л

м и

Фиг.Ъ

п

| Адаптивное устройство для дуплексной передачи цифровой информации | 1984 |

|

SU1195463A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-07-07—Публикация

1986-06-05—Подача