Јъ

00 СО ND

О

t14

Изобретение относится к радиотехнике и может быть использовано в быстродействующих высокоточных устройствах синхронизации, синтезаторах частоты и радиоизмерительных устройствах.

Целью изобретения является снижение уровня побочных спектральных составляющих, обусловленных помехами дискретизации, при сохранении быстродействия.

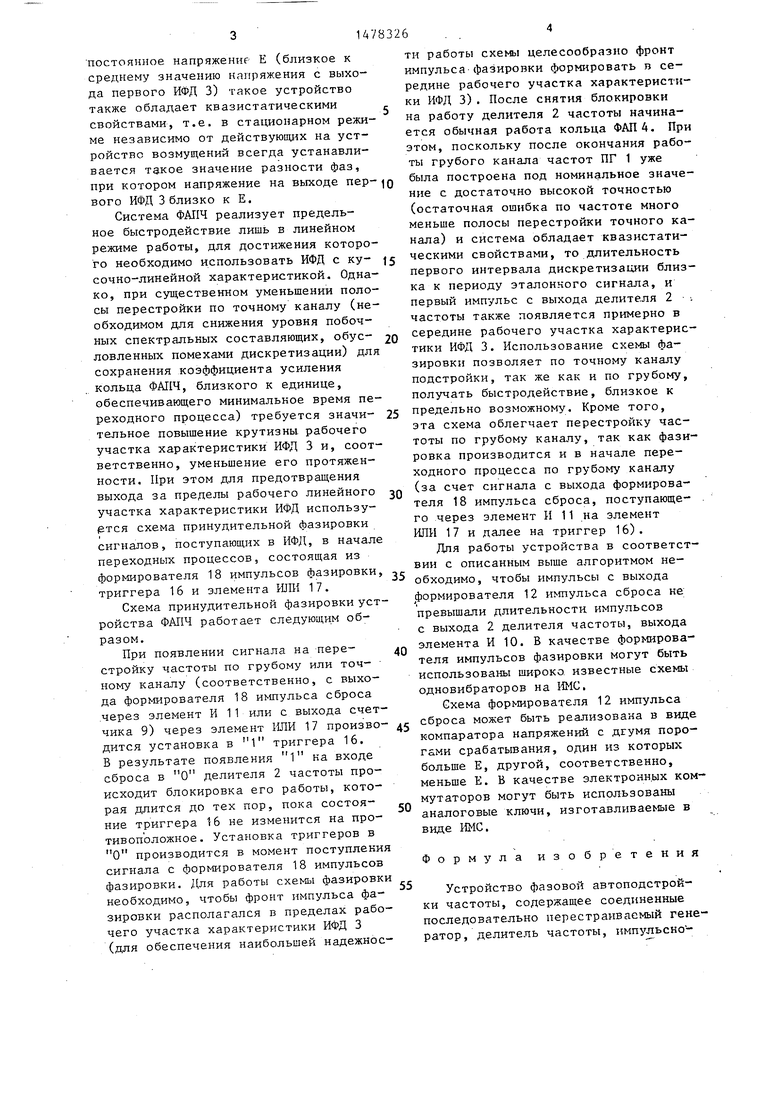

Устройство фазовой автоподстройки частоты (ФАПЧ) содержит перестраиваемый генератор (ИГ) 1, делитель 2 час

тоты, первый импульсно-фазовый детектор (ИФД) 3, фильтр 4 нижних частот (ФНЧ), эталонный генератор 5, первый электронный коммутатор 6, второй ИФД 7 и аналого-цифровой преобразователь (АЦП) 8, образующие цифровой фазовый детектор 9, элемент И-НЕ 10, элемент И 11, формирователь 12 импульса сброса, счетчик 13, цифроаналоговый преобразователь (ПАП) 14, второй элект- 25 частотой дискретизации с выхода дели

0

ляющий вход Г1Г1 подается с выхода второго ИФД 7) с оптимальным коэффициентом усиления кольца, равным единице. При этом переходной процесс за- вершается за один интервал дискретизации. Отметим, что наличие нелиней- ностей характеристик узлов устройства, а также появление запаздывания может несколько увеличить время переходного процесса, по сравнению с минимально достижимым значением, в связи с чем, при реализации устройства на это следует обращать особое внимание. Для надежной работы системы в широком диапазоне частот при действии различных возмущений время, отводимое на перестройку по грубому каналу, может быть задано несколько больше, чем один интервал дискретизации. Это время устанавливается выбором емкости счетчика, который, отсчитав заданное количество импульсов, поступающих на его счетный вход с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1091354A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Устройство для анализа периодических сигналов | 1981 |

|

SU978066A1 |

| ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ ПОДСТРОЙКОЙ ЧАСТОТЫ | 1992 |

|

RU2060584C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Цифровой телевизионный приемник | 1983 |

|

SU1321384A3 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

Изобретение относится к радиотехнике. Цель изобретения - снижение уровня побочных спектральных составляющих, обусловленных помехами дискретизации, при сохранении быстродействия. Устройство содержит перестраиваемый г-р 1, делитель 2 частоты, импульсно-фазовый детектор (ИФД) 3, фильтр 4 нижних частот, эталонный г-р 5, электронные коммутаторы 6 и 15, цифровой фазовый детектор 9, состоящий из ИФД 7 и АЦП 8, эл-т И-НЕ 10, эл-т И 11, формирователь 12 импульса сброса, счетчик 13, ЦАП 14, триггер 16, эл-т ИЛИ 17, формирователь 18 импульсов фазировки и источник 19 постоянного напряжения. Для предотвращения выхода за пределы рабочего линейного участка х-ки ИФД 3 используется схема принудительной фазировки сигналов, поступающих в ИФД 3, в начале переходных процессов, состоящая из триггера 16, эл-та ИЛИ 17 и формирователя 18. Использование схемы принудительной фазировки позволяет по точному каналу подстройки, также, как и по грубому, получать быстродействие, близкое к предельно возможному. Цель достигается введением коммутатора 15 и схемы принудительной фазировки сигналов. 1 ил.

ронный коммутатор 15, триггер 16, элемент ИЛИ 17, формирователь 18 импульсов фазировки и источник 19 постоянного напряжения.

Устройство работает следующим образом.

При поступлении возмущающего воздействия на вход устройства или изменении коэффициента деления делителя 2 частоты (по команде на изменение выходной частоты) на выходе первого ИФДЗ возникает сигнал рассогласования, поступающий на формирователь 12 импульса сброса, с выхода которого через элемент И 11 поступают сигналы на сброс счетчика 9 в О и установку начального состояния АЦП 8. При этом сигнал с выхода счетчика 9 устанавливает первый электронный коммутатор 6 на подключение к его выходу ис- 4с процесса аналого-цифрового преобразо i „-

точника 19 постоянного напряжения, а сигнал с выхода окончания преобразования АЦП 8 осуществляет в втором электронном коммутаторе 15 соединение второго управляющего входа ПГ1 с выходом второго ИФД 7. На этом завершается установка устройства ФАПЧ в начальное состояние, после чего начинается подстройка частоты по грубому каналу управления.

На первом этапе грубой подстройки устройство работает по принципу бесфильтровой линейной системы ФАПЧ (так как напряжение на второй управ50

55

вания сигналом Окончание преобразования второй электронный коммутатор 15 осуществляет переключение второго управляющего входа (грубой подстройки) ПГ 1 с выхода второго ИФД 7 на выход ЦАП 14. Возникающая после этого ошибка квантования при выборе достаточно большого числа разрядов в АЦП 8 и ЦАП 14 оказывается весьма незначительной и достаточно быстро обрабатывается точным каналом подстройки. Поскольку в устройстве во время работы грубого канала подстройки на выходе точного канала поддерживается

теля 2 частоты, через элемент И-НЕ 10 вырабатывает сигнал на переход к следующему этапу перестройки.

Этим сигналом осуществляется:

0 отключение счетного входа счетчика для предотвращения изменения его состояния элементом И-НЕ 10; запуск АЦП 8 за счет подачи сигнала разрешения преобразования; подключение первым электронным коммутатором к первому управляющему входу (точкой подстройки) ПГ1 вместо источника 19 постоянного напряжения с выхода точного канала подстройки; снятие запрета на

Q прохождение сигнала от формирователя 12 импульса сброса через элемент И11, действовавшего во время переходного процесса для предотвращения сбоев в работе устройства. После завершения

5

процесса аналого-цифрового преобразо i „-

вания сигналом Окончание преобразования второй электронный коммутатор 15 осуществляет переключение второго управляющего входа (грубой подстройки) ПГ 1 с выхода второго ИФД 7 на выход ЦАП 14. Возникающая после этого ошибка квантования при выборе достаточно большого числа разрядов в АЦП 8 и ЦАП 14 оказывается весьма незначительной и достаточно быстро обрабатывается точным каналом подстройки. Поскольку в устройстве во время работы грубого канала подстройки на выходе точного канала поддерживается

постоянное напряжешь Е (близкое к среднему значению напряжения с выхода первого ИФД 3) такое устройство также обладает квазистатическими свойствами, т.е. в стационарном режиме независимо от действующих на устройство возмущений всегда устанавливается такое значение разности фаз, при котором напряжение на выходе первого ИФД 3 близко к Е.

Система ФАГ1Ч реализует предельное быстродействие лишь в линейном режиме работы, для достижения которого необходимо использовать ИФД с ку- сочно-линейной характеристикой. Однако, при существенном уменьшении полосы перестройки по точному каналу (необходимом для снижения уровня побочных спектральных составляющих, обус- ловленных помехами дискретизации) для сохранения коэффициента усиления кольца ФА11Ч, близкого к единице, обеспечивающего минимальное время переходного процесса) требуется значи- тельное повышение крутизны рабочего участка характеристики ИФД 3 и, соответственно, уменьшение его протяженности. При этом для предотвращения выхода за пределы рабочего линейного участка характеристики ИФД используется схема принудительной фазировки сигналов, поступающих в ИФД, в начале переходных процессов, состоящая из формирователя 18 импульсов фазировки, триггера 16 и элемента ИЛИ 17.

Схема принудительной фазировки устройства ФАГИ работает следующим образом.

При появлении сигнала на пере- стройку частоты по грубому или точному каналу (соответственно, с выхода формирователя 18 импульса сброса через элемент И 11 или с выхода счетчика 9) через элемент ИЛИ 17 произво- дится установка в 1 триггера 16. В результате появления 1 ка входе сброса в О делителя 2 частоты происходит блокировка его работы, которая длится до тех пор, пока состоя- ние триггера 16 не изменится на противоположное. Установка триггеров в О производится в момент поступления сигнала с формирователя 18 импульсов фазировки. Для работы схемы фазировки необходимо, чтобы фронт импульса фазировки располагался в пределах рабочего участка характеристики ИФД 3 (для обеспечения наибольшей надежности работы схемы целесообразно фронт импульса фазировки формировать в середине рабочего участка характеристики ИФД 3). После снятия блокировки на работу делителя 2 частоты начинается обычная работа кольца ФАЛ 4. При этом, поскольку после окончания работы грубого канала частот ПГ 1 уже была построена под номинальное значение с достаточно высокой точностью (остаточная ошибка по частоте много меньше полосы перестройки точного канала) и система обладает квазнстати- ческими свойствами, то длительность первого интервала дискретизации близка к периоду эталонного сигнала, и первый импульс с выхода делителя 2 частоты также появляется примерно в середине рабочего участка характеристики ИФД 3. Использование схемы фазировки позволяет по точному каналу подстройки, так же как и по грубому, получать быстродействие, близкое к предельно возможному. Кроме того, эта схема облегчает перестройку частоты по грубому каналу, так как фази- ровка производится и в начале переходного процесса по грубому каналу (за счет сигнала с выхода формирователя 18 импульса сброса, поступающего через элемент И 11 на элемент ИЛИ 17 и далее на триггер 16).

Для работы устройства в соответствии с описанным выше алгоритмом необходимо, чтобы импульсы с выхода формирователя 12 импульса сброса не превышали длительности импульсов с выхода 2 делителя частоты, выхода элемента И 10. В качестве формирователя импульсов фазировки могут быть использованы широко известные схемы одновибраторов на ИМС.

Схема формирователя 12 импульса сброса может быть реализована в виде компаратора напряжений с дгумя порогами срабатывания, один из которых больше Е, другой, соответственно, меньше Е. В качестве электронных коммутаторов могут быть использованы аналоговые ключи, изготавливаемые в виде ИМС.

Формула изобретения

Устройство фазовой автоподстройки частоты, содержащее соединенные последовательно перестраиваемый генератор, делитель частоты, кмпульско514783266

фазовый детектор, другой вход которо- действия, в него введены элемент ИЛИ, го подключен к выходу эталонного генератора, фильтр нижних частот и электронный коммутатор, к другому входу которого подключен источник постоянного напряжения, последовавходы которого подключены к выходам счетчика, и элемента И соответственно, формирователь импульсов фазиров- ки, подключенный к выходу эталонного

генератора, триггер, вход установки в 1 которого подключен к выходу элемента ИЛИ, вход сброса - к выходу

тельно соединенные элемент И-НЕ и счетчик, включенные между выходом

делителя частоты и управляющим входом ю Формирователя импульсов фазировки,

электронного коммутатора, последовательно соединенные формирователь импульса сброса и элемент И, другой вход которого подключен к выходу счетчика, включенные между выходом импульсно-фазового детектора и входом сброса счетчика, а также цифровой фазовый детектор, входы которого подключенных к входам импульсно-фазово- го детектора, и цифроаналоговый преобразователь, выход которого подключен к первому управляющему входу перестраиваемого генератора, второй управляющий вход которого подключен к выходу1 электронного коммутатора, а инверсный вход элемента И-НЕ подключен к выходу счетчика, о т л и ч а ю- щ е е с я тем, что, с целью снижения уровня побочных спектральных составляющих, обусловленных помехами дискретизации, при сохранении быстро-

действия, в него введены элемент ИЛИ,

входы которого подключены к выходам счетчика, и элемента И соответственно, формирователь импульсов фазиров- ки, подключенный к выходу эталонного

действия, в него введены элемент ИЛИ,

генератора, триггер, вход установки в 1 которого подключен к выходу элемента ИЛИ, вход сброса - к выходу

выход - к входу сброса делителя частоты,, и второй электронный коммутатор, цифровой фазовый детектор выполнен в виде последовательно соединенных дополнительного импульсно-фазово- го детектора и аналого-цифрового преобразователя, при этом выход цифро- аналогового преобразователя подключен к первому управляющему входу перестраиваемого генератора через второй электронный коммутатор, второй вход которого подключен к выходу дополнительного импульсно-фазового детектора, вход управления - к выходу окончания преобразования аналого-цифрового преобразователя, входы начальной установки и разрешения преобразования которого подключены к выходу элемента И и выходу счетчика соответственно.

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1091354A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1987-04-21—Подача