Изобретение относится к радиотехнике и может быть использовано в приемо-передающей аппаратуре и в контрольно-измерительных устройствах.

Цель изобретения - повьппение быстродействия синтезатора частот.

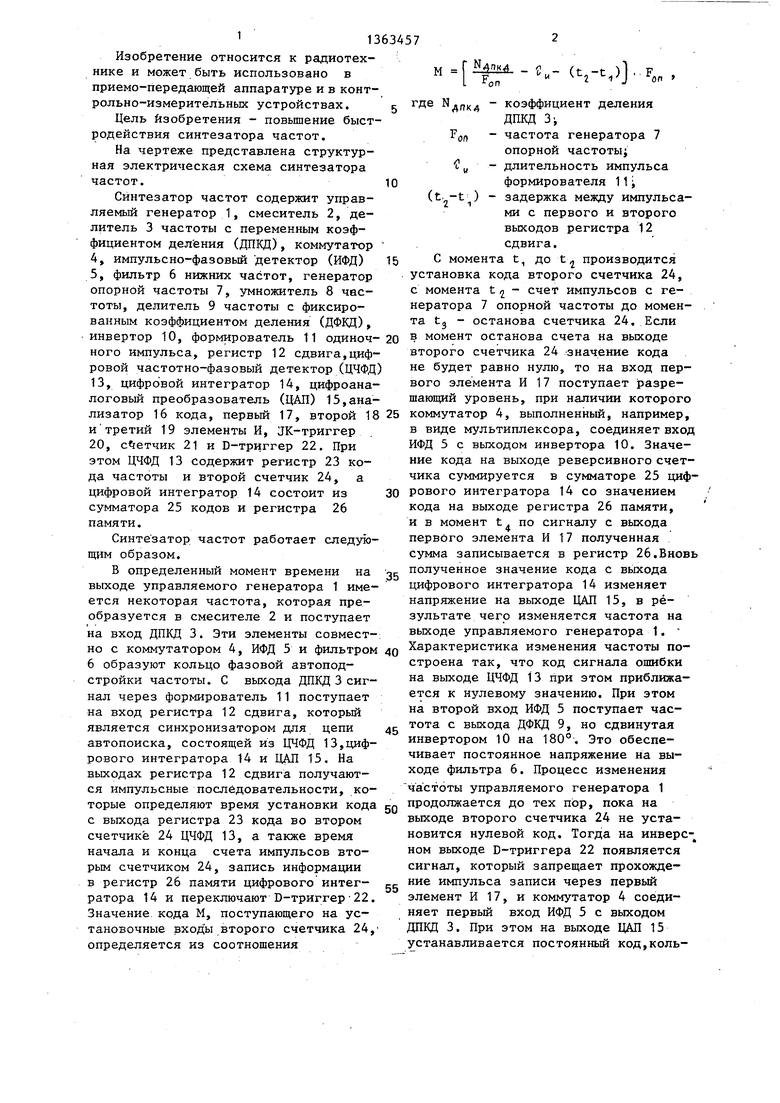

На чертеже представлена структурная электрическая схема синтезатора частот.

Синтезатор частот содержит управляемый генератор 1, смеситель 2, делитель 3 частоты с переменным коэффициентом дел ения (ДПКД), коммутатор

4,импульсно-фазовый детектор (ИФД)

5,фильтр 6 нижних частот, генератор опорной частоты 7, умножитель 8 частоты, делитель 9 частоты с фиксированным коэффициентом деления (ДФКД), инвертор 10, формирователь 11 одиноч- ного импульса, регистр 12 сдвига,цифровой частотно-фазовый детектор (ЦЧФД 13, цифровой интегратор 14, цифроана- логовый преобразователь (ЦАП) 15,анализатор 16 кода, первьй 17, второй 18 и третий 19 элементы И, JK-триггер

20, с гетчик 21 и D-триггер 22. При этом ЦЧФД 13 содержит регистр 23 кода частоты и второй счетчик 24, а цифровой интегратор 14 состоит из сумматора 25 кодов и регистра 26 памяти.

Синтезатор частот работает следующим образом.

В определенный момент времени на выходе управляемого генератора 1 имеется некоторая частота, которая преобразуется в смесителе 2 и поступает на вход ДПКД 3. Эти элементы совместно с коммутатором 4, ИФД 5 и фильтром 6 образуют кольцо фазовой автоподстройки частоты. С выхода ДПКД3 сигнал через формирователь 11 поступает на вход регистра 12 сдвига, который является синхронизатором для цепи автопоиска, состоящей из ЦЧФД 13,цифрового интегратора 14 и ЦАП 15. На выходах регистра 12 сдвига получаются импульсные последовательности, которые определяют время установки кода с выхода регистра 23 кода во втором счетчике 24 ЦЧФД 13, а также время начала и конца счета импульсов вторым счетчиком 24, запись информации в регистр 26 памяти цифрового интег- ратора 14 и переключают D-триггер22. Значение кода М, поступающего на установочные вход ы второго счетчика 24, определяется из соотношения

-С,- (t,-tp,.F

on

on

(Vt)

где - коэффициент деления ДПКД 3,

частота генератора 7 опорной частоты; длительность импульса формирователя 11 ; задержка между импульсами с первого и второго выходов регистра 12 сдвига.

С момента t, до t производится установка кода второго счетчика 24, с момента t - счет импульсов с генератора 7 опорной частоты до момента tj - останова счетчика 24. Если в момент останова счета на выходе второго счетчика 24 значение кода не будет равно нулю, то на вход первого элемента И 17 поступает разрешающий уровень, при наличии которого коммутатор 4, выполненный, например, в виде мультиплексора, соединяет вхо ИФД 5 с выходом инвертора 10. Значение кода на выходе реверсивного счетчика суммируется в сумматоре 25 цифрового интегратора 14 со значением кода на выходе регистра 26 памяти, и в момент t по сигналу с выхода первого элемента И 17 полученная сумма записывается в регистр 26.Внов полученное значение кода с выхода цифрового интегратора 14 изменяет напряжение на выходе ЦАП 15, в результате чего изменяется частота на выходе управляемого генератора 1. Характеристика изменения частоты построена так, что код сигнала ошибки на выходе ЦЧФД 13 при этом приближается к нулевому значению. При этом на второй вход ИФД 5 поступает частота с выхода ДФКД 9, но сдвинутая инвертором 10 на 180°. Это обеспечивает постоянное напряжение на выходе фильтра 6. Процесс изменения

частоты управляемого генератора 1 продолжается до тех пор, пока на выходе второго счетчика 24 не установится нулевой код. Тогда на инверс ном выходе D-триггера 22 появляется сигнал, который запрещает прохождение импульса записи через первый элемент И 17, и коммутатор 4 соединяет первый вход ИФД 5 с выходом ДПКД 3. При этом на выходе ЦАП 15 устанавливается постоянный код,коль3136345

цо фазовой автоподстройки включается и в синтезаторе частот устанавливается режим фазовой синхронизации.

Если синтезатор частот выйдет из g режима фазовой синхронизации, то вновь код на выходе ЦЧФД 13 будет отличен от нуля и на вход второго элемента И 18 через анализатор кода 16 поступает сигнал логической еди-- 10 ницы. Если в этот момент на второй вход второго элемента И 18 поступает уровень логического нуля, то D- триггер 22 по сигналу с регистра 12 сдвига переключается в единичное состояние. В таком же состоянии наодится и JK-триггер 20, при этом заканчивается сигнал установки в нуль счетчика 21 и на входе третьего элемента И 19 устанавливается разрешающий уровень. Счетчик 21 начинает счет импульсов с генератора 7 опорной частоты, пока на его выоде не появится сигнал логической единицы, который обнуляет JK-триг- гер 20. При этом D-триггер 22 по сигналу с регистра 12 сдвига устанавливается в нулевое состояние и на установочном входе счетчика 21 появляется сигнал установки нуля. После того, как с инверсного выхода -триггера 22 на второй вход первого элемента И 17 поступает разрешающий потенциал, включается цепь автопоиска, а коммутатор 4 соединяет вход ИФД 5 с входом инвертора 10. Еси на выходе ЦЧФД 13 значение кода

соответствует нулевому, то на выхое второго элемента И 18 будет уровень логической единицы. При помощи сигнала с соответствующего выхода регистра 12 сдвига переключается D- триггер 22, который дает запрет для первого элемента И 17, и коммутатор 4 подключает вход ИФД 5 к входу ДПКД 3. В этот момент начинается переходный процесс установления фазы колебаний управляемого генератора 1. Даее переключается JK-триггер 20, который блокирует второй элемент И 18 и разрешает счет импульсов счетчиком 21.

Блокировка держится до тех пор, пока на выходе счетчика 21 не появит-

ся логическая единица, которая уста- 3-входом ЭК-триггера, тактовый вход

навливает ЗК-триггер 20 в нулевое состояние. Таким образом, если даже на выходе ЦЧФД 13 значение кода отлично от нуля, что возможно при пё5которого объединен с первым входом третьего элемента И, с тактовым входом регистра сдвига, с первым входом формирователя одиночного импульса и

реходном процессе, второй элемент И 18 не изменяет своего состояния, а следовательно, цепь автопоиска не включается повторно. Это обеспечивает устойчивость работы синтезатора частот в режиме переходного процесса вследствие чего уменьшается время вхождения в синхронизм. Время блокировки определяется из расчета времени переходного процесса установления фазы.

Формула изобретения

0

5

0

5

0

Синтезатор частот, содержащий соединенные в кольцо управляемый генератор, смеситель, делитель частоты с переменным коэффициентом деления,коммутатор, импульсно-фазовый детектор и фильтр нижних частот, последовательно соединенные генератор опорной частоты и умножитель частоты, выход которого подключен к другому входу смесителя, последовательно соединенные цифровой частотно-фазовый детектор и цифровой интегратор, а также цифроаналоговый преобразователь, выход которого подключен к управляющему входу управляемого генератора,анализатор кода, вход которого соединен с выходом цифрового частотно-фазового детектора, первый вход которого подключен к выходу генератора опорg ной частоты, ЛК-триггер, D-триггер и счетчик, отличающийся тем, что, с целью повышения быстродействия, в него введены последовательно соединенные делитель частоты

0 с фиксированным коэффициентом деления и инвертор, последовательно соединенные формирователь одиночного импульса, регистр сдвига и первый элемент И, а также второй элемент И и третий элемент И, при этом выход первого элемента И соединен с тактовым входом цифрового интегратора, выход которого подключен к входу циф- роаналогового преобразователя, второй вход первого элемента И объединен с установочным входом счетчика и с управляющим входом коммутатора и подключен к инверсному выходу D-триггера, прямой выход которого соединен с

3-входом ЭК-триггера, тактовый вход

5которого объединен с первым входом третьего элемента И, с тактовым входом регистра сдвига, с первым входом формирователя одиночного импульса и

1

с входом делителя частоты с фиксированным коэффициентом деления и подключен к выходу генератора опорной частоты, второй вход формирователя одиночно1 о импульса соединен с выходом делителя частоты с переменным ко эффициентом деления, второй, третий и четвертый выходы регистра сдвига соединены соответственно с вторым входом цифрового частотно-фазового детектора, с управляющим входом цифрового частотно-фазового детектора, с тактовым входом D-триггера, первый и второй входы и выход второго эле63457

мента И подключены соответственно к выходу анализатора кода, к инверсному выходу JK-триггера и к D-входу D- g триггера, второй вход и выход третьего элемента И соединены соответственно с прямым выходом ЗК-триггера и с тактовым входом счетчика, выход которого подключен к установочному 10 входу JK-триггера, выход делителя частоты с фиксированным коэффициентом деления соединен с вторым входом импульсно-фазового детектора, а выход инвертора подключен к второму 15 входу коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1494215A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой синтезатор частоты | 1980 |

|

SU987817A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Цифровой синтезатор частоты | 1985 |

|

SU1325693A1 |

Изобретение относится к радиотехнике и обеспечивает расширение динамического диапазона и повьппение линейности детектирования. Выбором -величины резистора 3 достигается такое положение, когда на входном конденсаторе (к) 2 возникает напряжение, равное величине изменения напряжения на К 8, чем определяется стабильность угла отсечки входного напряжения в базоэммитерном переходе транзистора 1 при измерении уровня ВЧ-сигнала,. и тем самым обеспечивается расширение динамич. диапазона и повышение линейности детектирования. 1 ил. сл со О) со 4 СЛ

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-30—Публикация

1985-05-20—Подача