в

IB

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1988 |

|

SU1538253A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2011 |

|

RU2477920C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1774465A2 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2014733C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1985 |

|

SU1336231A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1704266A1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение девиации выходного колебания и стабильности его несущей частоты. Синтезатор содержит ключи 1,16,18 и 20, интегрирующие фильтры 2,17,19 и 21, фильтр 3 нижних частот, перестраиваемый генератор 4, делитель 5 частоты с переменным коэффициентом деления, коммутаторы 6,9 и 14, фазовый детектор 7, источник 8 модулирующего сигнала, управляемые аттенюаторы 10 и 15, блок смещения 11 напряжения, интегратор 12, фазовый модулятор 13, компараторы 22 и 23, элемент ИЛИ 24, блок управления 25, опорный генератор 26, элемент задержки 27, блок установки 28 частоты и генератор 29 стандартного напряжения. При модуляции выходной частоты синтезатора осуществляется режим двухточечной модуляции в кольце фазовой автоподстройки частоты (ФАПЧ) генератора 4. При этом кольцо ФАПЧ периодически размыкается для включения режима подстройки цепи интегратора 12, а также для его сброса. Потенциал управления генератором 4 на время размыкания кольца ФАПЧ запоминается и хранится в фильтре 2. При переходе от одного режима к другому и при каждом сбросе интегратора 12 осуществляется "привязка" разности фаз импульсов на входах детектора 7 за счет введения дополнительного кольца ФАПЧ. 2 ил.

СП

4

со ел

Јь

иия, интегратор 12, фазовый модуля- top 13, компараторы 22 и 23, элемент ИЛИ 24, блок 25 управления, опорный Генератор 26, элемент 27 задержки, флок 28 установки частоты и генератор 29 стандартного напряжения. При модуляции выходной частоты синтезатора Осуществляется режим двухточечной модуляции в кольце фазовой автопод- Стройки частоты (ФАПЧ) генератора 4. фри этом кольцо ФАПЧ периодически

Изобретение относится к радиотехнике и может быть использовано в нозбудителе передатчика с широкополосной частотной модуляцией. Цель изобретения - увеличение девиации выходного колебания и ста- рильности его несущей частоты.

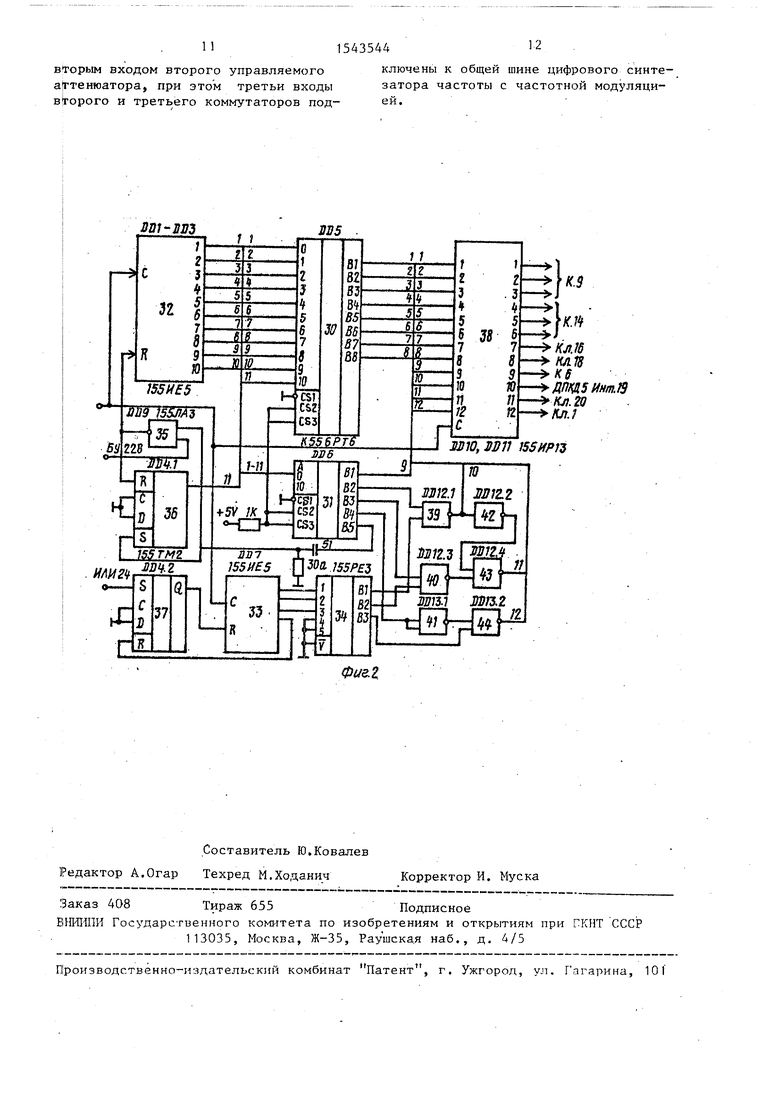

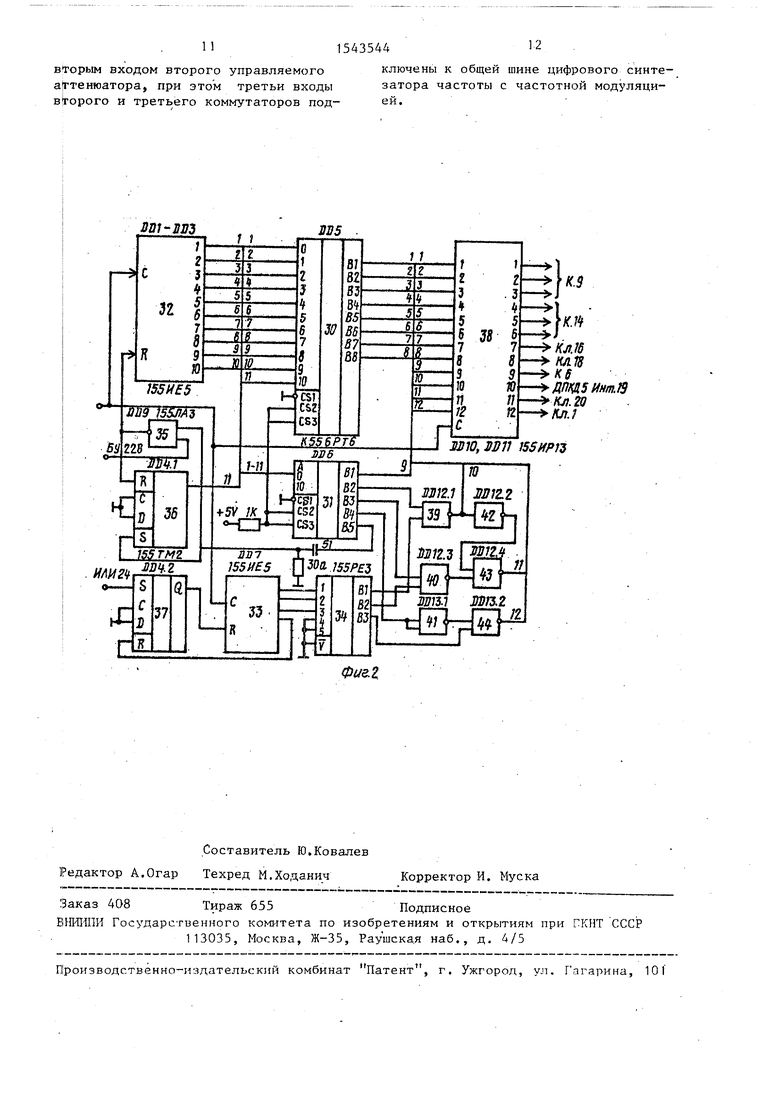

На фиг. 1 представлена структур- tjiaH электрическая схема цифрового Синтезатора частоты с частотной моду- 4яцией; на фиг. 2 - схема блока управления, пример исполнения.

Цифровой синтезатор частоты с час- ротной модуляцией содержит первый ключ 1, первый интегрирующий фильтр 4,фильтр 3 нижних частот (ФНЧ), пере- траиваемый генератор 4, делитель 5 Частоты с переменным коэффициентом Деления (ДПКД), первый коммутатор 6S фазовый детектор (ФД) 7, источник 8 модулирующего сигнала (ИМС), второй коммутатор 9, первый управляемый аттенюатор 10, блок 11 смещения напря- Зкения, интегратор 12, фазовый модулятор 13, третий коммутатор 14, второй управляемый аттенюатор 15, второй ключ 16, второй интегрирующий фильтр 17, третий ключ 18, третий интегри- рующий фильтр 19, четвертый ключ 20, четвертый интегрирующий фильтр 21, первый компаратор 22, второй компаратор 23, элемент ИЛИ 24, блок 25 управления, опорный генератор 26„ эле- мент 27 задержки, блок 28 установки частоты (БУЧ) и генератор 29 стандарного напряжения.

Блок 25 управления включает первый 30 и второй 31 блоки памяти, первый 32 и второй 33 счетчики, третий блок 34 памяти, первый элемент И 35, первый 36 и второй 37 RS-триггеры,

размыкается для включения режима подстройки цепи интегратора 12, а также для его сброса. Потенциал управления генератором 4 на время размыкания кольца ФАПЧ запоминается и хранится в фильтре 2. При переходе от одного режима к другому и при каждом сбросе интегратора 12 осуществляется привязка разности фаз импульсов на входах детектора 7 за счет введения до- полнителъного кольца ФАПЧ. 2 ил.

0

5

0 5 0 5 0

регистр 38 и с первого по шестой элементы ИЛИ 39 - 44.

Цифровой синтезатор частоты с частотной модуляцией работает следующим образом.

При модуляции выходной частоты синтезатора осуществляется режим двухточечной модуляции в кольце фазовой автоподстройки частоты перестраиваемого генератора 4. При этом кольцо подстройки периодически размыкается для включения режима подстройки цепи интегратора 12, а также для сброса интегратора 12 при достижении на его выходе определенного напряжения ±U. Потенциал управления перестраиваемым генератором 4 на время размыкания кольца автоподстройки запоминается и хранится в первом интегрирующем фильтре 2. При переходе от одного режима к другому и при каждом сбросе интегратора 12 осуществляется привязка разности фаз импульсов на входах ФД 7 за счет введения дополнительного кольца автоподстройки. При переходе на новую частоту по строби- рующему импульсу с БУЧ 28 код новой частоты подается на установочный вход ДПКД 5 и на управляющий вход первого управляемого аттенюатора 10. По сигналам с первого и второго кодовых выходов блока 25 управления на выходах второго и третьего коммутаторов 9 и 14 устанавливается нулевой уровень сигнала, сбрасывается интегра- . тор 1,2 .и предустанавливается ДПКД 5,

после чего открывается первый ключ 1 и происходит перестройка перестраиваемого генератора 4 на новую частоту сигналом с выхода ФД 7 по цепи: первый ключ 1, первый инте рирующий .фильтр 2,ФНЧ 3. После перестройки по

сигналу с блока 25 управления закры- , вается первый ключ 1 и открывается второй ключ 16, а на выходы второго

и третьего коммутаторов 9 и 14 посту-

пает напряжение с выхода генератора

По окончании режима коррекции осуществляется режим подстройки цели интегратора 12. По сигналам с блока 25 управления закрывается второй ключ 16, сбрасывается интегратор 12 и предустанавливается ДПКД 5. На вход третьего коммутатора 14 передается сигнал с выхода ИМС 8, на вход второго коммутатора 9 подается нулевой уровень напряжения, а на выход первого коммутатора 6 подаются импульсы с Йыхода опорного генератора 26. Для устранения скачков разности фаз импульсов на входах ФД 7 на два - четы- ре импульса включается кольцо привязки разности фаз, для чего открывается четвертый ключ 20 и сигнал с выхода ФД 7 через четвертый ключ 20 и

четвертый интегрирующий фильтр 21 по7 ступает на первый вход фазового моIг

дулятора 13. Напряжение на выходе четвертого интегрирующего фильтра 21 меняется до тех пор, пока разность фаз импульсов на- входах ФД 7 не будет равна нулю.

Кольцо привязки разности фаз представляет собой астатическое кольцо подстройки фазы первого порядка, переходные процессы в котором с высокой точностью заканчивается за 2-4 шага подстройки, затем четвертый ключ 20 закрывается, открывается третий ключ 18 и сигнал с выхода ФД 7 через третий интегрирующий фильтр 19 поступает на второй вход блока 11 смещения. В результате подстройки напряжение на втором входе блока 11 смещения устанавливается таким, чтобы выходное напряжение интегратора 12 не изменялось и било равно нулю.При этом на входах ФД 7 устанавливаются одинаковые частоты импульсов и нулевая разность фаз за счет применения третьего интегрирующего фильтра 19. Для достижения этого введен элемент 27 задержки. Он задерживает импульсы с опорного генератора 26 на половину периода их следования. Подстройка цепи интегратора обеспечивает высокую долговременную стабильность несущей частоты выходного сигнала (при нулевом напряжении с выхода ИМС 8 частота следования импульсов на выходе фазового модулятора 13 точно равна частоте опорного генератора 26). При осуществлении модуляции частоты выходного сигнала режим подстройки цепи интегратора 12 циклически повторяется. Для перехода к режиму модуляции по сигналам с блока 25 управления сбрасывается интегратор 12 и предустанавливается ДПКД 5, на выход второго коммутатора 9 поступает сигнал с выхода ИМС 8, на выход первого коммутатора 6 поступают импульсы с выхода ДПКД 5. Перед замыканием кольца подстройки перестраиваемого генератора 4 осуществляется привязка разности фаз импульсов на входах ФД 7, после чего открывается первый ключ 1, четвертый ключ 20 закрывается и осуществляется режим двухточечной модуляции частоты выходного сигнала. В этом режиме сигнал с выхода ИМС 8 подается в две точки схемы: на вход модуляции перестраиваемого генератора 4 через

третий коммутатор 14 и на второй вход фазового модулятора 13 через второй Коммутатор 9, цервый управляемый аттенюатор 10, блок 11 смещения и ин- terpaTop 12.

Подстройка перестраиваемого генератора 4 осуществляется с выхода ФД 7 через открытый первый ключ 1. Таким образом на входах ФД 7 поддерживает-, ея равенство частот и в силу применения первого интегрирующего фильтра 2 нулевая разность фаз импульсов. При постижении сигналом на выходе интегратора 12 некоторого значения напря- кения переключается первый 22 или второй 23 компаратор и через элемент ИЛИ 24 выходной сигнал первого 22 или нторого 23 компаратора поступает на первый информационный вход блока 25 управления (на вход второго RS-триг- гера 37). По следующему импульсу с опорного генератора 26 закрывается первый ключ 1, кольцо автоподстройки размыкается, и потенциал управления перестраиваемого генератора 4 запо- 1)шнается в первом интегрирующем филь- fре 2, Одновременно на выходе сброса блока 25 управления (регистр 38) формируются сигнал сброса интегратора 12 и сигнал предустановки ДПКД 5 длительностью в один период опорного сигнала. Предустановка ДПКД 5 осуществляется для уменьшения разности фаз Импульсов на входах ФД 7, которая возникает при сбросе интегратора 12. Для достижения нулевой разности по Сигналу с регистра 38 открывается четвертый ключ 20 и замыкается дополнительное кольцо автоподстройки. Сиг- нал с выхода ФД 7 проходит через четвертый ключ 20 и четвертый интегрирующий фильтр 21 и управляет положе- йием выходных импульсов фазового модулятора 13 относительно импульсов опорного генератора 26. После дости- нулевой разности фаз по сигналу с блока 25 управления закрывается четвертый ключ 20 и четвертый интегрирующий фильтр 21 запоминает потен- циал управления фазового модулятора 13, а первый ключ 1 открывается и опять осуществляется режим двухточеч- вой модуляции.

Для постоянной компенсации темпе- ратурного и других дрейфов цепи интегратора 12 при модуляции цикличности включается режим подстройки этой / цепи. По сигналу с блока 25 управления размыкается кольцо подстройки перестраиваемого генератора 4, на выходе второго коммутатора 9 устанавливается нулевой уровень напряжения и на выход первого коммутатора 6 проходят задержанные импульсы с выхода элемента 27 задержки. При этом сигнал с выхода ИМС 8 через третий коммутатор 14 подается на вход модуляции перестраиваемого генератора 4. Осуществляется сброс интегратора 12 и предустановка ДПКД 5, работает дополнительное кольцо привязки разности фаз, после чего открывается третий ключ 18 и производится подстройка цепи интегратора 12 в течение 20-50 периодов опорного сигнала. По окончании этого режима перед замыканием колца подстройки перестраиваемого генератора 4 виовь осуществляется сброс интегратора 12 и предустановка ДПКД 5} привязка разности фаз импульсов на входах ФД 7, после которой замыкается кольцо подстройки перестраиваемого генератора 4 и осуществляется режим двухточечной модуляции. Переключение режимов осуществляет блок 25 управления. Он содержит первый, второй и третий блоки 30, 31 и 34 памяти. С их помощью формируются управляющие сигналы. Управление адресами первого и второго блоков 30 и 31 памяти осуществляется первым двоичным десятиразрядным счетчиком 32 и первым RS- триггером 36, осуществляющим смену режимов по сигналу с БУЧ 28 с режима смены частоты на режим модуляции. Второй RS-триггер 37, второй счетчик 33 и третий блок 34 памяти формирует сигналы управления на выходе блока 25 управления при сбросе интегратора 12 в режиме модуляции. Двенадцатиразрядный регистр 38 служит для устранения дребезга выходящих сигналов с выходов первого и второго блоков 30 и 31 памяти, а также с выходов третьего блока 34 памяти и элементов ИЛИ 39- 44.

Периодичность смены режимов, как и длительность режима подстройки цепи-интегратора, не зависит от модулирующего сигнала и могут быть выбраны произвольно в зависимости, например, от скорости и величины температурного дрейфа. Практически для подстройки цепи интегратора 12 требует

ся 20-50 периодов опорного сигнала, а период повторения этого режима может быть больше указанного бремени в сотни и тысячи раз, поэтому его введение не ухудшает качества выходного сигнала.

В целом обеспечивается выходной сигнал с частотной модуляцией широкополосным сигналом произвольной формы с большой девиацией частоты, имеющий высокую долговременную стабильность несущей частоты.

Формула изобретения

Цифровой синтезатор частоты с частотной модуляцией, содержащий источник модулирующего сигнала,- первый управляемый аттенюатор, интегратор, последовательно соединенные опорный генератор, фазовый модулятор и фазовый детектор, последовательно соединенные первый интегрирующий фильтр, фильтр нижних частот, перестраиваемый генератор и делитель частоты с переменным коэффициентом деления, последовательно соединенные второй интегрирующий фильтр и второй управляемый аттенюатор, выход которого под- ключей к второму входу перестраиваемого генератора, блок установки час- тоты, информационный выход которого соединен с установочным входом делителя частоты с переменным коэффициен- ,- ходом делителя частоты с переменным

том деления и с управляющим входом первого управляемого аттенюатора, генератор стандартного напряжения и блок управления, последовательно соединенные лервый компаратор и элемент 40 ИЛИ, выход которого подключен к первому информационному входу блока управления, второй информационный вход которого соединен со стробирующим выходом блока установки частоты, второй Д5 компаратор, вход и выход которого соответственно подключены к входу первого компаратора и к второму входу элемента ИЛИ, а также третий и четвертый интегрирующие фильтры, о т- гп личающийся тем, что, с целью увеличения девиации выходного колебания и стабильности его несущей частоты, введены первьй ключ, второй ключ, третий ключ, четвертый ключ, ,-, первый коммутатор, второй коммутатор, третий коммутатор, элемент задержки и блок смещения напряжения, при этом первый вход первого ключа объединен

коэффициентом деления, выходом элемента задержки, выходом коммута ции блока управления и вторым входом -фазового детектора, первый вход второг коммутатора объединен с первым входом третьего коммутатора и подключен к выходу источника модулирующего напряжения, второй вход второго коммутатора объединен с вторым входом третьего коммутатора и соединен с вы ходом генератора стандартного напряж ния, управляющий вход и выход второг коммутатора подключены соответственно к первому кодовому выходу блока у равления и к входу первого управляемого аттенюатора, выход которого соединен с первым входом блока смещени напряжения, второй вход и выход кото рого соответственно подключены к выходу третьего интегрирующего фильтра и к входу интегратора, управляющий вход и выход третьего коммутатора со единены соответственно с вторым кодовым выходом блока управления и с

0

0 5 0

с первым входом второго ключа, пер-.- вым входом третьего ключа и с первым входом четвертого ключа и подключен к выходу фазового детектора, первый, второй, третий и четвертый управляющие выходы блока управления подключены соответственно к управляющим входам первого, второго, третьего и четвертого ключей, выход первого ключа соединен с входом первого интегрирующего фильтра, выход второго ключа подсоединен к входу второго интегрирующего фильтра, выход третьего клю- ча подключен к входу третьего интегрирующего фильтра, а выход четвертого ключа соединен с входом четвертого интегрирующего фильтра, выход которого подключен к первому управляющему входу фазового модулятора, второй управляющий вход которого объединен с входом первого компаратора и подключен к выходу интегратора, вход синхронизации блока управления объединен с входом элемента задержки и соединен с выходом опорного генератора, вход сброса интегратора объединен с входом предустановки делителя частоты с переменным коэффициентом деления и подключен к выходу сброса блока управления, первый.и второй информационные входы, вход управления и выход первого коммутатора соединены соответственно с вы-

коэффициентом деления, выходом элемента задержки, выходом коммута ции блока управления и вторым входом -фазового детектора, первый вход второго коммутатора объединен с первым входом третьего коммутатора и подключен к выходу источника модулирующего напряжения, второй вход второго коммутатора объединен с вторым входом третьего коммутатора и соединен с выходом генератора стандартного напряжения, управляющий вход и выход второго коммутатора подключены соответственно к первому кодовому выходу блока управления и к входу первого управляемого аттенюатора, выход которого соединен с первым входом блока смещения напряжения, второй вход и выход которого соответственно подключены к выходу третьего интегрирующего фильтра и к входу интегратора, управляющий вход и выход третьего коммутатора соединены соответственно с вторым кодовым выходом блока управления и с

11154354412

вторым входом второго управляемого ключены к общей шине цифрового синте- аттенюатора, при этом третьи входы затора частоты с частотной модуляци- второго и третьего коммутаторов под- ей.

вш-мз

ш

кз

к.щ

КЛ.16

клп

Кб

ЯШ5Инт.1Э

KJ1.2S

ля.;

ИПО, ЗБП 155ИРП

| Цифровой синтезатор частоты с частотной модуляцией | 1980 |

|

SU919040A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1982 |

|

SU1035776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-15—Публикация

1987-12-22—Подача