Изобретение относится к аптоматическому регулированию и может быть использовано при автоматизации группы однотипн ж технологических объектов, в частности в системах стабилизации и программного регулирования feMnepaTypbi на объектах с многозонным нагревом Известен многоканальный регулятор содержархий в каждом канале исполнит ;льный механизм и последовательно соединенные измеритель рассогласования и блок выделения модзяя, комiv yTaTOpt., блок анализа рассогласования, блок формирования сигнала уп- равления Сt. Недостатком этого регулятора является низкая точность и малая надежность, обусловленные тем, что когда регулятор по какой-то причине .не справляется с задачей регулирования в одном из каналов и модуль ошиб ки этого канала остается максималь HbJMs, данный канал остается длительное время включённым а остальные каналы остаются без регулирующего воздействия, кроме того, регулятор не обеспечивает контроля работы каналовНаиболее близким к предлагаемому по технической сущности является мно гокамальньш регулятор, содержащий регулирующее- устройство,, входы первого сумматора которого через первьгй и второй коммутаторы связа с канальньЕ4и нзмерительнь мй преобразователями и канальными задатчиками. Выход второго сумматора регулирующего устройства через третий ког шутатор соединен с канальными аналоговыми запоминающими устройствами,; выходы которых подключены к каналнтгык ислолнителБным механизмам и через четвер-;йгй коммутатор к неигЕйертирующим вхо дам трехпозиционного релейного элементаJ инвертирующий вход которого связан с выходом регулирующего устройства а выход через пятый коммутатор связан с дополнительным входом интегратора регулируттцего устройства .3, . Недостатком этого регулятора является TOj что коммутаторы работают по жесткой программе, вследствие чего регулирующее ус ойство подключается к каждому каналу по очереди,на одно и то же времяр заданное блоком управления, даже в том случае, когда рассогласование в канале равно нулю или находится в допустимых пределах, в то времяр как в других каналах могут существовать большие рассогласования. Это приводит к необоснованному увеличению общего времени обегания каналов, что снижает точность регулирования. При неблагоприятном совпадении возмущений в отдельных каналах может возникнуть ситуация, когда регулирующее устройство, не закончив цродесса регулирования в предьщущем канале, переключается на следуюихий канал. При этом также ухудшается точность регулирования. Кроме того, регулятор не обеспечивает контроля работы каналов, что снижает его надежность, Цель изобрет,ения - повытение точности регулирования путем сокращения времени обегания каналов и повьш ения надежности регулятора обеспечением контроля работь каналов регулироваинл, Поставленная дель достигается тем, что в регуляторе, содержащем канальные измерительные преобразователи, выходы которых соединены с входами первого коммутатора, подключенного своим выходом ,к одному из входов первого сумматора, к другому входу которого подсоединен выход второго коммутатора, связанного своими входами с выходами канальных задатчиков, выход первого сумматора подключен к основному входу интегратора и к первому входу нгорого сумматора, выход которого связан с инвертирующим входом трехпозиционного релейного элемента и с входом третьего коммутатора, связанного своими выходами через канальные аналоговью запоминающие элементы с входами соответствующих канальных исполнительных механизмов и с входами четвертого коммутатора, выход которого подключен к неинвертирующему входу трекпозидионного релейного элемента,, связанного своим выходом через пятый коммутатор с дополнительньпч входом интегратора, связанного своим выходом с BTOpbiM входом второго сумматора, дополнительно введены последовательно соединенные блок вьщеления модуля5 пороговый элемент, элемент ИЛИ, элемент задержки, шестой коммутатор и блок сигнализации, причем вход блока вьщеления модуля соединен с выходом первого сумматора, выход элемента задержки подключе к второму входу элемента ЯПИ. выход

которого связан с управляющими входами коммутаторов.

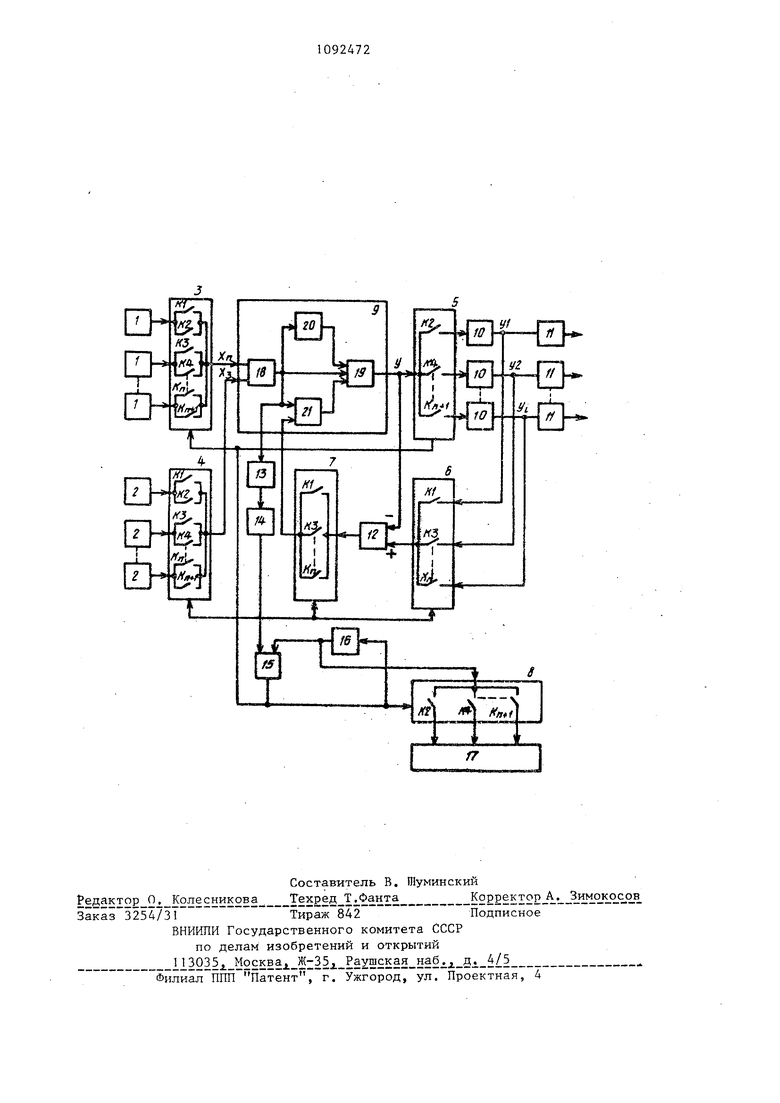

На чертеже представлена блок-схема регулятора.

Регулятор содержит канальные измерительные преобразователи 1, канальные задатчики 2, коммутаторы 3-8 регулирующее устройство 9, канальные аналоговые запоминающие элементы 10, канальные исполнительные механизмы

11,трехпозиционный релейный элемент

12,блок выделения модуля 13, пороговый элемент 14, элемент ИЛИ 15, элемент задержки 16, блок сигнализации 17. Регулирующее устройство 9 содержит сумматоры 18 и 19, дифференциатор 20 и интегратор21. На чертеж обозначено:

Х и Х - соответственно текущее и заданное значения регулируемого параметра, подаваемые на входной сумматор 18 регулирующего устройства 9 в момент связи последнего с i-ым каналом управления;

Y - выходной сигнал регулирующего устройства 9;

Y- - выходной сигнал i-ro канального аналогового запоминающего устройства 10;

К, К2, Kj, К, ключи, входящие в состав коммутаторов;

п - порядковые номера ключей.

Порядковые номера ключей соответствуют очередности их замыкания. Если замкнут ключ К , то все остальные разомкнуты, в дальнеЙ1 1ем при замыкании ключа К 2 ключ К размыкается и т.д.

Регулятор работает следующим образом.

Коммутаторы 3-5 в темпе, задаваемом частотой переключения элемента ИЛИ 15 из нулевого состояния в единичное, замыкают своими ключами соответствующий канал регулирования, состоящий из регулируемого объекта (не показаны), измерительного преобразователя 1, задатчика 2, регулирзпощего устройства 9, аналогового запоминающего элемента 10 и исполнительного механизма 11. При переключении регулирующего устройства 9 с непрерьгоным выходным сигналом на работу -с другим каналом (объектом регулирования) запоминаюп1ий элемент предыдущего канала запоминает последнее значение регулирующего воздействия. В результате пропорциональный исполнительный механизм 11 останется в положении, которое было до момента переключения выходной цепи регулирующего устройства 9 на работу с испол нительным механизмом 1 1 другого -(последующего) канала.

При этом регулирующее устройство 9 работает в двух режимах - основном и подготовительном. В основном режиме осуществляется связь регулирующег устройства 9 с тем или иным объектом регулирования в зависимости от положения соответствующих ключей коммутаторов 3-5, Подготовительный режим необходим для обеспечения безударной коммутации канальных исполнительных механизмов 11 с регулирующим устройством 9. В основном режиме замыкаются ключи с четными порядковьми номерами, а в подготовительном реж1-$ме с нечетными. Перед началом каждого основного режима работы регулирующего устройства 9 осуществляется предварительная его работа в подготовительном резкиме.

Для организации работы регулирующего устройства 9 в подготовительном режиме многоканальный регулятор содержит коммутаторы 6 н 7., а также трехпозиционный релейный элемент 12, В этом режиме все ключи коммутатора 5 разомкнуты, а в коммутаторах 3 и 4 замкнуты только те ключи, у которых совпадают порядковые номера с номе- рами замкнутых ключей, входящих в коммутаторы 6 и 7,

Предположим, что в коммутаторах 3, 4, 6 и 7 замкнуты ключи К.. Это значит, что на инвертиру5ощий вход трехпозиционного релейного элемента 12 подается непосредственно выходной сигнал регулирующего устройства 9;, а на неинвертирующий вход - выходной сигнал запоминающего элемента 10 пер вого канала через заг-пснутый ключ К коммутатора 6. При этом выход трехпозиционного релейного элемента 1,2 через замкнутый кгаоч К ко 1мутатора 7 связан с дополнительным (скоростньм) входом интегратора 21.

Совокупность технических средств, содержащая запоминающий элемент 10 первого капала, ключи К из коммутаторов 6 и 7, трехпозиционнъй релейный элемент 12, интегратор 21 и сумматор 19, образуют следяп1;ую систему, в которой входным (задающим) сигналом является выходной сигнал Y запоминающего элемента 10 первого канала, а выходньм сигналом - сигнал Y, }1 снимаемый с выхода регулирующего уст ройства 9. В подготовительном режиме на выхо де сумматора 18 формируется сигнал, пропорциональный ошибке регулирования и равный по величине разности вы ходных сигналов задатчика 2 и измери тельного преобразователя 1 первого канала. Этот сигнал разности подаетс на основной вход интегратора 21, дифференциатор 20 и сумматор 19. Если принять, что постоянная времени интегрирования по скоростному -входу интегратора 21 по величине намного меньте постоянной времени интегрирования по основному его входу, а суыматор 19 работает в линейном режиме (без насыщения), то выходной сигнал Y регулирующего устройства 9 практически мгновенно примет значение, рав ное по величине сигналу Y, снимаемому с выхода -запоминающего элемента 10 первого канала. Поэтому после переключения регулирующего устройства 9 на основной режим работы на исполнительный механизм 11 первого канала в первьй момент времени поступит такое регулирующее воздействие, которое по величине равно выходному сигналу запоминающего элемента 10 первого канала, сформированному на выходе последнего еще до подготовительного режима. Таким образом, обес печивается безударная коммутация канальных исполнитсшьных механизмов 11 с регулирующим устройством 9 независимо от величины сигнала ошибки регулирования. Время нахождения регулирующего устройства 9 в подготовительном режиме определяется элементом задержки 16, которое по истечении установленного промежутка времени через элемент ИЛИ 15 устанавливает коммутаторы в следующее положение, обеспечивая основной режим работы для этого канала, Время нахождения регулирующего устройства 9 в основном реяшме определяется элементом задержки 16 или моментом срабатывания порогового эле 2 мента 4, которые через элемент ИЛИ 15 устанавливают коммутаторы в следующее положение, обеспечивая подготовительньп режим работы для следующего канала. Пороговый элемент 14 срабатывает при наличии на его входе нулевого или допустимого, наперед выбранного, значения модуля ошибки, снимаемого с выхода блока выделения модуля 13, Кроме управляющих входов коммутаторов, сигнал с выхода элемента ИЛИ 15 поступает на элемент задержки 6, устанавливая его в нулевое состояние, и от этого момента начинается отсчет времени подготовительного или основного режима работы регулирующего устройства 9. Таким образом, регулирующее устройство 9 не задерживается подключенным к каналам с ошибкой регулирования равной или близкой к нулю, а к каналам, нуждающимся в регулирующем воздействии, оно подключено до тех пор, пока ошибка не сводится к нулю, но не более чем на время, необходимое для регулирования наиболее инерционного объекта, задаваемого с помощью элемента задержки 16. . Следовательно, зависимость вреиени основного режима от времени суицествования недопустимой ошибки в канале позволяет сократить время обегания каналов, что увеличивает точность регулирования или позволяет обслуживать большее количество каналов, В основном режиме замыкается соответствующий ключ коммутатора 8 и в случае, если в этом режиме срабатывает элемент задержки 16, что говорит о том, что регулирующее устройство 9 по какой-то причине не справилось с задачей регулирования в данном канале, в блоке сигнализации 7 срабатьгоает предупредительная сигнализация этогсь канала. Наличие сигнализации позволяет своевременно принять необходимые меры по выяснению и устранению причин нарушения нормальной работы каналов, что повышает надежность регулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный регулятор | 1989 |

|

SU1608629A1 |

| Многоканальный регулятор | 1986 |

|

SU1388840A1 |

| Устройство для регулирования технологических параметров по заданной программе | 1983 |

|

SU1136121A1 |

| Многоканальный регулятор | 1982 |

|

SU1100606A1 |

| Многоканальный регулятор | 1985 |

|

SU1290253A1 |

| Многоканальный регулятор | 1983 |

|

SU1161915A1 |

| Многоканальный регулятор технологических процессов | 1973 |

|

SU468220A2 |

| Импульсный регулятор | 1981 |

|

SU1004969A1 |

| Устройство для регулирования натяжения полосы между клетями непрерывного стана холодной прокатки | 1977 |

|

SU743741A1 |

| Устройство регулирования толщины полосы на непрерывном прокатном стане | 1979 |

|

SU865457A1 |

МНОГОКАНАЛЬНЫЙ РЕГУЛЯТОР, содержап(ий канальные измерительные преобразователи, выходы которых соединены с входами первого коммутатора, подключенного своим выходом к одному из входов первого сумматора, к другому входу которого подсоединен выход второго коммутатора, связанного своими входами с выходами канальных задатчиков, выход первого сумматора подключегт к основному входу интегратора и к первому входу второго сумматора, выход которого связан с инвертирующим входом трехпозиционного релейного элемента и с входом третьего коммутатора, связанного своими выходами через канальные аналоговые запоминающие элементы с входами соответствую111их канальных исполнительных механиз тв и с входами чет вертого коммутатора, выход которого подключен к неинвертирующему входу трехпозиционного релейного элемента, связанного своим выходом через пятый коммутатор с дополнительным входом интегратора, связанного своим выходом с вторым входом второго сумматора, отличающийся тем, что, с целью повышения точности регулирования путем сокращения времени обегаВИЯ каналов и повьпчения надежности регулятора за счет обеспечения контроля работы каналов регулирования, регулятор дополнительно содержит последовательно соединенные блок выделения модуля, пороговьш элемент, элемент ИЛИ, элемент задержки, тестой ;о коммутатор и блок сигнализации, прию чем вход блока выделения модуля сое4 динен с выходом первого сумматора выход элемента задержки подключен к Ю второму входу элемента ИЛИ, выход ко торого связан с управляющими входами коммутаторов.

Авторы

Даты

1984-05-15—Публикация

1983-01-11—Подача