(54) ИМПУЛЬСНЫЙ РЕГУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный регулятор | 1983 |

|

SU1117585A1 |

| Импульсный регулятор | 1982 |

|

SU1101787A1 |

| Импульсный регулятор | 1982 |

|

SU1105859A1 |

| Импульсный регулятор | 1984 |

|

SU1170426A1 |

| Устройство для регулирования технологических параметров по заданной программе | 1983 |

|

SU1136121A1 |

| Частотно-импульсный регулятор | 1985 |

|

SU1287100A1 |

| Частотно-импульсный регулятор температуры | 1981 |

|

SU1010606A1 |

| Многоканальный регулятор | 1983 |

|

SU1092472A1 |

| Позиционный регулятор для систем с запаздыванием | 1987 |

|

SU1427328A1 |

| Многоканальный регулятор | 1989 |

|

SU1608629A1 |

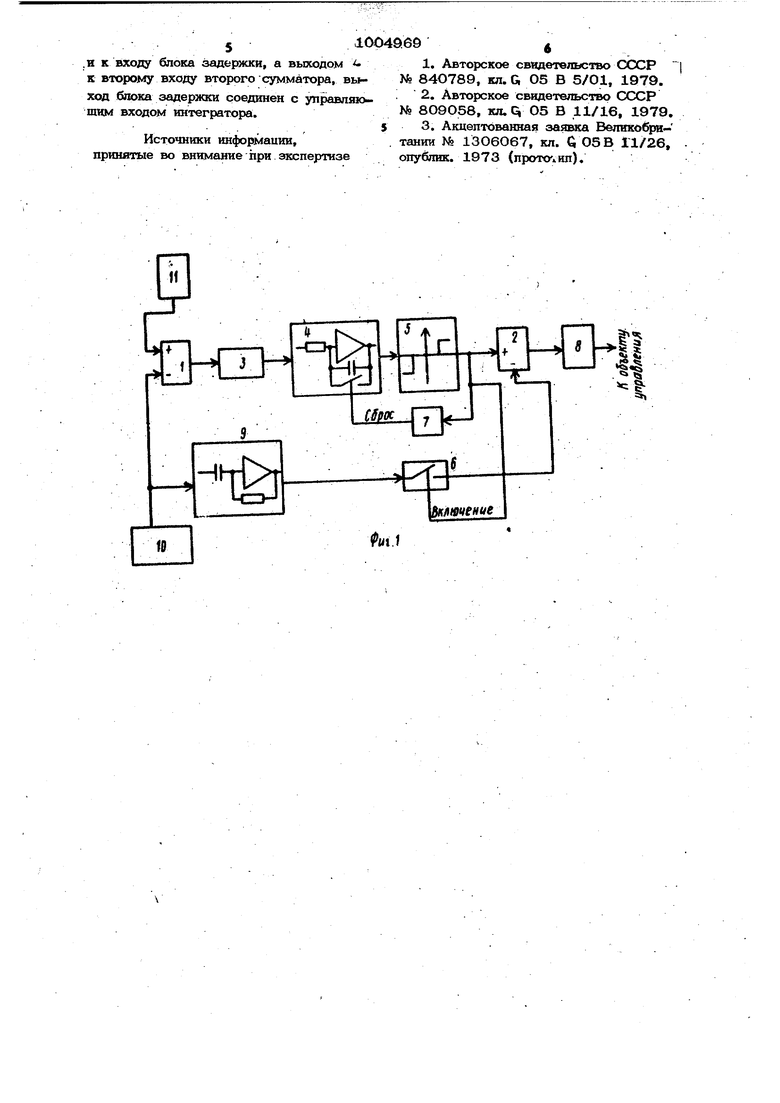

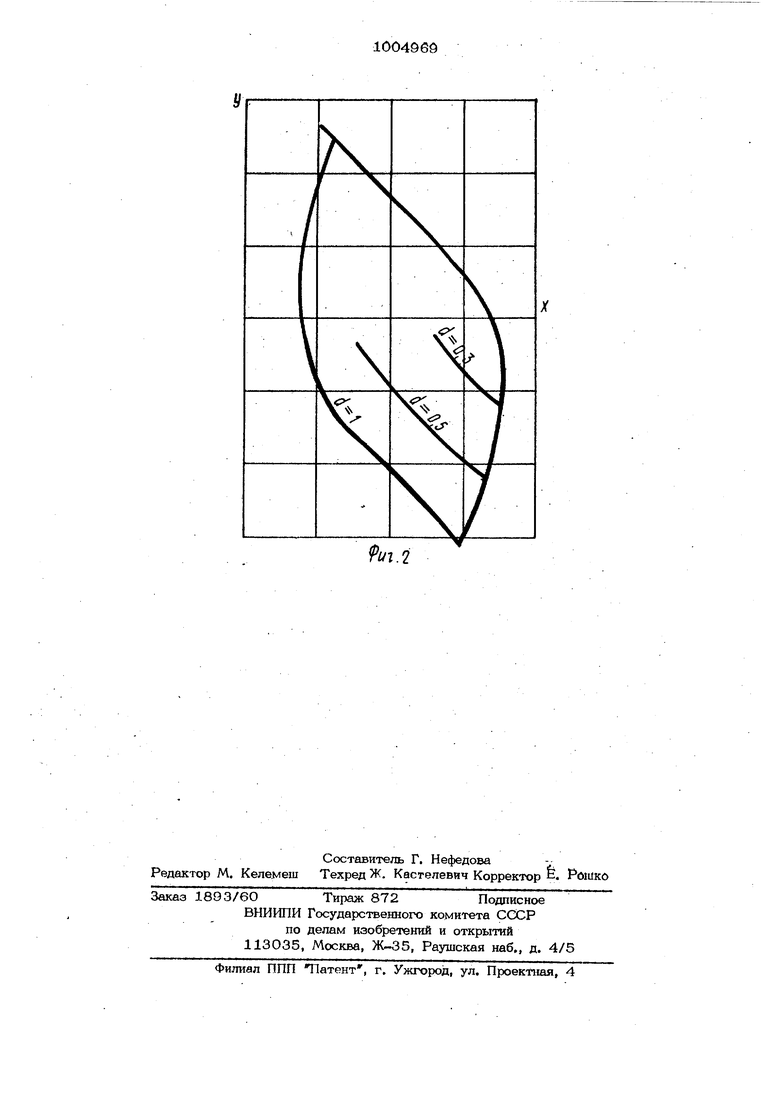

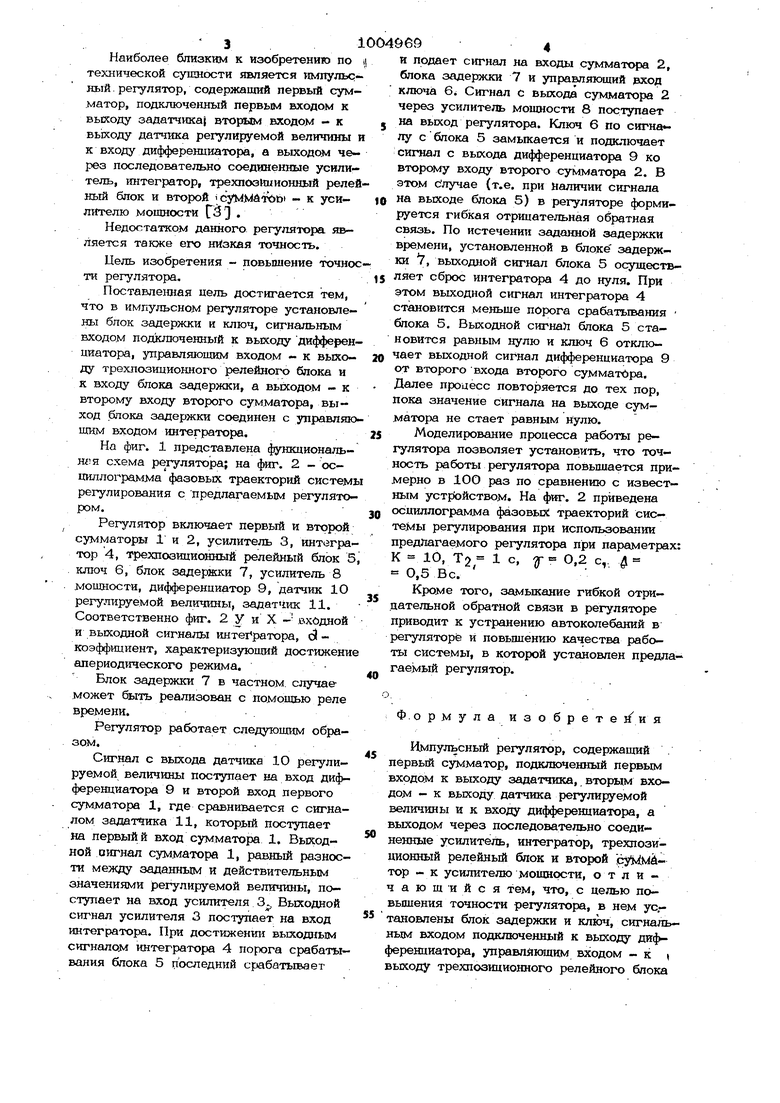

Изобретение относится к автоматическому управлению, а именно к автоматическим импульсным регуляторам, в кото рь1х выходной сиг}1ал является прерывной импульсной функцией отклонения входного сигнала от заданной величины, и может быть применено в системах автоматического управления различными объектами, в которых объект регулирования, исполнительное устройство и датчик регулируемой величины можно приближенно описать дифференциальным уравнением первого порядка, в частности при регулировании температуры с помощью различных электронагревательных устройств с высоким качеством регулирования. Известен регулятор, содержащий датчик регулируемой величины, и задатчик, подключенные выходами к соответствую.щим входам первого формирователя сигнала управления, выход которого соединен с первым входом второго формирователя сигнала управления, второй вход которого дифференциатор подключен к датчи- ку регулируемой величины, а выход - ко входу усилителя мощности, причем, если второй формирователь сигнала управления является пропорциональным звеном, то его функции может выполнять сумматор Cl . Известен также импульсный регулятор, содержащий датчик регулируемой величины и задатчик, подключенные к первому сумматору, выход которого соединен с первым входом второго суммато ра, выход которого через усилитель соединен с первым входом третьего сумматора и входом нелинейного корректирующего блока, выход которого через интегратор и переключатель соединен со вторым входом третьего сумматора, выход кото- . рого через трехпозиционный релейный блок подключен к управляющему входу переключателя и входу исполнительного механизма, выход которого через блок местной обратной связи соединен со вторым входом второго сумматора С2 . Недостатком известных регуляторов является их низкая точность. Наиболее близким к изобретению по технической сущности 5голяется импульсный регулятор, содержащий первый сумматор, подключенный первым входом к выходу задатчика| вторьш входом - к вь1ходу датчика регулируемой величины к входу дифференциатора, а выходом через последовательно соединенные усилитель, интегратор, трехпозИиионный релей ный блок и второй icyMWdirbbi - к усилителю мощности ГЗ ) , Недостатком данного регулятора является также его низкая точность. Цель изобретения - повышение точное ти регулятора, Поставленная цель достигается тем, что в импульсном регуляторе установлены блок задержки и ключ, сигнальным входом подключенный к выходу дифферен циатора, управляющим входом - к выходу трехпозиционного релейного блока и к входу блока задержки, а выходом - к второму входу второго сумматора, выход блока задержки соединен с управляю щим входом интегратора. На фиг. 1 представлена функциональшя схема регулятора; на фиг. 2 - осциллограмма фазовых траекторий систем регулирования с предлагаемым регулятором. Регулятор включает первый и второй сумматоры 1 и 2, усилитель 3, интегра тор 4, трехпозиционный релейный блок 5 ключ 6, блок задержки 7, усилитель 8 мощности, дифференциатор 9, датчик 10 регулируемой величины, задатчик 11. Соответственно фиг, 2 У и X - входной и выходной сигналы интет ратора, 61коэффициент, характеризующий достижени апериодического режима. Блок задержки 7 в частном, случае может быть реализован с помощью реле времени. Регулятор работает следующим образом. Сигнал с выхода датчика 10 регулируемой величины поступает на вход дифференциатора 9 и второй вход первого сумматора 1, где сравнивается с сигналом задатчика 11, который поступает на первый и вход сумматора 1. Выходной оигнал сумматора 1, равный разности между заданным и действительным значениями регулируемой величины, поступает на вжод усилителя 3, Выходной сигнал усилителя 3 поступает на вход интегратора. При достижении выходным сигналом интегратора 4 порога срабатывания блока 5 последний срабатьгоает и подает сигнал на входы сумматора 2, блока задержки 7 и управляющий эход ключа 6; Сигнал с выхода сумматора 2 через усилитель мощности 8 поступает на выход регулятора. Ключ 6 по сигна лу с блока 5 замьпсается и подключает сигнал с выхода дифференциатора 9 ко второму входу второго сумматора 2. В этом Случае (т.е. при наличии сигнала на выходе блока 5) в регуляторе формируется гибкая отрицательная обратная связь. По истечении заданной задержки времени, установленной в блоке задержки V, вькодной сигнал блока 5 осуществляет сброс интегратора 4 до нуля. При этом выходной сигнал интегратора 4 становится меньще порога срабатьгоания блока 5. Выходной сигнал блока 5 становится равным нулю и ключ 6 отключает выходной сигнал дифференциатора 9 от второго входа второго сумматйра. Далее процесс повторяется до тех пор, пока значение сигнала на выходе сумматора не стает равным нулю. Моделирование процесса работы регулятора позволяет установить, что точность работы регулятора повышается примерно в 1ОО раз по сравнению с известным устройством. На фиг. 2 приведена осциллограмма фазовьсС траекторий системы регулирования при использовании предлагаемого регулятора п)ри параметрах: К 10, Т2 1 с, 0,2 с,. 4 0,5 В с. Кроме того, замьшание гибкой отрицательной обратной связи в регуляторе приводит к устранению автоколебаний в регуляторе и повьпиению качества работы системы, в которой установлен предлагаемый регулятор. Ф.ормулаизобрете ия Импульсный регулятор, содержащий первый сумматор, подключенный первым входом к выходу задатчкка, вторым входом - к вькоду датчика регулируемой величины и к входу дифференциатора, а выходом через последовательно соединенные усилитель, интегратор, трехпозиционный релейный блок и второй pyWMAтор - к усилителю мощности, отличающийся тем, что, с целью повышения точности регулятора, в нем установлены блок задержки и ключ, сигнальным входом подключенный к выходу дифференциатора, управляющим входом - к ( выходу трехпозиционного релейного блока

,и к входу блока зад&ржки, а выходом к второму входу второго сумматора, выход блока задержки соединен с управлшощим входом интегратора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 84О789, кл.а О5 В 5/01, 1979. : 2. Авторское свидетельство СССР № 809О58, кл. С 05 В 11/16, 1979.

Авторы

Даты

1983-03-15—Публикация

1981-11-04—Подача