памяти, информационный вход nepBOio буферного регистра подключен к третьему выходу коммутатора связи с интерфейсом, информационные выходы регистров второй группы соединены с информационным входом второго арифметического блока, управляющие входы сдвигателя соединены с соответствующими управляющими выходами группы узла памяти микропрограмм блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый процессор спектральной обработки сигналов | 1978 |

|

SU744603A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU955085A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Процессор | 1974 |

|

SU526902A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| МНОГОПРОЦЕССОРНАЯ ВЕКТОРНАЯ ЭВМ | 1995 |

|

RU2113010C1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

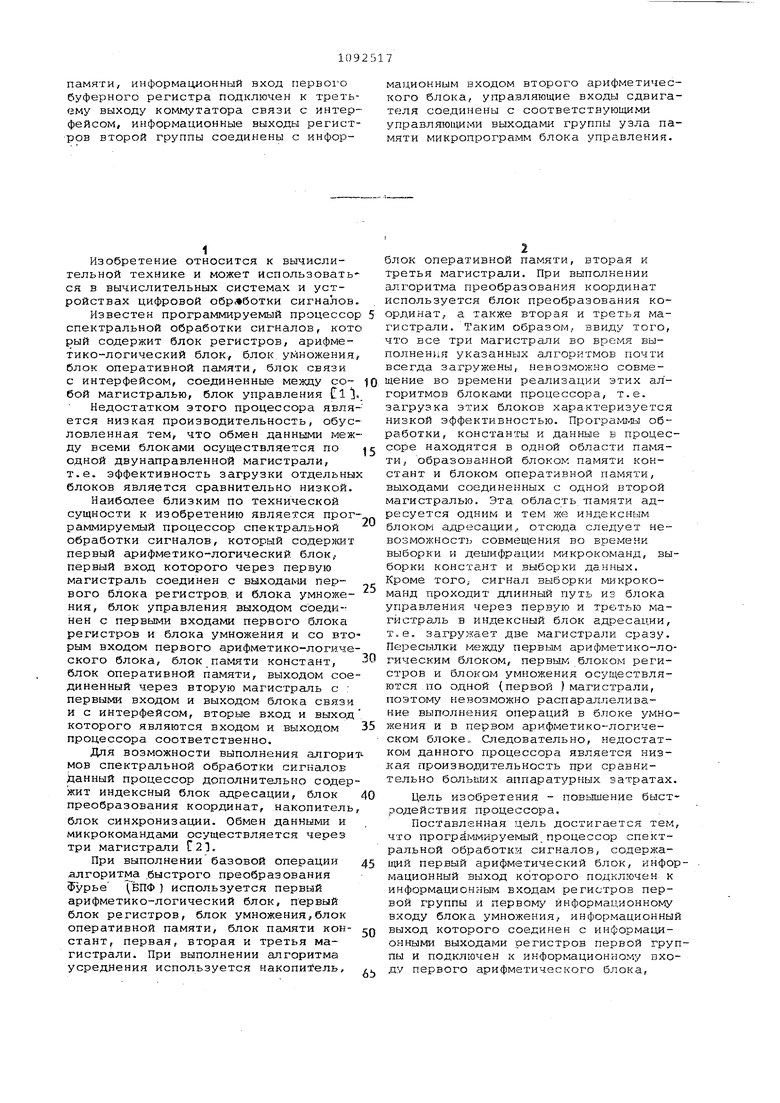

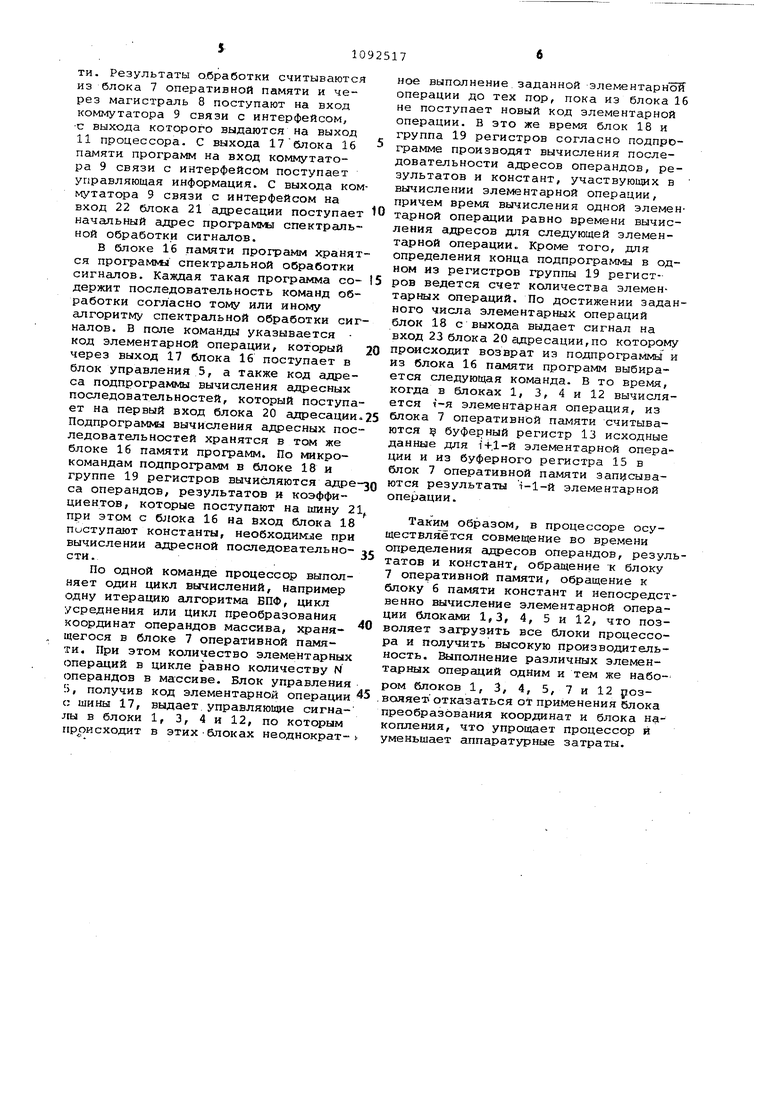

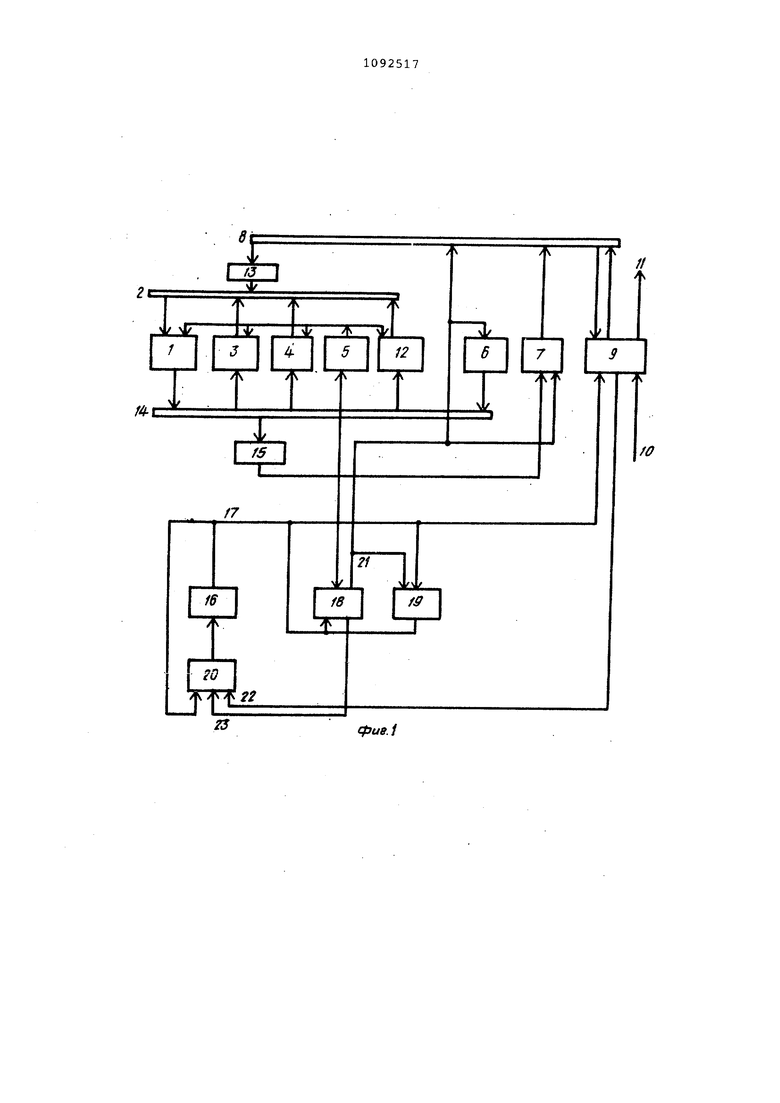

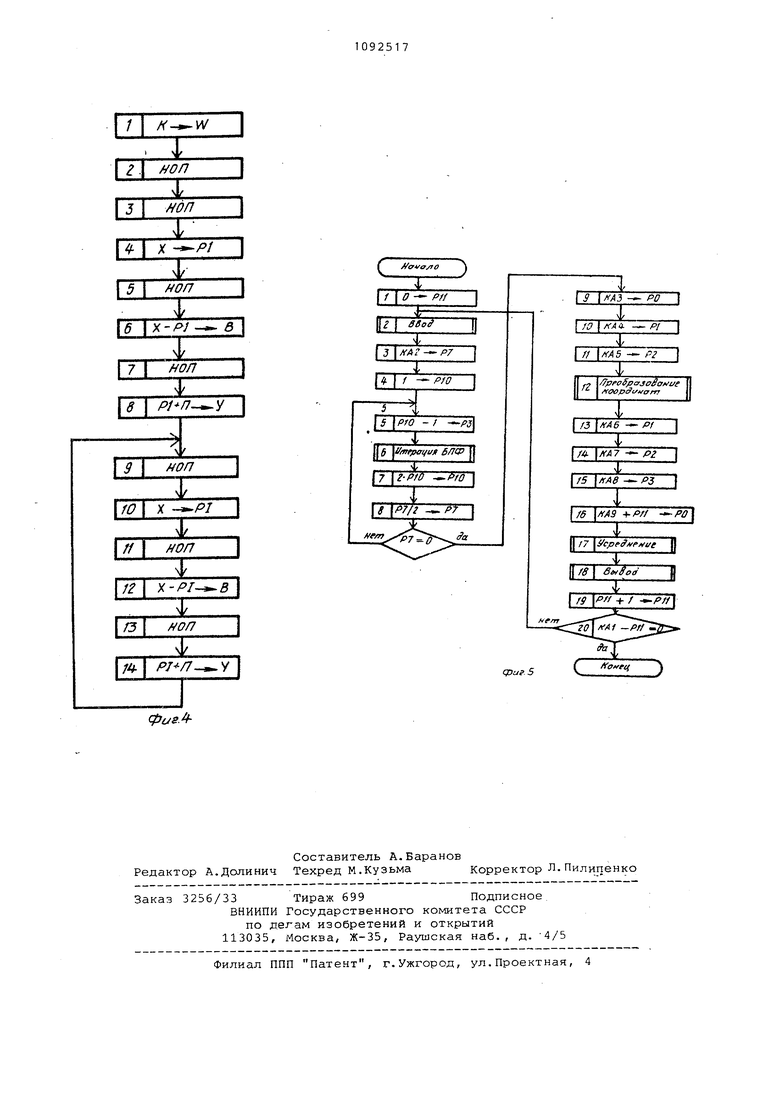

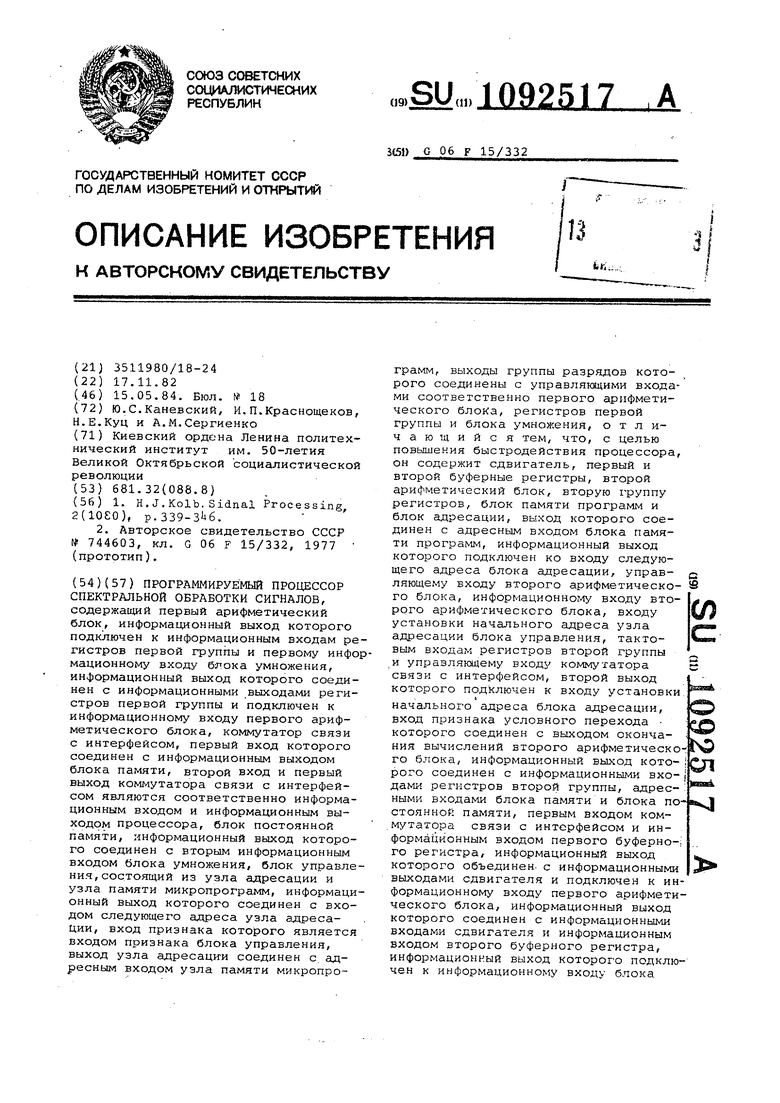

Изобретение относится к вычислительной технике и может использоваться в вычислительных системах и устройствах цифровой обрлботки сигналов. Известен программируемый процессор спектральной обработки сигналов, кото рый содержит блок регистров, арифметико-логический блок, блок.умножения блок оперативной памяти, блок связи с интерфейсом, соединенные между собой магистралью, блок управления Cl Недостатком этого процессора является низкая производительность, обусловленная тем, что обмен данными между всеми блоками осуществляется по одной двунаправленной магистрали, т.е. эффективность загрузки отдельны блоков является сравнительно низкой. Наиболее близким по технической сущности к изобретению является прог раммируемый процессор спектральной обработки сигналов, который содеришт первый арифметико-логический блок,, первый вход которого через первую магистраль соединен с выходами первого блока регистров, и блока умножения, блок управления выходом соединен с первыми входами первого блока регистров и блока умножения и со вто рым входом первого арифметико-логического блока, блок памяти констант, блок оперативной памяти, выходом сое диненный через вторую магистраль с : первыми входом и выходом блока связи и с интерфейсом, вторые вход и выход которого являются входом и .выходом процессора соответственно. Для возможности выполнения алгориэ мов спектральной обработки сигналов Данный процессор дополнительно содержит индексный блок адресации, блок преобразования координат, накопитель блок синхронизации. Обмен данными и микрокомандами осуществляется через три магистрали С 21. При выполнении базовой операции алгоритма .быстрого преобразования Фурье БПФ ) используется первый арифметико-логический блок, первый блок регистров, блок умножения,блок оперативной памяти, блок памяти констант, первая, вторая и третья магистрали. При выполнении алгоритма усреднения используется накопитель, блок оперативной памяти, вторая и третья магистрали. При выполнении алгоритма преобразования координат используется блок преобразования координат, а также вторая и третья магистрали. Таким образом,, ввиду того, что все три магистрали во время выполнения указанных алгоритмов почти всегда загружены, невозможно совмещение во времени реализации этих алгоритмов блоками процессора, т.е. загрузка этих блоков характеризуется низкой эффективностью. Програм1 и обработки, константы и данные в процессоре находятся в одной области памяти, образованной блоком памяти констант и блоком оперативной памяти, выходами соединенных с одной второй магистралью. Эта область -памяти адресуется одним и тем же индексным блоком адресации, отсюда следует невозможность совмещения во времени выборки и дешифрации микрокоманд, выборки констант и выборки данных. Кроме ТОГО; сигнал выборки микрокоманд проходит длинный путь из блока управления через первую и третью магистраль в индексный блок адресации, т.е. загружает две магистрали сразу. Пересылки между первым арифметико-логическим блоком, первым блоком регистров и блоком умножения осуществляются по одной (первой (магистрали, поэтому невозможно распараллеливание выполнения операций в блоке умножения и в первом арифгметико-логическом блоке, Отедовательно, недостатком данного процессора является низкая производительность при сравнительно больйшх аппаратурнЕЛХ затратах. Цель изобретения - повышение быстродействия процессора. Поставленная цель достигается тем, что прогрйммируе1 Ш1й процессор спектральной обработк; 1 сигналов, содержащий первый арифметический блок, информационный выход которого подключен к информационным входам регистров первой группы и первому информационному входу блока умножения, информационный выход которого соединен с информационными выходами регистров первой группы и подключен к информационному входу первого арифметического блока, коммутатор связи с интерфейсом, первый вход которого соединен с информа ционным выходом блока памяти, второй вход и первый выход коммутатора связи с интерфейсом являются соответственно информационным входом и информационны1м выходом процессора, блок постоянной Памяти, информационный выход которого соединен с вторым информационным входом блока умножения, блок управления, состоящий из узла адресации и узла памяти микропрограмм, информационный выход которого соединен со входом следующего адреса узла адресации, вход признака которого является входом признака блока управления, выход узла адресации соединен с адресным входом узла памяти микропрограмм, выходы группы разрядов, которого соединены с управляющими входами соответственно nepBo го арифметического блока, регистров первой группы и блока умножения, содержит сдвигатель, первый и второй буферные регистры, второй арифметический блок, вторую группу регистров блок памяти программ и блок адресации, выход которого соединен с адрес ым входом блока памяти программ, информационный выход которого подклю чен к входу следующего адреса блока адресации, управляющему входу второго арифметического блока, информационному входу второго арифметического блока, входу установки начального адреса узла адресации блока управления, тактовым входам регистров второй группы и управляющему входу коммутатора связи с интерфейсом, второй выход которого подключен к входу установки начального адреса блока адресации, вход признака условного перехода которого соединен с выходом окончания вычислений второго арифметического блока, информационный выход которого соединен с информационными входами регистров второй группы с1дресными входами блока памяти -и блока постоянной памяти, первым входом коммутатора связи с интерфейсом и информационным входом первого буфе ного регистра, информационный выход которого объединен с информационными выходами сдвигателя и подключен к информационному входу первого арифме тического блока, информационный выхо которого соединен с информационными входами сдвигателя и информационным входом второго буферного регистра, информационный выход которого подклю чен к информационному входу блока па мяти, информационный вход первого бу ферного регистра подключен к третьему выходу коммутатора связи с интерфейсом, информационные выходы регистров второй группы соединены с информационным входом второго арифмети ческого блока, управляющие входы сдв гателя соединены с соотвс- тгтвх-ющими. управляющими вЕзТходами группы зла памяти микропрограмм блока управления. На фиг. 1 представлена блок-схема процессора; на фиг. 2 - блок-схема алгоритма вычисления адресной последовательности для преобразования координат; на фиг. 3 - блок-схема а.пгоритма вычисления адресной последова.тельности усреднения; на фиг. 4 :блок-схема алгоритма вычисления усреднения; на фиг. 5 -блок-схема алгоритма цифровой обработки сигналов. Программируемый процессор спектральной обработки сигналов содержит арифметический блок 1, магистраль 2, группу регистров 3, блок умножения 4, блок управления 5, блок постоянной памяти (констант ) 6, 6J7OK (оперативной памяти 7, магистраль 8, коммутатор связи с интерфейсом 9, вход 10 и выход 11 процессора соответственно, сдвигатель 12, буферный регистр 13, магистраль 14, буферный регистр 15, блок 16 памяти программ, выхс 17 блока 16, арифметический блок 18, группу 19 регистров, блок 20 адресации, выход 21 блока 18, вход 22 (вход установки начального адреса программы} блока 20 адресации, вход 23 (признак условного перехода ). Программируемый процессор спектральной обработки сигналов работает следующим образом. Блок 1, гру.ппа регистров 3, блок умножения 4 и сдвггатель 12 под Bd действием управляющих сигналов из блока управления 5, обмениваясь между собой операндами через магистрали 2 и 14, выполняют одну из элементарных операций, таких как базовая операция алгоритма БПФ, операция усреднения, операция преобразования координат и другие. Код этой операции поступает в блок 5 управления с выхода 17 блока 16 памяти программ. Обрабатываемые массивы операндов хранятся в блоке 7 оперативной памяти, считываются из него и через магистраль 8 и буферный регистр 13 поступают в магистраль 2 и далее в блоки 1, 3, 4, 12, где обрабатываются согласно алгоритму заданной элементарной операции. Результаты этой операции из магистрали 14 через буферный регистр 15 записываются в блок оперативной памяти 7. Константы, необходимые при выполнении элементарной операции, хранятся в блоке 6 памяти констант, откуда выдаются в магистраль 14. Адреса для блока 6 памяти констант и блока 7 оперативной памяти поступают с выхода 21 блока 18. Исходные данные со входа 10 процессора поступают в коммутатор 9 связи с интерфейсом через его вход и далее с его выхода через магистраль 8 записываются в блок 7 оперативной памяти. Результаты о.бработки считываются из блока 7 оперативной памяти и через магистраль 8 поступают на вход коммутатора 9 связи с интерфейсом, с выхода которого выдаются на выход 11 процессора. С выхода 17 блока 16 памяти программ на вход коммутатора 9 связи с интерфейсом поступает управляющая информация. С выхода коммутатора 9 связи с интерфейсом на вход 22 блока 21 адресации поступает начальный адрес программл спектральной обработки сигналов.

в блоке 16 памяти программ хранятся программл спектральной обработки сигналов. Каждая такая программа содержит последовательность команд обработки согласно тому или иному алгоритму спектргшьной обработки сигналов. В поле команды указывается код элементарной операции, который через выход 17 блока 16 поступает в блок управления 5, а также код адреса подпрограммы вычисления сщресных последовательностей, который поступает на первый вход блока 20 адресации Подпрограммы вычисления адресных последовательностей хранятся в том же блоке 16 памяти программ. По микрокомандам подпрограмм в блоке 18 и группе 19 регистров вычисляются адре са операндов, результатов и коэффициентов, которые поступают на шину 2 при этом с блока 16 на вход блока 18 поступают константы, необходимее при вычислении гщресной последовательности.,

По одной команде процессор выполняет один цикл вычислений, например одну итерацию алгоритма БПФ, цикл усреднения или Цикл преобразования координат операндов массива, хранящегося в блоке 7 оперативной памяти. При этом количество элементарных операций в цикле равно количеству N операндов в массиве. Блок управления i, получив код элементарной операции с шины 17, выдает управляющие сигналы в блоки 1, 3, 4 и 12, по которым происходит в этих-блоках неоднократмое выполнение . заданной элементарней операции до тех пор, пока из блока 16 не поступает новый код элементарной операции. В это же время блок 18 и группа 19 регистров согласно подпрограмме производят вычисления последовательности а,цресов операндов, результатов и констант, участвующих в вычислении элементарной операции, причем время вычисления одной элементарной операции равно времени вычисления адресов для следующей элементарной операции.. Кроме того, для определения конца подпрограммы в одном из регистров группы 19 регистров ведется счет количества элементарных операций. По достижении заданного числа элементарных операций блок 18 с выхода выдает сигнал на вход 23 блока 20 с1Дресации,по которому происходит возврат из подпрограмм и из блока 16 памяти программ выбирается следующая команда. В то время, когда в блоках 1, 3, 4 и 12 вычисляется 1-я элементарная операция, из блока 7 оперативной памяти считываются щ буферзный регистр 13 исходные данные для 1+,1-й элементарной операции и из буферного регистра 15 в блок 7 оперативной памяти зап1 сываются результаты i-1-й элементарной операции.

Таким образом, в процессоре осуществляется совмещение во времени определения адресов операндов, резултатов и констант, обращение к блоку 7 оперативной памяти, обращение к блоку 6 памяти констант и непосредственно вычисление элементарной операции блоками 1,3, 4, 5 и 12, что позволяет загрузить все блоки процессора и получить высокую производительность. Выполнение различных элементарных операций одним и тем же набором блоков 1, 3, 4, 5, 7 и 12 роз. воляет отказаться от применения блока преобразования координат и блока накопления, что упрощает процессор и уменьшает аппаратурные затраты.

,, i

Z PO -(-f

i 3 PO

i PO f 0

0. /7 Pff

i

{го IP/

/ox

|f/ i

i r

IГ2 I /o/ - I

°I иI

t

I g/ I

«

i

t 7У I On

Bo PI - .

ei PI -h/Y/ /r- /o/J

Ш

РГИ xl - xl

EDZZm

-|Ш1.и,.У

ДТП

f 7

I p/ H-/ /;/ -

f1 A -

,IZI3L ,

j/f

;l.

I /3 лн/ I

8Z Pf - Л4|

ftfm

p p/ - P/r

(риг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| H.J.Kolb.Sidnal Processing, 2(), р.339-3 4б | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Программируемый процессор спектральной обработки сигналов | 1978 |

|

SU744603A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-15—Публикация

1982-11-17—Подача