Изобретение относится к т4Ы |Игли- телыюЛ технике и может бьп ь использовано в качестве пррифериГшого yci- ройства универс.чл1,11ой 3Bf иысокой производительности для п 11числения элементарных функций 1 , 1пх, sinx,

COSX.

Цель изобретения - порьопение производительности за счет параллельного вычисления элементарных функций, организаичи асинхронного взаимодействия между устройствами процессора, что позволяет осущестпить конвейерную обработку данных, а также за сче одновременного обслуживания нескольких запросов на вычисление элементарных функций.

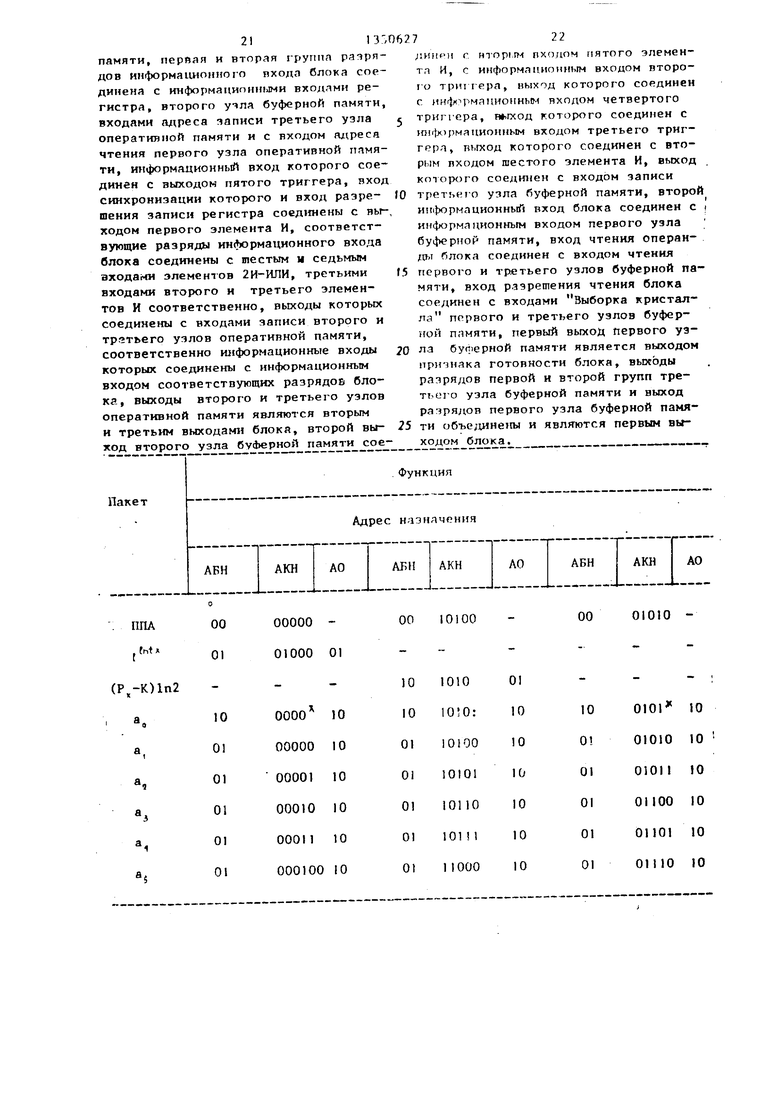

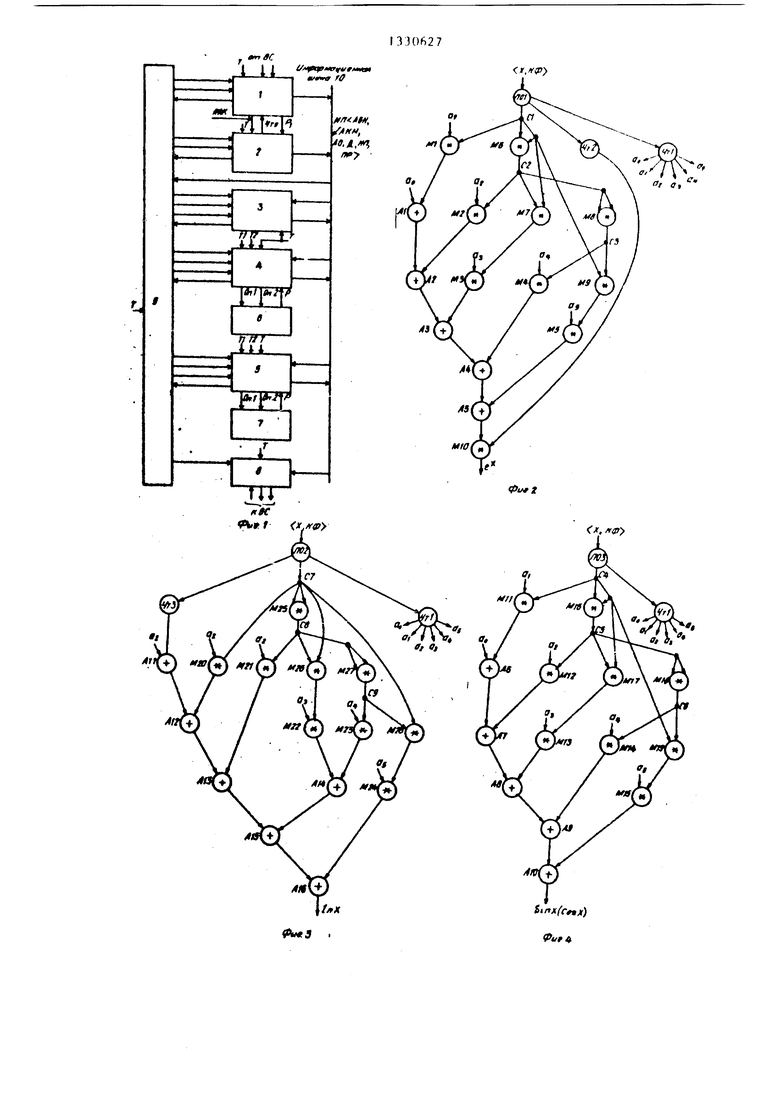

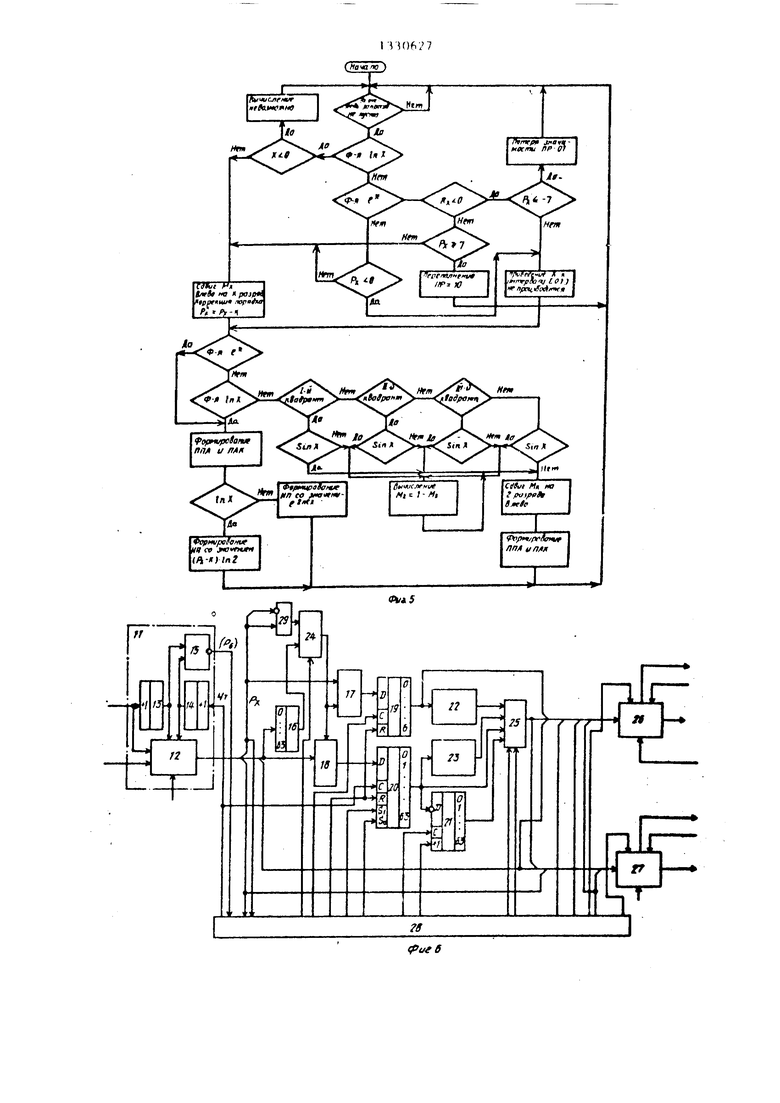

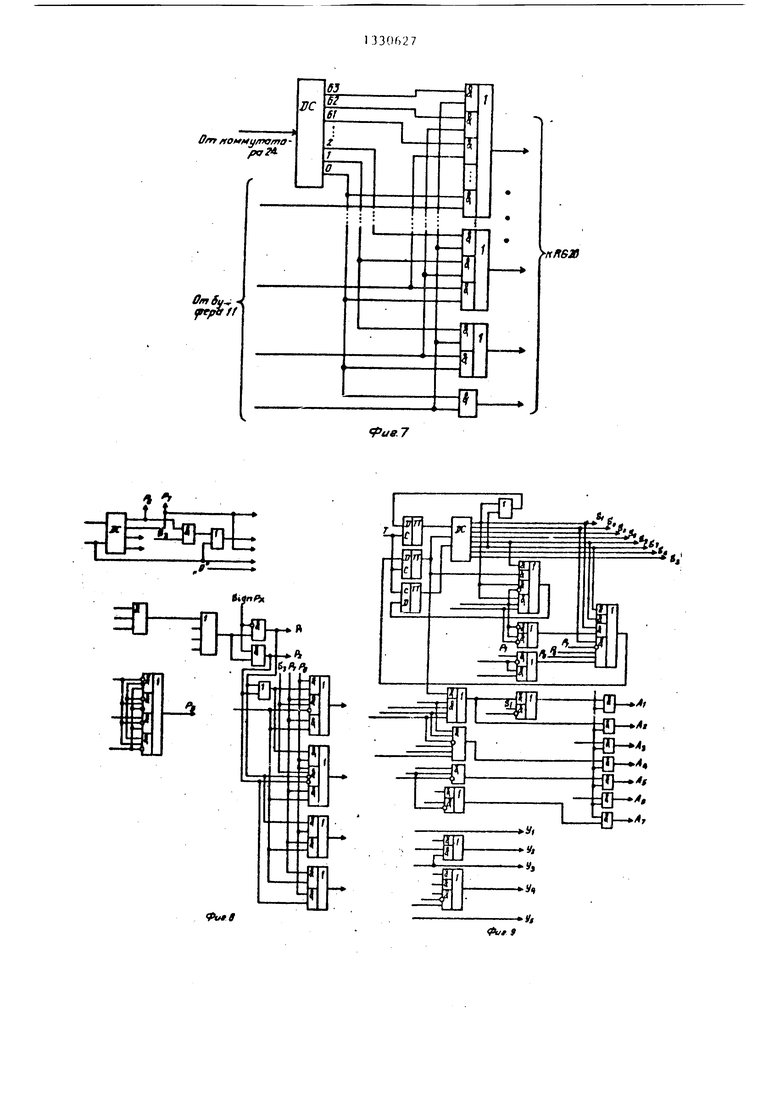

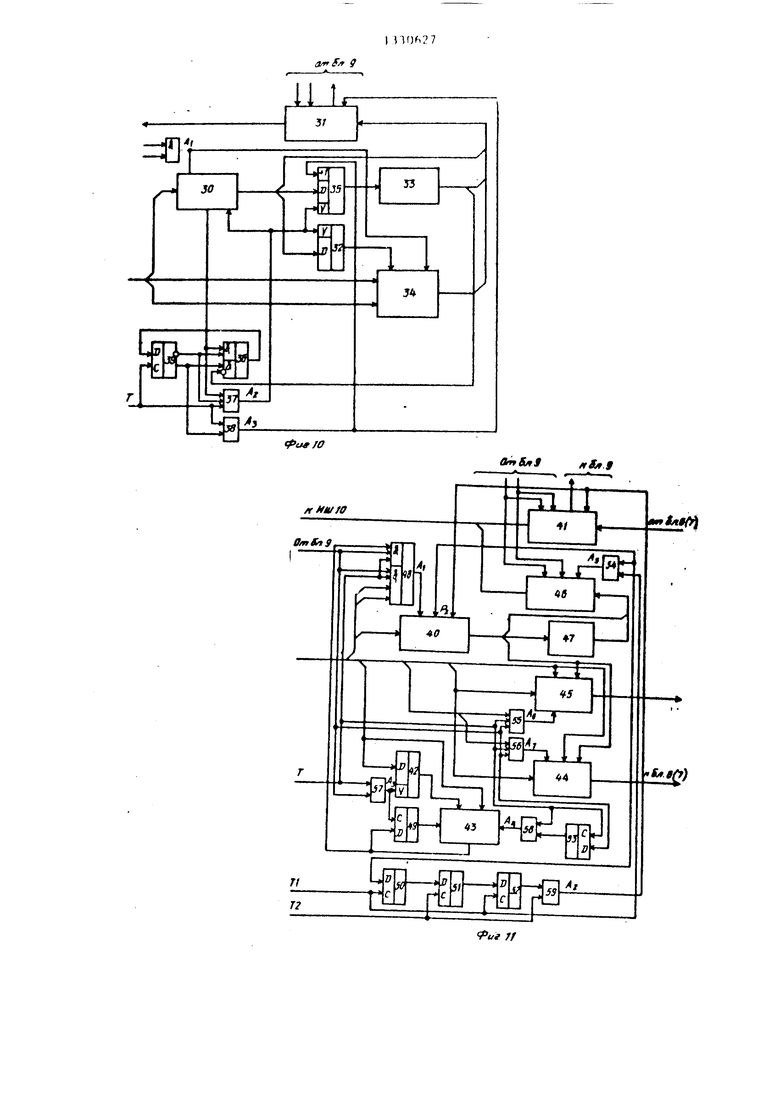

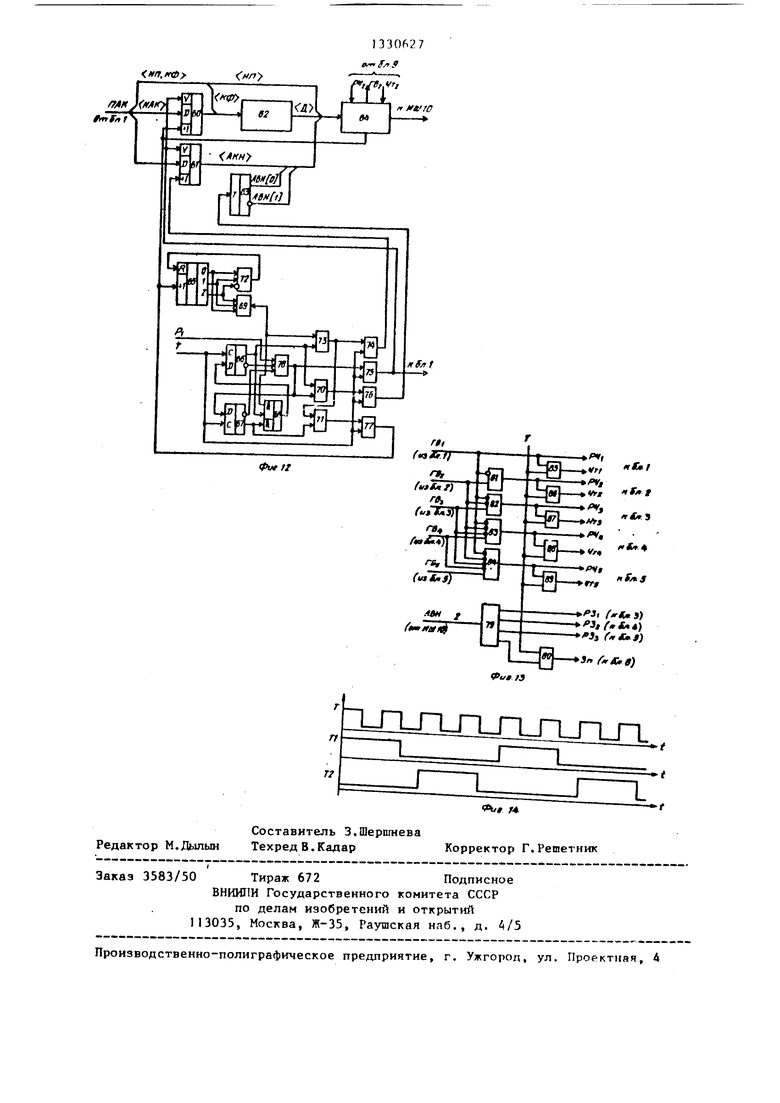

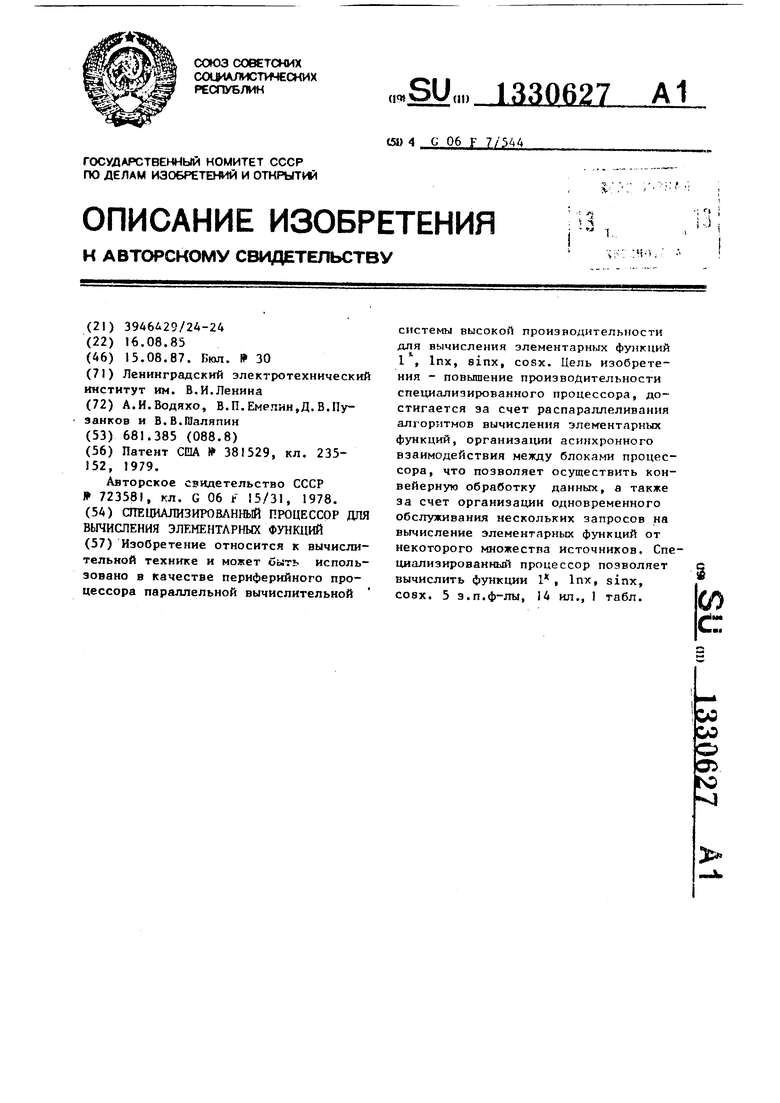

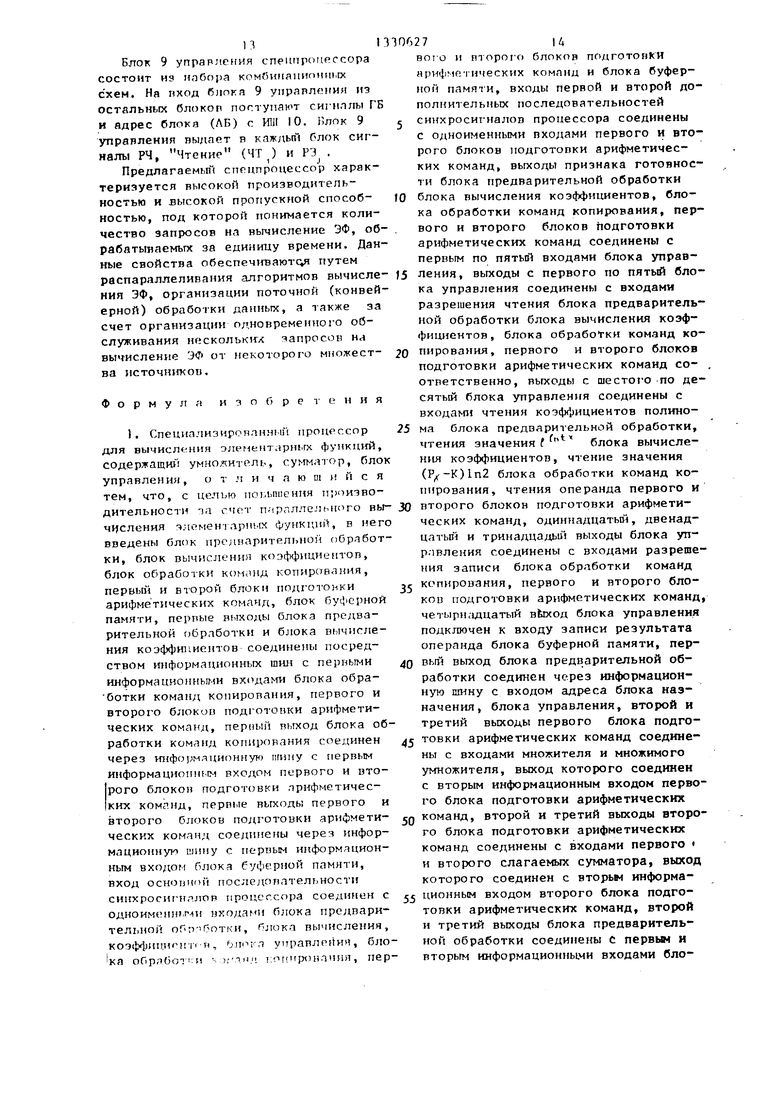

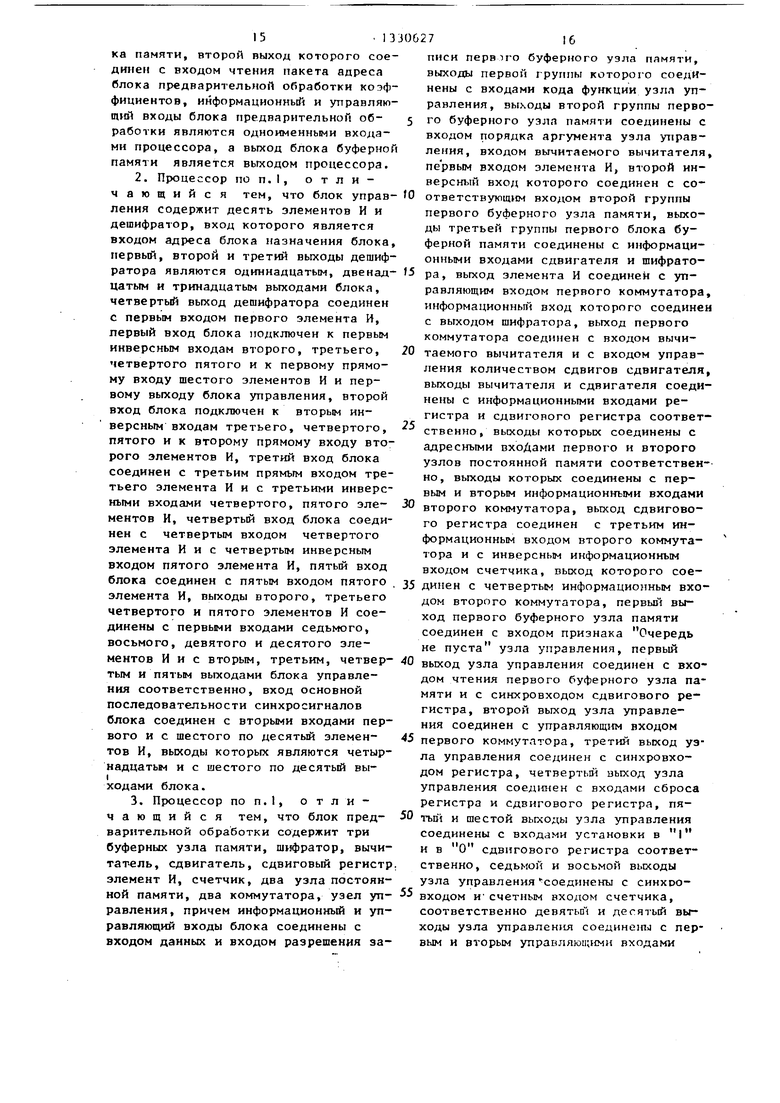

На фиг.1 приведена структурная схема спецпроцесгора; на фиг.2-4 - потоковые графы алгоритмов нмчис- лення 1 , Inx, fiinx(cosx) соответственно; на фиг.5 - алгоритм предварительной обработки аргу.мен1а; на фиг.6 - функциональнал схема блока предварительной оГфаОатки аргу.мента; на фиг. 7 - функционяльмая схема /:дви гателя; на фиг. 8 и 9 - функциг нлль- ная схема блока управления; на фиг.10 - функциональная схема блока обработки Kf). на фиг.II фуикциоилльная схема блока подготопки арифметических команд; на ф1ГГ. 1 2 - функционал ьная схема блока вычисления ( фиииентов; на фиг.13 функциональная схема блока управления; на фиг. 1ц - испольэуег-иле последовательности синхросигналов.

Снеииали-ифОБанньй процессор (фиг.1) содерл .ит блок 1 пре/.,варитель ной обработки (НПО), блок 2 вычисления K034xJ nuHi. HTou (RK), блок J обработки команд копирования (БОКК), блок 4 и 5 (юд1 отовки арифметических команд (BILAK), множительное устройство 6 (ЬГУ) сумматор 7, блок 8 буферной памяти, бпок 9 упранления (НУ), информаииоину uitniy 10 (ИШ).

БГЮ служи 1 ;viH нриведе нич аргумента функции к И|(те) (О, 1 ) фо1)миро вания паксич aiu t coi к ПЗУ, где хра- няп ся ко-,)ф.1п1ии :П М полинома.

БК CJiV ; ; - i ,1. :.;раир 1 ия (1ИП.исн тов anniiQK .ii u; , i:.rr го т олияома, уп- равлс:1И;1 i:. j -oii и формироп.чния

очерод roi - -г m ; ; ; и.1И нтос .

;f)vl r,-i iiv Р М;Г |1Я к омГ .ЧД KCnHp-,. lUiI : . . - :; Ь ИЧ ( с н:; ( МИрОx.-iiiiiM 1чсрг ди речультатоп конирова™ пни.

служит для хранения арифметических команд, приема входных информационных пакетов, обработки команд, I oioHMx к выполнения), и формировання операндов /итя множительного устройства и сумматора, формирования очереди

рочультаюн выполнения команд.

FilK) (фиг. 6) содержит буферный узел II памяти, состоящий из оперативного запоминающего устройства 12, счетчиков 13 и 14, схемы 15 сравнеg НИИ, шифратора 16, вычитателя 7,

сдвигателя 18, регистра 19, сдвигового регистра 20, счетчика 21, двух уз- лоп постоянной памяти 22 н 23, двух коммутаторов 24 и 25, двух буферных

уплов 26-27 памяти, узла 28 управле- нил и элемента И 29.

КОКК 3 (фиг.10) содержит два узла 30 и 31 буферной памяти, ре- . гисч р 32, узел 33 постоянной памяти,

5 34 оперативной памяти, счетчик 33, элемент 2И-ИПИ 36, два элемента И 37 и 38, триггер 39.

БПЛК 4 и 5 (фиг.1) содержит два узпа 40 н 41 буферной памяти, ре0 гистр 42, три узла 43-45 оперативной памяти, узел 46 буферной памяти, А7 постоянной памяти, эле- 2И-ИЛИ 48, ня1ь триггеров 49-53, шесть элементоп И 54-59.

FK (фиг.12) содержит счетчики 60

и 61, узел 62 постоянной памяти,

триггер 63, буферный узел 64 памяти, счетчик 65, два триггера 66 и 67, элемент 2И-Ш1И 68, три элемента ИЛИ 69- 71, семь элементов И 72-78.

Блок 9 управления (фиг.13) содержит дешифратор 79 и десять элементов Ь К 79-89; буферные узлы 11, 30, 40, 42, 26, 27, 31 н 46 памяти и буфе piibm узел 8 памяти идентичны по составу входящих в них блоков и выполняемым ими функциями узлу II.

Вьгчнсление элементарных функций ()Ф) от аргумента в форме с плаваю- nteu запятой разделяется на три этапа.

O На первом этапе выполняется приведе- )ие ; ргумента функции к интервалу (O.i). На втором этапе выполняется чгание коэф4)ициентов аппроксимирующего полинома из ПЗУ, а на третьем эта пе - вычисление полинома и постобработка для функци 1 и Inx.

Приведение функции к заданному интервалу основано на известных из ма- тсмати.ки cou 1 НотенияА.

0

5

31ЛЗ 6 /

функция 1 . сп, 1«

де 1 - функция от целой чястн

ч еиЬ аргумента; 1 - функция от дробной части аргумента, аппроксимируемая полиномом. Функция

1п(х) - ln()-() 1п2,

де Z - аргумент приведеиия к интервалу (0,1);

Р - порядок исходного аргумента; К - число сдвигов влево мантиссы

исходного аргумента; п(1+ Z) - аппроксимируется полиномом. Функция

10

15

20

рьг ко к иг эо сут вы он Кро вр co чи да со са к по чи в да есл ют но тел

где V - аргумент, приведенный к интервалу (О,1);

аппроксимируется полиномом.

Вычисление значения функции на интервале 0-1 для всех функций выполняется одинаково. Функция раскладывается в степенной ряд, число членов которого определяется исходя из требуемой точности вычислений. Расчеты показывают, что при работе с форматом с плавающей запятой, принять в ЕС ЭВМ (7 разрядов - порядок и 56 разрядов - мантисса), число членов ряда составляет 5,

F(x)

, 1

3 4

X а X +а

.где а,а

,а - коэффициенты

Постобработка для

разложения, фуикции 1 включает в себя умножение значения

, f Ht «

многочлена на величину 1 , а для функции 1п(х) - сложение значения полинома и константы ()1п2.

Наиболее наглядно процесс вычисления ЭФ с помощью предлагаемого процессора можно представить в виде графов алгоритмов (фиг.2-4). Каждая вер- шира такого графа отождествляется с определенной командой, а дуги являются информационными связями, по кото

рьгм передакптя aaiiHi-io fT комяиды к команде. Комли;ът считаетгя г-отопой к ры11олне1ипо, когда п нее пог 1упнли иге иеобход1тм1.к данные. Тпким o6fir - эом, в каждьп момет npfMeiiH может сутцес цовять несколько команд, готовых к выполнению, и, следовательно, они могут вынолня 1.С.Я одноррем - sifio . Кроме того, для осупюствления одновременной обработки нескольких чанро- cof) но одной и той же программе BI.I- числення элементарной функции все данные снабжаются призуьтком (индексом), соответствуюц1тм номеру процесса, из которого произошло обращение к спецпроцессору. Под процессом здесь поннмается один из параллельн 1х вычислительных процессов, протекающих в ВС. С учетом этого признака команда становится готовой к выполнению, если поступившие для нее данные имеют один и тот же признак НП, т.е. относятся к одному и тому же вычислительному процессу.

Процесс вычисления ЭФ начинается по мере поступления запросов в узел 11 (фиг.6).

Запрос на вычисление ЭФ имеет следующую структуру:

КФ

}т

5

0

5

0

5

где КФ - код ЭФ (2 разряда);

X - аргумент ЭФ (для ЕС ЭВМ 64

разряда);

НП - номер процесса, иа которого произошло обращение к спецпроцессору (4 разряда).

Узел 11 работает следующим образом.

В начальном состоянии содержимое пятого и mecTOi o счетчиков 13 и 14 равно нулю. Посредством управляющего сигнала из ВС происходит запись информации в узел 12 и увеличение содержимого счетчика 13 на единицу. Новое состояние счетчика соответствует адресу ячейки узла 12,в которую в дальнейшем будет происходить запись следующего запроса на вычисление элементарной функцин. После записи запроса в узел 12 на выходе (ОП схемы сравнения появляется сигнал Очередь не пуста, который поступает н узел 28 управления. Запись в узел 12 может производиться несколько раз, при этом образуется очередь запросов.

При чтении запросов из узла 12 содержимое счетчика 14 соответствует

5i:« U)62

адресу ячейки, в которой находится первый запрос из очереди запросов. После чтения запроса из узла 12 содержимое счетчика 14 увеличивается на Г, т.е. происходит переход к ячейке, содержащей следующий запрос из очереди запросо. Чтение запросов может происходить до тех пор, пока содержимое счетчика 14 не будет рав-- ным содержимому счетчика 13, что сви- jg детельствует об отсутствии запросов на вычисление элементарных функций Узел 12 построен на микросхемах

ПР - признак результата. Обмен информацией между блоками

типа KI802, что позволяет производить

одновременно и независимо запись и 5осуществляется следующим образом, чтение информации, это в свою очередь Блоки-источники ИП посьшаит в

дает возможность организовать асинх-блок 9 управления сигналы Готовность

ронное взаимодействие между ВС иблока (ГБ) для передачи ИП (фиг.

спецпроцессором.и 13). Блок управления в соответстрии

Первь|й, второй, третий и четверт ый уп приоритетами блоков подключает выузлы 34, 43, 44 и 45 соответственноход одного из готовых блоков к ИШ 10

построены также на микросхемах ти-путем формирования сигнала Разрешить

па К1802.чтение (РЧ), после чего на ИШ 10 поВ предла1 аемом процессоре исполь- является ИП, содержащий АБН блока уп- зуется три последовательности синхро- 25равления 9, в зависимости от АБН фор- сигналов: основная последовательностьмирует сигнал Разрешить запись (РЗ), с периодом Т типа меандр, вспомога-которьп позволяет записать ИП в соот- TejibHbie последовательности Т и Т2,ветствующий блок назначения по прибы- сдвинутые относительно друг другатию си гхроимпульса (,Т). В следующем на полпериода. Длительность сигналов JQтакте работы процессора может прои- Т1 и. Т2 равна 3/2 Т (фиг.14).зойти обмен данными между двумя другиОбмен информацией между блоками процессора имеет асинхронный характер и осуществляется с помощью информационных пакетов ( ИП ) посредством бло35

ми блоками процессора. Каждый блок- источник ИП имеет выходной буфер с трехстабильными выходами, за счет чего осуществляется работа с ИШ 10. В каждый момент времени посредством блока 9 с Ш 10 взаимодействуют только два блока: блок-источн{п ИП и блок- приемник данного ИП.

ка управления. Обмен ИП осуществляет через информационную шину ЭИШ 10. ИП имеет следующую структуру:

где АБН - адрес блока назначения.

- адрес команды назначения внутри блока;

- адрос назначения, представляющий АБН, АК, АО;,

- адргм: операнда внутри коман- Abi;

0

00 - д-тии( )Л не коступлет в команду

О - даннор поступает на 2-Г о операнда

10- данное поступает на место

1-го операнда

11- данное поступает на место

1 и 2-го операндов; ИГ - номер (идентификатор) процессора;

Д - значение передаваемого ценно го;

ПР - признак результата. Обмен информацией между блоками

ми блоками процессора. Каждый блок- источник ИП имеет выходной буфер с трехстабильными выходами, за счет чего осуществляется работа с ИШ 10. В каждый момент времени посредством блока 9 с Ш 10 взаимодействуют только два блока: блок-источн{п ИП и блок- приемник данного ИП.

С выхода узла 11 код функции поступает в узел 27 и узел 28 управления, номер процесса поступает в узлы 26 и 27, мантисса аргумента поступает на шифратор 16 и на сдвига- тель 18, порядок аргумента - в узел 28 управления и вычитатель 17. При появлении аргумента ЭФ узел 28 управления начинает проверку его корректности согласно алгоритму на фиг.5. В результате этой проверки формируется код признака результата ПР :

00- аргумент функции корректен

01- при вычислении произойдет

потеря значимости

10- при вычислении произойдет

переполнение

11- вычисление невозможно.

ПР

Если аргумент корректен, то начинается его предварительная обработ7

ка (фиг.5), которая заключается в приведении аргумента (X) функции к интервалу (0,1), коррекции мантиссы для функций sinx или cosx в зависимости от номера квадранта, в который попадает аргумент функции (вычисляется 1-М при необходимости), формировании 11П, инициирующего вычисление аппроксимирующего полинома, формировании ИП со значениями ()1п2 для функций 1пх и 1 и в формировании пакета адреса коэффициентов (ПАК).

Предварительная обработки для все функций начинается со сдвига мантисс аргумента в сдвигателе 18 в случае положительного порядка (). Если сдвиг не производится. В случае функции 1 и sinx сдвиг осуществляется до равенства порядка нулю. Количество сдвигов (К) формируется с по- мощью схемы И 39 (если sign Р О, то К Р , иначе К 0. Для функции 1пх мантисса М,

. сдвигается влево до первой единицы в старших разрядах

сдвигающего регистра 20 плюс еще оди сдвиг. Количество сдвигов определяется кодом на выходе шифратора 16:К N+I, Где N - номер старшей единицы в мантиссе М. Вычисление происходит путем установки в О старшего разряда информационного входа шифра

Р -К

f j

тора 16. Коррекция порядка Р, вьтолняется с помощью вычитателя 17. Результат фиксируется на регистре 19 и служит адресом к ПЗУ 22, где хранятся величины ()1п2.

Сдвинутая мантисса поступает на сдвигаюоцш регистр 20, 1-8-й разряды которого используются для хранения

имеющий следующую структуру: КФ, -Mp (9-19), ПАКН и НП, где КФ - код ЭФ; М (9-19) - старшие разряды мантисс используемые для формирования адрес эс коэффициентов; НАКН - начальный адрес команд назначения, равный адрес команды, в которую поступает коэффициент а, (т.е. НАКН-00000 - для 1 НАКН-01010 - для sinx и НАКН-10100

целой части аргумента ( ), и слу- 40 Д 1пх, что следует из размещения

жит адресом к узлу 23, где хранятся величины 1 , 9-63-й разряды используются для хранения мантиссь.

Номер квадранта, в котором находится аргумент функций sin(x),cos(x), определяется значением 9 и 10-го разрядов. В случае 11 и IV квадрантов для sinx или 1 и 1II квадрантов для COSX выполняется коррекция мантиссы путем формирования дополнения до 1 с помощью счетчика 21. Для этого мантисса, находящаяся в сдвигающем регистре 20, записывается в счетчик 21 в обратном коде, после чего к его

содержимому прибавляется I . После коррекции 9 и 10-й разряды мантиссы не используются, поэтому производится ее сдвиг на 2 разряда влево в сдвигающем регистре 20.

(о

06278

В случае вычисления функций 1 и 1пх происходит обращение к узлам 22 нлн 23.

В заключении предварительно об- 5 работки необходимо сформировать информационные пакеты (Ю1), которые будут инициировать последующие этапы вычисления ЭФ.

пнсывается

ЯП приведенного аргумента должен содержать адрес назначения (АН), состоящий из АБН, АКН и АО, далее аргумент, приведенный к интервалу (0,1), затем ПП и ПР формнруются и узел 28 управления, а НП передается без изменения из запроса на вычисление ЭФ, находящегося в узле 11. Аргумент к моменту-формирования пакета находится или в сдвигающем регистре 20, или в счетчике 21. АН также формируется в узле 28 управления с учетом размещения в памяти программы вычисления полинома и постобработки (таблица).

Пакет приведенного аргумента зав узел 26, откуда он в дальнейшем передается в соответствующий блок назначения. Одновременно с пакетом приведенного аргумента формируется пакет адреса коэффициентов (ПАК) аппроксимирующего полинома.

пнсывается

имеющий следующую структуру: КФ, -Mpi (9-19), ПАКН и НП, где КФ - код ЭФ; М (9-19) - старшие разряды мантиссы, используемые для формирования адреса коэффициентов; НАКН - начальный адрес команд назначения, равный адресу команды, в которую поступает коэффициент а, (т.е. НАКН-00000 - для 1 , НАКН-01010 - для sinx и НАКН-10100 Д 1пх, что следует из размещения

45

программы вычисления полинома и постобработки, см. таблицу); НП - номер процесса.

КФ и НП передаются без изменения из запроса, находящегося в узле 11, М (9-19) к моменту формирования пакета находится или в сдвигающем регистре 20 (9-19), или в счетчике 21 50 (9-19), а НАКН то же самое что и АКН в пакете приведенного аргумента

(величина (9-19) является начальным адресом коэффициентов).

Готовый пакет адреса коэффициентов 55 помещается в узел 27.

Пакет, содержащий значения (Ру -К)1п2 и , имеет анплогичную структуру, что и пакет приведенного аргумента.

flocjio lOi o, КПК пикет ;uip 4 Kn-it}i- фициемто пометен и уюл 27, формируется сигнал Fivijirp ИР пуст. По сигналу начпнаем я .чГштл 1JK (фиг. 12). Котф4.|нцие1п .I гюлииокя (п л ) нпхо- дятсп р после до) ;г1Т Л.и1.1Х .ччР11кпх учла 62. Адрес кп-1ффициептл я . чаписыплк

вается ил в счетчик 61, ко:}фф1шиепт, ра 63, АКН с

н счетчик 60,,ч ИАКН - Р,|.|брачиый из узла 62 Л1И с выходов Т1)игге- рыходов счетчика 61 и

20

25

30

НП поступают на информационные пходы узла 6А. Г1олучен1(И}1 111 паписыняетсл в выходной буфер 6А, а содержимое счетчика 60 (адрес козсМ ициента) и содер- (5 жнмое счетчика 61 (АКН) унеличинаются на единицу. Команды ут ноження, ц которые поступают ко .ф4)ициенты а -а , расгголожены и памяти команд и последовательных ячрйклх н в той 1(ослр;1,о- вательности, н когорой выбираются указанные коч(1.1ф|И1И(. нты. для того, чтобь: неслоД5 и-11г ий )11ииент попадал в сооч всп стнук.и;ую команду, достаточно унеличтктть АКМ на Cfiv.- ницу.

ВД.альнейшем процедура выборки коэффидиентои продолжается аналот ич- но, тюка не будут прочитаны и:( учла 62 все ко-.ффици нты . Признак 1Ч1ГО, ч 1 п np J ivriaH иос.пед- нш1 KO-nf 4 Muiieiri , форг.-.нруется с помощью c4f T4Hf а б.).

На вход НС КК 3 (фчг.Ь )) но инфор- мационно | liiiiHe liOC iynaniT адррс команды (АКН), Л1, дл1 мые (Л), котор1 ге передпютс,я нп 11Н(| ормацнон11ые рходы узла 34, ЛК1 и 1111 - на информационные входы учла 30 и адрРСШ11е БХОДЫ (записи) утла 34. По сигналу РЗ из блока 9 упрапления AKli, Ш, Р записываются к у 1лы 30 и 34. По сигналу А2 из узла 30 считываются знсТче- ния АКН и ПП, коюрые записываются в счетчик 35, а Ш поступает непосредственно на информационный пход узла 31. Содержимое счетчика 5 является адресом к узлу 33, где хранятся команды копирования, содерж;1 ;ие призto Первый н второй БГ1АК 4 и 5 (фиг предназначены обработки команд умножения и сложения. Каждый из н осуществляет прием ИН по ИШ 10, оп ределяет готовые к выполнению кома ды, операнды готовьте комакд посьта н множительное устройство 6 или су матор 7, а после вьтолиения операц формируют ИП результатов.

Арифметические команды являются диухоперандными, поэтому не каждый ВНОИ1, прнГп,1вшт ИП приводит к появ лению ГО10ВОЙ команды (арифметичес кая команда готова, если для нее п ступнли два операнда). Вьщелим три состояния, в которых может находит ся арифметическая команда;

-команда свободна, т.е. для не не поступил ни один операнд;

-команда активна, т.е. для нее поступил один из операндов (непажн к а кой);

-команда готова к выполнению. Определение готовности команд ос

щесч вляется с помощью узла 43 для 35 хранения тегов. В исходном состояни

во нсех ячейках данного узла находя ся О , что свидетельствует о том, что все команды свободны, т.е. не имеют операндов.

40 Г.слн в какую-то команду поступае операнд, то он записывается или в узел 44, или узел 45 операндов по адресу ЛК, НП а в узел 43 тегов по этому же адресу записывается эиачеи

45 тега, равное |, что соответствует активному состоянию команды. Если в дальнейшем в ту же команду поступае другой операнд, имеющий такой же ко НП, то команда должна быть готовой

мак конца копирования (ПКК) и АН, ко- 50 вьпюлнению, это определяется путем

торый поступает на ц)1формацноннь:й вход узла 31. Содержимое регистра 32 является a;i,pe - M для чтения данного из узла .34 и не меняется в ггроцессе копиронання. Чтение команды из узла 33 и дл) нч узла 34 производится (1ди М1 -1111о . Полученные значения АИ, Р г- с с И таписьшяются н узел 31 по .. .А . Jai eM содер

20

25

30

(5

0627К)

)«им:м счет чика 3) у1и мп1чипается па единпцу но сит налу АЗ. Нопое значение- АП ( пени же данньтми записывается и учел 41. Копирование продолжа- , ечс.ч до тех пор, ттока на выходе узла 33 HP поянмтся ПКК. Чтение информационны); пакетов (копий) производится по сигналам из блока 9 управления .

to Первый н второй БГ1АК 4 и 5 (фиг.1) предназначены обработки команд умножения и сложения. Каждый из них осуществляет прием ИН по ИШ 10, определяет готовые к выполнению команды, операнды готовьте комакд посьтает н множительное устройство 6 или сумматор 7, а после вьтолиения операций формируют ИП результатов.

Арифметические команды являются диухоперандными, поэтому не каждый ВНОИ1, прнГп,1вшт ИП приводит к появлению ГО10ВОЙ команды (арифметическая команда готова, если для нее по- ступнли два операнда). Вьщелим три состояния, в которых может находиться арифметическая команда;

-команда свободна, т.е. для нее не поступил ни один операнд;

-команда активна, т.е. для нее поступил один из операндов (непажно к а кой);

-команда готова к выполнению. Определение готовности команд осущесч вляется с помощью узла 43 для 35 хранения тегов. В исходном состоянии

во нсех ячейках данного узла находятся О , что свидетельствует о том, что все команды свободны, т.е. не имеют операндов.

40 Г.слн в какую-то команду поступает операнд, то он записывается или в узел 44, или узел 45 операндов по адресу ЛК, НП а в узел 43 тегов по этому же адресу записывается эиачеине

45 тега, равное |, что соответствует активному состоянию команды. Если в дальнейшем в ту же команду поступает другой операнд, имеющий такой же код НП, то команда должна быть готовой к

чтония тега из второго ОЗУ 43 тегов. Если тег равен l, то данный операнд последний и команда становится гото- о вой к выполнению. Ее адрес помещает- 55 ся в узел 46, операнд записывается или в узел 44, или узел 45 операндов, а значение тега равно О.

ИП, тгостуиившлй по ИШ 10, содержит АКБ, НП АО, Д, которые заггисываIIГВ062712

ются: AKH, НП - в узел Д6, регистр 2; рЫ110Л11е(гию компнд будут происходить Д - в узел 45; АО поступает на вход с одинаковой шктопой частотой, то записи узла 40 и на вход Запись уз- загрузка множительного устройства 6 лов 44 и 45. Кроме АКН, ИП поступают (сумматора 7) операндами будет не- на вход адрес запись узлов 44 и 45. г равномерной. Это следует из того, что Значения АКН и HI1 являются адресом вновь прибывший ИГ1 в каждом тякте по- ,Чтение узла 43, где хранятся те- рождает готовую к вьтолненик) команду ги (признаки). По тактовому импуль- приблизительно с вероятностью 0,5, су Т и сигналу РЗ блока 9 управления так как операндов в команде два. Не- значенне тега записывается в триг- tO равномерность потока готовых команд гер 49, а в регистр 42 записьгеаются можно сгладить, если осуществлять об- АКН и НП, которые служат адресом За- мен ИП через № 1 10 и прием ИП в пер- пись к второму узлу 43. В этом же вый и второй БПАК 4 и 5 на большей такте Т операнд, содержащийся в ИП, тактовой частоте по сравнению с обра- записывается или в узел 44, или 15 боткой готовых команд в первом и вто- узел 45. Если , то операнд запи- ром БПАК 4 и 5. Диаграмма, показываю- сывается в оба узла 44 и 45. Если зна щая соотношение тактовых частот, ис- чение тега на выходе второго узла-43 пользуемых в процессоре, показана на равно единице, то команда готова к фиг.14.

выполнению, ее адрес АК, а также НП 20 Окончательньй результат вычисления записываются в узел 40. В следующем (значение ЭФ) из первого или второ- такте инверсное значение теса, нахо- го БПАК 4 и 5 по ИШ 10 поступает в дящегося в триггере 49, записывается блок 8 буферной памяти. Блок 8 гене- в узел 43. рирует признак готовности результата,

25 который поступает в вычислительную

Далее производится обработка го- систему. По этому сигналу вычисли- товых к вьтолнению команд, адреса ко- тельная система сигналом Чтение торых находятся в узле 40. Если узел считывает ИП результата, непуст (признак Р2), то на его инфор- Вычисление полинома и постобработ- мационном выходе находится адрес оче- 30 ка осуществляются в соответствии с редности команды, готовой к выполне- программой, машинные коды которой нию АК и НП. АК передается в узел 47 представлены в таблице. команд для чтения готовой команды. Данная программа полностью соответ- а АК и НП - на адресные входы Чте- ствует потоковым графам алгоритмов ние узлов 44 и 45 для чтения операн-- 35 фиг. 2 - 4. Программа в записимос- дов. Чтение происходит одновременно ти от типа команд распределена по из узлов 44 и 45. Полученные операн- блокам: БОКК 3, БПАК 4, БПАК 3. Каж- ды передаются или в множительное уст- дая команда представляет собой АН ре- ройство -6, или в сумматор 7. Команда, зультата, состоящий из АБН, АКН и АО содержащая адрес назначения результа- 40 и признака конца команды (ПКК), иста, т.е. АБН, АКН, АО, а также НП, пользуемый только командами копиро- передаваемый без изменения из узла 40, вания. Команды копирования занимают перемещается в узел 41. Одновременно несколько ячеек в узле 33. Если ПКК с этим операнды направляются в кон- I , то ячейка является последней для вейерное МУ 6 (сумматор 7), имеющее 45 данной коман ;ы KonnpoeatrHH. В прог- глубину конвейера.рамме приняты следующие обозначения:

С помощью триггеров 50, 51 и 52 со- АБ - адрес блока; АК - адрес команды ответственно определяется момент по- внутри блока; ИК - идентификатор ко- явления результата на выходе МУ 6 или манды и ИКН - идентификатор команды сумматора 7 и его запись в узел 41. 50 назначения, согласно потоковым апго- При записи результата устанавливает- ритмам на фиг.2-4.

ся признак ГБ, свидетельствующий о Как отмечалось вьпае, адрес назна- появлении результата арифметической чения для пакета приведенного аргу- команды. Признак ГБ поступает в блок 9 мента, l ()1п2 и коэффициен- управления.55 тов полинома формируется в соответстОбработка арифметических команд вии с размещением команд в памяти. осуществляется конвейерным способом, В таблице приведены АН, которые однако если в первом и втором БПАК 4 формируются в НПО 1 для соответст- и 5 прием ИП и обработка го1чэвых к вующ1гх информационных пакетов.

Блок 9 управления спецпроцессора состоит иэ набора комбинаиипмш.гх схем. На «ход блока 9 упраплииия из остальных блокоп поступают сигналы ГБ и адрес блока (ЛБ) с И111 10. Блок 9 управления выдает в каждьп Слок сигналы РЧ, Чтение (ЧТ ) и РЭ .

Предлагаемьш спецпроцессор характеризуется высокой производительностью и высокой пропускной способ- ностью, под которой понимается количество запросов на вычисление ЭФ, об- рабатынаемьпс за единицу времени. ДанBOi o и торого блоков подготояКИ нрнфметических команд и блока буферной памя1И, входы первой и второй дополнительных последовательностей синхросигналов процессора соединены с Одноименными входами первого и второго блоков подготовки арифметических команд, вьгходы признака готовности блока предварительной обработки блока вычисления коэффи1и1еитов, блока обработки команд копирования, первого и второго блоков подготовки арифметических команд соединены с первым по пятый входами блока управные свойства обеспечиваютсу путем распараллеливания алгоритмов вычисле- f5 ления, выходы с первого по пятый бло- ния ЭФ, организации поточной (конвей- ка управления соединены с входами ерной) обработки данных, а также за

разрешения чтения блока предварительной обработки блока вычисления коэффициентов, блока обработки команд косчет организации одновременного обслуживания нескольких запросов на вычисление ЭФ от некоторого множества источников.

Формула изобретения

1. Специализнроплнньи процессор для вычисления эленеитарш.гх функций, содержащий умножитель, сумматор, блок управления, о т л и ч а ю ш и и с я тем, что, с целью поььпиення 1;)оизворазрешения чтения блока предварительной обработки блока вычисления коэффициентов, блока обработки команд ко20 пирова гия, первого и второго блоков подготовки арифметических команд соответственно, выходы с шестого по десятый блока управления соединены с входами чтения коэффициентов полино25 ма блока предварительной обработки, чтения значения f блока вычисления коэффициентов, чтение значения )1п2 блока обработки команд копирования, чтения операнда первого и дительности та счет п.чрпллельного вы- 30 второго блоков подготовки арифмети- числения -элементарных функций, в него ческих команд, одиннадцатый, двенадцатьп1 и тринадцадый выходы блока уп- рпвления соединены с входами разрешения записи блока обработки команд 5 копирования, первого и второго блоков подготовки арифметических команд, четырм щцатый вЬкод блока управления подключен к входу записи результата операнда блока буферной памяти, пер- 40 вый выход блока предварительной обработки соединен через информационную пшну с входом адреса блока назначения, блока управления, второй и третий выходы первого блока подговведены блок прсдварител1энон обработки, блок вычисления коэффициентов, блок обработки команд копирования, первьвЧ и второй блоки подготоьки арифметических , блок буферной памяти, первые в111ходы блока предварительной обработки и блока вычисления коэффициентов соединены посредством информационных шин с первыми ннформационныТ Ж вxoдa fll блока обра- ботки команд копирования, первого и второго блокоп подготовки арифметических команд, пероый выход блока тонки арифметических команд соединены с входами множителя и множимого умножителя, выход которого соединен с вторым информационным входом первого блока подготовки арифметических второго блоков подготовки арифмети- Q команд, второй и третий выходы второ- ческих команд соединены через инфор- го блока подготовки арифметических

команд соединены с входами первого и второго слагаемых сумматора, выход которого соединен с вторым информа- сипхросиг-пплов процессора соединен с ционным входом второго блока подго- одноимепш. иходаии блока предвари- тонки арифметических команд, второй тельной оГ рчботки, блока вычисления, и третий выходы блока предваритель- K03(}xiJHn,Hf H if н, fj jinir.T управлейни, бло- ной обработки соединены С первым и ка обрябо и )г Л.. ()нлиия, пер- вторым информационными входами блоработки команд копирования соединен через илфо1;мяци(1ннук) пгниу с первым информационном входом первого и второго блоков подготс вки арифметических команд, первые выходы первого и

мационную ииму с первым информационным входом блока буферной памяти, вход основиг й последопательности

BOi o и торого блоков подготояКИ нрнфметических команд и блока буферной памя1И, входы первой и второй дополнительных последовательностей синхросигналов процессора соединены с Одноименными входами первого и второго блоков подготовки арифметических команд, вьгходы признака готовности блока предварительной обработки блока вычисления коэффи1и1еитов, блока обработки команд копирования, первого и второго блоков подготовки арифметических команд соединены с первым по пятый входами блока управления, выходы с первого по пятый бло- ка управления соединены с входами

ления, выходы с первого по пятый бло- ка управления соединены с входами

разрешения чтения блока предварительной обработки блока вычисления коэффициентов, блока обработки команд копирова гия, первого и второго блоков подготовки арифметических команд соответственно, выходы с шестого по десятый блока управления соединены с входами чтения коэффициентов полинома блока предварительной обработки, чтения значения f блока вычисления коэффициентов, чтение значения )1п2 блока обработки команд кока памяти, второй выход которого соединен с входом чтения пакета адреса блока предварительной обработки коэффициентов, информационньй и управляющий входы блока предварительной обработки являются Одноименными входами процессора, а выход блока буферной памяти является выходом процессора.

2. Прюцессор по П.1, отличающийся

ления содержит десять элементов И и дешифратор, вход которого является входом адреса блока назначения блока, первый, второй и третий выходы дешифписи первтго буферного узла памяти, выходы первой группы которого соединены с входами кода функции узла управления, выходы второй группы первого буферного узла памяти соединены с входом порядка аргумента узла управления, входом вычитаемого вычитателя, пе рвым входом элемента И, второй инверсный вход которого соединен с со- тем, что блок управ- О ответствутощим входом второй группы

первого буферного узла памяти, выходы третьей группы первого блока буферной памяти соединены с информационными входами сдвигателя и шифраторатора являются одиннадцатым, двенад- f5 pa, выход элемента И соединен с упцатым и тринадцатым выходами блока, четвертый вькод дешифратора соединен с первым входом первого элемента И, первый вход блока подключен к первым инверсным входам второго, третьего, четвертого пятого и к первому прямому входу шестого элементов И и первому выходу блока управления, второй вход блока подключен к вторым инверсным входам третьего, четвертого, пятого и к второму прямому входу второго элементов И, третий вход блока соединен с третьим прямьгм входом третьего элемента И и с третьими инверсными входами четвертого, пятого элементов И, четвертый вход блока соединен с четвертым входом четвертого элемента И и с четвертым инверсным входом пятого элемента И, пятый вход блока соединен с пятым входом пятого элемента И, выходы второго, третьего четвертого и пятого элементов И соединены с первыми входами седьмого, восьмого, девятого и десятого элементов И и с вторым, третьим, четвертым и пятым выходами блока управления соответственно, вход основной последовательности синхросигналов блока соединен с вторыми входами первого и с шестого по десятьй элементов И, выходы которых являются четыр- надцатьм и с шестого по десятый выходами блока.

3. Прюцессор по п. 1, отличающийся тем, что блок предварительной обработки содержит три буферных узла памяти, шифратор, вычи- татель, сдвигатель, сдвиговый регистр элемент И, счетчик, два уэла постоянной памяти, два коммутатора, узел управления, причем информационный и управляющий входы блока соединены с входом данных и входом разрешения записи первтго буферного узла памяти, выходы первой группы которого соединены с входами кода функции узла управления, выходы второй группы первого буферного узла памяти соединены с входом порядка аргумента узла управления, входом вычитаемого вычитателя, пе рвым входом элемента И, второй ин0

5

0

равляющнм входом первого коммутатора, информационньй вход которого соединен с выходом шифратора, выход первого коммутатора соединен с входом вычн- таемого вычнтателя и с входом управления количеством сдвигов сдвигателя, выходы вычитателя и сдвигателя соединены с информационными входами регистра и сдвигового регистра соответственно, выходы которых соединены с адресными вхоДами первого и второго узлов постоянной памяти соответствен-- но, выходы которых соединены с первым и вторым информационными входами второго коммутатора, выход сдвигового регистра соединен с третьим информационным входом второго коммутатора и с инверсным информационным входом счетчика, выход которого сое- 5 динен с четвертым информационным входом второго коммутатора, первый выход первого буферного узла памяти соединен с входом признака Очередь не пуста узла управления, первый выход узла управления соединен с входом чтения первого буферного узла памяти и с синхровходом сдвигового регистра, второй выход узла управления соединен с управляющим входом первого коммутатора, третий выход уэла управления соединен с синхровходом регистра, четвертый выход узла управления соединен с входами сброса регистра и сдвигового регистра, пя- TbDi и шестой выходы узла управления соединены с входами установки в | и в О сдвигового регистра соответственно, седьмой и восьмой выходы узла управления соединены с синхоо- входом И счетным входом счетчика, соответственно девятьп и десятый выходы узла управления соединеши с первым И вторым управляющими входами

0

5

0

5

второго коммутаторя, второй выход, первого узла буферной памяти, выход регистра, выход второго коммутатора, с одиннадцатого по тринадца1ый выходы узла управления соединены с соответствующими разрядами информационио- го входа второго узЛа буферной памяти, второй выход первого блока буферной памяти, выход второго коммутатора и тринадцатый выход блока соедине- fO дом шестого элемента И, выход которо- ны с разрядами информационного входа го соединен со счетными входами перво- третьего буферного узла памяти, че- го и второго счетчиков и входом раз- тырнадцатый и пятнадцатый бло- решения записи буферного узла памяти, ка соединены с входами разрешения записи второго и третьего буферных уз- 15 лов памяти, вход чтения коэффициентов

первый, второй выходы третьего счетчика соединены с первыми, вторыми входами седьмого элемента И и третьего элемента ИЛИ соответственно, тре- Гнй выход третьего счетчика соединен с третьим инверсным входом седьмого

полинома блока соединен с входом разрешения чтения второго буферного узла памяти, вход разрешения чтения

блока соединен с входом выборки крис- 20 элемента И и третьим входом третьего

тагла второго буферного узла памяти, первый и второй выходы второго буферного узла памяти являются первым и вторым выходами блока, первый и

элемента ИЛИ, выход третьего элемеи та ИЛИ соединен с вторым входом вто рого элемен та И и третьим входом эл мента 2И-Ш1И, выход которого соедивторой выходы третьего буферного уз- 25 иен с D-входом первого D-триггера,

ла памяти являются третьим и четвертым выходами блока.

4. Процессор ПОП.1, отличающийся тем, что блок коэфвход осноьной последовательности синхроимпульсов блока соединен с вторыми входами с третьего по шестой элементов И, выход третьего элеменфициентов содержит три счетчика, узел ЗО та И соединен с вторым выходом блока постоянной памяти, буферный узел па- и входами разрешения записи первого

и второго счетчиков, выход пятого элемента И соединен со счетным входом

второго счетчика, выход седьмого элемяти, два D-триггера, Т-триггер, элемент 2И-ИЛИ, три элемента ИЛИ, семь элементов И, причем первая группа разрядог информационного входа блока мента И соединен с входом сброса тре- соедине 1а с D-входами первого и вто- тьего счетчика, третья группа разря- рого счетчиков, выход первого счетчи- дов информационного входа блока, вы- ка и вторая группа разрядов информа- ход узла постоянной памяти, выход

ционного входа блока соединены с соответствующими разрядами третьего входа узла постоянной памяти, вход основной последовательности синхросигналов блока соединен с С-входами первого и второго D-триггеров, инверсные выходы которых соединены с первым и вторым входами первого элемента И, прямой выход первого D-триггера соединен с первыми входами втовторого счетчика, прямой и инверсньй 40 выходы Т-трнггера соединены с соответствующими разрядами информационного входа узла буферной памяти, входы разрешения чтения и чтения значения { блока соединены с входами 45 чтения и выборки кристалла узла буферной памяти соответственно, выход Очередь не пуста является выходом признака готовности блока, выход узла буферной памяти является первым

рого элемента И, первого элемента ИЛИ, элемента 2И-ИЛИ, прямой выход второ- 50 выходом блока.

го элемента И, первого элемента ИЛИ, . Процессор по п.1, о т л и - элемента 2И-ИЛИ, прямой вькод второ- ч а w п; и и с я тем, что блок обра- го D-триггера соединены с вторым вхо- ботки команд копирования содержит дом элемента 2H-R TH и первым входом два узла буферной памяти, три элемен- второго элемента ИЛИ, второй информа- 55 элемент 2И-ИЛИ, триггер, счет- циоиньш вход блока соединен с третьим чик, регистр, узел постоянной памя- входом перного элемента И, выход ко- ти, узел оперативной памяти, вход ос- торого соединен с первым входом тре- новной последовательности синхросиг- тьего элемента И, пторым входом пер- налов диска соединен с первым входом

вого элемента ИЛИ и с D-входом второго D-триггера, выход первого элемен- тп ИЛИ соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом Т-триггера, выход второго элемента И соединен с первым входом элемента И и вторым входом второго элемента ИЛИ, выход которого соединен с первым вхо

дом шестого элемента И, выход которо- го соединен со счетными входами перво- го и второго счетчиков и входом раз- решения записи буферного узла памяти,

первый, второй выходы третьего счетчика соединены с первыми, вторыми входами седьмого элемента И и третьего элемента ИЛИ соответственно, тре- Гнй выход третьего счетчика соединен с третьим инверсным входом седьмого

элемента ИЛИ, выход третьего элемеи- та ИЛИ соединен с вторым входом второго элемен та И и третьим входом элемента 2И-Ш1И, выход которого соедивход осноьной последовательности синхроимпульсов блока соединен с вторыми входами с третьего по шестой элементов И, выход третьего элеменвторого счетчика, выход седьмого элемента И соединен с входом сброса тре- тьего счетчика, третья группа разря- дов информационного входа блока, вы- ход узла постоянной памяти, выход

второго счетчика, прямой и инверсньй 40 выходы Т-трнггера соединены с соответствующими разрядами информационного входа узла буферной памяти, входы разрешения чтения и чтения значения { блока соединены с входами 45 чтения и выборки кристалла узла буферной памяти соответственно, выход Очередь не пуста является выходом признака готовности блока, выход узла буферной памяти является первым

50 выходом блока.

19 133062720

первого элемента И, второй вход кото-ра:1ряды пррвои и пторой групим

рого соединен с входом разрешения за-млииоиного входа блока сосдинон. с

писи блока, выход первого элемента Иинформационным входом первого утла

соединен с адресныни входами первогобуферной память и входом пдрося -эаузла буферной памяти и узла оператив- писи уила оператипиой пямяти, инг юрной памяти, вход основной последова-мационныП вход которого соодинеи с

тельности синхросигналов блока сое-разрядами третьей группы нмформяпион-динен с первыми входами второго иного входа блока.

третьего элементов И и входом синх-6. Процессор по п, I, о т л и - роииэации триггера, прямой выход ко-10 ч а ю щ и и с я тем, что блок под- торого соединен с вторым входом тре-готовки арифметических команд содер- тьего элемента И и первым входом эле-жит три узла оператппной памяпи, три мента 2И-ИПИ, выход которого соеди-учла буферной памяти, узел постоянней с информационным входом триггера,ной памяти, пять триггеров, эле- инверсный выход которого соединен с15 мент 2 И-ИЛИ, шесть элементов И, ре- вторыми входами второго элемента Игистр, причем нход основной последо- и элемента 2И-ИЛИ, третьи входы кото-вателыюсти синхросигналов блока сое- рьпс соединены с выходом признакадипен с первыми входами с первого по

Очередь не пуста узла буферной па-четвертый элементов И, с входом синх- мяти, выход второго элемента И сое-20 ропизации первого триггера, первын и динен с входом чтения первого узлавторым входами элемента 2И-ИГ1Н, вход Йуферной памяти и входом разрешенияпервой дополнительной последователь- записи счетчика и регистра, вьгхидпости синхроимпульсов блока соединен счетчика соединен с адресным входомс входами си|гхронизации второго и узла постоянной памяти, выход разря-25 третьего триггеров и с первым входом дов первой группы которого соединенпятог о элемента И, вход второй допол- с информационным входом соответствую-нительной последовательности синхрю- щих разрядов первого узла буфернойимпульсов блока соединен с входом памяти, выход соответствующего разря-синхрюнизации четвертого триггера и да узла постояиной памяти соединен с30 первым входом шестого элемента И, вы- четвертым инверсным входом элемен-ход которого соединен с входом чте- та 2И-ИЛИ, выход третьего элемента Иния второго и с входами записи перво- соединен со счетным входом счетчикаго узлов буферной памяти, вход разре- и входом записи второго узла буфер-шения записи блока соединен с третыгм ной памяти выход разрядов первой и35 четвертым входами элемента 2И-ИЛИ, второй группы первого узла буфернойс вторыми входами с первого по третий памяти соединен с информационным вхо-элементов И и с информпционным входом дом соответствующих разрядов регист-первого триггера, выход которого сое- ра, выход которого соединен с входомдинен с вторым вхрдом четвертого эле- адреса чтения узла оперативной памя-40 мента И, выход которого соединен с ти, вьгходы разрядов первой группывходом записи первого узла оператив- первого узла буферной памяти соедине-ной памяти, выход которого соединен ны с информационными входами счетчи-с информационным входом пятого триг- ка, выходы разрядов вторюй группыгера и с пятым входом элемента 2И-ИЛИ, первого узла буферной памяти соедине-45 выход которого соединен с входом эа- ны с информационным входом соответст-писи второго узла буферной памяти, вующих разрядов второго узла буфер-выход разрядов первой группы которо- ной памяти, выход разрядов узла one-го соединен с адресш.гм входом узла ративной памяти соединен с информа-постоянной памяти, выход разрядов ционным входом соответствующих разря-50 первой группы которого соедт1ен с ин- дов второго узла буферной памяти,формпционным входом первой группы входы разрешения чтения копируемогоразрядов третьего узла буферной памя- операнда блока соединены с входамити, вторая группа разрядов инсуюрма- , выбора кристалла и чтения второго уз-ционного входа которого соединена с ла буферной памяти, выход признака55 выходом разрядов второй группы второ- Очередь не пуста которого являетсяго блока буферной памяти, РМХОДЫ раз- выходом признака готовности блока,рядов первой и второй группы которо- второй выход второго узла буфернойго соединены с входам . чтения памяти является первым вьпсодом блока,второго и третьего узлов оперятивной

21 п

памяти, первая и вторая группа разрядов информационного входа блока соединена с информаиионними входами регистра, второго учла буферной памяти, входами адреса записи третьего узла оперативной памяти и с входом адреса чтения первого узла оперативной памяти, информационный вход которого соединен с выходом пятого триггера, вход синхронизации которого и вход разрешения записи регистра соединены с выходом первого элемента И, соответствующие разряды инЛормационного входа блока соединены с шестым и седьмым аходаьш элементов 2И-ИЛИ, третьими входами второго и третьего элемен тов И соответственно, выходы которых соединены с входами записи второго и третьего узлов оперативной памяти, соответственно информационные входы которых соединены с информационным входом соответствующих разрядов блока, выходы второго и третьего узлов оперативной памяти являются вторым и третьим выходами блока, второй выход второго узла буферной памяти сое722

диирц г нторггм входом пятого элемента И, с информациояным входом второго тритгера, выход которого соединен с инф(1рмаииомным входом четвертого

триггера, в.гход которого соединен с )рмаиионпым входом третьего триг- грра, выход которого соединен с вторым входом шестого элемента И, вьосод кторого соединен с входом записи

третье1-о узла буферной памяти, второй ии|}юрмационный вход блока соединен с t информационным входом первого узла буферной памяти, вход чтения операнда блока соединен с входом чтения

первого и третьего узлов буферной памяти, вход разрешения чтения блока соединен с входами Выборка кристалла первого и третьего узлов буферной памяти, первый выход первого узла буферной памяти является выходом признака готовности блока, выходы разрядов первой и второй групп тре- Tijoro узла буферной памяти и выход разрядов первого узла буферной памяти объеданеяы и являются первым выходом блока.

пвС

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая логическая машина | 1975 |

|

SU532862A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве периферийного процессора параллельной вычислительной системы BbicoKoil производительности для вычисления элементарных функций 1 , 1пх, sinx, COSX. Цель изобретения - повышение производительности специализированного процессора, достигается за счет распараллеливания алгоритмов вычисления элементарных функций, организации асинхрониого взаимодействия между блоками процессора, что позволяет осуществить кои- вейериую обработку данных, а также за счет организации одновременного обслуживания нескольких запросов на вычисление элементарных функций от некоторого множества источников. Спе- (и ализированный процессор позволяет вычислить функции 1, 1пх, sinx, СО8Х. 5 з.п.ф-лы, 14 ил., I табл.

7в рие6

t

fue.7

т

J

V ±b.i

tijnf

9W

r -I

т

лЛг

т

€L

-rQ}-,

-:ffl- I

,

-y/

йитЛг g

11 Ir

tf af /O

Л КяЗf,S/ff

/(MMttO

9f

.НП.1Гф)

, Л

).

IQ-icj

А// Г4

Редактор М.Дыпьш

Составитель З.Шершнева Техред В.Кадар

Заказ 3583/50 Тираж 672Подписное

ВНИИГ1И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г.Решетник

| Патент США № , кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-08-16—Подача