Изобретение относится к вычислительной технике и может использоваться в вычислительных системах и устройствах цифровой обработки ин формации. Известно устройство, которое содержит четыре умножителя, шесть сум маторов, блоки памяти, индексное устройство, устройство упрсшления Это устройство обладает единым алгоритмом вычисления, вбплощеиным в жесткой структуре, эффективность таких процессоров требует согласо-вания по быстродействию всех входящих Б него блоков. Недостатком устройства является невозможность реализовать другой . алгоритм вычисления, более производительный при имеющихся характеристиках отдельных блоков. Наиболее близким по технической сущности к предлагаемому изобретению является программируемый процес сор обработки сигналов, применяемый также для спектральной обработки сигналов, в котором можно реализова различные алгоритмы вычислений. Он содержит блок суммирования-вычитания, блок умножения, входные шины данных которых подсоединены к первой магистрали данных,- первый блок регистров общего назначения, выходные шины данных которого также соединены с первой магистралью данных, управля сщие входы всех указанных блоков соединены между собой, блок памяти программ ii койстакт, блок сопряжения и обмена, выходные шины данных которых соединены со второй Магистралью данных/ индексный блок, выход которого соединен с адресными шинами блока памяти программ t и констант и адресными шинс1ми блока сопряжения и обмена, входные шины последнего блока, а также индексного блока соединены с третьей магистралью данных, блок управления, входные шины данных которого соеди-нены со второй магистралью данных, управляющие выходы - со входами уп1:1авления блока памяти программ и констант, индексного блока, блока сопряжения и обмена-, блоки нормализации и деления, первые и вторые входы которых соединены соответственно со второй и третьей магистралями данных, выходы - с первой магистралью данных, управлякядие входы

С выходом блока управления, индексный блок, второй информационный вход которого соединен с третьей. магистралью данных, вход первого блока регистров общего назначения и выхода блоков умножения и суммированиявычитания соединены с первой магистралью данных, при этом дополнительные входы выходы блока сопряжения и обмена являются входами я выходами программируемого процессора 2 .

Недостатком этого процессора, имещего модульную структуру, является малое быстродействие, что объясняется ориентацией модульной структуры этого процессора на широкий класс задач и, в связи с этим, недостаточным учетом особенностей спектральных алгоритмов обработки сигналов .

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем, что. в программируемый процессор спектральной обработки сигналов, содержащий .сумматор, блок умножения, первый блок регистров, блок памяти констант и программ, блок адресации и блок сопряжения, причем информационые входы сумматора и блока умножения соединены через первую магистрал с выходом первого блока регистров, а управляющие входы первого блока регистров, сумматора и блока умножения соединены между собой, первый выход блока памяти констант и программ первая группа выходовблока сопряжен соединены через вторую магистраль с первым выходом блока управления, первая группа входов блока сопряжения соединены через третью магистрал с первым входом блока адресации, первый выход блока управления соединен с второй группой входов блока сопряжения, с первым входом блока памяти констант и программ и вторым входом блока адресации, вторая группа выходов и третья группа входов блока сопряжения являются соответственно выходами и входами процессора, введены коммутатор, второй блок. регистров, п блоков оперативной памяти, блок синхронизации, причем первый выход блока управления подключен к первым входам п блоков оперативной памяти, второго блока регистров, коммутатора и блока синхронизации, первый выход которого Соединен со вторыми входами второго блока регистров, п блоков оперативной памяти, с третьим входом блока памяти констант и программ, с третьей группой входов блока сопряжения и вторым входом блока управления, второй выход блока синхронизации подключен к вторым выходам блока умножения и коммутатора, третий вход которого соединен через первую магистрал

с выходами сумматора,блока умножения третьим входом коммутатора и вторым входом блока синхронизации, третий вход которого подключен ко вторым выходам первого блока регистров, сумматора и блока умножения, вторые выходы п блоков оперативной памяти и второго блока регистров соединены через вторую магистраль с четвертым входом коммутатора, второй выход котрого подключен через третью магистраль ко вторым входам второго блока регистров, п блоков оперативной памяти и ко второму выходу блока управления, а также тем, что блок сопряжения содержит узел связи с внутренн интерфейсом, узел преобразования координат и накопитель, первые выходы которых подключены соответственно к первой группе выходов блока, первые входы узла преобразования координат, узла связи с внутренним интерфейсом и накопителя подключены соответственно к первой группе входов блока, их вторые входы соединены соответственно со второй группой входов блока, вторые выходы узла преобразования координат, узла связи с внутренним интерфейсом и накопителя соединены соответственно со второй группой выходов блока, третьи входы и выходы узла связи с внутренним интерфейсом и накопителя, соединены соответственно с третьей группой входов и второй группой выходов блока, четвертый вход блока связи с внутренним интерфейсом соединён с входом блока.

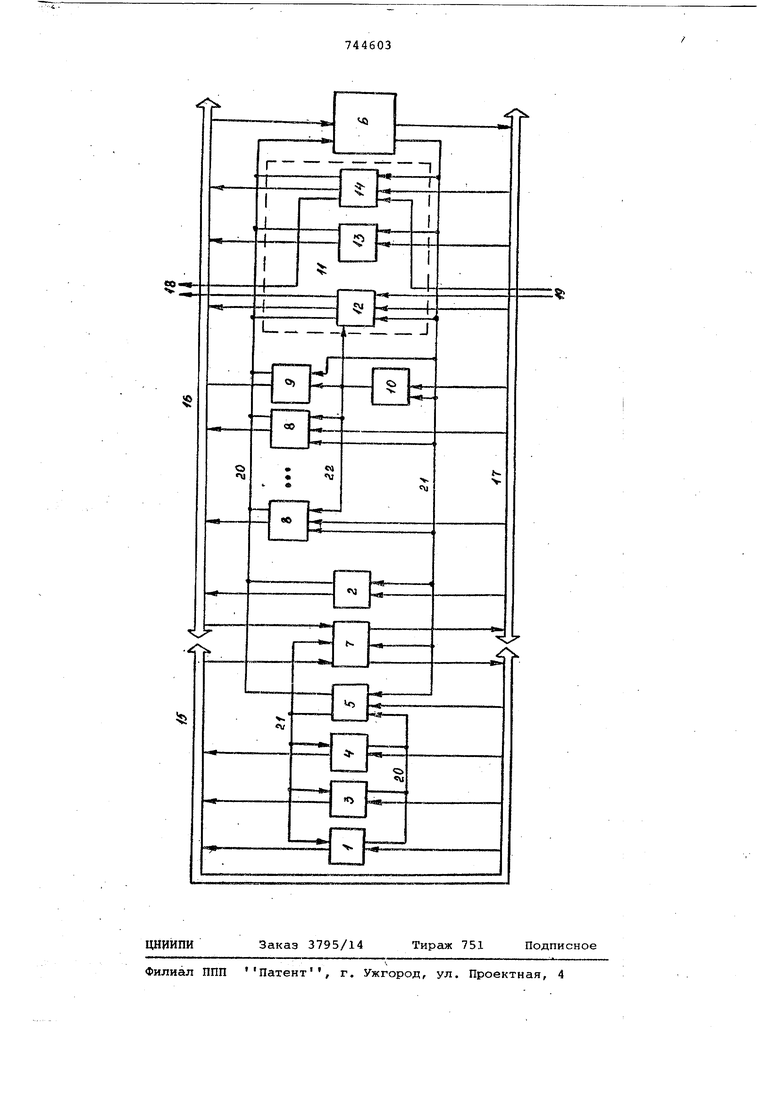

На чертеже представлена блок-схема программируемого процессора спектральной обработки сигналов.

Блок-схема содержит блоки 1,2 регистров, сумматор 3, блок 4 умножения, блок 5 управления, блок 6 синхронизации, коммутатор 7, п блоков 8 оперативной памяти, блок 9 памяти констант и программ, индексный блок 10 адресации, блок 11 сопряжения, который состоит из блока 12 связи с внутренним интерфейсом, блока 13 преобразования координат и накопителя 14, магистрали 15, 16, 17, выходы 18 процессора, входы 19 процессора, управляющие входы и выходы 20, 21 блоков управления, адресные шины 22.

Работа программируемого процессора спектральной обработки сигналов определяется конкретностью выбранного алгоритма быстрого преобразования Фурье (БПФ) 3, алгоритмов умножения на весовую функцию, вычисления амплитуды и фазы, алгоритмов усреднения (накопления) спектров.Так можно реализовывать на предложенной структуре алгоритмы БПФ на основе элементарных операций двухточечного преобразования Фурье, четырехточечного преобразования

Фурье и т.п. Формулы для двухточеч.ного преобразования Фурье имеют вид

(-j.2jK)

, + 2 п-,,-.-л-Хп.,-,,-р(),

1 - номер итерации (i

где

О, 1, 2, .. ., ecg(N - 1), Сама элементарная операция выполняется на блоках умножения и сумматоре 3, а также с использованием первого блока 1 регистров и под управлением блока 5. Все передачи между указанными блоками выполняются по первой магистрали данных. В первом блоке 1 регистров хранится исходная информация, записываемая в них из блоков 8 оперативной -памяти, константы, выбираемые из блока, результаты четырехточечного преобразования, которые из регистров заносятся в блоки 8.

Все пересылки между любым блоком 8, 9 памяти и первым блоком 1 регистров обеспечиваются через коммутатор 7, который управляется блоками б и 5 с помощью управляющих шин 21.

Вся адресация памяти рассматриваемом программируемом процессоре осуществляется блоком 10, в частности, этот блок обеспечивает выработку четырех текущих адресов для считывания новых операн,цов и адресов для записи результатов обработки четырехточечного преобразования Фурье, а также для выработки адреса константы. Все передачи адресов производятся по шинам 22.

Возможность подключения нескольких блоков 8 оперативной памяти позволяет получить высокую производительность алгоритмов БПФ ввиду . организация конвейерного способа обращения к блокам памяти. Тем самым имеется возможность согласовать быстродействие блоков 3 и 4.

В зависимости от назначения процессора спектральной обработки сигнлов блок 11 сопряжения может быть либо в минимальной комплект.ации, либо в максимальной. В последнем случае этот блок включает блок 12 связи с внутренним интерфейсом вычислительной системы, блок 13 преобразования координат, реализую. ... 744603

X + iy , А ехр ( iv)

щий операцию где

, « oirct y

накопитель 14. Последний блок осуществпяет вьщачу по сигналам, поступакщйм по шинам 19, результата АГ, одной из следугадих операций:

п К п- i rt-Jt 1,2,.... АГЧ KjA + + г. г

п 1,2,. . .

на внешние средства отображения либо регистрации информации.

Управление всем программируемым процессором осу11 ествляется по программе, которая составляется для конкретных характеристик имекидихся отдельных модулей и выбранного алгоритма БПФ. Блок 5 управления адресуется через третью магистраль и

через индексный блок 10 к блоку 9 памяти и выбирает за одно обращение очередную порцию команд, содержащихся S одном формате операндов, хранимых в этой памяти. Далее блок

5 управления реализует эти команды, управляя второй и третьей магистралями 16, 17 и коммутатором 7.

Блок 2 регистров служит некоторой сверхоперативной памятью, его

объем определяется количеством различных модулей и принятыми алгоритмами обработки.

Связь выхода блока 10 с одним из входов блока 12 обеспечивает формирование адресов как для внутренней

оперативной памяти блока 8, так и для памяти вычислительной системы, с которой идет обращение блока связи при обмене по внутреннему интерфейсу. Рассмотрим один из , примеров выполнения задачи вычисления прямого

дискретного преобразования Фурье от , одной порции информации, хранимой в блоке памяти 6ц с параллельным вычислением амплитуды и фазы от результата, полученного в предыдущем цикле при выполнении прямого дискретного преобразования Фурье.

Предыдущий результат хранится в блоке памяти 8. Причем происходит

накопление (простое суммирование массивов) амплитудного спектра и передача его в третий блок оперативной памяти 8.

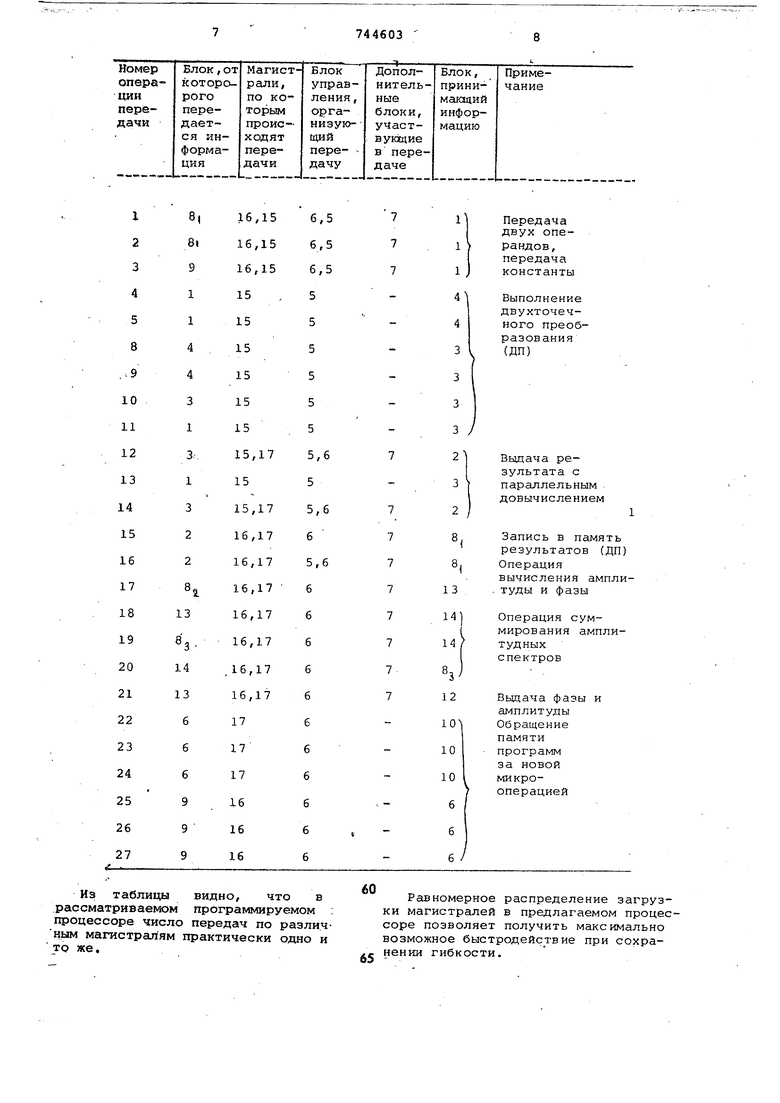

Последовательность операций передачи по магистралям для этого примера и для одного цикла вычислений представлена в таблице.

Из таблицы видно, что

в

рассматриваемом программируемом ; процессоре число передач по различным магистралям практически одно и то же.

Равномерное распределение загрузки магистралей в предлагаемом процессоре позволяет получить максимально возможное быстродействие при сохранении гибкости. Формула изобретения Программируемый процессор спектральной обработки сигналов, содержащий сумматор, блок умножения, пер вый блок регистров, блок памяти кон стант if программ, блок адресации и блок сопряжения, причем информацион входы сумматора и блока умножения соединены через первую маги тЕраль с выходом первого блока регистров, а управляющие входы первого блока регистров, сумматора и блока умножени соединены между собой, первый выход блока памяти констант и програм первая группа выходов блока сопряже ния соединены через вторую магистра с первым входом блока управления, первая группа входов блока сопряжения соединена через третьюмагистра в первым входом блока адресации, первый выход блока управления соеди нен с второй группой входов блока сопряжения, с первым входом блока памяти констант и программ и вторь№1 входом блока адресации, вторая группа выходов и третья группа входов блока сопряжения являются соответственно выходами и вxoдaJVIИ процессора, отличающийся тем, что, с целые повышения быстродействия, в процессор введены коммутатор, второй блок регистров, п блоков оперативной памяти, блок синхронизации, причем первый выход блока управления подключен к первым входам блоков оператив ной памяти, второго блока регистров, коммутатора и блока синхронизации, первый выход которого соединен со вторыми входс1ми второго блока регистров, п блоков оперативной памяти, с третьим входом блока памяти, констант и программ, с третьей группой входов блока сопряжения и вторым входом блока управления, вто рой выход блока синхронизации подключен к вторым выходам блока умножения и коммутатора, третий вход которого соединен через первую магистраль с выходами сумматора, блока умножения, третьим входом ком мутатора, вторым входом блока синхронизации, третий вход которого подключен ко вторым выходам первого блока регистров, сумматора и блока умножения, вторые выходы п блоков оперативной памяти и второго блока регистров соединены через вторую магистраль с четвертым входом коммутатора, второй выход которого подключен через третью магистраль ко вторым входам второго блока регистров, п блоков оперативной памяти и ко второму выходу блока управления. 2. Процессор по п. 1, о т л ичающийся тем, что блок сопряжения содержит узел связи с внутренним интерфейсом, узел преобразования координат и накопитель, первые выходы котЪрых подключены соответственно к первой группе выходов блока, первые, входы узла преобразования координат, узла связи с внутренним интерфейсом и накопителя подключены соответственно к первой группе входов блока, вторые выходы узла преобразования координат, узла .связи с внутренним интерфейсом и накопителя соединены соответственно со второй группойВыходов блока, третьи входы и выходы узла связи с внутренним интерфейсом и накопителя соединены соответственно с третьей группой входов и второй группой выходов блока, четвертый вход блока связи с внутренним интерфейсом соединен с входом блока. Источники информации, принятые во внимание при экспертизе, 1.Toukin А. Savage J. An app6i-r cation of correlation to radaz systems. - Radio and Engineer . 1972, GuCy, vofc. 42, №7, . p 344. 2,BCankensnip P. E. etc. l.SP/2 ргодгаптааЬбе signaB processore. Proc. Nat EBectron. Cnicago, 111, 1974, voE. 29, Oak Brook, 416 - 429.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 1998 |

|

RU2130641C1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734708A1 |

| Каскадный процессор спектральной обработки сигналов | 1978 |

|

SU742948A1 |

| Коррелятор вибросейсмических данных | 1989 |

|

SU1665326A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734707A1 |

| МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2008 |

|

RU2399089C2 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

Авторы

Даты

1980-06-30—Публикация

1978-03-20—Подача