Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих вычислительных систем.

Цель изобретения - повышение быстродействия процессора.

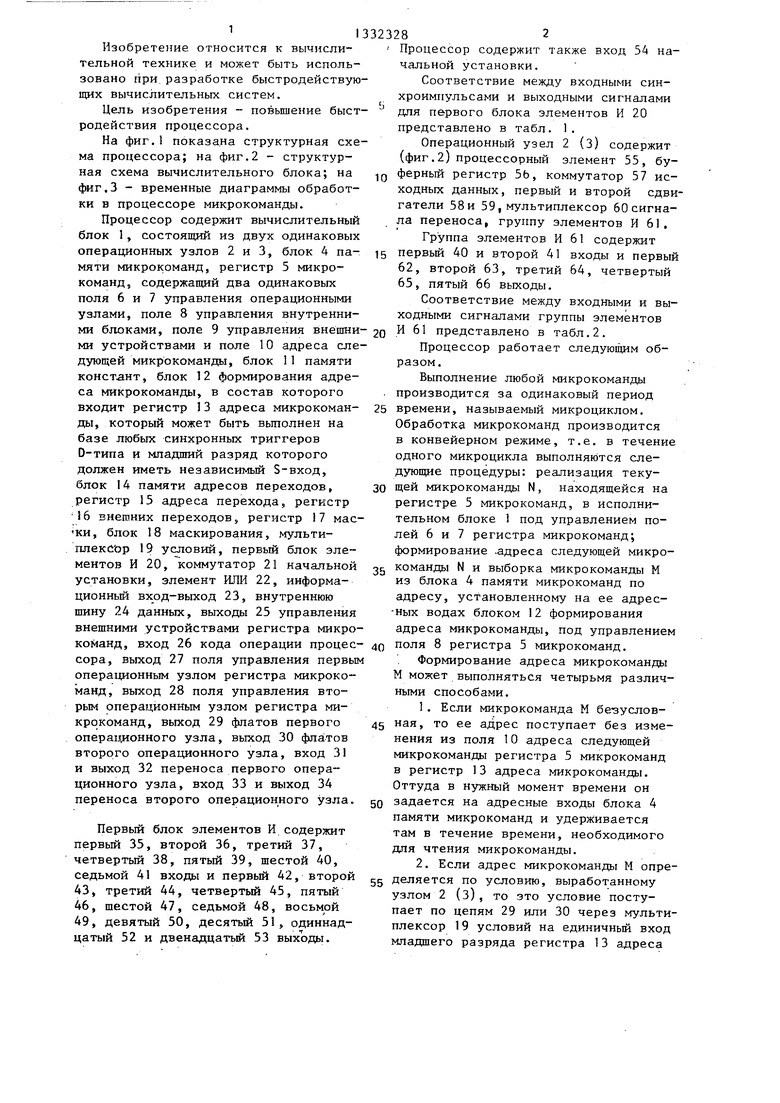

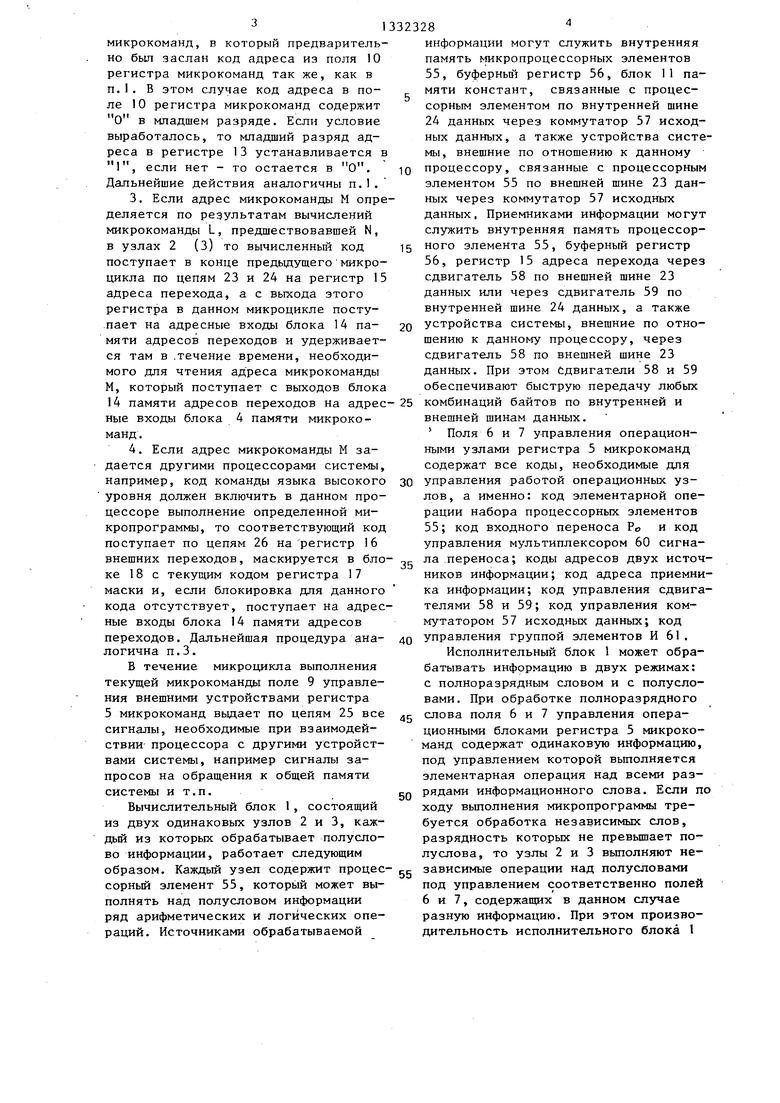

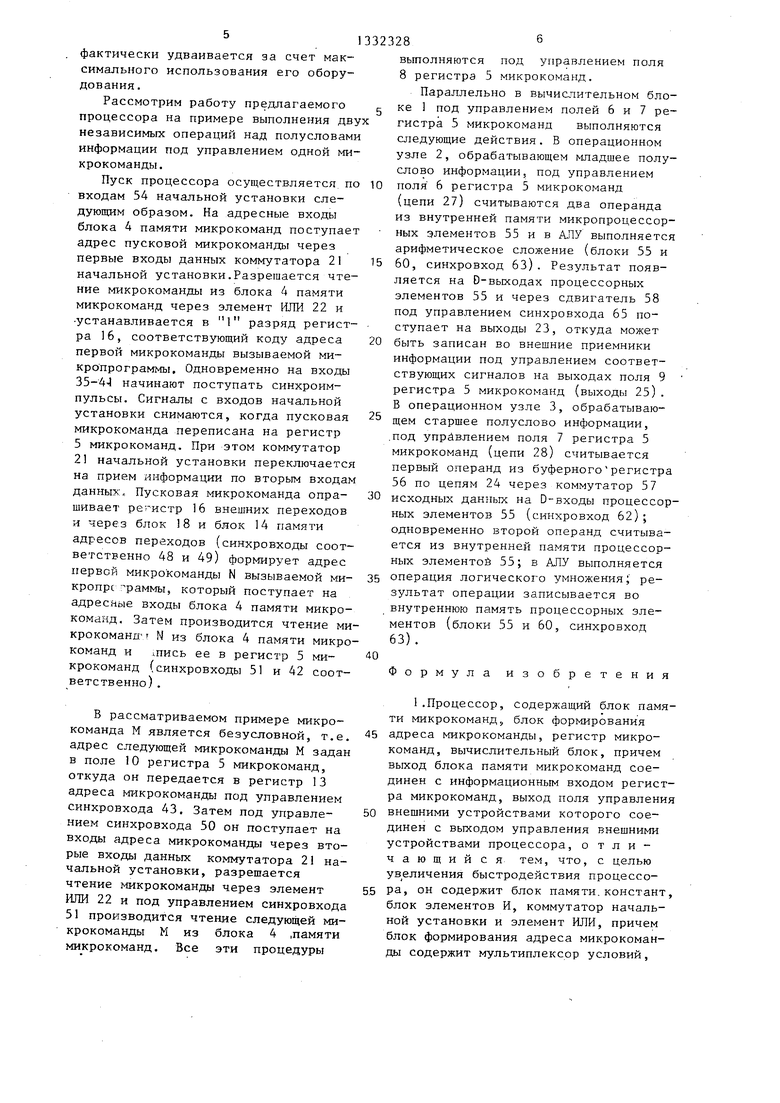

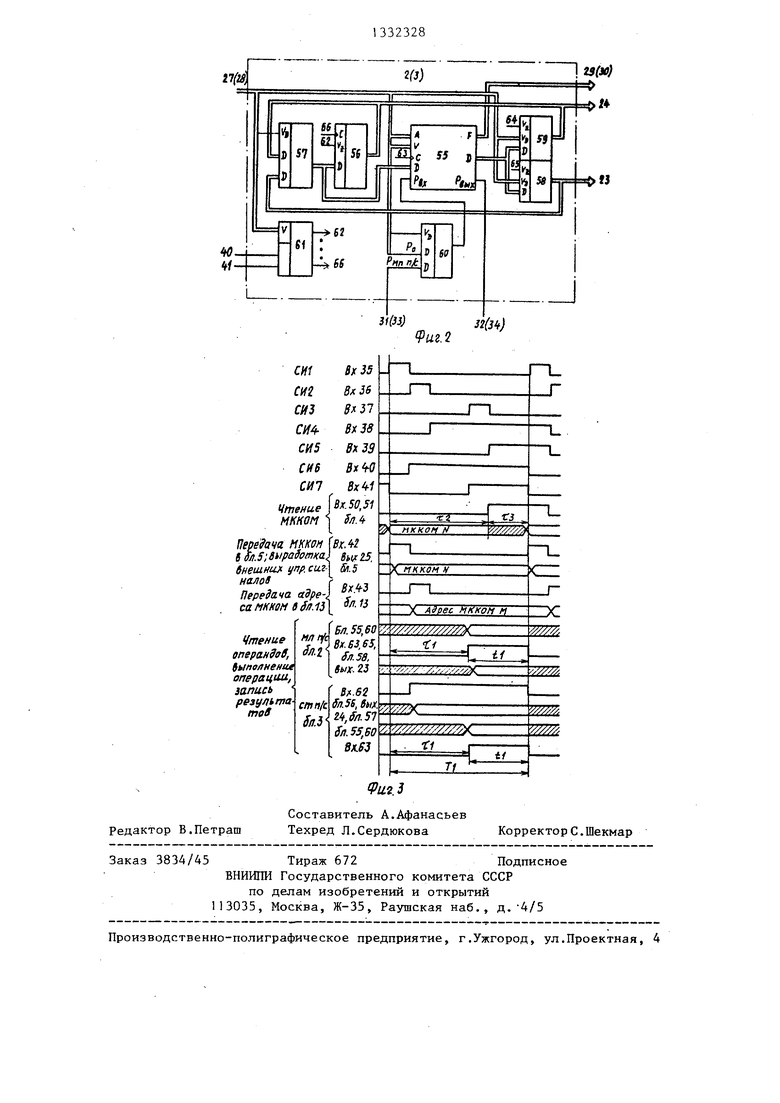

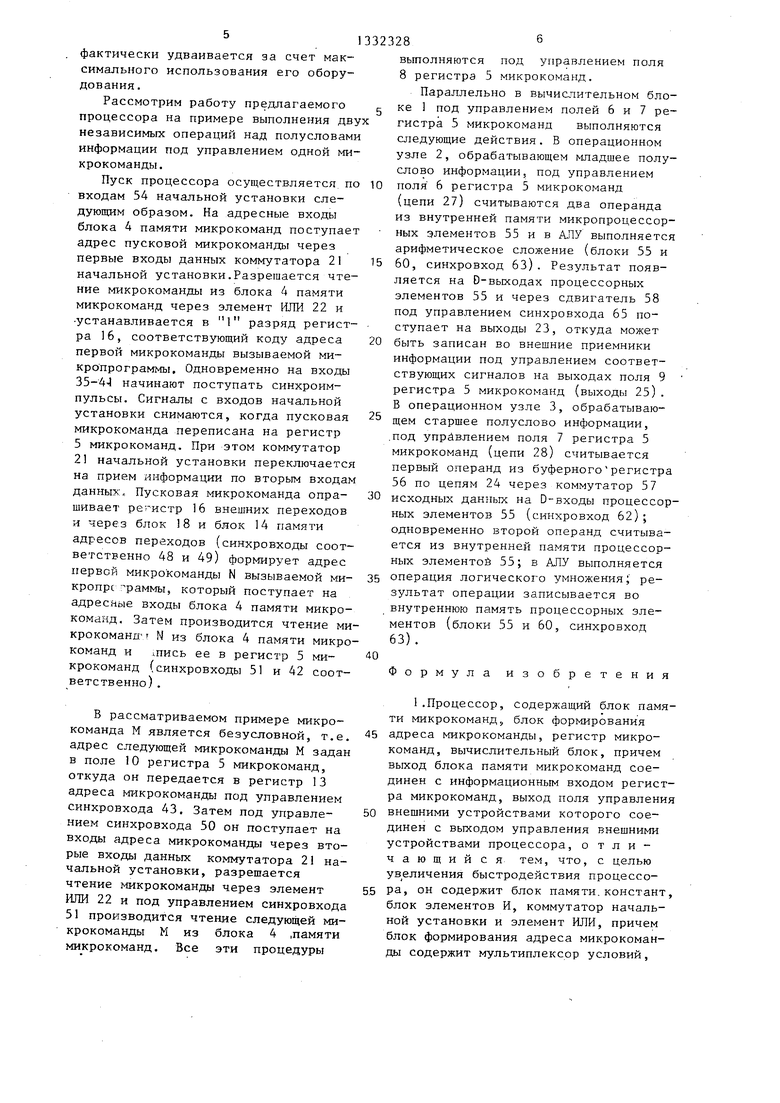

На фиг.1 показана структурная схема процессора; на фиг.2 - структурная схема вычислительного блока; на фиг.З - временные диаграммы обработки в процессоре микрокоманды.

Процессор содержит вычислительный блок 1, состоящий из двух одинаковых операционных узлов 2 и 3, блок 4 памяти микрокоманд, регистр 5 микрокоманд, содержащий два одинаковых поля 6 и 7 управления операционными узлами, поле 8 управления внутренни Процессор содержит также вхо чальной установки.

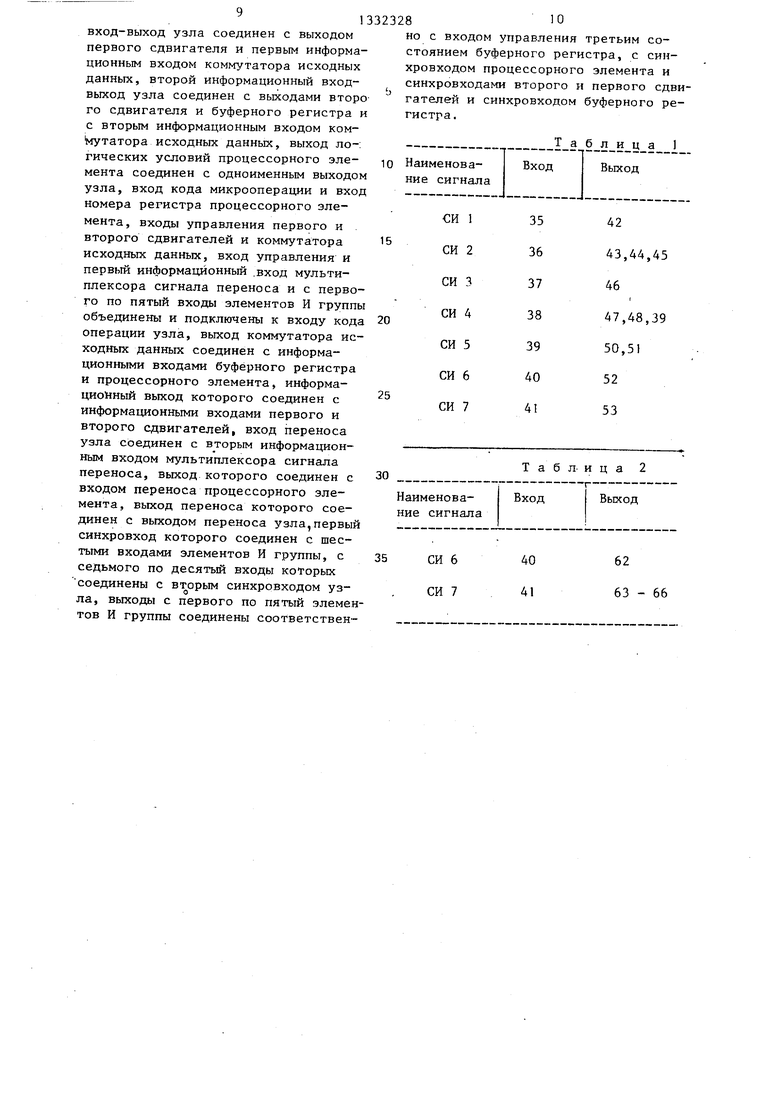

Соответствие между входны хроимпульсами и выходными си для первого блока элементов представлено в табл. 1.

Операционный узел 2 (З) с (фиг.2) процессорный элемент р ферный регистр 5Ь, коммутато ходных данных, первый и втор гатели 58 и 59, мультиплексор ла переноса, группу элементо

Группа элементов И 61 сод 15 первьй 40 и второй 41 входы 62, второй 63, третий 64, че 65, пятый 66 выходы.

Соответствие между входны ходными сигнгшами группы эле

ми блоками, поле 9 управления внешни-20 . 61 представлено в табл.2, ми устройствами и поле 10 адреса следующей микрокоманды, блок 11 памяти констант, блок 12 формирования адреса микрокоманды, в состав которого входит регистр 13 адреса микрокоманды, который может быть вьшолнен на базе любых синхронных триггеров О-типа и младший разряд которого должен иметь независимый , блок 14 памяти адресов переходов, регистр 15 адреса перехода, регистр }6 внешних переходов, регистр 17 маспроцессор работает следую разом.

Выполнение любой микроком . производится за одинаковый п 25 времени, называемый микроцик Обработка микрокоманд произв в конвейерном режиме, т.е. в одного микроцикла выполняютс дующие процедуры; реализация 30 щей микрокоманды N, находящ регистре 5 микрокоманд, в ис тельном блоке 1 под управлен лей 6 и 7 регистра микрокома формирование .адреса следующе

ки, блок 18 маскирования, мультиВыполнение любой микрокоманды . производится за одинаковый период 25 времени, называемый микроциклом. Обработка микрокоманд производится в конвейерном режиме, т.е. в течение одного микроцикла выполняются следующие процедуры; реализация теку- 30 щей микрокоманды N, находящейся на регистре 5 микрокоманд, в исполнительном блоке 1 под управлением полей 6 и 7 регистра микрокоманд; формирование .адреса следующей микро25 команды N и выборка микрокоманды М из блока 4 памяти микрокоманд по адресу, установленному на ее адрес- Ньпс водах блоком 12 формирования адреса микрокоманды, под управлением

плекС ор 19 условий, первый блок элементов И 20, коммутатор 21 начальной установки, элемент ИЛИ 22, информационный вход-выход 23, внутреннюю шину 24 данных, выходы 25 управления внещними устройствами регистра микрокоманд, вход 26 кода операции процес- 40 поля 8 регистра 5 микрокоманд. сора, выход 27 поля управления первым . Формирование адреса микрокоманды операционным узлом регистра микрокоманд, выход 28 поля управления вторым операционным узлом регистра микрокоманд, выход 29 флатов первого операционного узла, выход 30 фла;тов второго операционного узла, вход 31

45

М может выполняться четырьмя различными способами.

1.Если микрокоманда М безусловная, то ее адрес поступает без изменения из поля 10 адреса следующей микрокоманды регистра 5 микрокоманд в регистр 13 адреса микрокоманды. Оттуда в нужный момент времени он

и выход 32 переноса первого операционного узла, вход 33 и выход 34 переноса второго операционного узла.

Первый блок элементов И содержит первый 35, второй 36, третий 37, четвертый 38, пятый 39, щестой 40, седьмой 41 входы и первый 42, второй 43, третий 44, четвертый 45, пятый 46, шестой 47, седьмой 48, восьмой 49, девятый 50, десятый 51, одиннадцатый 52 и двенадцатый 53 выходы.

Процессор содержит также вход 54 начальной установки.

Соответствие между входными синхроимпульсами и выходными сигналами для первого блока элементов И 20 представлено в табл. 1.

Операционный узел 2 (З) содержит (фиг.2) процессорный элемент 55, бу- ферный регистр 5Ь, коммутатор 57 исходных данных, первый и второй сдви- гатели 58 и 59, мультиплексор 60 сигнала переноса, группу элементов И 61.

Группа элементов И 61 содержит первьй 40 и второй 41 входы и первый 62, второй 63, третий 64, четвертый 65, пятый 66 выходы.

Соответствие между входными и выходными сигнгшами группы элементов

. 61 представлено в табл.2,

процессор работает следующим образом.

Выполнение любой микрокоманды производится за одинаковый период времени, называемый микроциклом. Обработка микрокоманд производится в конвейерном режиме, т.е. в течение одного микроцикла выполняются следующие процедуры; реализация теку- щей микрокоманды N, находящейся на регистре 5 микрокоманд, в исполнительном блоке 1 под управлением полей 6 и 7 регистра микрокоманд; формирование .адреса следующей микрокоманды N и выборка микрокоманды М из блока 4 памяти микрокоманд по адресу, установленному на ее адрес- Ньпс водах блоком 12 формирования адреса микрокоманды, под управлением

поля 8 регистра 5 микрокоманд. . Формирование адреса микрокоманды

поля 8 регистра 5 микрокоманд. . Формирование адреса микрокоманды

М может выполняться четырьмя различными способами.

1.Если микрокоманда М безусловная, то ее адрес поступает без изменения из поля 10 адреса следующей микрокоманды регистра 5 микрокоманд в регистр 13 адреса микрокоманды. Оттуда в нужный момент времени он

задается на адресные входы блока 4 памяти микрокоманд и удерживается там в течение времени, необходимого для чтения микрокоманды.

2.Если адрес микрокоманды М опре- деляется по условию, выработанному

узлом 2 (З), то это условие поступает по цепям 29 или 30 через мультиплексор 19 условий на единичньй вход младшего разряда регистра 13 адреса

1

микрокоманд, в который предварительно бьт заслан код адреса из поля 10 регистра микрокоманд так же, как в п.I. В этом случае код адреса в поле 10 регистра микрокоманд содержит о в младшем разряде. Если условие выработалось, то младший разряд адреса в регистре 13 устанавливается в 1, если нет - то остается в О. Дальнейшие действия аналогичны п.1.

3.Если адрес микрокоманды М определяется по результатам вычислений микрокоманды L, предшествовавшей N,

в узлах 2 (З) то вычисленный код поступает в конце предьщушего микроцикла по цепям 23 и 24 на регистр 15 адреса перехода, а с выхода этого регистра в данном микроцикле поступает на адресные входы блока 14 памяти адресов переходов и удерживается там в .течение времени, необходимого для чтения адреса микрокоманды М, который поступает с выходов блока 14 памяти адресов переходов на адрес ные входы блока 4 памяти микрокоманд.

4.Если адрес микрокоманды М задается другими процессорами системы, например, код команды языка высокого уровня должен включить в данном процессоре выполнение определенной микропрограммы, то соответствующий код поступает по цепям 26 на регистр 16 внешних переходов, маскируется в блоке 18 с текущим кодом регистра 17 маски и, если блокировка для данного кода отсутствует, поступает на адресные входы блока 14 памяти адресов переходов. Дальнейшая процедура аналогична п.З.

В течение микроцикла выполнения текущей микрокоманды поле 9 управления внешними устройствами регистра 5 микрокоманд вьщает по цепям 25 все сигналы, необходимые при взаимодействии процессора с другими устройствами системы, например сигналы запросов на обращения к общей памяти системы и т.п.

Вычислительный блок 1, состоящий из двух одинаковых узлов 2 и 3, каждый из которых обрабатывает полуслово информации, работает следующим образом. Каждый узел содержит процессорный элемент 55, который может выполнять над полусловом информации ряд арифметических и логических операций. Источниками обрабатываемой

32328

информации могут служить внутренняя память микропроцессорных элементов

55,буферньшг регистр 56, блок 11 памяти констант, связанные с процессорным элементом по внутренней шине 24 данных через коммутатор 57 исходных данных, а также устройства системы, внешние по отношению к данному

Ю процессору, связанные с процессорным элементом 55 по внешней шине 23 данных через коммутатор 57 исходных данных, Приемниками информации могут служить внутренняя память процессор15 ного элемента 55, буферный регистр

56,регистр 15 адреса перехода через сдвигатель 58 по внешней шине 23 данных или через сдвигатель 59 по внутренней шине 24 данных, а также

20 устройства системы, внешние по отношению к данному процессору, через сдвигатель 58 по внешней шине 23 данных. При этом Сдвигат.ели 58 и 59 обеспечивают быструю передачу любых 25 комбинаций байтов по внутренней и внешней шинам данных. Поля 6 и 7 управления операционными узлами регистра 5 микрокоманд содержат все коды, необходимые для

30 управления работой операционных узлов, а именно: код элементарной операции набора процессорных элементов 55; код входного переноса Ро и код управления мультиплексором 60 сигна„ ла переноса; коды адресов двух источников информации; код адреса приемника информации; код управления сдвига- телями 58 и 59; код управления коммутатором 57 исходных данных; код

40 управления группой элементов И 61.

Исполнительный блок 1 может обрабатывать информацию в двух режимах: с полноразрядным словом и с полусловами. При обработке полноразрядного

45 слова поля 6 и 7 управления операционными блоками регистра 5 микрокоманд содержат одинаковую информацию, под управлением которой вьшолняется элементарная операция над всеми раз50 рядами информационного слова. Если по ходу выполнения микропрограммы требуется обработка независимых слов, разрядность которых не превьшзает полуслова, то узлы 2 и 3 выполняют неgg зависимые операции над полусловами под управлением соответственно полей 6 и 7, содержащих в данном случае разную информацию. При этом производительность исполнительного блока 1

фактически удваивается за счет максимального использования его оборудования.

Рассмотрим работу предлагаемого процессора на примере выполнения дву независимых операций над полусловами информации под управлением одной микрокоманды.

Пуск процессора осуществляется, по входам 54 начальной установки следующим образом. На адресные входы блока 4 памяти микрокоманд поступает адрес пусковой микрокоманды через первые входы данных коммутатора 21 начальной установки.Разрешается чтение микрокоманды из блока 4 памяти микрокоманд через элемент ИЛИ 22 и устанавливается в 1 разряд регистра 16, соответствующий коду адреса первой микрокоманды вызываемой микропрограммы. Одновременно на входы 35-4-J начинают поступать синхроимпульсы. Сигналы с входов начальной установки снимаются, когда пусковая микрокоманда переписана на регистр 5 микрокоманд. При этом коммутатор 21 начальной установки переключается на прием информации по вторым входам данных. Пусковая микрокоманда опрашивает регистр 16 внешних переходов и через блок 18 и блок 14 памяти адресов переходов (синхровходы соответственно 48 и 49) формирует адрес первой микрокоманды N вызываемой ми- кропрс -граммы, который поступает на адресные входы блока 4 памяти микрокоманд. Затем производится чтение ми крокоманд N из блока 4 памяти микрокоманд и ягась ее в регистр 5 микрокоманд (синхровходы 51 и 42 соответственно) .

В рассматриваемом примере микрокоманда М является безусловной, т.е. адрес следующей микрокомандь) М задан в поле 10 регистра 5 микрокоманд, откуда он передается в регистр 13 адреса микрокоманды под управлением синхровхода 43. Затем под управлением синхровхода 50 он поступает на входы адреса микрокоманды через вторые входы данных коммутатора 21 начальной установки, разрешается чтение микрокоманды через элемент ИЛИ 22 и под управлением синхровхода 51 производится чтение следующей микрокоманды М из блока 4 .памяти микрокоманд. Все эти процедуры

32328

выполняются под управлением поля 8 регистра 5 микрокоманд.

Параллельно в вычислительном блоg ке 1 под управлением полей 6 и 7 регистра 5 микрокоманд выполняются следующие действия. В операционном узле 2, обрабатывающем младшее полуслово информации 5 под управлением

10 поля 6 регистра 5 микрокоманд

(цепи 27) считываются два операнда из внутренней памяти микропроцессорных элементов 55 и в АЛУ выполняется арифметическое сложение (блоки 55 и

15 60, синхровход 63). Результат появляется на D-выходах процессорных элементов 55 и через сдвигатель 58 под управлением синхровхода 65 поступает на выходы 23, откуда может

20 быть записан во внешние приемники информации под управлением соответствующих сигналов на выходах поля 9 регистра 5 микрокоманд (выходы 25) . В операционном узле 3, обрабатываю щем старшее полуслово информации, .под упрйвлением поля 7 регистра 5 микрокоманд (цепи 28) считывается первый операнд из буферного регистра 56 по цепям 24 через коммутатор 57

30 исходных данных на D-входы процессорных элементов 55 (синхровход 62); одновременно второй операнд считывается из внутренней памяти процессорных элементой 55; в АЛУ выполняется

35 операция логического умножения; результат операции записывается во внутреннюю память процессорных элементов (блоки 55 и 60, синхровход 63).

5

0

5

Формула изобретения

1.Процессор, содержащий блок памяти микрокоманд, блок формирования адреса микрокоманды, регистр микрокоманд, вычислительный блок, причем выход блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, выход поля управления внешними устройствами которого соединен с выходом управления внешними устройствами процессора, отличающий с я тем, что, с целью ув еличения быстродействия процессора, он содержит блок памяти, констант, блок элементов И, коммутатор начальной установки и элемент ИЛИ, причем блок формирования адреса микрокоманды содержит мультиплексор условий,

7

регистр адреса микрокоманды, блок памяти адресов переходов, регистр адреса перехода, регистр внешних переходов, регистр маски, блок маскирования, а вычислительный блок содержит первый и второй операционные узлы, причем выходы первого и второго полей микроопераций соединены соответственно с входами кода операции первого и второго операционных узлов, первые информационные входы- выходы которых объединены и соединены с первым информационным входом регистра адреса перекода и с информационным входом-выходом процессора,, старший разряд информационного входа регистра внешних переходо-в, первый информационный вход и управляющий вход коммутатора начальной установки и первый вход элемента ИЛИ объединен и подключены к входу начальной установки процессора, вход кода команды процессора соединен с остальными разрядами информационного входа регистра внешних переходов, выход которого соединен с первым информационным входом блока маскирования, второ информационный вход которого соединен с выходом регистра маски, информационные входы регистра маски, адресные входы и вход управления чтением блока памяти констант, вход управления мультиплексора условий, вход управления чтением блока памяти адресов переходов,вход управления третьим состоянием регистра адреса перехода и с первого по двенадцатый входы блока элементов И объединены и подключены к выходам поля управления внутренними блоками регистра микрокоманд, выход поля адреса следующей микрокоманды, которого соединен с информационным входом регистра адреса микрокоманды, выход которого соединен с выходом блока памяти адресов переходов и с вторым информационным входом коммутатора начальной установки, выход которого соединен с входом адреса блока памяти микрокоманд, вход управления чтением которого соединен с выходом элемента ИЛИ, выход блока маскирования соединен с выходом регистра адреса переходов и с адресным входом блока памяти адресов переходов, вторые информационные входы-выходы первого и второго операционных узлов объединены и соединены с выходом блока памяти констант и

1

10

15

25

20332328о

вторым информационным входом регистра адресов переходов, выходы логических условий первого и второго операционных узлов соединены соответственно с первым и вторым информационными входами мультиплекс5ра условий, выход которого соединен с входом установки в I младшего разряда регистра адреса микрокоманды, первый синхровход процессора соединен с первыми синхровходами первого и второго операционных узлов и тринадцатым входом блока элементов И, второй синхровход процессора соединен с вторыми синхровходами первого и второго операционных узлов и с четырнадцатым входом блока элементов И, третий синхровход процессора соединен с пятнадцатым и шестнадцатым входами блока элементов И, четвертый синхровход процессора соединен с семнадцатого по девятнадцатый входы, а пятый синхровход процессора соединен с двадцатого по двадцать второй входы блока элементов И, шестой и седьмой синхровходы процессора соединены соответственно с двадцать третьим и двадцать четвертым входами блока элементов И, с первого по двенадцатый выходы которого соединены соответственно с синхровходами регистра микрокоманд, регистра адреса микрокоманды, регистра внешних переходов, регистра маски, мультиплексора условий, с входами управления третьим состоянием регистра адресов переходов, блока маскирования, блока памяти адресов переходов, регистра адреса микрокоманды, блока памяти микрокоманд, блока памяти констант, с син- хровходом рег истра адреса переходов, выход признака переноса второго операционного узла соединен с входом признака переноса второго операционного узла, выход признака переноса которого соединен с выходом признака переноса из старшего разряда слова процессора, вход признака переноса в младший разряд слова процессора соединен с входом признака переноса первого операционного узла.

2. Процессор по п.1, о т л и - чающийся тем, что содержит 55 процессорный элемент, группу элементов И, буферный регистр, мультиплексор сигнала переноса, коммутатор исходных данных, первый и второй сдви- гатели, причем первый информационный

30

35

40

45

50

вход-выход узла соединен с выходом первого сдвигателя и первым информационным входом коммутатора исходных данных, второй информационный вход- выход узла соединен с выходами второ го сдвигателя и буферного регистра и с вторым информационным входом ком- мутатора исходных данных, выход ло-: гических условий процессорного эле- мента соединен с одноименным выходом узла, вход кода микрооперации и вход номера регистра процессорного элемента, входы управления первого и второго сдвигателей и коммутатора исходных данных, вход управления и первый информационный .вход мультиплексора сигнала переноса и с первого по пятый входы элементов И группы объединены и подключены к входу кода операции узла, выход коммутатора исходных данных соединен с информационными входами буферного регистра и процессорного элемента, информа- циойный выход которого соединен с информационными входами первого и второго сдвигателей, вход переноса узла соединен с вторым информационным входом мультиплексора сигнала переноса, выход которого соединен с входом переноса процессорного элемента, выход переноса которого соединен с выходом переноса узла,первый синхровход которого соединен с шестыми входами элементов И группы, с седьмого по десятый входы которых соединены с вторым синхровходом узла, выходы с первого по пятый элементов И группы соединены соответствен

но с входом управления третьим состоянием буферного регистра, с синхровходом процессорного элемента и синхровходами второго и первого сдвигателей и синхровходом буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство выборки команд процессора | 1986 |

|

SU1410028A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Устройство микропрограммного управления | 1983 |

|

SU1151961A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих вычислительных систем. Цель изобретения -повышение быстродействия процессора за счет совмещения во времени выполнения независимых операций над полусловами. Процессор содержит блок 4 памяти микрокоманд, регистр 5 микрокоманд, вычислительный блок 1, блок 11 памяти констант, блок 20 элементов И, коммутатор 21 начальной установки, элемент ИЛИ 22, мультиплексор 19 условий, регистр 13 адреса микрокоманды, блок 14 памяти адресов переходов, двухкортовый 15 адреса перехода, регистр 16 внешних переходов, регистр 17 маски и блок 18 маскирования. 1 з.п. ф-лы, 3 ил., 2 табл. С S (Л j«

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Брик Дж.Мик.Дж | |||

| Проектирование микропроцессорных устройств с раз- рядно-модульной организацией.-М.: Мир, 1984, кн.2, с.361-392. | |||

Авторы

Даты

1987-08-23—Публикация

1986-04-07—Подача