f2 1

1Н 12-5П- П-Н

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Делитель частоты следования импульсов | 1987 |

|

SU1431070A2 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

Изобретение относится к импульсной технике, может быть использовано в цифровых синтезаторах частот, в цифровых фазометрах, в цифровых системах автоподстройки частоты. Цель изобретения - расширение диапазона коэффициентов деления при одновременном поньшении в два раза быстродействия - достигается использованием младших каскадов с управляемым козффициентом деления 2/3 счетчика 4 импульсов, дешифратора 8, К-тригге- ров 1,2 и 9, при этом управляющий код поступает на шину 12, входная частота - на шину II. 2 ил.

11

Од СО

9иг.1

Изобретение относится к импульсной технике, в частности к устройствам автоматики, телемеханики, вычислительной и измерительной техники, и может быть использовано в синтезаторах частот, в цифровьпс фазометрах, в измерительной аппаратуре и цифровых системах автоподстройки частоты.

Цель изобретения - расширение ся по спаду импульсов, поступающих

пазона коэффициентов деления при од новременном повышении в два раза быстродействия устройства.

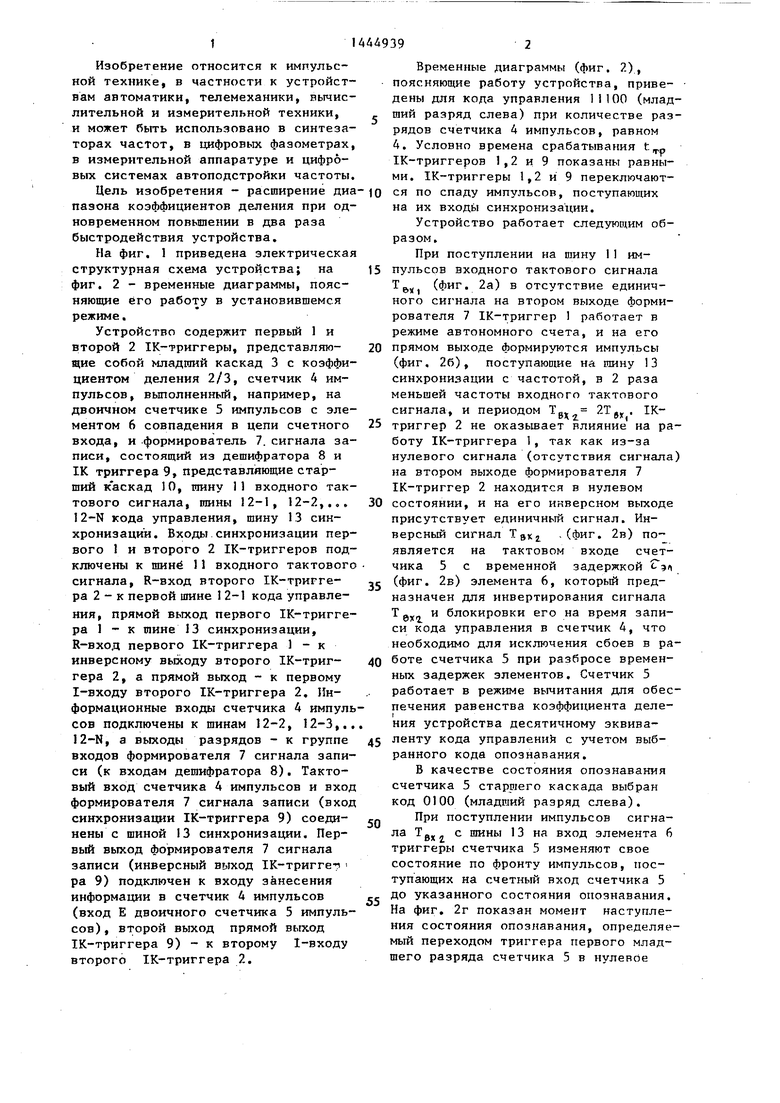

На фиг. 1 приведена злектрическая структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу в установившемся режиме.

Устройство содержит первый 1 и второй 2 1К-триггеры, представляющие собой младший каскад 3 с коэффициентом деления 2/3, счетчик 4 импульсов, вьтолненный, например, на двоичном счетчике 5 импульсов с элементом 6 совпадения в цепи счетного входа, и формирователь 7. сигнала записи, состоящий из дешифратора 8 и IK триггера 9, представляющие старший каскад 10, шину 11 входного тактового сигнала, шины 12-1, 12-2,.,. 12-N кода управления, шину 13 синхронизации. Входы синхронизации первого 1 и второго 2 1К-триггеров подключены к шине 11 входного тактового сигнала, R-вход второго 1К-тригге- ра 2 - к первой шине 1 2-1 кода управления, прямой выход первого 1К-тригге- ра 1 - к шине 13 синхронизации, R-вход первого 1К-триггера 1 - к инверсному выходу второго 1К-триг- гера 2, а прямой выход - к первому 1-входу второго 1К-триггера 2. Информационные входы счетчика 4 импульсов подключены к шинам 12-2, 12-3,... 12-N, а выходы разрядов - к группе входов формирователя 7 сигнала записи (к входам дешифратора 8). Тактовый вход счетчика 4 импульсов и вход формирователя 7 сигнала записи (вход синхронизации 1К-триггера 9) соединены с шиной 13 синхронизации. Первый выход формирователя 7 сигнала записи (инверсный выход ТК-тригге-п ра 9) подключен к входу занесения информации в счетчик 4 импульсов (вход Е двоичного счетчика 5 импульсов), второй выход прямой выход 1К-триггера 9) - к второму 1-входу второго 1К-триггера 2.

50

55

на их входь синхронизации.

Устройство работает следующим об разом.

При поступлении на шину 11 им15 пульсов входного тактового сигнала , (фиг. 2а) в отсутствие единичного сигнала на втором выходе форми рователя 7 1К-триггер 1 работает в режиме автономного счета, и на его

20 прямом выходе формируются импульсы (фиг. 26), поступаюпще на шину 13 синхронизации с частотой, в 2 раза меньшей частоты входного тактового сигнала, и периодом Т 2Tj, IK25 триггер 2 не оказьшает влияние на р боту 1К-триггера 1, так как из-за нулевого сигнала (отсутствия сигнал на втором выходе формирователя 7 1К-триггер 2 находится в нулевом

30 состоянии, и на его инверсном выход присутствует единичный сигнал. Инверсный сигнал Т9X2. .(фиг. 2в) появляется на тактовом входе счет чика 5 с временной задержкой

эс (фиг. 2в) элемента 6, который предназначен для инвертирования сигнала Т „„ и блокировки его на время запи си кода управления в счетчик 4, что необходимо для исключения сбоев в р

40 боте счетчика 5 при разбросе времен ных задержек элементов. Счетчик 5 работает в режиме вычитания для обе печения равенства коэффициента деле I ния устройства десятичному эквивад5 ленту кода управлени) с учетом выбранного кода опознавания.

В качестве состояния опознавания счетчика 5 старшего каскада выбран код 0100 (младший разряд слева).

При поступлении импульсов сигна

ла Tgj( с шины 13 на вход элемента триггеры счетчика 5 изменяют свое состояние по фронту импульсов, поступающих на счетный вход счетчика 5 до указанного состояния опознавания На фиг, 2г показан момент наступле ния состояния опознавания, определя мый переходом триггера первого млад шего разряда счетчика 5 в нулевое

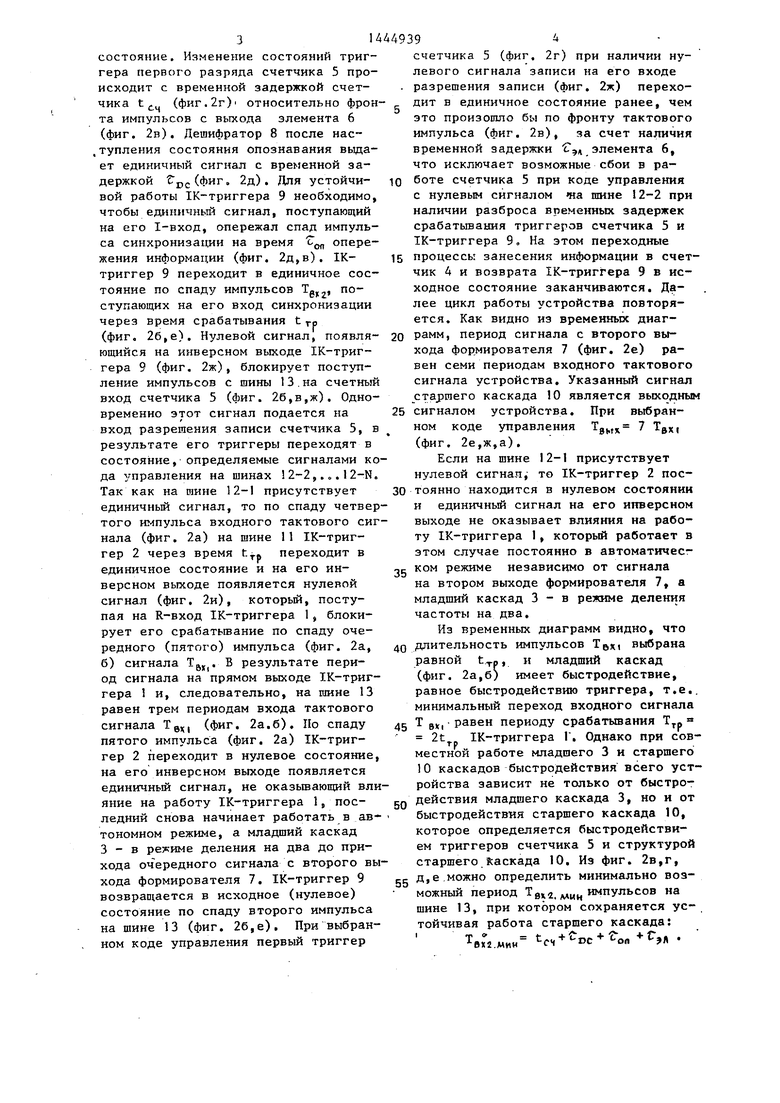

Временные диаграммы (фиг, 2), поясняющие работу устройства, приве- дены для кода управления 11100 (младший разряд слева) при количестве разрядов счетчика 4 импульсов, равном 4. Условно времена срабатывания 1К-триггеров 1,2 и 9 показаны равными. 1К-триггеры 1,2 и 9 переключают0

5

на их входь синхронизации.

Устройство работает следующим образом.

При поступлении на шину 11 им5 пульсов входного тактового сигнала , (фиг. 2а) в отсутствие единичного сигнала на втором выходе формирователя 7 1К-триггер 1 работает в режиме автономного счета, и на его

0 прямом выходе формируются импульсы (фиг. 26), поступаюпще на шину 13 синхронизации с частотой, в 2 раза меньшей частоты входного тактового сигнала, и периодом Т 2Tj, IK5 триггер 2 не оказьшает влияние на работу 1К-триггера 1, так как из-за нулевого сигнала (отсутствия сигнала) на втором выходе формирователя 7 1К-триггер 2 находится в нулевом

0 состоянии, и на его инверсном выходе присутствует единичный сигнал. Инверсный сигнал Т9X2. .(фиг. 2в) появляется на тактовом входе счетчика 5 с временной задержкой

с (фиг. 2в) элемента 6, который предназначен для инвертирования сигнала Т „„ и блокировки его на время записи кода управления в счетчик 4, что необходимо для исключения сбоев в ра0 боте счетчика 5 при разбросе временных задержек элементов. Счетчик 5 работает в режиме вычитания для обеспечения равенства коэффициента деле- I ния устройства десятичному эквива5 ленту кода управлени) с учетом выбранного кода опознавания.

В качестве состояния опознавания счетчика 5 старшего каскада выбран код 0100 (младший разряд слева).

При поступлении импульсов сигнала Tgj( с шины 13 на вход элемента 6 триггеры счетчика 5 изменяют свое состояние по фронту импульсов, поступающих на счетный вход счетчика 5 до указанного состояния опознавания. На фиг, 2г показан момент наступления состояния опознавания, определяемый переходом триггера первого младшего разряда счетчика 5 в нулевое

состояние. Изменение состояний триггера первого разряда счетчика 5 происходит с временной задержкой счетчика t (фиг.2г) относительно фронта импульсов с выхода элемента 6 (фиг. 2в). Дешифратор 8 после нас- .тупления состояния опознавания вьща- ет единичный сигнал с временной задержкой Гр2(фиг. 2д). Для устойчивой работы 1К-триггера 9 необходимо, чтобы единичньш сигнал, поступающий на его 1-вход, апережал спад импульса синхронизации на время сГ опережения информации (фиг, 2д,в). IK- триггер 9 переходит в единичное состояние по спаду импульсов Tg,, поступающих на его вход синхронизации через время срабатывания t р (фиг. 2б,е). Нулевой сигнал, появляющийся на инверсном выходе 1К-триг- гера 9 (фиг. 2ж), блокирует поступление импульсов с 1 3 . на счетный вход счетчика 5 (фиг. 26,в,ж). Одновременно этот сигнал подается на вход разрешения записи счетчика 5, в результате его триггеры переходят в состояние,определяемые сигналами кода управления на шинах 2-2,.„.12-N. Так как на тине 12-1 присутствует единичный сигнал, то по спаду четвертого импульса входного тактового сигнала (фиг. 2а) на шине П 1К-триг- гер 2 через время t. переходит в единичное состояние и на его инверсном выходе появляется нулевой сигнал (фиг. 2и), который, поступая на R-вход 1К-триггера 1, блокирует его срабатывание по спаду очередного (пятого) импульса (фиг. 2а,

б) сигнала Т. В результате период сигнала на прямом выходе 1К-триг- гера 1 и, следовательно, на шине 13 равен трем периодам входа тактового сигнала Тц, (фиг. 2а.б), По спаду

пятого импульса (фиг. 2а) 1К-триг- гер 2 переходит в нулевое состояние, на его инверсном выходе появляется единичный сигнал, не оказьшающий влияние на работу 1К-триггера 1, пос- ледний снова начинает работать в ав- тономном режиме, а младший каскад 3 - в режиме деления на два до прихода оч ередного сигнала с второго выхода формирователя 7, 1К-триггер 9 возвращается в исходное (нулевое) состояние по спаду второго импульса на шине 13 (фиг, 2б,е), При выбранном коде управления первый триггер

счетчика 5 (фиг. 2г) при наличии нулевого сигнала записи на его входе разрешения записи (фиг. 2ж) переходит в единичное состояние ранее, чем это произошло бы по фронту тактового импульса (фиг. 2в), за счет наличия временной задержки элемента 6, что исключает возможные сбои в ра-

боте счетчика 5 при коде управления с нулевым сигналом на шине 12-2 при наличии разброса временных задержек срабатывания триггеров счетчика 5 и 1К-триггера 9. На этом переходные

процессы занесения информации в счетчик 4 и возврата 1К-триггера 9 в исходное состояние заканчиваются. Далее цикл работы устройства повторяется. Как видно из временньпс диаграмм, период сигнала с второго выхода формирователя 7 (фиг, 2е) равен семи периодам входного тактового сигнала устройства. Указанный сигнал старшего каскада 10 является выходным

сигналом устройства. При выбран0

ВМЯ

7 Т

BXI

g

ном коде управления (фиг. 2е,ж,а).

Если на шине 12-1 присутствует нулевой сигнал, то 1К-триггер 2 постоянно находится в нулевом состоянии и единичный сигнал на его инверсном выходе не оказывает влияния на работу 1К-триггера 1, который работает в этом случае постоянно в автоматичесс ком режиме независимо от сигнала на втором выходе формирователя 7, а младший каскад 3 - в режиме деления частоты на два.

Из временных диаграмм видно, что

0 длительность импульсов выбрана равной Ьтр, и младший каскад (фиг. 2а,б) имеет быстродействие, равное быстродействию триггера, т,е,. минимальный переход входного сигнала

5 Bxi равен периоду срабатывания Т. 2t 1К-триггера Г, Однако при совместной работе младшего 3 и старшего 10 каскадов быстродействия всего устройства зависит не только от быстродействия младшего каскада 3, но и от быстродействия старшего каскада 10, которое определяется быстродействием триггеров счетчика 5 и структурой старшего Каскада 10. Из фиг, 2в,г,

е д,е,можно определить минимально возможный период Tgj2. мин шине 13, при котором сохраняется устойчивая работа старшего каскада:

Тв,%.мии tcH-b --DC

г

л

На элементы серии ТТЛ можно ориентировочно принять, что trt.,;

ЭХ S

Зе, 21. t 2€,. Тогда Тв,,,«„„ 10Г,„ Лтр 2,5 Следовательно, быстродействие стар- шего каскада 10 в 2,5 раза менее быстродействия отдельного триггера. Минимальный период входного тактовог сигнала всего устройства Т, , +77, 5,, 1,25 Tvp (фиг. 2а,6,в), следовательно, fg, 0,5 . мин быстродействие всего устройства вьше быстродействия старшего каскада (прототипа) в два раза.

Коэффициент деления предлагаемого устройства К m-N М, где m 2 - коэффициент деления младшего каскада в автономном режиме, N - коэффициент деления старшего каскада в управляемом режиме, М - приращение коэффициента деления младшего каскада, равное О или 1 в зависимости от сигнала младшего (первого) разряда кода уп равления.

Коэффициент деления старшего каскада 10 изменяется от 2 до-2 +1 где п - число триггеров счетчика 5 старшего каскада 10. Тогда диапазон коэффициентов деления предлагаемого устройства изменяется от 4 до К

MCJIItC

- + 3, т.е. UK

I П(

Таким образом, диапазон коэффициентов деления прототипа, представленного в виде старшего каскада, &К 2, а диапазон коэффициентов деления предлагаемого устройства йК , т.е. вдвое больше. При этом быстродействие предлагаемого устройo s

0 5

о

5

Q

ства в два раза выше быстродействия прототипа, В обР1ем случае быстродействие данного устройства определяется меньшей из неличин 2f . г и f ,., где f ддакс ст быстродействие старшего каскада 10, а fij-p, быстродействие 1К-триггера 1 младшего каскада 3.

Формула изобретения

Делите11ь частоты с .переменным коэффициентом деления, содержащий счетчик импульсов с установкой начального кода, информационные входы которого подключены к соответствующим, кроме первой, шинам кода управления, и формирователь сигнала записи, группа входов которого соединена с выходами разрядов счетчика импульсов, первый выход - с входом занесения информации счетчика импульсов, тактовый вход которого подключен к входу формирователя сигнала записи и к шине синхронизации, отличающийся тем, что, с целью расширения диапазона коэффициентов деления при одновременном повышении быстродействия, в него введены первый и второй 1К-триггеры, входы синхронизации которых соединены с. шиной входного тактового сигнала, R-вход первого 1К-триггера подключен к инверсному выходу второго 1К-триг- гера, первый 1-вход которого соединен с прямым выходом первого 1К-триг- гера и шиной синхронизации, второй 1-вход - с вторым выходом формирователя сигнала записи, а R-вход - с первой шиной кода управления.

.

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1261108A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-03-27—Подача