с ел

со

ел

со

Изобретение относится к импульсной технике и может быть использовано в измерительной аппаратуре, в цифровых системах автоподстройки частоты, в синтезаторах частоты.

Цель изобретения - повышение надежности при одновременном расширении диапазона значений коэффициентов деления и сохранении высокого быстродействия устройства.

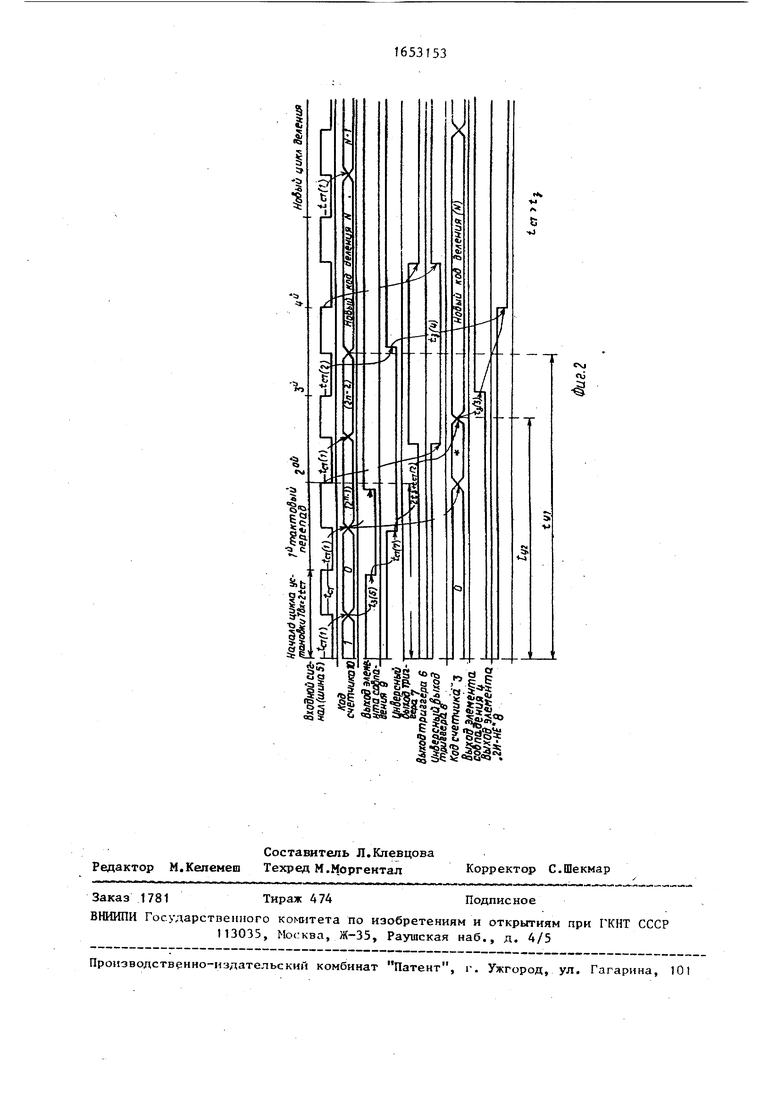

На фиг о 1 приведена структурная электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие его работуо

Делитель частоты с переменным коэффициентом деления содержит N-раз- рядный пересчетный блок 1, где N- число разрядов шины 2 управления, состоящий из первого счетчика 3 импульсов, инверсные выходы Njt,- N разрядов которого соединены с соответствующими входами первого элемента 4 совпадения, входящего в пересчетный блок 1, где п - номер старшего разряда, счетный вход пере- счетного блока 1 соединен с входной шиной 5 и с С-входами первого и второго lK-трнггеров b и 7, a N,- М„ разрядов шины 1 управления соединены с соответствующими информационными входами пересчетного блока 1, выход переноса которого соединен с R-входом первого 1К-триггера 6, инверсный вы- ход которого соединен с первым входом разрешения переноса пересчетного блока 1s а прямой - с первым входом разрешения записи пересчетного блока 1, причем пересчетный блок 1 снабжен вторым входом разрешения записи и вторым входом разрешения переноса и в него введены второй элемент совпаде- ния (дешифратор) 2И-НЕ 8 и третий элемент совпадения 9 (дешифратор),; причем выход переноЈа пересчетного блока 1 соединен с S-входом второго 1К-триггера 7, прямой выход которого соединен с его же I-входом и 1-вхо- дом первого JK-трнггера 6, К-вход второго IK-триггера 7 соединен с прямым выходом первого 1К-триггера 7, К-вход которого соединен с инверсным выходом второго 1К-триггера 7 и вторыми входами разрешения записи и разрешения переноса пересчетного блока 1, причем в пересчетный блок 1 введен второй счетчик 10 импульсов, выполненный в виде счетчика младших разрядов, счетный вход которого соединен со счетным входом пересчетного блока 1, N - N информационных входов - с соответствующими разрядами

шины 2 управления, а инверсный выход 1-го разряда - со счетным входом первого счетчика 3 импульсов, вход разрешения записи - с вторым входом разрешения записи пересчетного блока 1,

инверсный выход первого элемента 4 совпадения соединен с первым входом второго элемента 8 совпадения, второй вход которого соединен с вторым входом разрешения переноса пересчетного

5 блока 1, а инверсный выход - с первым входом третьего элемента 9 совпадения второй вход которого соединен с первым входом разрешения переноса пересчетного блока 1, третий 0 с прямым выходом k-ro разряда второго счетчика 10 импульсов, инверсные выходы остальных i-1 разрядов которого соединены с соответствующими с четвертого noCi+2)-u входами третьего

5 элемента 9 совпадения, инверсный выход которого является выходом переноса пересчетного блока 1.

Синхронный счетчик 10 выполнен по схеме с параллельным переносом и

0 асинхронной загрузкой информации,

что обеспечивает минимальные задержки распространения сигналов: от тактового входа счетчика до выходов разрядов в цепях организации переносов: от входа асинхронной установки до установочных входов триггеров.

Подобная реализация счетчика 10 позволяет работать на максимальной входной частоте и при этом использовать прямые и инверсные выходы любых разрядов счетчика как равноценные

Установка ДПКД в исходное состояние происходит за четыре периода , входных тактовых импульсов, при этом удается распределить операции по тактам таким образом, что задержка распространения сигнала при выполнении операций одного такта, определяющая минимальный период входных тактовых импульсов Тд,и(„, не превышает суммы задержек переключения триггера и простого логического элемента, т.е.

тминг.- tcr + fc3 2tcr где t - задержка переключения триг0

0

5

ст

гера счетчика;

t, - усредненная задержка

простого логического элемента.

Таким образом, максимальная входная частота предложенного делителя . макс л примерно равна максимальной частоте для делителей с фиксированным коэффициентом деления

/ Fex, максЈ 2tcr как для делителей с фиксированным коэффициентом деления.

Максимальная входная частота By. ллаис определяется быстродействием счетчика, которое, в свою очередь, определяется быстродействием счетного триггера первого разряда счетчика, т.е.

1

ex. макс

где t

, + t cr

or

fi задержка переключения триггера счетчика; длительность сигнала записи

ч

информации в триггер; Р. - предельная рабочая частота

переключения триггера, Учитывая, что Ј i t T, получим, что Fw макс для делителей с фикси- рованным коэффициентом деления опредляется выражением

F1- 6JT. 2t ст

Для получения коэффициента делени равного заданному с шины управления, установку ДПКД необходимо начинать за четыре периода тактовых импульсов до окончания цикла деления, поэтому с входами третьего элемента 9 совпадения соединены прямой выход третьего разряда и инверсные выходы остальных разрядов счетчика 10„

В предложенном устройстве диапазо коэффициентов деления определяется выражением 4 Ј Kg Ј- 2 + 4, где минимальный коэффициент деления определяется управляющей схемой (триггеры 6, 7, а аддитивная составляющая коэффициента деления может быть изменена выбором соответствующей комбинации подключения прямых и инверсных выходов синхронного счетчика 10 к дешифратору 9). В частном случае, эта составляющая может быть сделана равн нулю, т„е, заданный с шины 2 управления и реальный коэффициенты деления будут равны. Коэффициент деления предложенного устройства определяется выражением:

+ 4-m,

где m - величина, значение которой определяется комбинацией подключения

5

0

5

прямых и инверсных выходов разрядов синхронного счетчика 10 к элементу 9 совпадения дешифратора и выбирается пользователем для получения требуемого соотношения между Кд и N.

Значение m определяется выражением

4- m 2 ;

1

где 1 - количество разрядов синхронного счетчика 10; 1, если прямой выход К-го разряда счетчика 10 подключен к элементу 9 совпадения дешифратора;О, если подключен инверсный

ВЫХОД о

Для обеспечения работоспособности устройства на максимальной входной частоте величина m должна удовлетворять неравенству

m L 2 - 1,

где i - количество разрядов синхронного счетчика 10.

Например соотношение К а N получается при m 4 „ Для получения тре-- буемого га коэффициенты а должны быть равны:

если К

30

5

0

5

0

5

Тогда m a( 1 2 4

Физически это реализуется подключением к элементу 9 совпадения прямого выхода третьего разряда счетчика 1 и инверсных выходов всех остальных разрядов о

Устройство работает следующим образомо

В исходном состоянии в счетчиках 3 и 10 записан код коэффициента деления N, соответствующий состоянию шины 2 управления, 1К-триггеры 6 и 7 обнулены, на выходе элемента 9 совпадения уровень 1.

С шины 5 поступают тактовые импульсы и уменьшают содержимое счетчиков о Когда содержимое счетчика 3 санет равно нулю, на всех его инверсных выходах появится уровень I, Сигналы инверсных выходов объединяются в элементе 4 совпадения, на выходе которого появляется уровень О. Сигнал с выхода элемента 4 инвертируется элементом 2И-НЕ 8 и поступает на один из входов элемента 9 совпадения и подготавливает его к срабатыванию. После этого изменяется только состояние синхронного счетчика 10.

После прихода (N - 4)-го импульса, где N - требуемый коэффициент деления ня всех выходах счетчика 10, подключенных к входам элемента 9 устано- вятся уровни 1. На инверсном выходе элемента 9 появится уровень О, После прихода (N - 3)-го импульса состояние счетчика изменяется и на выходе элемента 9 снова устанавлива- ется уровень 1. Таким образом, на выходе элемента 9 фррмируется отрицательный импульс с длительностью, равной периоду тактовых импульсов. Этот импульс устанавливает в триггер 7 и удерживает сброшенным триггер 6„ Задержка фронтов этого импульса относительно такторых перепадов входных импульсов меньше Тмицй

Уровень 0 с инверсного выхода

триггера 7 поступает на инверсный вход асинхронной установки счетчика

3,производя его установку, и на вход элемента 2И-НЕ 8, поддерживая

на его выходе уровень 1 независи- мо от состояния на выходе элемента

4,что предотвращает укорочение им- пульса ка выходе элемента 9 при низкой частоте тактовых импульсов на шине 5„ (N - 2)-ft импучьс устанавли- вает триггер b и не изменяет состояния триггера 7.

Уровень О с инверсного выхода триггера 6 запрещает работу элемента 9 совпадения до окончания процесса установки ДПКД в исходное состояние, что предотвращает образование паразитных импульсов на выходе элемента 9 при работе на максимальной частоте и определенных коэффициентах деления. А уровень 1 с прямого входа триггера 6 поступает на вход асинхронной установки счетчика 10, производя его установку, и на К-вход триггера 7, разрешая его сброс (N - 1)-м такто- вым импульсом,(N - 1)-й импульс сбрасывает триггер 7 и не изменяет состояния триггера 6, N-н импульс сбрасывает триггер 6, установка ДПКД закончена. ДПКД готов к новому циклу деления„

Заметим, что выполнение дешифратора многоступенчатым не ухудшает быстродействия устройствас

При рассмотрении влияния элементов первой ступени дешифратора (элемент совпадении 4 и элемент 2И-НЕ 8) на быстродействие устройства анализируют процесс установки и выделяют моменты,

г Q 5

0

5

0

Q

5

0

определяющие быстродействие устройства.

Все операции по установке ДПКД можно разделить на три этапа: переход от деления к установке; установка счетчиков; переход от установки к делению.

Для примера рассмотрим вариант, когда к элементу 9 совпадения дешифратора подключены инверсные выходы всех разрядов счетчика 10.

Анализ перехода устройства от процесса деления к установке в исходное состояние.

Счетчики 10 и 3 включены последовательно и работают в режиме вычитания „ Содержимое синхронного счетчика 10 уменьшается на единицу после каждого отрицательного перепада на тактовом входе 5 устройства, а содержимое счетчика 3 уменьшается на единицу после отрицательного перепада напряжения на инверсном выходе триггера последнего разряда счетчика 10. Этот перепад формируется при переходе синхронного счетчика 10,из нулевого сос- тяния в состояние 2 - 1, где i - разрядность счетчика 10. Приходит отрицательный тактовый перепад на вход 5 устройства, счетчик 10 устанавливается в состояние 2 - 1, а счетчик 3 обнуляется о Когда начинает работать первая ступень дешифратора, но до начала установки ДПКД в исходное состояние, (когда счетчик 10 обнулится) еще 2 - 1 периодов тактовой частоты, задержка дешифрации t. состояния счетчика 3 относительно тактового перепада определяется выражением

t| t (1) -i- t (2) + ) + + 4(4),3

где tCT(1) - задержка переключения последнего триггера счетчика 10; tCT(2) - задержка переключения

триггера счетчика 3; t (3) и t,(4) - задержки распрост- ранения элемента 4

совпадения и элемента 2И-НЕ 8 соответственно. (t} t tCT).

Таким образом, t д i и при разрядности синхронного счетчика H)i 1 сигнал от первой ступени дешифратора к моменту, когда счетчик 10 обнулится, будет уже на входе элемента 9 совпадения м никаким образом не ограничит быстродействие

при переходе ДПКД от режима деления к режиму установки. Далее счетчик 1U обнуляется и начинается собственно цикл установки ДПКД. Элемент 9 совпадения регистрирует наличие на всех своих входах уровней 1 и на его выходе устанавливается уровень О (активный)„ Этот сигнал поступает на S-вход триггера 7 и устанавливает его и на R-вход триггера 6, удерживая его сброшенным.

Сигнал низкого уровня с инверсного выхода триггера 7 поступает на вход асинхронной установки счетчика на элемент 2И-НЕ 8. Начинается процесс установки счетчика 3. Первый тактовый перепад цикла установки ДПКД переключает счетчик 10 из нулевого состояния в состояние 2 - 1 и не изменяет состояния триггеров.

На выходе элемента совпадения устанавливается уровень 1 т.е. сигна на S-входе триггера 7 и R-входе триггера 6 становится пассивным и эти триггеры теперь могут переключаться тактовыми импульсами, приходящими на их С-входЫо

Быстродействие ДПКД на этапе перехода от деления к установке определяется задержками переключения триггера счетчика 10 и«элемента 9 совпадения. Так как tcr(1) + t . : TBX 2tCT то сигнал на выходе элемента 9 совпадения станет пассивным до прихода второго тактового перепада цикла установки, что и обеспечивает нормалную работу Д11КД на максимальной тактовой частоте о Второй тактовый перепад цикла установки не изменяет состояния триггера 7 и устанавливает триггер 6о Сигнал с выхода триггера 6 поступает на вход асинхронной установки счетчика 10, а сигнал О с инверсного выхода.блокирует элемент 8 совпадения. Начинается установка счетчика 10. Переход от деления к установке закончен.

Таким образом, установка счетчика 3 начинается раньше, чем счетчика 10. Определим задержку tuj, установки счетчика 3 в исходное состояние относительно начала цикла установки

Ч + М9 + сст(7) + + 2tm+tCT(3) 3(tcr + t), где tCT(1) - задержка переключения триггера счетчика 10;

t-(9) - задержка переключения

элемента 9 совпадения; t (7) - задержка переключении триггера 7;

2t,(3) - задержка распространения сигнала установки в счетчике 3 (от входа асинхронной установки до ус- тановочных S- и R-входов

триггеров счетчика; если разрядность счетчика 3 невелика, то эта задержка может быть уменьшена в 2 раза; tcr(3) - задержка переключения

триггера счетчика 3, т.е„ Т и-, L 3T о и к моменту прихода третьего тактового перепада цикла установки ДПКД на входах элемента 7 0 совпадения уже находится исходная

комбинация сигналов высокого и низкого уровней с выходов счетчика 3, т.е. установка счетчика 3 закончена. Определим задержку установки 5 счетчика 10 tu относительно начала цикла установки

tu, 2Т ex+ tCT(6) + t,(1) +

ч- te; (о зтвх + tr

где t CT(6) - задержка переключения 0триггера 6;

t(O задержка распростране- ния сигнала установки

в счетчике 10; t (1) - задержка переключения

триггеров счетчика 10; - задержка начала установки счетчика 10 относительно начала цикла установки,

0 Т„е. на входах элемента 9 совпадения исходная информация от счетчика 10 установится после прихода третьего тактового перепада цикла установки.

5 Приходит третий тактовый перепад. Он не изменяет состояние триггера 6 и обнуляет триггер 7. Пока переключается триггер 7, срабатывает элемент 4 совпадения. Поэтому на входах С элемента 2И-НЕ появляется уровень 1 с выхода элемента 4 совпадения, а затем - уровень 1 с инверсного выхода триггера 7. Через ty(8) на выходе элемента 2И-НЕ 8 появляется 5 сигнал несовпадения первой ступени дешифратора низкого уровня. Таким образом, до прихода четвертого последнего тактового перепада цикла установки все процессы, связанные с

5

2Т

ВХ

установкой счетчика 3 и работой первой ступени дешифратора, закончены. Следовательно, влияние первой ступени дешифратора на быстродействие ДПКД при переходе от установки к делению также отсутствует

Приходит четвертый тактовый перепад, обнуляет триггер 6 и оставляет обнуленным, триггер 7, т„е, ДПКД установлен D исходное состояние. Следующий тактовый перепад является первым тактовым перепадом нового цикла деления.

Таким образом, выполнение дешифратора многоступенчатым (на основе эле- ментов 4, 8 и 9 совпадения) не ухудшает быстродействия предложенного устройства и позволяет устройству рабо- тать с входной частотой

1

8, макс 2t

ст

Формула и з о б р е т е н и я

Делитель частоты с переменным коэффициентом деления, содержащий N разрядный пересчетный блок, N - чис- ло разрядов управления, соединенных с соответствующими информационными входами пересчетного блока, который состоит из первого счетчика импульсов, инверсные выходы Njr, - N раз рядов которого соединены с соответствующими входами первого элемента совпадения входящего в лересчетный блок, где п - номер старшего разряда, входящего в пересчетный блок, счетный вход пересчетного блока соединен с входной шиной и с С-входами первого н второго IK-триггеров, а N it N tl РаэРяАов пересчетного блока соединены с соответствующими информационными входами первого счетчика импульсов, выход переноса которого соединен с R-входом первого IK-триггера, инверсный выход которого соединен с первым входом разреше- ния переноса пересчетного блока, а прямой - с первым входом записи пересчетного блока, отличающийся тем, что, с целью повышения надежности при одновременном расширении диапазона значений коэффициентов деления и сохранении высокого быстродействия, пересчет-

о

5

0

0 Q -п

5

ный блок снабжен вторым входом разрешения записи и вторым входом разрешения переноса и в него введены второй и третий элементы совпадения, причем .выход переноса пересчетного блока соединен с S- -входом второго IK-триггера, прямой выход которого соединен с его же I-пходом и 1-вхо дом первого iK-триггера, К-вход второго IK-триггера соединен с прямым выходом первого IK-триггера, К-вход которого соединен с инверсным выходом второго IK-триггера и вторыми входами разрешения записи и разрешения переноса пересчетного блока, причем в пересчетный блок введен второй счетчик импульсов, выполненный в виде синхронного счетчика младших разрядов с параллельным переносом и с числом разрядов i, счетный вход которого соединен со счетным входом пересчетного блока, Nr - Nt информационных входов - с соответствующими разрядами пересчетного блока, а инверсный выход 1-го разряда - со счетным входом первого счетчика импульсов, вход разрешения записи - с вторым входом разрешения записи пересчетного блока, инверсный выход первого элемента совпадения соединен с первым входом второго элемента совпадения, второй вход которого соединен с вторым входом разрешения переноса пересчетного блока, а инверсный выход - с первым входом третьего элемента совпадения, второй вход которого соединен с пер-, вым входом разрешения переноса пересчетного блока, третий - с прямым выходом k-ro разряда второго счетчика импульсов, инверсные выходы остальных i - 1 разрядов которого соединены с соответствующими с четвертого по (1 + 2)-й входами третьего элемента совпадения, инверсный выход которого является выходом переноса пересчетного блока, причем фнциеят деления делителя с переменным коэффициентом деления равен К N + 4 - т, где in Г а „

i - количество разрядов второго счетчика импульсов, причем а 1, если прямой выход k-ro разряда второго счетчика импульсов подключен к третьему входу третьего элемента совпадения, или 0, если подключен инверсный выход.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

Изобретение относится к импульсной технике и может быть использовано в измерительной аппаратуре, в цифровых системах автоподстройки частоты, в синтезаторах частоты,, Цель изобретения - повышение надежности при одновременном расширении диапазона значений коэффициентов деления k N + 4 - ш и сохранении высокого быстродействия устройства - достигается путем введения в устройство элементов 8 и 9 совпадения, счетчика 10 импульсов, выполненного в виде счетчика младщих разрядов, и образования новых функциональных связей. Кроме того, устройство содержит элемент 4 совпадения, счетчик 3 импульсов, выполненный в виде счетчика старших разрядов, триггеры 6 и 7, шины 2 и 5 кодовую и входную соответственно. 2 ил.

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1218461A1 |

| Многоразрядный управляемый делитель частоты | 1988 |

|

SU1529443A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-30—Публикация

1988-08-02—Подача