0&. СЈ

|

О S3 NP

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1987 |

|

SU1503070A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Устройство для фазовой автоподстройки частоты | 1990 |

|

SU1739487A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Синтезатор частот | 1980 |

|

SU886254A2 |

Изобретение может быть использовано для генерации сетки частот в измерительных устройствах, а также в приемных и передающих устройствах с широким диапазоном частот, малым шагом перестройки и установившейся ошибкой по фазе, близкой к нулю, Целью изобретения является повышение быстродействия при изменении выходной частоты. Сущность изобретения заключается в том, что в цифровой синтезатор частоты дополнительно введены умножитель 21 частоты и делитель 22 частоты, позволяющие при тех же значениях опорной и выходной частот снизить значения коэффициентов деления делителей 2 и 3 частоты и повысить частоту сравнения фазы в кольце фазовой автоподстройки Цифровой синтезатор также содержит задающий генератор 1, делители 2 и 3 частоты, триггеры 4-6, счетчик 7 импульсов, дешифратор 8, реверсивный счетчик 9, цифроаналоговый преобразователь 10, вентили 11-17, перестраиваемый генератор 18. 2 ил о «g сл

го

Изобретение относится к импульсной технике, может быть использовано для генерации сетки частот в измерительных устройствах, а также в при- емных и передающих устройствах, и является усовершенствованием синтезатора по основному авт.ев„ № 15030700

Цель изобретения - повышение быстродействия при изменении выходной частоты.

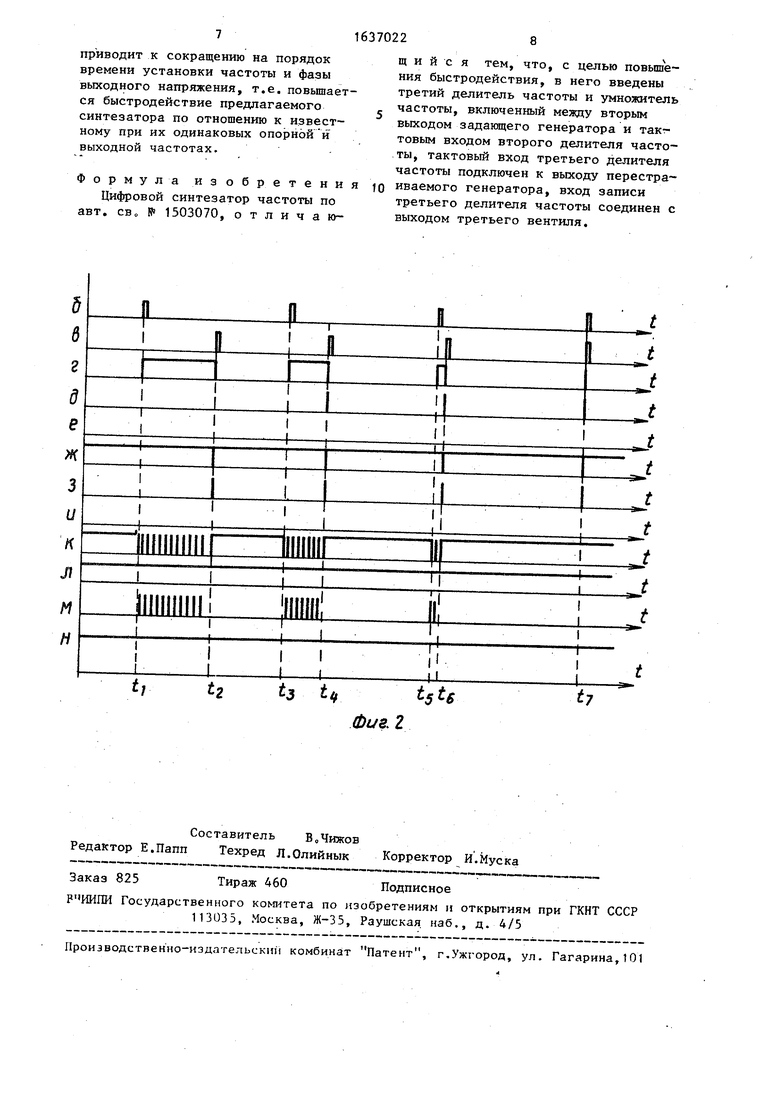

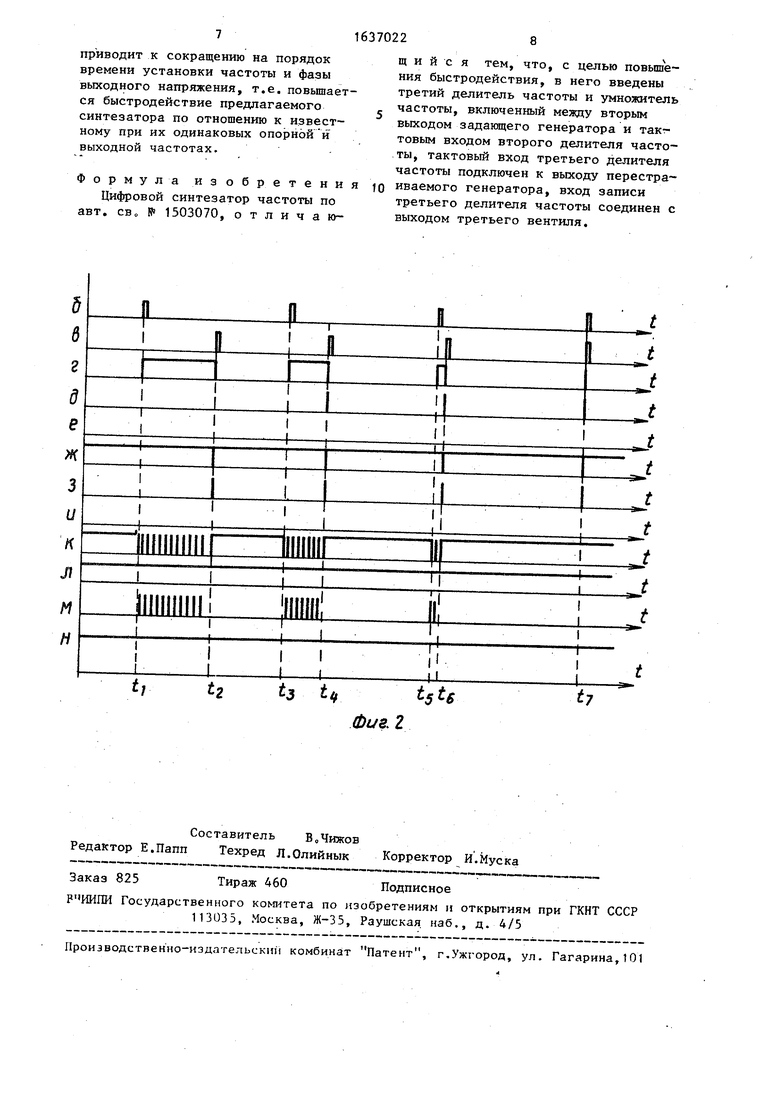

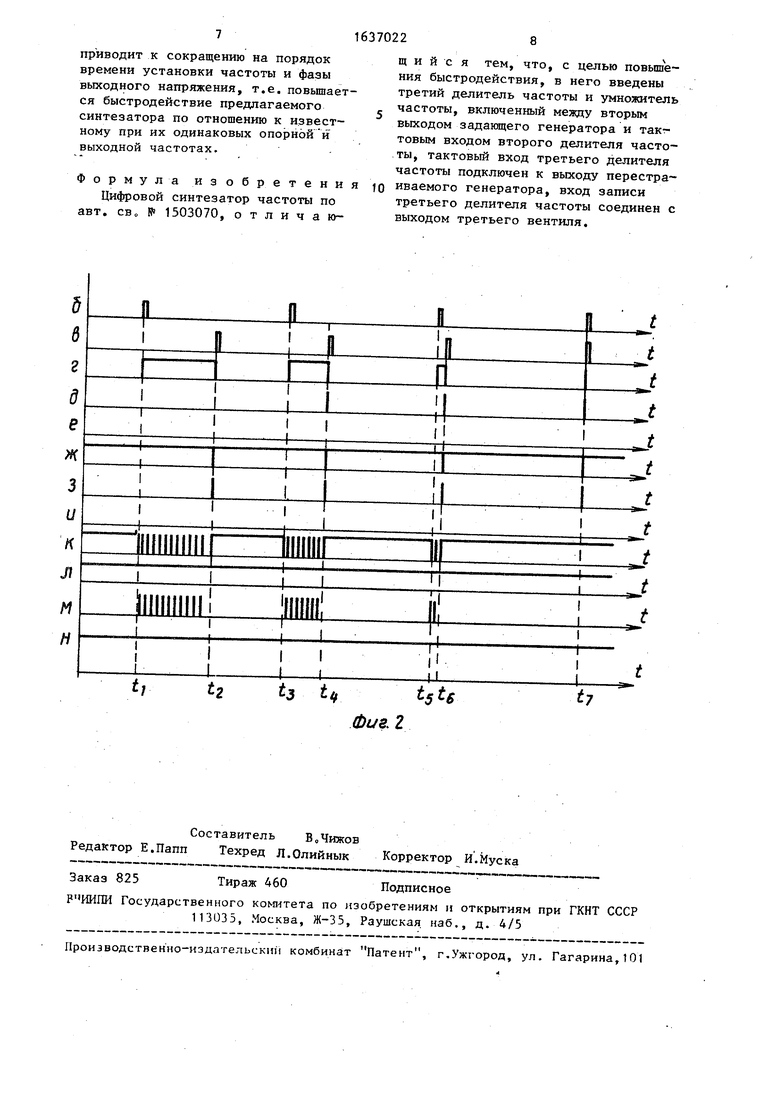

На фиг 1 приведена электрическая структурная схема цифрового синтезатора частот; на фиг. 2 - временные диаграммы, поясняющие работу устрой- ства в установившемся режиме„

Цифровой синтезатор частоты содержит задающий генератор 1, первый и второй делители 2 и 3 частоты, первы 4, второй 5 и третий 6 триггеры, счетчик 7 импульсов, дешифратор 8, реверсивный счетчик 9 импульсов, циф роаналоговый преобразователь 10, первый, второй, третий, четвертый, пятый, шестой и седьмой вентили 11- 17 (вентили 11, 12, 14, 16 и 17 - элементы И-НЕ, вентили 13 и 15 - элементы ИЛИ-НЕ), перестраиваемый генератор 18, шину 19 управления и выходную шину 20, умножитель 21 частоты и третий делитель 22 частоты. Выход (инверсный) первого триггера 4 соединен с первыми входами первого и четвертого вентилей 11 и

14,выход (инверсный) второго триг- гера 5 соединен с первым входом второго вентиля 12 и с вторым входом четвертого вентиля 140 Выход первого вентиля 11 соединен с первым входом седьмого вентиля 17 и с входом суммирования реверсивного счетчика 9 импульсов, вход вычитания которого соединен с выходом второго вентиля

12 и с вторым входом седьмого вентиля 17, выход которого соединен с счетным входом счетчика 7 импульсов вход сброса которого соединен с S- входами первого и второго триггеров 4 и 5 и с выходом пятого вентиля

15,а первый вход которого соединен с первым входом дешифратора 8, с выходом четвертого вентиля 14 и с вторым входом третьего вентиля 13. Второй вход пятого вентиля 15 соединен

с R-входами первого, второго и тре- тьего триггеров 4-6, с шиной 19 управления и с входом стробирования дешифратора 8, входы которого с второго по n-й соединены с соответствующими выходами счетчика 7 импульсов, причем n-й выход счетчика 7 импульсов соединен с его же входом разрешения счета и с тактовым входом третьего триггера 6, прямой выход которого соединен с первым входом третьего вентиля 13, выход которого соединен с входами записи первого, второго и третьего делителей 2, 3 и 22 частоты. Инверсный выход третьего триггера 6 соединен с первым входом шестого вентиля 16, выход которого соединен с вторыми входами первого и второго вентилей 11 и 12, второй вход с первым выходом задающего генератора 1, второй выход которого через умножитель 21 частоты соединен с тактовым входом второго делителя 3 частоты, третий выход с третьими входами первого и второго вентилей 11 и 12. Выходы реверсивного счетчика 9 импульсов через цифроаналоговый преобразователь 10 соединены с входом перестраиваемого генератора 18, выход которого соединен с тактовым входом первого делителя 2 частоты, с выходной шиной 20 и с тактовым входом третьего делителя 22 частоты Тактовые входы первого и второго триггеров 4 и 5 соединены с выходами соответственно второго и первого делителей 3 и 2 частоты. D-входы первого, второго и третьего триггеров 4-6 соединены с общей шиной.

В качестве умножителя 21 частоты можно использовать адаптивный умножитель частоты следования импульсов, а в качестве первого, второго и третьего делителей частоты - делитель частоты следования импульсов с переменным коэффициентом деления.

Синтезатор работает в двух режимах: в режиме грубой частотной автоподстройки и режиме фазовой автоподстройки частоты генератора 18.

В первом режиме устройство работает либо при его включении, либо при переключении устройства на другую частоту. Во второй режим работы устройство автоматически переходит после завершения первого режима. Задание частоты осуществляется подачей на установочные входы умножителя 21 и делителей 2, 3 и 22 (с переменным коэффициентом деления) двоичных кодов, а также импульса на шину 19. При этом на инверсных выходах триггеров 4-6 устанавливаются уровни логической 1

а на выходе вентиля 14 формируется отрицательный импульс В результате этого на выходе вентиля 13 формируется положительный импульс, устанавливающий делители 2, 3 и 22 в исходное состояние, при котором в них записываются двоичные коды коэффициентов деления, подаваемые на их установочные входы. После окончания импульса на шине 19 на выходе вентиля 15 появляется положительный импульс, который сбрасывает счетчик 7 в О и устанавливает триггеры 4 и 5 в единич/

ное состояние, что приводит к оконча- диаграммами, изображенными на фиг.2,,

нию импульсов на выходах вентилей 14 и 15. С этого момента делители 2, 3 и 22 одновременно начинают счет опорных импульсов с выхода генератора 1

В моменты времени t3, t5 и t формируются положительные импульсы на выходе делителя 2 (фиг. 26), а в моменты ta, t4, tg и t7 - на выходе делителя 3 (фиг. 2в)„ Эти импульсы ус танавливают в единичное состояние инверсные выходы соответствующих триггеров 4 и 5 (фиг. 2г,д). При этом открывается соответствующий вентиль

20

и импульсов с выхода генератора 18 соответственно После завершения полных циклов счета делителей 2, 3 и 22 на их выходах формируются положительные импульсыо Импульсы, формируемые делителями 3 и 2, устанавлива- 25 11 или 12 (фиг. 2к,л), пропускающие ют в единичное состояние по С-входу на входы счетчика 9 тактовые импуль- инверсные выходы соответствующих сы частоты f с третьего выхода гене- триггеров 4 и 50 При этом открывается ратора 1 (фиг. 2к,л), что, как и в

В моменты времени t3, t5 и t формируются положительные импульсы на выходе делителя 2 (фиг. 26), а в моменты ta, t4, tg и t7 - на выходе делителя 3 (фиг. 2в)„ Эти импульсы ус танавливают в единичное состояние инверсные выходы соответствующих триггеров 4 и 5 (фиг. 2г,д). При этом открывается соответствующий вентиль

соответствующий вентиль 11 или 12, пропускающий на выходы счетчика 9 тактовые импульсы частоты f, с третьего выхода генератора 1 и через открытый вентиль 16 тактовые импульсы повышенной частоты f с второго выхода генератора 1. При этом соответственно увеличивается или уменьшается число, записанное в счетчике 9 и, следовательно, возрастает или снижается уровень напряжения на выходе преобразователя 10, что приводит к повышению или понижению частоты на выходе генератора 18. Если периоды выходных импульсов делителей 2 и 3 Совпадают с точностью до одного периода тактовых импульсов, поступающих с второго выхода генератора 1, то отрицательный импульс, формируемый на выходе вентиля 14, проходит через дешифратор 8, в результате чего на выходе дешифратора 8 формируется положительный импульс, устанавливающий триггер 6 в единичное состояние„ При этом нулевой потенциал на инверсном выходе триггера 6 запрещает прохождение тактовых импульсов повышенной частоты fд на входы счетчика 11, а единичный потенциал на прямом выходе триггера 6 запрещает прохождение через вентиль 13 отрицательных импервом режиме, приводит к соответству30 ющему изменению напряжения на выходе преобразователя 10 (фиг. 2и) и частоты на выходе генератора 18, что при- водит к сокращению фазовой ошибки„ Максимально допустимая фазовая

,с ошибка контролируется с помощью вентиля 17 и счетчика 7„ При достижении фазовой ошибкой допустимого значения, соответствующего половине емкости счетчика 7, на выходе его старшего

40 разряда устанавливается единичный потенциал, запрещающий дальнейший счет импульсов этим счетчиком и устанавливающий триггер 6 в нулевое состояние, обеспечивая возможность

45 прохождения импульсов с выхода вентиля 14 через вентиль 13 на входы записи делителей 2 и 3. При этом уст- ройство автоматически переходит в первый режим работы.

Таким образом, умножитель 21. и делитель 22 позволяют повысить частоту сравнения импульсов в кольце частотно-фазовой автоподстройки за счет умножения частоты опорного генератора, а также за счет перестройки коэффициента L умножения опорной частоты, позволяющей на порядок снизить значения коэффициентов деления X и У делителей 2 и 3 частоты, что

50

55

т16370226

/ ,

пульсов с выхода вентиля 14 на входы

записи делителей 2 и 3, запрещая тем самым прерывание цикла работы этих делителей0

Таким образом, устройство осуществляет грубую ускоренную автоподстройку частоты генератора 18 за несколько циклов работы делителей 2 и 3 и автоматически переходит во второй режим работы - фазовую автоподстройку частоты генератора 18 с минимальной начальной фазовой ошибкой.

Второй режим работы иллюстрирован

11 или 12 (фиг. 2к,л), пропускающие на входы счетчика 9 тактовые импуль- сы частоты f с третьего выхода гене- ратора 1 (фиг. 2к,л), что, как и в

В моменты времени t3, t5 и t формируются положительные импульсы на выходе делителя 2 (фиг. 26), а в моменты ta, t4, tg и t7 - на выходе делителя 3 (фиг. 2в)„ Эти импульсы устанавливают в единичное состояние инверсные выходы соответствующих триггеров 4 и 5 (фиг. 2г,д). При этом открывается соответствующий вентиль

первом режиме, приводит к соответствующему изменению напряжения на выходе преобразователя 10 (фиг. 2и) и частоты на выходе генератора 18, что при- водит к сокращению фазовой ошибки„ Максимально допустимая фазовая

ошибка контролируется с помощью вентиля 17 и счетчика 7„ При достижении фазовой ошибкой допустимого значения, соответствующего половине емкости счетчика 7, на выходе его старшего

разряда устанавливается единичный потенциал, запрещающий дальнейший счет импульсов этим счетчиком и устанавливающий триггер 6 в нулевое состояние, обеспечивая возможность

прохождения импульсов с выхода вентиля 14 через вентиль 13 на входы записи делителей 2 и 3. При этом уст- ройство автоматически переходит в первый режим работы.

Таким образом, умножитель 21. и делитель 22 позволяют повысить частоту сравнения импульсов в кольце частотно-фазовой автоподстройки за счет умножения частоты опорного генератора, а также за счет перестройки коэффициента L умножения опорной частоты, позволяющей на порядок снизить значения коэффициентов деления X и У делителей 2 и 3 частоты, что

приводит к сокращению на порядок времени установки частоты и фазы выходного напряжения, т.е. повышается быстродействие предлагаемого синтезатора по отношению к известному при их одинаковых опорной и выходной частотах.

Формула изобретени

Цифровой синтезатор частоты по авт. сВо № 1503070, отличаюk Ј« Фие.2

щ и и с я тем, что, с целью повышения быстродействия, в него введены третий делитель частоты и умножитель частоты, включенный между вторым выходом задающего генератора и тактовым входом второго делителя частоты, тактовый вход третьего делителя частоты подключен к выходу перестраиваемого генератора, вход записи третьего делителя частоты соединен с выходом третьего вентиля.

| Цифровой синтезатор частоты | 1987 |

|

SU1503070A1 |

Авторы

Даты

1991-03-23—Публикация

1989-04-14—Подача