информационному ныкрду счетчика итераций, выход р-го разряда счетчика адреса записи соединен с входом второго элемента НЕ, выход которого подключен к входу р-го разряда сумматора, вход переноса которого является входом задания логической единицы устройства, выход дешифратора соединён с ёторым входом первого элемента И, выход которого подключен к счетному входу счетчика адреса считывания, выход нулевого разряда которого соединен с входом третьего элемента НЕ, выход которого соединен с нулевым разрядом второго входа первого мультиплексора, информационный вход второго счетчика является входом задания параметра устройства, второй вход второго элемента И является первым синхровходом устройства, а второй вход элемента ИЛИ .является вторым синхровходом устройства, выход i-го (,р+1) разряда первого счетчика блока управления соединен с i -м разрядом второго мультиплексора блока управления, выход которого подключен к адресному входу блока памяти, управляющий вход которого объединен с управляющим входом блока буферной памяти и подключен к выходу второго разряда первого счетчика блока управления, выход дешифратора блока управления соединен с управляющим входом мультиплексора, а выход первого мультиплексора блока управления подключен к адресному входу блока буферной па.мятй.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1982 |

|

SU1086437A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

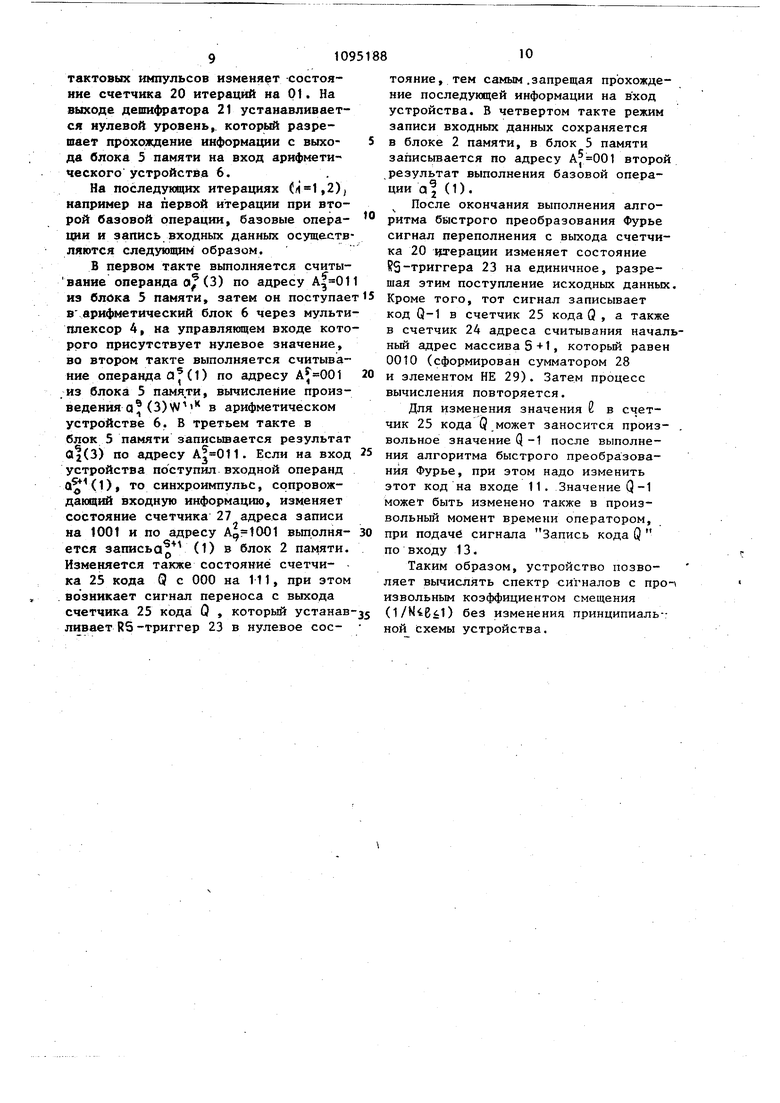

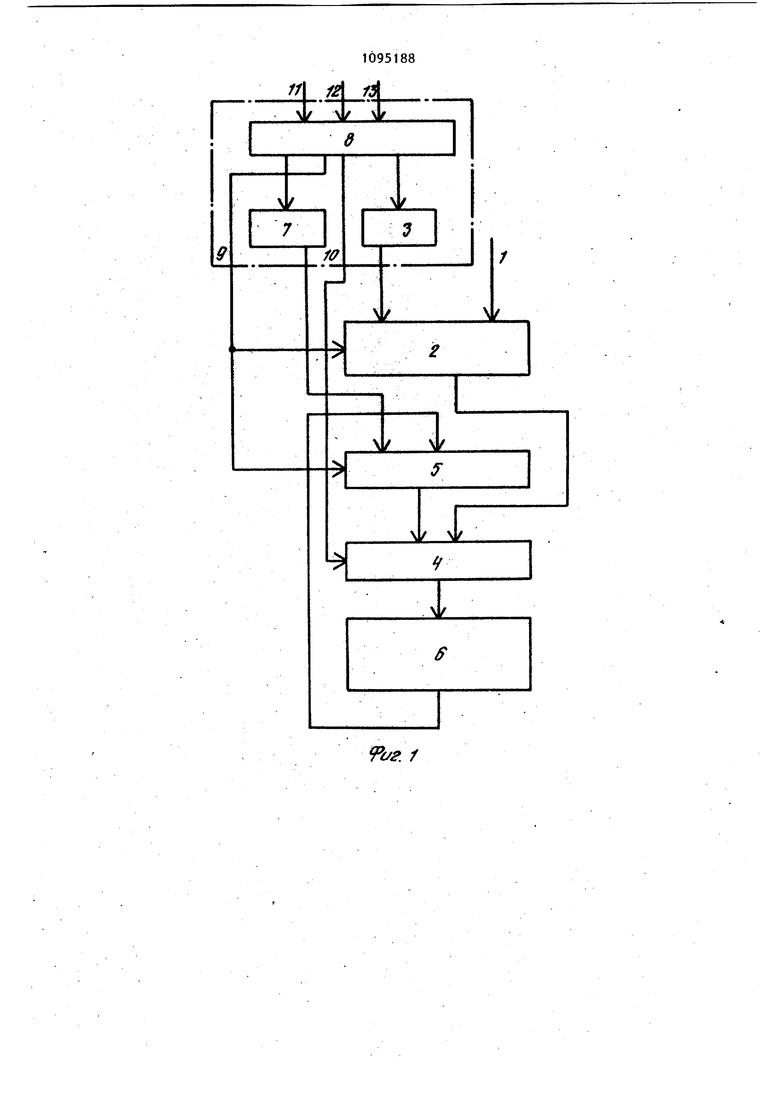

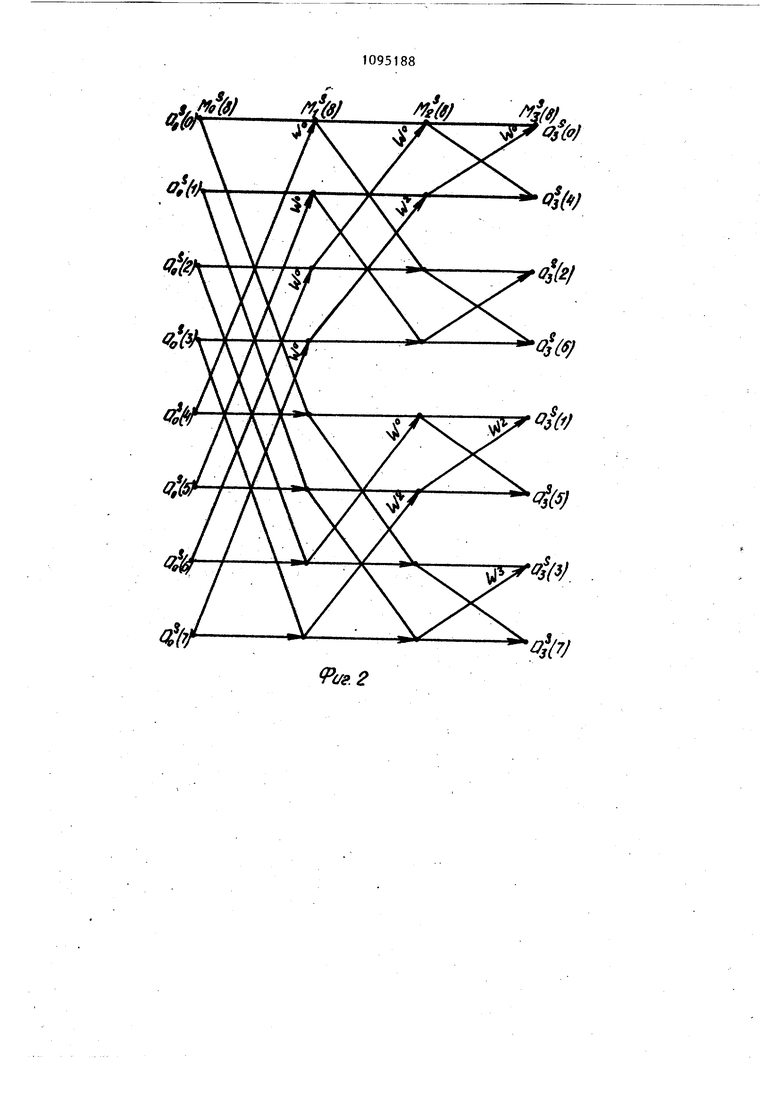

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА, содержащее блок управления, блок памяти и арифметический блок, информационный выход которого соединен с информационным входом блока памяти, отличающееся тем, что, с целью расширенияфункциональных возможностей путем вычисления скользящего спектра с переменным шагом скольжения, в него введены блок буферной памяти и мультиплексор, первый вход которого соединен с информационным выходом блока памяти, информационный вход арифметического блока подключен к выходу мультиплексора, второй вход которого соединен с информационным, выходом блока буферной памяти, информационный вход которого является информационным входом устройства, причем блок управления содержит пер-, вый и второй мультиплексоры, первый . .tjil.: SaasTrciur И второй счетчики, счетчик адреса Записи, счетчик адреса считывания, первый, второй и третий элементы НЕ, RS-триггер, счетчик итераций, сумматор, первый и второй элементы И, дешифратор, элемент ИЛИ и генератор тактовых импульсов, выход . которого подключен к первому входу первого элемента И и счетному входу первого .счетчика, выход переполнения которого соединен со счетным входом счетчика итераций, выход переполнения которого подключен к управляющему входу счетчика адреса считывания, 5 -входу R5 -триггера и первому входу элемента ИЛИ, вьпсод которого соединен с управляющим входом второго счетчика, выход переполнения , которого подключен к R-входу RS-триггера, выход которого соединен с первым входом второго элемента И, выход которого подключен к счетному входу второго счетчика и счетному входу счетчика адреса записи, выход i -го

Изобретение относится к вычислительной технике, предназначено для вычисления циклического,скользящего и мгновенного сигналов по алгоритму быстрого преобразования Фурье и может быть использовано в анализаторах спектра, работающих в реальном масштабе времени при цифровой обработке сигналов в геологииj медицине, радиолокации.

Известно устройство для нахождения спектров сигналов,включающее арифметический блок, блок оперативной памяти, мультиплексор и устройство управления lj . Недостаток данного устройства невозможность вычисления скользящего спектра сигналов с произвольным шагом скольжения. .

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее v 1/Р+1 блотсов буферной памяти, блок памяти, формирователи адреса, устройство ввода, блок управления, содержащий блок синхронизации и блоки адресации арифметический блок,выход которого , соединен с информационным входом блока памяти, адресный вход которого подключен к .выходу блока адресации.

вход которого соединен с выходом блока синхронизации 2.

Однако скользящий спектр в устройстве вычисляется только для одного

значения коэффициента смещения 2 . При необходимости изменить коэффициент смещения (шаг скольжения) требуется доработка как устройства управления, так и изменение количества

и объема блоков буферной памяти, что делает вычисление скользящего спектра с произвольным коэффициентом 6 (1/Иб6 1) практически невозможным. Цель изобретения - расширение

функциональных возможностей устройства путем вычисления скользящего спектра с переменным шагом скольжения.

Поставленная цель достигается тем, что устройство для вычисления скользящего спектра, содержащее блок управления, блок памяти и арифметический блок, информационный выход

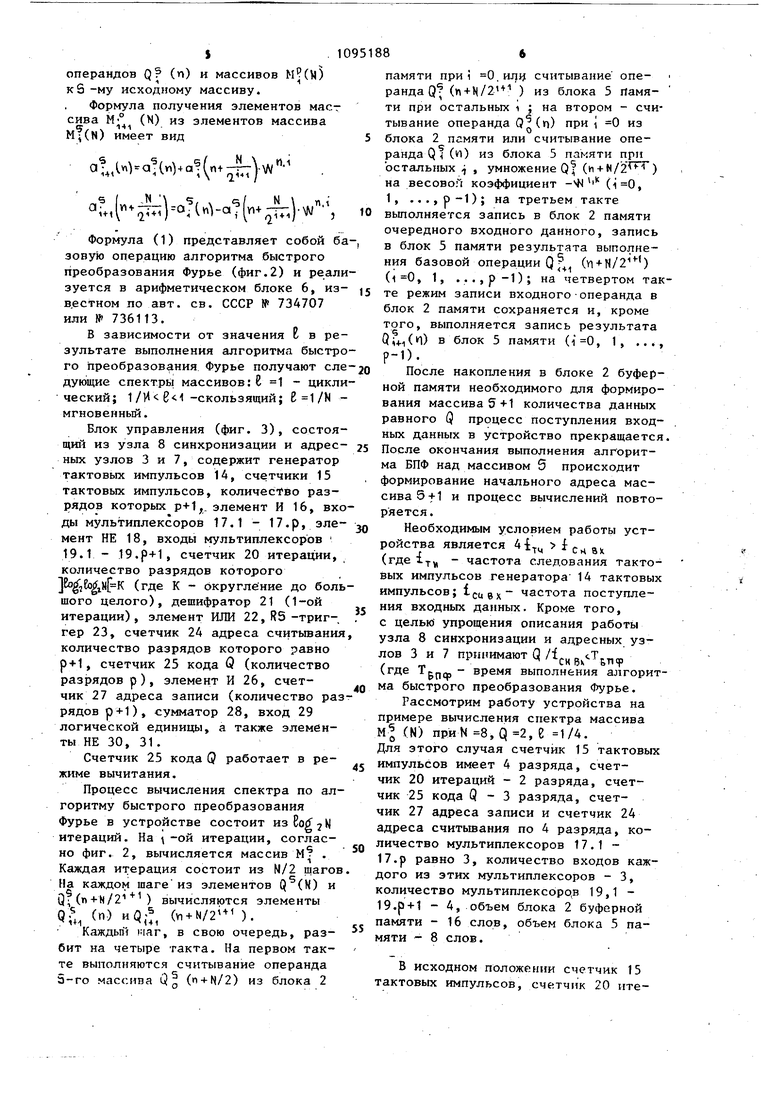

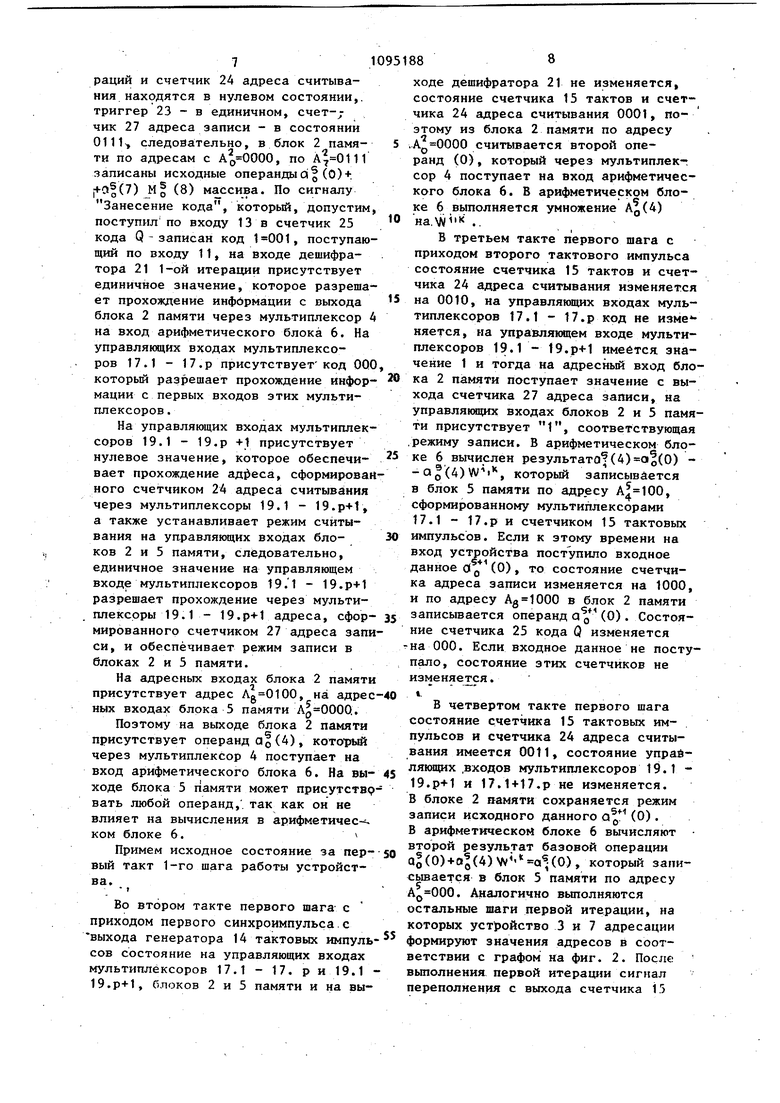

которого, соединен с информационньм входом блока памяти, введены блок буферной памяти и мультиплексор, первый вход которого соединен с информационным выходом блока памяти, информационный вход арифметического блока подключен к выходу гyльтиплeк-. сора, второй--вход .которого соединен Э с информационным выходом блока буфер ной памяти, информационный вход кото рого является информационным входом устройства, причем блок управления содержит первый и второй мультиплексоры, первый и второй счетчики, счет чик адреса записи, счетчик адреса считывания, первый, второй и третий элементы НЕ, R5-триггер, счетчик итё раций, сумматор, первый и второй зле менты И, дешифратор, элемент ИЛИ и генератор импульсов, выход которого подключен к первому входу первого элемента И и счетному входу первого счетчика, выход переполнения которого соединен со счетным входом счетчика итераций, выход переполнения которого подключен к управляющему входу счетчика адреса считывания, 5-входу RS -триггера и первому входу элемента ИЛИ, выход которого соедине с управляющим входом второго счетчика, выход первого переполнения которого подключен к R-входу RS-триггера выход которого соединен с первым вхо дом второго элемента И, выход которого подключен к счетному входу второго счетчика и счетному входу счетчика адреса записи, выход i -го (i 0, р-1) разряда которого подключен к т-му разряду первого входа первого мультиплексора и входу -го разряда сумматора, выход 4-го ( 0, р ) разряда которого соединен с входом { го разряда счетчика адреса считывания, выход 1 -го (,р ) разряда которого соединен с i-ым разрядом второго вхо да первого мультиплексора, управляющий вход .которого соединен с выходом второго разряда первого счетчика, ВЫ ход первого разряда которого подключен к входу первого элемента НЕ, выход которого соединен с входом первого разряда второго мультиплексора, управляющий вход которого объединен с входом дешифратора и подключен к информационному выходу счетчика итераций, выход р-го разряда счетчика адреса записи соединен с входом втогрого элемента НЕ, выход которого под ключен к входу р -го разряда сумматора, вход переноса которого является входом задания логической единицы , устройства, выход дешифратора соединен с вторым входом первого элемента И, выход которого подключен к счетному входу счетчика адреса считывания, выход нулевого разряда ко88торого соединен с входом третьего элемента НЕ, выход КОТОРОГО соедин н; с нулевым разрядом второго входа первого мультиплексора,информационнный вхрл второго счетчика является входом задания параметра устройства, второй вход элемента И является первым синхровходом устройства, второй вход второго элемента ИЛИ является:вторым с:.:нхровходом устройства, выход i -го (,p +1) разряда первого счетчика блока управления соединен с i -ым разрядом второго мультиплексора блока управления, выход которого подключен к адресному входу блока памяти, управляющий вход которого объединен с управляющим входом блока буферной памяти и подключен к выходу второго разряда первого счетчика-блока управления, выход дешифратора блока управления соединен с управляющим входом мультиплексора, а вь1ход первого мультиплексора блока управления подключен к адресному входу блока буФерной памяти, Блок буферной памят вьтолнен с объемом памяти 2 N слов. На фиг. 1 изображена структурная схема устройства; на фиг. 2 - блоксхема алгоритма; на фиг. 3 - конкретная реализация адресньпс блоков и блока синхронизации. Устройство (фиг. 1) содержит информационный вход 1, блок 2 буферной памяти, адресный узел 3, мультиплексор 4, блок 5 памяти, арифметический блок 6, адресный узел 7, узел 8 синхронизации и выходы 9 и 10 узла синхронизации. По входам 11-13 узла синхронизации поступают соответственно код числа (вход 11), синхроимпульсы, сопровождающие входные данные (вход 12) и сигнал начального занесения кода О (вход 13). Устройство вычисляет спектральные составляющие M(N) исходного массива M(N) по алгоритму быстрого преобразования Фурье, граф которого „ представлен на фиг. 2. В используемом алгоритме законы записи и считывания операндов на итерации одинаковы. М обозначает последовательные массивы данных направленного графа; .0|(Ю - элементы массива i изменяется от О до р -1 ; р , ,1,2,...,N-1 соответствует номеру узла графа в i -ом массиве;5 0,1, ; указьшает на принадлежность операндов Q (n) и массивов M(Vl) к9 -му исходному массиву. Формула получения элементов мает сива М° (N) из элементов массива 9 / ч M(N) имеет вид ..а(п,Д;) ,(-°(г.), Формула (1) представляет собой б зовую операцию алгоритма быстрого преобразования Фурье (фиг.2) и реал зуется в арифметическом блоке 6, из в.естном по авт. св. СССР № 73А707 или № 736113. В зависимости от значения Ь в ре зультате выполнения алгоритма быстр го преобразования Фурье получают ел дующие спектры массивов:С 1 - цикл ческий; -скользящий; мгновенный. Блок управления (фиг. 3), состоя щий из узла 8 синхронизации и адрес ных узлов 3 и 7, содержит генератор тактовых импульсов 14, счетчики 15 тактовых импульсов, количество разрядов которых р+1;. элемент И 16, вх ды мультиплексоров 17.1 - 17.р, эле мент НЕ 18, входы мультиплексоров 19.1 - 19.р+1, счетчик 20 итерации, количество разрядов которого Eog, (где К - округление до бол шого целого), дешифратор 21 (1-ой итерации) , элемент ИЛИ 22, R5 -триггер 23, счетчик 24 адреса считьгоани количество разрядов которого равно р+1, счетчик 25 кода Q (количество разрядов р), элемент И 26, счетчик 27 адреса записи (количество ра рядов р+1), сумматор 28, вход 29 логической единицы, а также элементы НЕ 30, 31. Счетчик 25 кода Q работает в режиме вычитания. Процесс вычисления спектра по ал горитму быстрого преобразования Фурье в устройстве состоит из 8о N итераций. На -ой итерации, согласно фиг. 2, вычисляется массив М . Каждая итерация состоит из N/2 шаго На каждом шагеиз элементов Q (К) и Q (n+N/2 M вычисляются элементы Qfn f Qi, ( ). Каждьп) Miar, в свою очередь, разбит на четыре такта. На первом такте выполняются считывание операнда 5-го массива Q (n + N/2) из блока 2 памяти при i 0, Щ1} считывание операнда Q (п + К/2 ) из блока 5 памяти при остальных i ; на втором - считывание операнда Q(п) приi 0 из блока 2 памяти или считывание операнда Qf(n) из блока 5 памяти при остальных -J , умножение of (h + N/2) на BecoBofi коэффициент (, 1, ...,р-1); на третьем такте вьтолняется запись в блок 2 памяти очередного входного данного, запись в блок 5 памяти результата выполнения базовой операции Q (vi-t-fl/2 ) (, 1, ...,р-1); на четвертом такте режим записи входного-операнда в блок 2 памяти сохраняется и, кроме выполняется запись результата (n) в блок 5 памяти (, 1, .., р-1). После накопления в блоке 2 буферной памяти необходимого для формирования массива 5+1 количества данных равного Q процесс поступления входных данных в устройство прекращается. После окончания выполнения алгоритма БПФ над массивом 5 происходит формирование начального адреса массива 5+1 и процесс вычислений повторяется. Необходимым условием работы устройства является i сц аи (где ITVI частота следования тактовых импульсов генератора 14 тактовых импульсов; icuex частота поступления входных данных. Кроме того, с целью упрощения описания работы узла 8 синхронизации и адресных узлов 3 и 7 принимают (J/1 .,.., ,.i.Hr5XbT (где - время выполнения алгоритма быстрого преобразования Фурье. Рассмотрим работу устройства на примере вычисления спектра массива М (N) ,,е 1/4. Для этого случая счетчик 15 тактовых импульсов имеет 4 разряда, счетчик 20 итераций - 2 разряда, счетчик 25 кода Q - 3 разряда, счетчик 27 адреса записи и счетчик 24 адреса считьшания по 4 разряда, количество мультиплексоров 17.1 17.р равно 3, количество входов каждого из этих мультиплексоров - 3, количество мультиплексоро.в 19,1 19.р+1 - 4, объем блока 2 буферной памяти - 16 слов, объем блока 5 памяти - 8 слов. В исходном положении счетчик 15 тактовых импульсов, счетчик 20 итераций и счетчик 24 адреса считывания находятся в нулевом состоянии,, триггер 23 - в единичном, счетчик 27 адреса записи - в состоянии 0111 следовательно, в блок 2 памяти по адресам с , по записаны исходные операнды d| (О) + гЮ|(7) Мп (8) массива. По сигналу г -о- - о . Занесение кода, который, допустим, поступил по входу 13 в счетчик 25 кода Q - записан код , поступающий по входу 11, на входе дешифратора 21 1-ой итерации присутствует единичное значение, которое разрешает прохождение информации с выхода блока 2 памяти через мультиплексор 4 на вход арифметического блока 6. На управляющих входах мультиплексоров 17.1 - 17.р присутствуеткод 000 который разрешает прохождение информации с первых входов этих мультиплексоров. На управляющих входах мультиплексоров 19.1 - 19.Р +1 присутствует нулевое значение, которое обеспечивает прохождение , сформировай ного счетчиком 24 адреса считывания через мультиплексоры 19.1 - 19., а также устанавливает режим считывания на управляющих входах блоков 2 и 5 памяти, следовательно, единичное значение на управляющем ВХОД0 мультиплексоров 19.1 - 19.Р+1 разрешает прохождение через мультиплексрры 19.1 - 19.р+1 адреса, сформированного счетчиком 27 адреса запи си, и обеспечивает режим записи в блоках 2 и 5 памяти. На адресных входах блока 2 памяти присутствует адрес , на адрес ных входах блока 5 памяти .. Поэтому на выходе блока 2 памяти присутствует операнд а (4), кото1 ый через мультиплексор 4 поступает на вход арифметического блока 6. На выходе блока 5 памяти может присутствр вать любой операнд,, так как он не влияет на вычисления в арифметическом блоке 6. Примем исходное состояние за первый такт 1-го шага работы устройства. t Во втором такте первого шага с приходом первого синхроимпульса с выхода генератора 14 тактовых импуль сов состояние на управляющих входах мультиплексоров 17.1 - 17. ри19.1 19.Р+1, б.поков 2 и 5 памяти и на вы188 ходе дешифратора 21 не изменяется, состояние счетчика 15 тактов и счетчика 24 адреса считывания 0001, поэтому из блока 2 памяти по адресу считывается второй операнд (0), который через мультиплекг сор 4 поступает на вход арифметического блока 6. В арифметическом блоке 6 выполняется умножение Ha. .. В третьем такте первого шага с приходом второго тактового импульса состояние счетчика 15 тактов и счетчика 24 адреса считывания изменяется на 0010, на управляющих входах мультиплексоров 17.1 - 17.Р код не изме няется, на управляющем входе мультиплексоров 19.1 - 19. имеется значение 1 и тогда на адресный вход блока 2 памяти поступает значение с выхода счетчика 27 адреса записи, на управляющих входах блоков 2 и 5 памяти присутствует 1, соответствующая режиму записи. В арифметическом блоке 6 вычислен результата(4)0(0) который записывается в блок 5 памяти по адресу , сформированному мультиплексорами 17.1 - 17.Р и счетчиком 15 тактовых импульсов. Если к этому времени на вход устройства поступило входное данное of jj (0) , то состояние счетчика адреса записи изменяется на 1000, и по адресу в блок 2 памяти С.Л.Л. записывается операнд а (0). Состояние счетчика 25 кода Q изменяется на 000. Если входное данное не поступало, состояние этих счетчиков не изменяется. . В четвертом такте первого шага состояние счетчика 15 тактовых импульсов и счетчика 24 адреса считывания имеется ООН, состояние упрайлякнцих .входов мультиплексоров 19.1 19.Р+1 и 17.1+17.р не изменяется. В блоке 2 аамяти сохраняется режим записи исходного данного а (0). В арифметическом блоке 6 вычисляют второй результат базовой операции ao(0)+a(4)(0), который записьшается в блок 5 памяти по адресу . Аналогично выполняются остальные шаги первой итерации, на которых устройство 3 и 7 адресации формируют значения адресов в соответствии с графом на фиг. 2. После выполнения первой итерации сигнал переполнения с выхода счетчика 13 тактовых импульсов изменяет состояние счетчика 20 итераций на 01. На выходе дешифратора 21 устанавливается нулевой уровень, который разрешает прохождение информации с выхода блока 5 памяти на вход арифметического устройства 6. На последующих итерациях ((,2), например на первой итерации при второй базовой операции, базовые операции и запись входных данньк осуществ ляются следующим образом, В первом такте выполняется считывание операнда 0 (3) по адресу из блока 5 памяти, затем он поступае В арифметический блок 6 через мульти плексор 4, на управляющем входе кото рого присутствует нулевое значение, во втором такте выполняется считывание операнда а(1) по адресу из блока 5 памяти, вычисление произведения а (3) в арифметическом устройстве 6. В третьем такте в блок 5 памяти записывается результат ) по адресу . Если на вход устройства поступил входной операнд Q(1), то синхроимпульс, сопровождающий входную информацию, изменяет состояние счетчика 27 адреса записи на 1001 и по адресу вьшрлняется записьОр У (1) в блок 2 памяти. Изменяется также состояние счетчика 25 кода Q с 000 на 111, при этом возникает сигнал переноса с выхода счетчика 25 кода О , который устанав ливает R5 -триггер 23 в нулевое состояние, тем самым .запрещая прохождение последующей информации на вход устройства. В четвертом такте режим записи входных данных сохраняется в блоке 2 памяти, в блок 5 памяти запис лвается по адресу второй результат выполнения базовой операции 02(1)После окончания выполнения алгоритма быстрого преобразования Фурье сигнал переполнения с выхода счетчика 20 итерации изменяет состояние i S-триггера 23 на единичное, разрешая зтим поступление исходных данных. Кроме того, тот сигнал записывает код Q-1 в счетчик 25 кодаQ , а также в счетчик 24 адреса считывания начальный адрес массива S-1, который равен 0010 (сформирован сумматором 28 и злементом НЕ 29). Затем процесс вычисления повторяется. Для изменения значения 2 в счетчик 25 кода Q может заносится произ- , вольное значение Q-1 после выполнения алгоритма быстрого преобразования Фурье, при этом надо изменить этот код на входе 11. Значение Q-1 может быть изменено также в произвольный момент времени оператором, при подаче сигнала Запись кода Q по входу 13. Таким образом, устройство позволяет вычислять спектр сигналов с про- извольным коэффициентом смещения (1/М4б 1) без изменения принципиаль-г ной схемы устройства.

Гг

/

/

X

j.6f)(ffJ 3fff},

(/.2

0(7}

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для реализации алгоритма быстрого преобразования фурье | 1973 |

|

SU480079A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| И | |||

| , ПикуЛИН B.C | |||

| и др | |||

| Аппаратурная реализа- ция дискретного преобразования Фурье | |||

| М., Энергия, 1978, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

Авторы

Даты

1984-05-30—Публикация

1983-03-14—Подача