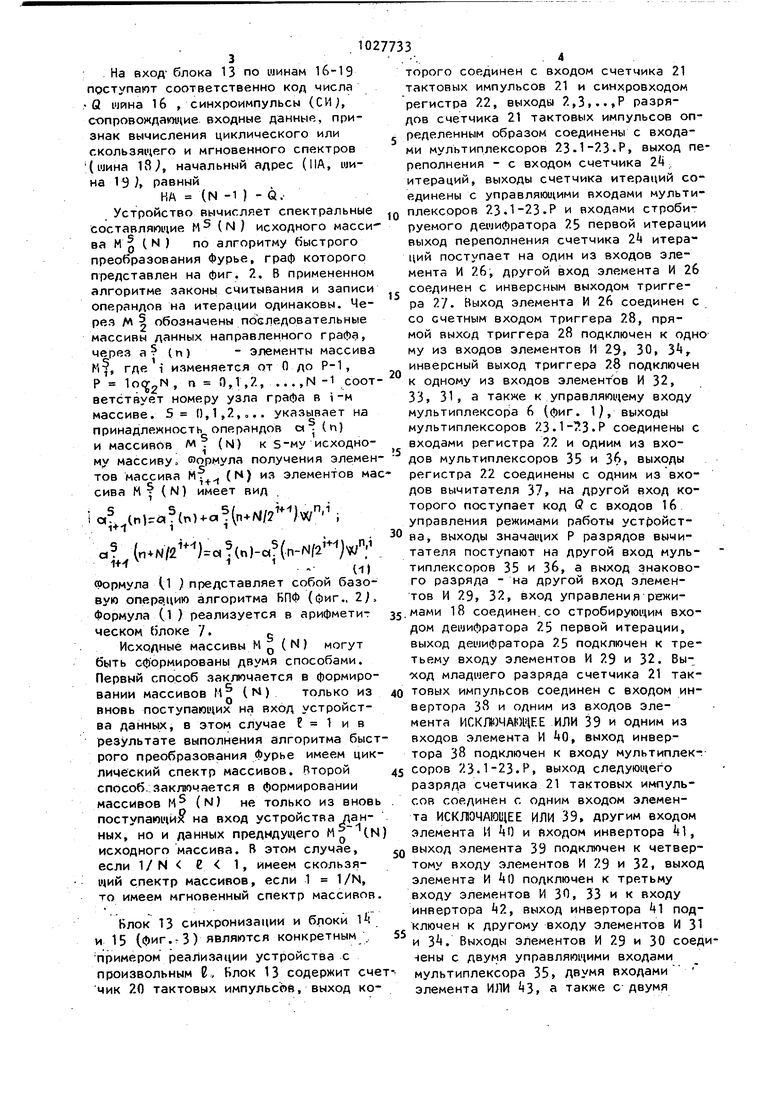

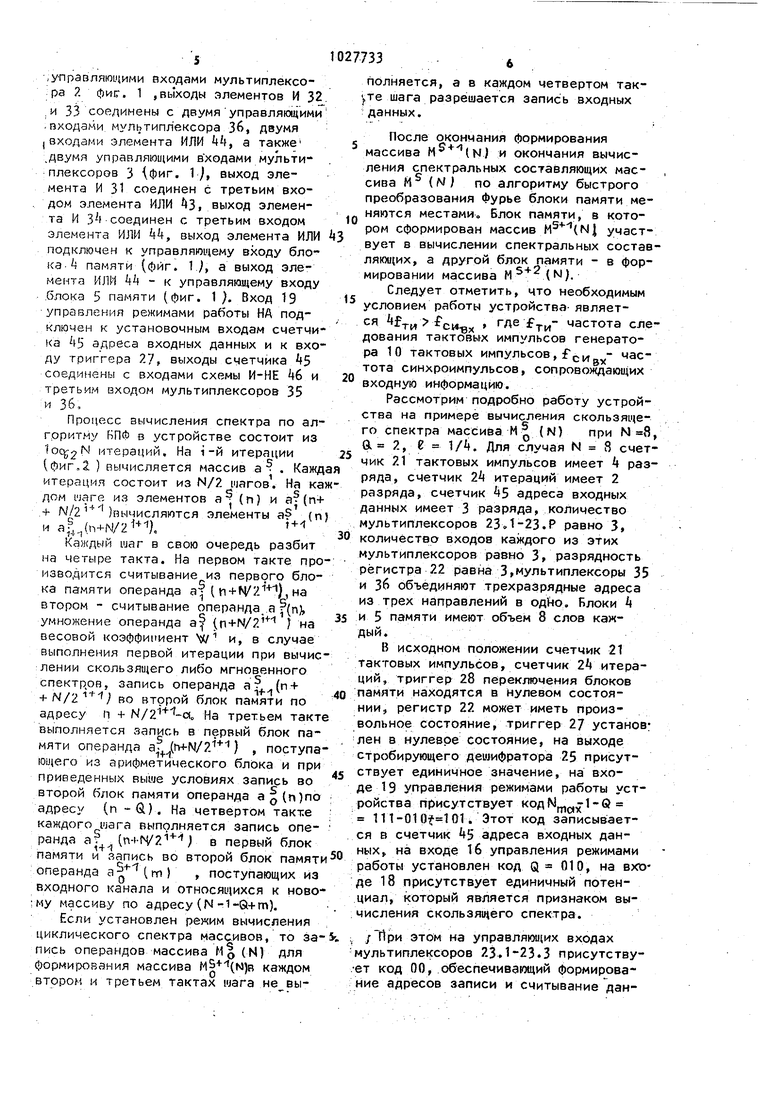

11 Изобретение относится к вычислительной технике -и предназначено для вычисления циклического, скользящего и мгновенного спектров сигналов по алгоритму быстрого преобразования Фурье, Изобретение может быть использовано 3 анализаторах спектра, работающих в реальном масштабе времени при цифровой обработке сигналов в гео логии, медицине, радиолокации. Известны устройства для нахождения спектров сигналов, включающие арифметический блок, блок оперативной памяти, мультиплексоры, устройство управления 1 . Недостатком аналогов является невозможность вычисления скользящего и мгновенного спектров сигналов. Наиболее близким по технической сущности к предлагаемому Является устройство для вычисления циклическо го и скользящего спектров сигналов по алгоритму быстрого преобразования Фурье (ВПФ) с постоянным коэффициентом смещения для скользящего спектра Q /N , где N - размерность обрабатываемого массива, Q - количество входных данных, участвующих в формировании следующего.массива, и содержит г 1/2 - 1 блоков буферной памяти, формирователи адреса, устройство ввода, устройство управления, процессор 2. . Спектр сигнала вычисляется на базе быстрого преобразования Лурье,при этом в состав процессора входит запоминающее и арифметическое устройство, Недостатком прототипа является то, что скользящий спектр в устройстве вычисляется только для одного значения коэффициента смещения Е, При необходимости изменить коэффициент смещения требуется переделка как устройctBa управления, так и изменение количества и объема блоков буферной памяти, что делает вычисление скользящего.спектра с произвольным коэффициveHTOM С, а также (мгновенного спектра ( i/N ) практически невозможным. К недостатку прототипа можно также отн ти наличие буферных блоков памяти, что увеличивает аппаратурные затраты устройства, особенно при малых С. Цель изобретения - расширение функ циональных возможностей устройства за счет выключения скользящего, с произвольным коэффициентом смещения,, и мгн 1зенного спектров, а также уменьшение объеь -5 аппаратурных затрат. 3 Поставленная цель достигается тем, что устройство для вычисления скользяр1его спектра, содержащее первый блок памяти, арифметический блок, блок синхронизации, первый и второй блоки формирования адреса, первый выход бло-ка синхронизации соединен с входом первого блока формирования адреса, выход которого подключен к первому входу первого блока памяти, второй вход которого соединен с вторым выходом блока синхрюнизации, третий выход блока синхронизации соединен с входом второго блока формирования адреса, дополнитель но содержит второй блок памяти и три мультиплексора, четвертый выход блока синхронизации соединен с управляющим входом первого мультиплексора, вы ход которого подключен к третьему входу первого блока памяти, выход которого соединен с первыми входами второго и третьего мультиплексоров, управляющие входы которых подключены соответственно к пятому и шестому вь1ходам блока синхронизации, седьмой выход которого соединен с первым входом второго блока памяти, второй вход которого подключен к выходу второго блока формирования адреса, выход арифметического 6лока подклочен к первому входу еого мультиплексора и второму вхол второго мультиплексора, третий вход которого объединен с вторн.ч входом первого мультиплексора и является входом устройства, вход арифметического блока соединен с выходсж третьего муль типлексора, выход второго мультиплек сора соединен с третьим входом второго блока памяти, выход которого подключен к второму входу третьего мультиплексора и третьему входу первого мультиплексора, выход которого соединен с третьим входом первого блока памяти, первый вход блока синхронизации является входом задания кода числа устройства, второй вход - синхронизирующим входом устройства, третий вход входом задания признака устройства, а четвертый вход - входом установки начального адреса устройства. На фиг. 1 изображено устройство, функциональная схема; на фиг. 2 блок-схема алгоритма; на фиг. 3 блок-схема блока синхронизации. Схема фиг. Т )включает вход 1 устройства, мультиплексоры 2 и 3, блоки i и 5 памяти мультиплексора 6, арифметический блок 7, выхода 8-12 блока 13 синхронизации, блоки t и 15 формирования адреса. ; -На ВХОДблока 13 по шинам 16-19 прступают соответственно код числа . Q шина 16 , синхроимпульсы (СИ;, сопровождатцие входные данные, признак вычисления циклического или скользя1чего и мгновенного спектров (шина 18, начальный адрес (НА, шина 19 )t равный НА (N -1 ) - Q.Устройство вычисляет спектральные составляющие М (N) исходного масси ва М Q ( N ) по алгоритму быстрого преобразования Фурье, граф которого представлен на фиг, ., В примененном алгоритме законы считывания и записи операндов на итера.ции одинаковы. Через Дл I обозначены последовательные массивы данных направленного графа, через а (п) - элементы массива М, где i изменяется от О до Р-1, Р locjj,N, п 0,1,2, ...,N -1 COOT ветствует номеру узла графа в i-м массиве. 5 0,1,2,,.. указывает на принадлежность операндов а j (п) и массивов /и (М) к s-му исходному массиву о йормула получения элемен тов массива м| (N) из элементов ма с 11-1 5 /411 ,.от г,...п сива М (N) имеет вид I 1(..(г.)-с.,( i - , f, о. ((2 . (п)-о(. (n-Nf2 | - (1) Формула и JI представляет собой базовую оперэ.Цию алгоритма ВПФ (фиг., 2) Формула (1 ) реализуется в арифметит часком блоке 7. Исходные массивы М Р (N) могут быть сформированы двумя способами. Первый способ заклочается в формировании массивов fif (N) только из вновь поступающих на вход устройства данных, в этом случае 1 и в результате выполнения алгоритма быст рого преобразования Фурье имеем циклический спектр массивов. Второй способ, заключается в формировании массивов М (N) не только из вновь поступающй на вход устройства данных, но и данных предыдущего (.N исходного массива. В этом случае, если 1/N е 1, имеем скользящий спектр массивов, если 1 1 /N, то имеем мгновенный спектр массивов. Блок 13 синхронизации и блоки 1 и 15 (фиг.гЗ) являются конкретным примером реализации устройства с произвольным К, Блок 13 содержит сче цик 20 тактовых импульсов, выход которого соединен с входом счетчика 21 тактовых импульсов 21 и синхровходом регистра 22, выходы 2,3,..,Р разрядов счетчика 21 тактовых импульсов определенным образом соединены с входами мультиплексоров 23.1-ЯЗ.Р выход переполнения - с входом счетчика 2Ц, итераций, выходы счетчика итераций соединены с управляющими входами мультиплексоров 23.1-23.Р и входами стробируемого де1чифратора 25 первой итерации выход переполнения счетчика итераций поступает на один из входов элемента И 26, другой вход элемента И 2б соединен с инверсным выходом триггера 27. Выход элемента И 2б соединен с со счетным входом триггера 28, прямой выход триггера 28 подключен к одно му из входов элементов И 29, 30, 3 инверсный выход триггера 28 подключен к одному из входов элементов И 32, 33, 31, а также к управляющему входу мультиплексора 6 (фиг. 1), выходы мультиплексоров 23.1-7-3.Р соединены с входами регистра 22 и одним из входов мультиплексоров 35 и 36, выходы регистра 22 соединены с одним из входов вычитателя 37, на другой вход которого поступает код G с входов 16 управления режимами работы устройстна, выходы значащих Р разрядов вычитателя поступают на другой вход мультиплексоров 35 и 36, а выход энакового разряда - на другой вход элемеНтов И 29, 32, вход управления рнжи соединен, со стробирующим входом дешифратора 25 первой итерации, выход дешифратора 25 подключен к третьему входу элементов И 23 и 32. младшего разряда счетчика 21 тактовых импульсов соединен с входом инвертора 38 и одним из входов Элемента ИСКШЧАОДЕЕ ИЛИ 39 и одним из входов элемента И АО, выход инвертора 38 подключен к входу мультиплекг соров 23.1-23.Р, выход следующего разряда счетчика 21 тактовых импульсов соединен с одним входом эленента ИСКЛ10ЧАЮУ1ЕЕ ИЛИ 39, ДРУГим входом элемента И 0 и йходом инвертора k, ВЫХОД элемента 39 подключен к четвертому входу элементов И 29 и 32, выход элемента И А О подключен к третьму входу элементов И 30, 33 и к входу инвертора А2, выход инвертора kl подключен к другому входу элементов И 31 и ЗА. Выходы элементов И 29 и 30 соединены с двумя управляющими входами мультиплексора 35, двумя входами элемента ИЛИ 43, а также с двумя ,управляющими входами мультиплексора . фиг. 1 ,выходы элементов И 32. .и 33 соединены с двумяуправляющими -входами мультиплексора Зб, двумя (входами элемента ИЛИ kk, а также .двумя управляющими входами мультиплексоров 3 фиг. 1), выход элемента И 31 соединен с третьим входом элемента ИЛИ 43, выход элемента И соединен с третьим входом элемента ИЛИ kk, выход элемента ИЛИ подключен к управляющему входу блока- А памяти (фиг. Г), а выход элемента ИЛИ - к управляиацему входу блока 5 памяти (фиг. 1 ), Вход 19 управления режимами работы НА подключен к установочным входам счетчика f5 адреса входных данных и к входу триггера 27, выходы счетчика 5 соединены с входами схемы И-НЕ 6 и третьим входом мультиплексоров 35 и 36, Процесс вычисления спектра по алгоритму ВПФ в устройстве состоит из loQ итеоаций. На i-и итерации f .i ,, ч S ,,,л вычисляется массив а . Кажд .., 1 11 итерация состоит из N/2 шагов. На ка м/;1-м-, °« а (п) и а (n-f + N/2 /вычисляются элементы а (п S , , j+1 . „ ° Каждый шаг в свою очередь разбит на четыре такта. На первом такте про изводится считывание из первого блока памяти операнда af Щ + ), на втором - считывание с перанда а| п), ч : ,/oi-(-i S умножение операнда а {,n+N/. J на весовой коэффициент W и, в случае 3 W к,, о jjTM выполнения первой итерации при вычис и лении скользящего либо мгновенного 5 / спектррв, запись операнда а (n-f + ) во второй блок памяти по адресу п + , На третьем такт выполняется запись в первый блок паS //nl+l мяти операнда a.(tvbN/2i -) , поступа ющего из арифметического блока и при приведенных выше условиях запись во второй Ьлок операнда ао(п)по адресу (п -&). На четвертом так-пе каждого шага выполняется запись операнда а (n-(-fS/2 j в первый блок iT-i„ памяти и запись во второй блок памят операнда а Чт) , поступающих из входного канала и относящихся к ново;му массиву по адресу (N-1-Q+т). Если установлен режим вычисления циклического спектра массивов, то запись операндов массива М (N) для формирования массива м5(М)в каждом втором и третьем тактах шага не выполняется, а в каждом четвертом такj,Te шага разрешается запись входных сданных. После окончания формирования массива (М) и окончания вычисления спектральных составляющих массива М (N по алгоритму быстрого преобразования Фурье блоки памяти меняются местами. Блок памяти, в котором сформирован массив (NJ участвует в вычислении спектральных составляющих, а другой блок памяти - в формировании массива ). Следует отметить, что необходимым условием работы устройства является f-ги где частота следования тактовых импульсов генератора 10 тактовых импульсов, f си - частота синхроимпульсов, сопровождавдих входную информацию. Рассмотрим подробно работу устройства на примере вычисления скользящего спектра массива М Q(N) при , а 2, 6 1/4. Для случая N 8 счетi-i i чик 21 тактовых импульсов имеет ч разл1 - / ряда, счетчик 2ч итерации имеет 2 45 адреса входных , разряда, количество оэ t «vo г. мультиплексоров 23Л-23.Р равно 3, количество входов каждого из этих мультиплексоров равно 3, разрядность Регистра.22 равна 3,мультиплексоры 35 объединяют трехразрядные адреса направлении в одНо. Блоки и 5 памяти имеют объем о слов ка«v ,, о g исходном положении счетчик 21 . тактовых импульсов, счетчик 2ч итера„ оо ции, триггер 2о переключения блоков памяти находятся в нулевом состоянии, регистр 22 может иметь произвольное состояние, триггер 2/ установ: лен в нулевое состояние, на выходе СП D njTJi OWti . f f i« стробирующего дешифратора 25 присут у единичное значение, на входе ig управления режимами работы устройства присутствует 111-010 101. Этот код записывается в счетчик э адреса входных данных на входе 16 управления режимами g, установлен код Q 010, на вхо g присутствует единичный потенциал, который является признаком вычисления скользящего спектра. этом на управляющих входах мультиплексоров 23.1-23.3 присутствует код 00, обеспечивающий формирование адресов записи и считывание данIннх для выполнения первой итерации ал гбритма, на выходах мультиплексоров :23.1-23о3 имеем код 100. На управляю;щих входах мультиплексора 35 присутствует код ПО, так как на входы эле;ментов И 29 и 30 поступает нулевой потенциал с прямого выхода триггера 28 переключения блоков памяти. Пусть код 00 на управляющих входах мультиплексоров 35 и Зб разрешает про хождение кода с выхода мулътиплексора 23.1-23.3 на адресный вход блокад памяти или блока 5 памяти соответственно. На адресных входах блока k памяти присутствует код 100. На входах элемента И 31 присутствуют единичные значения, поступающие с выхода инвер;тора 1 и инверсного выхода триггера 28. Единичное значение с выхода элемента И 31 пройдя через элемент ИШ «3, поступает на управляющий вход блока 4 памяти. Пусть единич ное значение на управляющем входе ,бло ков памяти разрешает считывание информации из блоков памяти Считаем, что а блок Ц памяти по последовательным адресам записаны данные массива МдЛб), тогда в блоке 5 памяти формируется массив , Таким образом, на выходе блока f{ памяти присутствует операнд а Q (4) . На управлякяцем входе мультиплексора 6 присутствует значение 1. Пусть единичное значение на управлякяцем входе мультиплексора 6 . разрешает прохождение информации с вы хода блока 4 памяти на вход арифметического блока 7, а нулевое значение разрешает прохождение информации С выхода блока 5 памяти на вход арифметического блока 7, На один из входов элементов И 32 и 33 поступает нулевой потенциал с выходов элементов И 39 и 0 соответственно, тогда на вы ходе элементов И 32 и 33 присутствует код 00j он же поступает на управляюи ие входы мультиплексора 36, разрешая прохождение кода 100 с выхода мультиплексоров 23.1-23.3 на адресный вход блока 5 памяти, на выходах элемента ИЛИ 3 присутствует нулевые значес выхода элемента единичния, ный потенциал поступает на управляющий вход блока 5 памяти, разрешая считывание данных из блока 5 памяти. Данные, считанные из блока 5 памяти, не попадают на вход арифметического блока 7, так как на управляющем входе мультиплексора 6 присутствует единичное значение, разрешающее прохождение информации из блока k памяти. Код 00 на управляющих входах мультиплексора 3 разрешает прохождение данных с выхода арифметического блока 7 на блока 5 памяти. Следовательно, состояние управляющих входов мультиплексоров, соединенных с блоком памяти, в котором идет формирование следующего массива, является безразличным. Таким образом, а исходном состоянии выполнился первый такт, первого шага работы устройства. Во втором такте первого шага с ходом первого тактового импульса код 100 на выходе мультиплексоров 23.1- 23.3 запишется в регистр 22, а счетчик 21 тактовых импульсов изменит свое состояние на 0001. Код на выходе мультиплексоров 23.1-23.3 изменит свое значение на 000. Состояние управляющих входов мультиплексоров 35 и 36 и управляющего входа блока не изменяется и из блока памяти выпол- ; няется считывание операнда а (0)по адресу 000. На выходе блока памяти присутствует операнд а (4) ив арифметическом блоке 7 выполняется умножение а (4j на fj На выходе вычитателя 37 в этом такт те образуется код 010, а на выходе его знакового разряда единичное значение которое является признаком положительной разности адреса ТОО операнда а (4) и кода 010 Q .Это единичное значение, поступая на вход элемента И 29, не изменит состояния его выходов, а поступая на вход элемента И 32 изменит состояние его выхода на единичное, так как в это же время на входе элемента И 32 Присутствует единичное значение с выхода элемента ИСКЛОЧАЮЩЕЕ ИЛИ 39 и инвертора 2. Состояние выхода элемента И 33 не изменяется. Таким ббрйзои, на управляющих входах мультиплексоров 36 и 3 присутствует код 10, а на управляющем входе блока 5 памяти нулевое значение. Код 10 разрешает прохождение кода 010 с выхода вычитателя 37 через мультиплексор 36 на адресный вход блока 5 памяти и Операнда (М а ч с выхода блока памяти через мультиплексор 3 на вход блока 5 памяти, а нулевое значение на управляющем входе блока 5 памяти разрешает запись операнда а| (k) по адресу 010 в блок 5 гтаняти. На этом второй такт первого шага заканчивается, В третьем такте первого шага с приходом второго тактового импульса код

000 на входе мультиплексоров 23-123.3 запишется в регистр 22, а счетчик .1 тактовых импульсов изменит свое состояние на ОП10. Код на выход мультиплексоров 23И-23.3 изменит свое значение на ТОП. Состояние управляющих входов мультиплексоров 35, 2 и 6 не изменится, а управляющего входа блока 4 памяти изменится на нулевое за счет присутствия единичных значений на входах элемента И 31 Нулевое значение на управляющем входе блока k памяти разрешает запись операндов. На выходе блока памяти в этом такте имеем операнд а (0), а на выходе арифметического олока 7 результат a(k ) вычитания операнда а5{П) и операнда а (4). Следовательно, операнд а (4 ) запишется в блок 4 памяти по адресу 100.

На выходе вычитателя 37 в этом такте знаковый разряд имеет нулевое значение, которое является признаком отрицательной разности адреса 000 операнда а (П ) и кода 010 S . Это нулевое значение, поступая на вход элемента И 29, не изменит состояния его выходов, а поступая на вход элемента И 32 изменит состояние его выхода на нулевое. Состояние выхода элемента И 33 не изменяется. Таким образом, на управляющих входах мультиплексоров 36 и 3 присутствует код 00 а на управляющем входе блока 5 памяти -единичное значение, которое не разрешает запись в блок 5 памяти операнда а.,{0;. На этом третий такт работы устройства заканчивается.

В четвертом такте первого шага с приходом третьего тактового импульса код 100 на выходе мультиплексоров 23.1-23оЗ заносится в регистр 22 а счетчик 21 тактовых импульсов изменит свое состояние на 0011. Код на выходе мультиплексоров 23.1-23.3 изменит свое значение на 000. Состояние управляющих входов мультиплексоров 35, 2 и 6 и управляющего блока k памяти не изменится. На выходе арифметического блока 7 в этом такте получаем результат суммирования а(0) операнда 8(0) и а|( . Операнд а(0 ) запишется в блок А памяти по адресу 000. Четвертый такт каждого шага отведен для записи в блок памяти входного данного. Если входное данное (() ) поступило на вход устройства до четвертого такта, то первый синхроимпульс (СИ) с шины 17 изменит

состояние счетчика 5 на 110, а состояние триггера 27 первым СИ изменяется на единичное. В этом случае на управляющих входах мультиплексоров 36

5 и 3 присутствует.код 01, который получается за счет всех единиц на входе элемента И 33 и нулевого значения на входе элемента И 32. Код знакового разряда вычитателя 37 на формирование управляющих сигналов мультиплексоров 36 .и 3 в четвертом такте не влияет. На управляющем входе бло-ка 5 памяти присутствует значение. Код 01. разрешает прохождение через

5 мультиплексор ЗЬ адреса входного данного, сформированного на счетчике 5, а через мультиплексор 3 самого данного на вход блока 5 памяти. Если входное данное не поступило, то выполняется

0 холостой такт считывания из блока 5 памяти.

На этом четвертый такт и первый шаг работы устройства заканчивается. Последущие три шага работы устройства аналогичны первому. После выполнения четвертого шага счетчик 21 тактовых импульсов приходит в исходное состояние 0000, а сигнал переноса с его выхода изменяет состояние счетчика 24 итераций на 01. Это состояние,

поступая на управляюи1ие входы мультиплексоров 23.1-23.3, изменяет законы формирования адресов записи и считывания для выполнения второй итерации

, алгоритма (последовательность формирования адресов видна из графа алгоритма на фиг. . ), а также, поступая на стробируемый дешифратор 25 первой итерации, изменяет состояние его выхода на нулевое, тем самым запрещая формирование на элементах И 32, 33 кода 10, который обеспечивает запись в блок 5 памяти данных с выхода блока 4 памяти.

Выполнение третьей итерации алгоритма аналогично.

Когда заканчивается выполнение алгоритма быстрого преобразования Фурье, сигнал с выхода переполнения 0 счетчика 24 итераций поступает на вход элемента И 26.

Если все входные данные, участвующие в формировании массива (8), поступили на вход устройства, то 5 счетчик 45 находится в состоянии 111. :Это состояние, поступая на элемент ;И-НЕ 46, изменяет состояние его выхода на нулевое, которое в свою очередь

изменяет состояние триггера 27 на нулевое. Единичное значение инверсного выхода триггера 27 поступает на вход элемента И 2б, а нулевое значение с прямого выхода триггера 27 по- s ступает на вход элементов И 33 запрещая формирование управляющего кода для записи входных данных в блок 5 памяти. Если окончено выполнение алгоритма и формирование массива М (NJio то сигнал с выхода элемента И 26 изменяет состояние триггера 28 переключения блоков памяти на противоположное, тем самым подключая блок 5 памяти для вычисления алгоритма, а блок 5 памяти для формирования массива (N).

Работа устройства повторяется аналогично описанной выше.

Если требуется вычислить циклический спектр массивов, то состояние входа 18, управляюи его режимами работы, изменяется на нулевоео запрещая формирование на выходе дешифратора 25 единичного значения, а следовательно, и управляющих кодов для записи данных массива 1C (8) . при формировании массива (8). На входе 19 при вычислении циклического спектра присутствует код 111.

Из приведенного примера видно, что изменяя состояния входов управ«ляюишх режимами работы, можно вычислить скользящий с произвольный t и , мгновенный спектры сигнале.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА, coAepwaujee первый Ц5лок памяти, арифметический блок, блок синхронизации, первый и второй блоки формирования адреса, первый выход блока синхронизации соединён с входом первого блока формиро вания адреса, выход которого подключен к первому входу первого блока памяти, второй вход которого соединен с вторым выходом блока синхронизации, третий выход блока синхронизации соединен с входом второго блока формирования адреса, о т л ичающееся тем, что, с целью расширения фукнциональных возможностей за счет вык/вочения скользящего спектра с ПРОИЗВОЛЬНЫМ коэффициентом смещения и уменьшения аппаратурных затрат,оно содержит второй блок памяти и три мультиплексора, четвертый выход блока синхронизации соединен с управляющим выходом первого мультиплексора , выход которого подключен к третьему входу первого блока памяти, выход которого соединен с первыми входами второго и третьего мультиплексоров, управляющие входы которых подключены соответственно к пятому и шестому выходам блока синхронизации седьмой выход которого соединен с первым входом второго блока памяти, второй вход KdToporo подключен к выходу второго блока формирования адреса, выход арифметического блока подключен § к первому входу первого мультиплексо(Л ра и второму входу второго мультиплек сора, третий вход которого объединен с .вторым входом первого мультиплексора и является входом устройства, вход - 9 арифметического блока соединен с выхо дом третьего мультиплексора, выход второго .мультиплексора соединен с Q ГО третьим входом второго блока памяти, выход которого подк/точен к второму входу третьего мультиплексора и Третьему входу первого мультиплексора, САЭ выход которого соединен с третьим 00 входом первого блока памяти, первый вход блока синхронизации является входом задания кода числа устройства, второй вход - синхронизирующим входом устройства, третий вход входом задания признака устройства, а четвертый вход - входом установки начального адреса устройства.

Фаг. /

/ V л ,.W

Л уК

/ /

.

w

a//О

) aj/)

;ь,

.

JY2

.

ш

-

IV/

ч

€

Авторы

Даты

1983-07-07—Публикация

1981-10-26—Подача