1

Изобретение относится к вычислительной технике, предназначено для вьтисления скользящего спектра сигналов и может быть использовано в анализаторах спектра, работающих в реальном масштабе времени при цифровой обработке сейсмических и других сигналов.

Целью изобретения является повышения быстродействия устройства при вычислении мгновенного спектра сигналов,

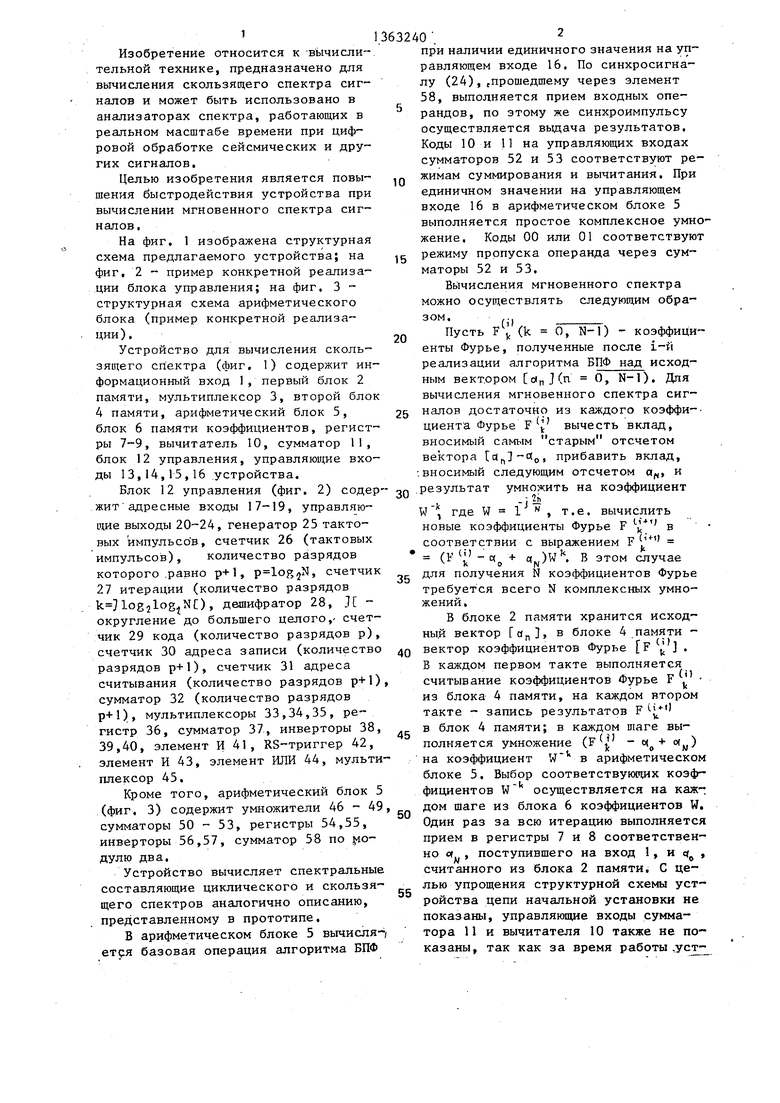

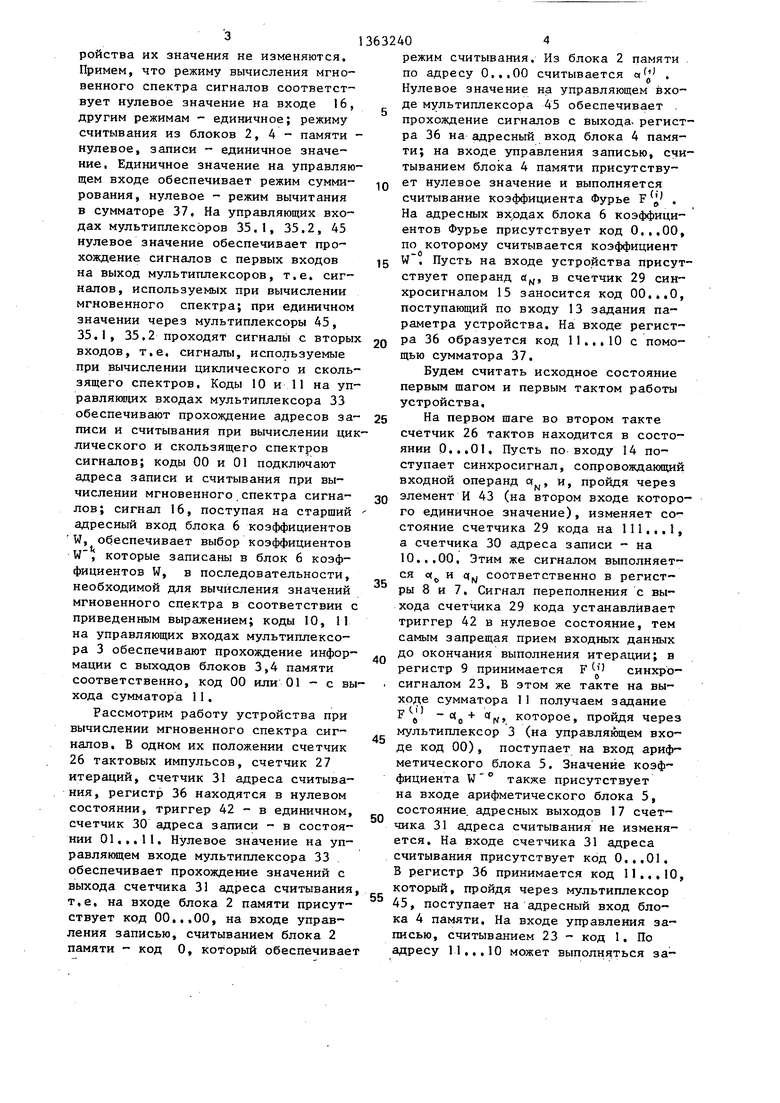

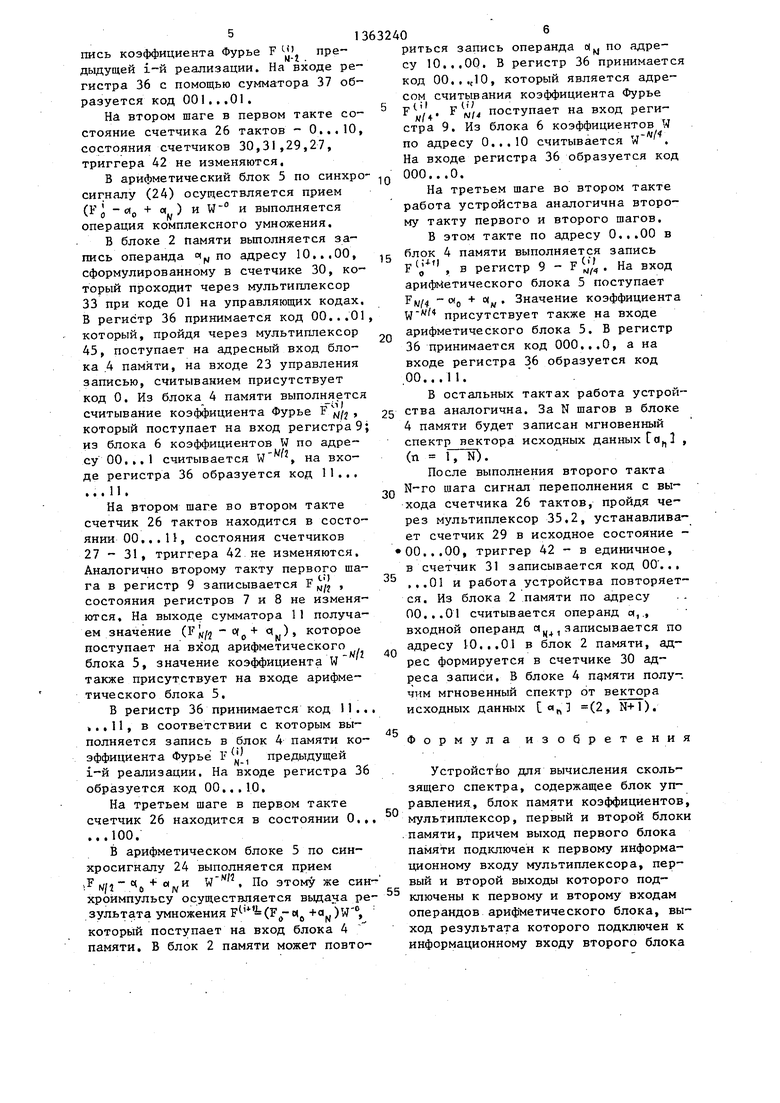

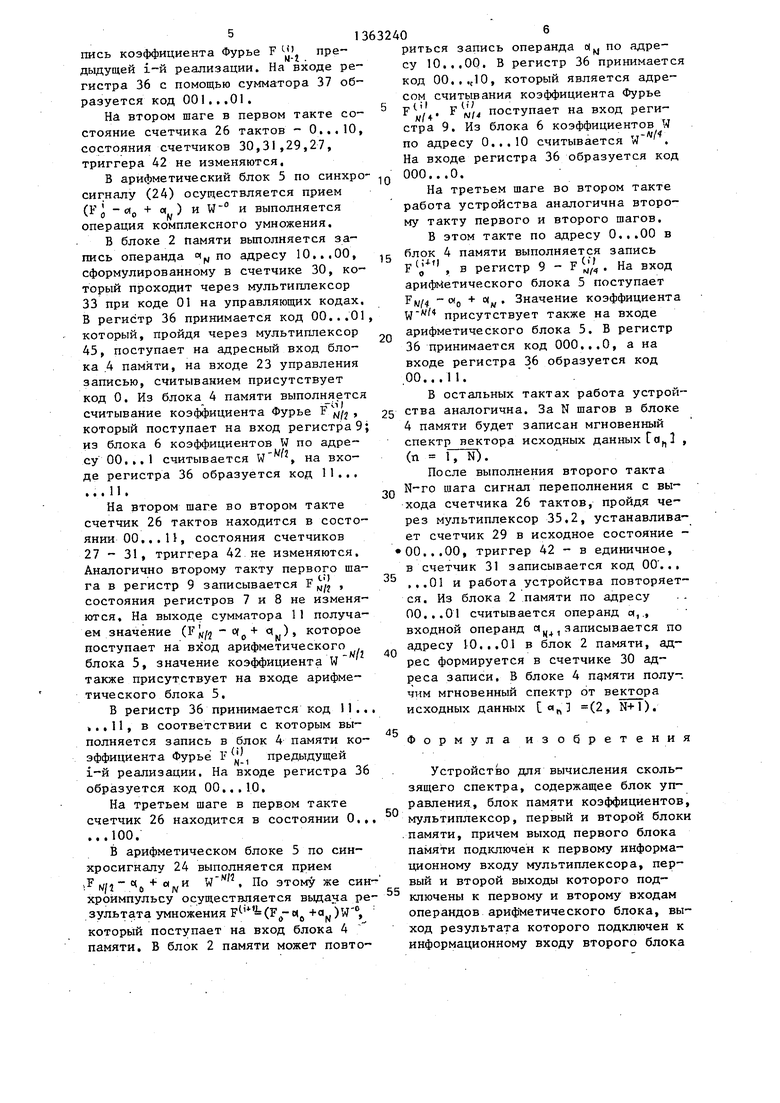

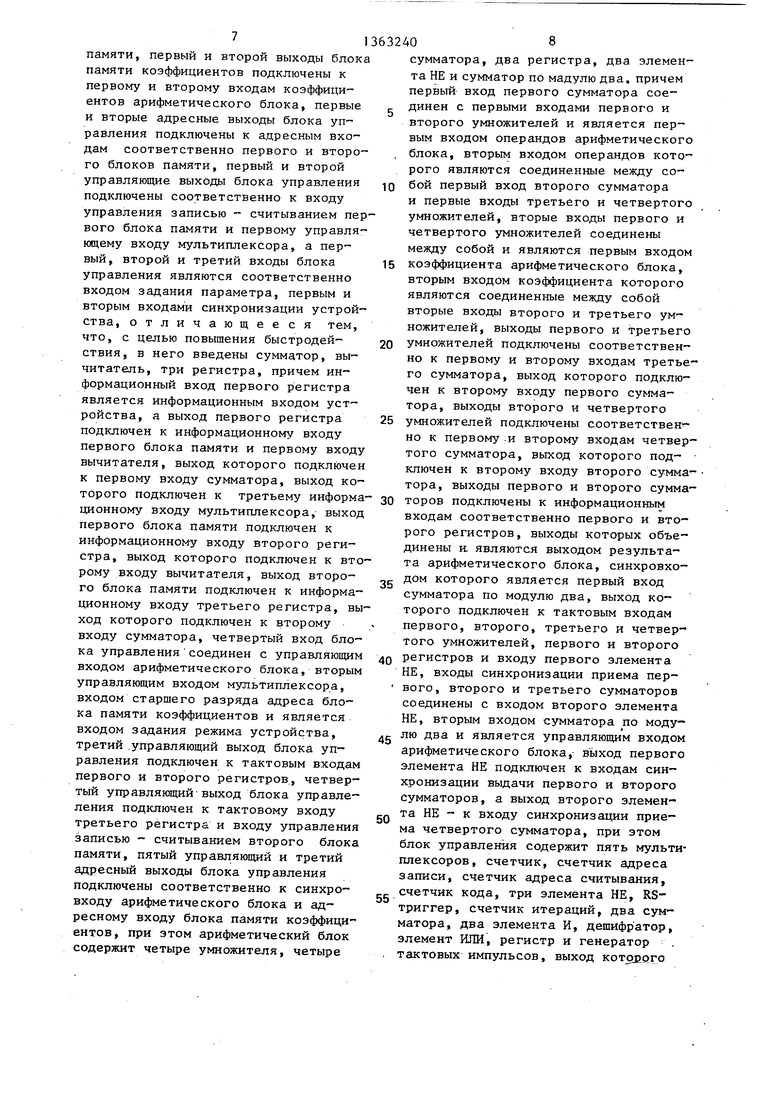

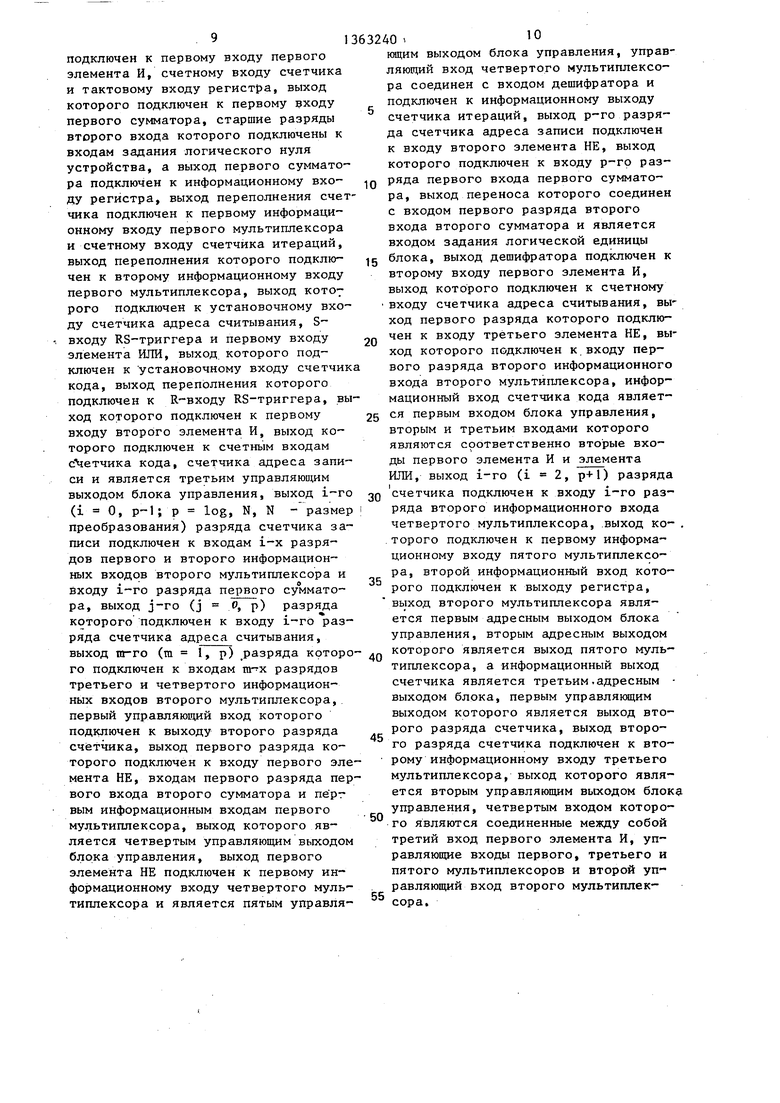

На фиг, 1 изображена структурная схема предлагаемого устройства; на фиг, 2 - пример конкретной реализации блока управления; на фиг, 3 - структурная схема арифметического блока (пример конкретной реализации).

Устройство для вычисления скользящего спектра (фиг, 1) содержит ин- формационнь й вход 1 , первый блок 2 памяти, мультиплексор 3, второй блок 4 памяти, арифметический блок 5, блок 6 памяти коэффициентов, регистры 7-9, вычитатель 10, сумматор 11, блок 12 управления, управляющие входы 13,14,15,16 устройства.

Блок 12 управления (фиг, 2) содер житадресные входы 17-19, управляющие выходы 20-24, генератор 25 тактовых импульсо в, счетчик 26 (тактовых импульсов), количество разрядов которого .равно р+1, p log2N, счетчик 27 итерации (количество разрядов k }log2log NC), детпифратор 28, } - округление до большего целого,- счетчик 29 кода (количество разрядов р), счетчик 30 адреса записи (количество разрядов р+1), счетчик 31 адреса считывания (количество разрядов р+1) сумматор 32 (количество разрядов р+1), мультиплексоры 33,34,35, регистр 36, сумматор 37, инверторы 38, 39,40, элемент И 41, RS-триггер 42, элемент И 43, элемент ИЛИ 44, мультиплексор 45,

Кроме того, арифметический блок 5 (фиг, 3) содержит умножители 46 - 49 сумматоры 50 - 53, регистры 54,55, инверторы 56,57, сумматор 58 по jio- дулю два.

Устройство вычисляет спектральные составляющие циклического и скользящего спектров аналогично описанию, представленному в прототипе,

В арифметическом блоке 5 вычисляетря базовая операция алгоритма БПФ

63240;2

при наличии единичного значения на управляющем входе 16, По синхросигналу (24), прошедшему через элемент 58, выполняется прием входных операндов, по зтому же синхроимпульсу осуществляется выдача результатов. Коды 10 и 11 на управляющих входах сумматоров 52 и 53 соответствуют ре.„ жимам суммирования и вычитания. При единичном значении на управляющем входе 16 в арифметическом блоке 5 выполняется простое комплексное умножение. Коды 00 или 01 соответствуют

«с режиму пропуска операнда через сумматоры 52 и 53,

Вычисления мгновенного спектра можно осуществлять следующим образом, .j

2Q Пусть F (k 0, N-1) - коэффици™ енты Фурье, полученные после i-й реализации алгоритма БПФ над исходным вектором cipj(n О, N-1), Для вычисления мгновенного спектра сиг25 налов достаточно из каждого коэффи-циента Фурье F вычесть вклад,

вносимый самым старым отсчетом

вектора tc(-c(p, прибавить вклад,

: вносимый следующим отсчетом а,,, и

-п результат умножить на коэффициент

5U. 9

J

W, где W 1 , т.е, вычислить новые коэффициенты Фурье F в соответствии с выражением F (У (О ц . ) в этом случае

25 для получения N коэффициентов Фурье требуется всего N комплексных умножений,

В блоке 2 памяти хранится исходный вектор Г Of,, в блоке 4 памяти 40 вектор коэффициентов Фурье F j , В каждом первом такте выполняется считывание коэффициентов Фурье F j| из блока 4 памяти, на Кс1ждом втором такте - запись результатов F в блок 4 памяти; в каждом шаге выполняется умножение ( м на коэффициент W в арифметическом блоке 5, Выбор соответствующих коэффициентов W осуществляется на каж-:

., дом шаге из блока 6 коэффициентов W. 50

Один раз за всю итерацию выполняется

прием в регистры 7 и 8 соответственно Of , поступившего на вход 1, и с , считанного из блока 2 памяти, С це- лью упрощения структурной схемы устройства цепи начальной установки не показаны, управляющие входы сумматора П и вычитателя 10 также не показаны, так как за время работы .устройства их значения не изменяются. Примем, что режиму вычисления мгновенного спектра сигналов соответствует нулевое значение на входе 16, другим режимам - единичное; режиму считывания из блоков 2, 4 - памяти - нулевое, записи - единичное значение, Единичное значение на управляющем входе обеспечивает режим суммирования, нулевое - режим вычитания в сумматоре 37, На управляющих входах мультиплексоров 35.1, 35.2, 45 нулевое значение обеспечивает прохождение сигналов с первых входов на выход мультиплексоров, т.е. сигналов, используемых при вычислении мгновенного спектра; при единичном значении через мультиплексоры 45, 35.1, 35.2 проходят сигналы с вторых входов, т.е. сигналы, используемые при вычислении циклического и скользящего спектров. Коды 10 и 11 на управляющих входах мультиплексора 33 обеспечивают прохождение адресов записи и считывания при вычислении циклического и скользящего спектров сигналов; коды 00 и 01 подключают адреса записи и считывания при вычислении мгновенного спектра сигналов; сигнал 16, поступая на старший адресный вход блока 6 коэффициентов W, обеспечивает выбор козффициентов W, которые записаны в блок 6 коэффициентов W, в последовательности, необходимой для вычисления значений мгновенного спектра в соответствии с приведенным выражением; коды 10, 11 на управляющих входах мультиплексора 3 обеспечивают прохождение информации с выходов блоков 3,4 памяти соответственно, код 00 или 01 - с выхода сумматора 11.

Рассмотрим работу устройства при вычислении мгновенного спектра сигналов. В одном их положении счетчик 26 тактовых импульсов, счетчик 27 итераций, счетчик 31 адреса считывания, регистр 36 находятся в нулевом состоянии, триггер 42 - в единичном, счетчик 30 адреса записи - в состоянии 01... 11. Нулевое значение на управляющем входе мультиплексора 33 обеспечивает прохождение значений с выхода счетчика 31 адреса считывания т.е. на входе блока 2 памяти присутствует код 00...00, на входе управления записью, считыванием блока 2 памяти - код О, который обеспечивае

3632404

режим считывания. Из

блока 2 памяти

10

15

20

25

30

35

40

45

50

55

по адресу 0...00 считывается a j . Нулевое значение на управляющем входе мультиплексора 45 обеспечивает прохождение сигналов с выхода, регистра 36 на адресный вход блока 4 памяти; на входе управления записью, считыванием блока 4 памяти присутствует нулевое значение и выполняется считывание коэффициента Фурье F . На адресных входах блока 6 коэффициентов Фурье присутствует код 0,..00, по которому считывается коэффициент W. Пусть на входе устройства присутствует операнд а,, в счетчик 29 синхросигналом 15 заносится код 00...О, поступающий по входу 13 задания параметра устройства. На входе регистра 36 образуется код 11 ... 10 с помощью сумматора 37.

Будем считать исходное состояние первым шагом и первым тактом работы устройства.

На первом шаге во втором такте счетчик 26 тактов находится в состоянии 0...01. Пусть по входу 14 поступает синхросигнал, сопровождающий входной операнд о(, и, пройдя через элемент И 43 (на втором входе которого единичное значение), изменяет состояние счетчика 29 кода на 111..., а счетчика 30 адреса записи - на 10...00. Этим же сигналом выполняется « и of| соответственно в регистры 8 и 7. Сигнал переполнения с выхода счетчика 29 кода устанавливает триггер 42 в нулевое состояние, тем самым запрещая прием входных данных до окончания выполнения итерации; в регистр 9 принимается F J синхросигналом 23. В этом же такте на выходе сумматора 11 получаем задание в которое, пройдя через мультиплексор 3 (на управляющем входе код 00), поступает на вход арифметического блока 5. Значение коэффициента V ° также присутствует на входе арифметического блока 5, состояние, адресных выходов 17 счетчика 31 адреса считывания не изменяется. На входе счетчика 31 адреса считывания присутствует код 0...01. В регистр 36 принимается код 11 ... 10, который, пройдя через мультиплексор 45, поступает на адресный вход блока 4 памяти. На входе управления записью, считыванием 23 - код I. По адресу 11...10 может выполняться запись коэффициента Фурье F предыдущей i-й реализации. На входе регистра 36 с помощью сумматора 37 образуется код О01..,01,

На втором шаге в первом такте состояние счетчика 26 тактов - 0...10, состояния счетчиков 30,31,29,27, триггера 42 не изменяются,

В арифметический блок 5 по синхросигналу (24) осуществляется прием

(V о - о

и выполняется

, ., , с,) и W-° операция комплексного умножения.

В блоке 2 памяти вьтолняется запись операнда °if по адресу 10...00, сформулированному в счетчике 30, который проходит через мультиплексор 33 при коде 01 на управляющих кодах В регистр 36 принимается код 00...0 который, пройдя через мультиплексор 45, поступает на адресный вход блока 4 памяти, на входе 23 управления записью, считыванием присутствует код 0. Из блока 4 памяти выполн яется считывание коэффициента Фурье F ii/j , который поступает на вход регистра 9 из блока 6 коэффициентов W по адре36

f-Wf2 образуется код

су 00,.. считывается W , на вхоП

м/г изменяде регистра ..,11.

На втором шаге во втором такте счетчик 26 тактов находится в состоянии 00... И, состояния счетчиков 27-31, триггера 42 не изменяются. Аналогично второму такту первого шага в регистр 9 записывается F состояния регистров 7 и 8 не ются. На выходе сумматора 11 получаем значение (Hii 0(5+ .,) которое поступает на вход арифметического блока 5, значение коэффициента W также присутствует на входе арифметического блока 5.

В регистр 36 принимается код 11 .. ... 11 , в соответствии с которым выполняется запись в блок 4 памяти коэффициента Фурье 1

N-1

предыдущей

i-и реализации. На входе регистра 36 образуется код 00...10.

На третьем шаге в первом такте счетчик 26 находится в состоянии О,,. ...100.

В арифметическом блоке 5 по синхросигналу 24 выполняется прием iF.j- с( 4- . По этому же синхроймпульсу осуществляется выдача ре- зульт та умножения (( + n()W который поступает на вход блока 4 памяти, В блок 2 памяти может повто

риться запись операнда « по адресу 10...00. В регистр 36 принимается код O0..,tl0, который является адресом считывания коэффициента Фурье F V/4 N/4 поступает на вход регистра 9. Из блока 6 коэффициентов W по адресу 0...10 считывается . На входе регистра 36 образуется код 000...О.

На третьем шаге во втором такте работа устройства аналогична второму такту первого и второго шагов.

В этом такте по адресу 0...00 в

5

блок 4 памяти выполняется в регистр 9 - F

)

0

5

0

5

0

запись

л t ft- у J А KjM на вход арифметического блока 5 поступает PW/ ° w Значение коэффициента присутствует также на входе арифметического блока 5. В регистр 36 принимается код 000...О, а на входе регистра 36 образуется код .00... 11.

В остальных тактах работа устройства аналогична. За N шагов в блоке 4 памяти будет записан мгновенный спектр вектора исходных данных , (п 1, N).

После выполнения второго такта N-ro шага сигнал переполнения с выхода счетчика 26 тактов, пройдя через мультиплексор 35.2, устанавливает счетчик 29 в исходное состояние - 00...00, триггер 42 - в единичное, в счетчик 31 записывается код 00.., ...01 и работа устройства повторяется. Из блока 2 памяти по адресу .- 00...01 считывается операнд а,., входной операнд а записывается по адресу Ю...01 в блок 2 памяти, адрес формируется в счетчике 30 адреса записи. В блоке 4 памяти полу-. чим мгновенный спектр от вектора исходных данных C«f, (2, N+1).

Формула изобретения

Устройство для вычисления скользящего спектра, содержащее блок управления, блок памяти коэффициентов, мультиплексор, первый и второй блоки памяти, причем выход первого блока памяти подключен к первому информационному входу мультиплексора, первый и второй выходы которого подключены к первому и второму входам операндов арифметического блока, выход результата которого подключен к информационному входу второго блока

памяти, первый и второй выходы блока памяти коэффициентов подключены к первому и второму входам коэффициентов арифметического блока, первые и вторые адресные выходы блока управления подключены к адресным входам соответственно первого и второго блоков памяти, первый и второй управляющие выходы блока управления подключены соответственно к входу управления записью - считыванием первого блока памяти и первому управляющему входу мультиплексора, а первый, второй и третий входы блока управления являются соответственно входом задания параметра, первым и вторым входами синхронизации устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены сумматор, вы- читатель, три регистра, причем информационный вход первого регистра является информационным входом устройства, а выход первого регистра подключен к информационному входу первого блока памяти и первому входу вычитателя, выход которого подключен к первому входу сумматора, выход которого подключен к третьему информационному входу мультиплексора, выход первого блока памяти подключен к информационному входу второго регистра, выход которого подключен к второму входу вычитателя, выход второго блока памяти подключен к информационному входу третьего регистра, выход которого подключен к второму входу сумматора, четвертый вход блока управления соединен с управляющим входом арифметического блока, вторым управляющим входом мультиплексора, входом старшего разряда адреса блока памяти коэффициентов и является входом задания режима устройства, третий .управляющий выход блока управления подключен к тактовым входам первого и второго регистров., четвертый управляющий-выход блока управле- ления подключен к тактовому входу третьего регистра и входу управления записью - считыванием второго блока памяти, пятый управляющий и третий адресный выходы блока управления подключены соответственно к синхро- входу арифметического блока и адресному входу блока памяти коэффициентов, при этом арифметический блок содержит четыре умножителя, четыре

0

5

0

5

0

сумматора, два регистра, два элемента НЕ и сумматор по мадулю два. причем первый вход первого сумматора соединен с первыми входами первого и второго умножителей и является первым входом операндов арифметического блока, вторьш входом операндов которого являются соединенные между собой первый вход второго сумматора и первые входы третьего и четвертого умножителей, вторые входы первого и четвертого умножителей соединены между собой и являются первым входом коэффициента арифметического блока, вторым входом коэффициента которого являются соединенные между собой вторые входы второго и третьего умножителей, выходы первого и третьего умножителей подключены соответственно к первому и второму входам третьего сумматора, выход которого подключен к второму входу первого сумматора, выходы второго и четвертого умножителей подключены соответствен но к первому .и второму входам четвертого сумматора, выход которого подключен к второму входу второго сумматора, выходы первого и второго сумматоров подключены к информационным входам соответственно первого и второго регистров, выходы которых объединены и. являются выходом результата арифметического блока, синхровхо- дом которого является первый вход сумматора по модулю два, выход которого подключен к тактовым входам первого, второго, третьего и четвертого умножителей, первого и второго регистров и входу первого элемента НЕ, входы синхронизации приема первого, второго и третьего сумматоров соединены с входом второго элемента НЕ, вторым входом сумматора по модулю два и является управляющим входом арифметического блока, выход первого элемента НЕ подключен к входам синхронизации выдачи первого и второго сумматоров, а выход второго элемента НЕ - к входу синхронизации приема четвертого сумматора, при этом блок управления содержит пять мультиплексоров, счетчик, счетчик адреса записи, счетчик адреса считывания, счетчик кода, три элемента НЕ, RS- триггер, счетчик итераций, два сумматора, два элемента И, дешифратор, элемент ИЛИ, регистр и генератор тактовых импульсов, выход KOTpjjpro

0

5

0

5

подключен к первому входу первого элемента И, счетному входу счетчика и тактовому входу регистра, выход которого подключен к первому входу первого сумматора, старшие разряды второго входа которого подключены к входам задания логического нуля устройства, а выход первого сумматора подключен к информационному входу регистра, выход переполнения счетчика подключен к первому информационному входу первого мультиплексора и счетному входу счетчика итераций, выход переполнения которого подключен к второму информационному входу первого мультиплексора, выход кото7 рого подключен к установочному входу счетчика адреса считывания, S- входу RS-триггера и первому входу элемента ИЛИ, выход которого подключен к установочному входу счетчик кода, выход переполнения которого подключен к R-входу RS-триггера, выход которого подключен к первому входу второго элемента И, выход которого подключен к счетным входам с етчика кода, счетчика адреса записи и является третьим управляюпщм выходом блока управления, выход i-ro (i О, р-1; р log, N, N - размер преобразования) разряда счетчика записи подключен к входам i-x разрядов первого и второго информационных входов второго мультиплексора и входу i-ro разряда первого су ммато- ра, выход j-ro (j о, р) разряда которого подключен к входу i-ro раз- ряда счетчика адреса считывания, выход та-го (т 1, р) разряда которого подключен к входам разрядов третьего и четвертого информационных входов второго мультиплексора, первый управляющий вход которого подключен к выходу второго разряда счетчика, выход первого разряда которого подключен к входу первого элемента НЕ, входам первого разряда первого входа второго сумматора и пёрг вым информационным входам первого мультиплексора, выход которого является четвертым управляющим выходом блока управления, выход первого элемента НЕ подключен к первому информационному входу четвертого мультиплексора и является пятым управляа- 10

363240 10

ющим выходом блока управления, управляющий вход четвертого мультиплексора соединен с входом дешифратора и подключен к информационному выходу счетчика итераций, выход р-го разряда счетчика адреса записи подключен к входу второго элемента НЕ, выход которого подключен к входу р-го разряда первого входа первого сумматора, выход переноса которого соединен с входом первого разряда второго входа второго сумматора и является входом задания логической единицы

g блока, выход дешифратора подключен к второму входу первого элемента И, выход которого подключен к счетному входу счетчика адреса считывания, вы- ход первого разряда которого подклю-

J,. чен к входу третьего злемента НЕ, выход которого подключен к.входу первого разряда второго информационного входа второго мультиплексора, информационный вход счетчика кода являет-

25 ся первым входом блока управления, вторым и третьим входами которого являются соответственно вторые входы первого элемента И и элемента ИЛИ, выход i-ro (i

30

35

40

45

50

55

2, р+1) разряда счетчика подключен к входу i-ro разряда второго информационного входа четвертого мультиплексора, ,выход ко- . торого подключен к первому информационному входу пятого мультиплексора, второй информационный вход которого подключен к выходу регистра, выход второго мультиплексора является первым адресным выходом блока управления, вторым адресным выходом которого является выход пятого мультиплексора, а информационный выход счетчика является третьим,адресным выходом блока, первым управлякяцим выходом которого является выход второго разряда счетчика, выход второго разряда счетчика подключен к второму информационному входу третьего мультиплексора, выход которого является вторым управляющим выходом блока управления, четвертым входом которого являются соединенные между собой третий вход первого элемента И, управляющие входы первого, третьего и пятого мультиплексоров и второй управляющий вход второго мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

Изобретение относится к вычис- лительной технике, предназначено для вычисления скользящего спектра сигналов и может быть использовано в анализаторах спектра, работающих в реальном масштабе времени, при цифровой обработке сейсмических и других сигналов. Цель изобретения - по- вьпиение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят информационный вход 1, блок памяти 2, мультиплексор 3, блок памяти 4, арифметический блок 5, блок памяти 6 коэффициентов, регистры 7,8,9, вычита- тель 10, сумматор 11, блок управления 12, управляющие входы 13 - 16. 3 ил. (Л 00 О5 00 ю 4 flut.f .

Составитель А. Баранов Редактор А.Маковская ,Техред М.ДиДЫККорректор А.

, 4m,fi,fmf,fft яв тг ,fmerf f fimmm if f,

Заказ 6364/42 Тираж 671Подписное

ВНИИПИ Государственного ко14итета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-19—Подача