Изобретение Относится к области автоматики, вычислительной и измерительной техники и может быть использовано в приборах определения характеристик случайных последовательностей и устройствах управления по сигналам среднеквадратичной ошибки.

Для определения квадрата двоичного числа и дальнейшего усреднения для получения оценки дисперсии в известном устройстве ислользуют арифметическое устройство (АУ) универсального типа, включающее два регистра сдвига., сумматор « сложную схему упразления, и запоминающее уст2ойство (ЗУ) для хранения Л чисел для их усреднения.

Однако известное устройство имеет существенные недостатки: -если накопление суммы

N

2Лг производится дополнительным отдельным сумматором, то ЗУ не требуется, но оценки могут быть получены только после приема каждых N чисел, т. е. после накопления суммы;

если значения оценки необходимо получать каждый раз с приходом очередного числа, то известные устройства требуют наличия ЗУ для хранения N предыдущих чисел, что значительно усложняет аппаратуру, схемы управления и уменьшает быстродействие;

- универсальное АУ весьма.сложно, имеет сложные схемы управления, его возможности

полностью не используются при решении частиой сформулированной задачи.

Цель изобретения заключается в исключении ЗУ и упрощении всей схемы устройства, обладающего воз.можностью определять оценки дисперсии одновременно с приходом каждого числа последовательности.

В предлагаемом устройстве эта цель достигается тем, что оно содержит два сумматора; выход первого сумматора подключен к первому входу первого вентиля, ко второму входу которого подключен первый выход блока управления, а выход первого вентиля соединей со входом второго сумматора; первый выход второго сумматора подключен к выходной клемме устройства, а второй - к первому входу второго вентиля, второй вход которого соединен со вторым выходом блока управления, а выход - с первым входом схемы ко второму входу схемы «ИЛИ подключен выход третьего вентиля, первый вход которого соединен с третьим выходом блока управления, а второй - с выходом логического блока, ко входу которого подключен выход приемного регистра; четвертый выход блока управления соединен с первым входом четвертого вентиля, ко второму входу которого подключен выход приемного регистра, выход чет

вертого вентиля соединен с третьим входом

схемы «ИЛИ, выход которой подключен ко входу первого сумматора.

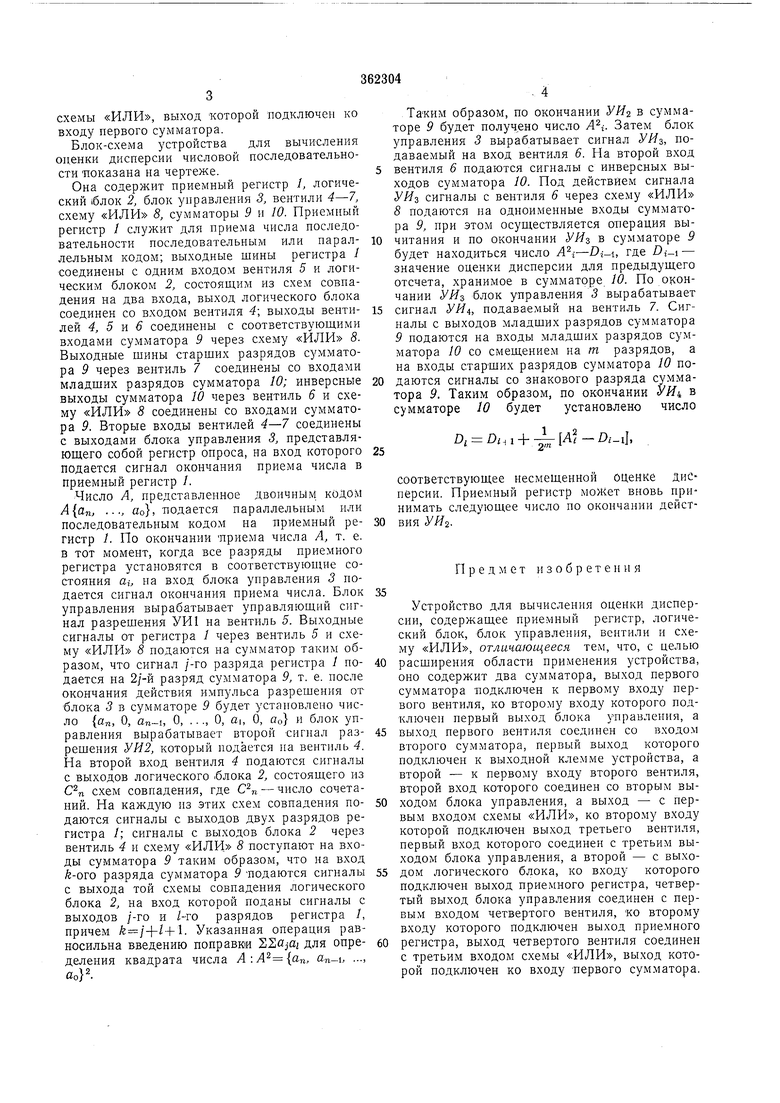

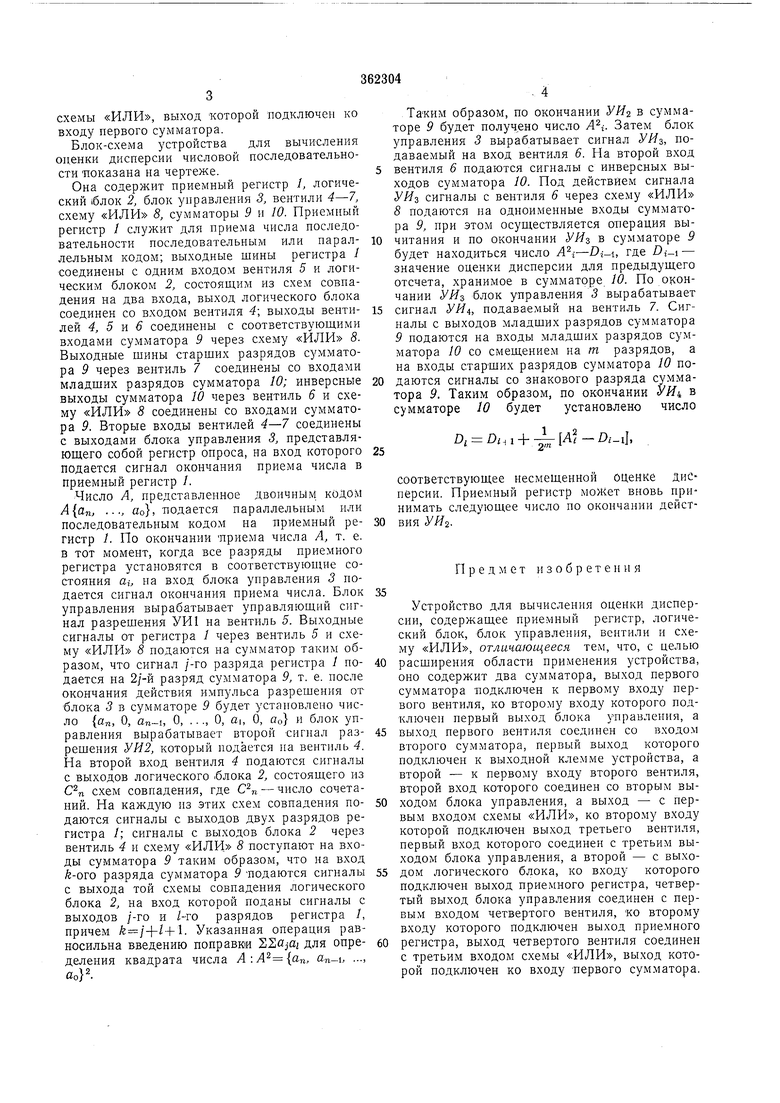

Блок-схема устройства для вычисления опенки дисперсии числовой последовательности показана на чертеже.

Она содержит приемный регистр /, логический блок 2, блок управления 3, вентили 4-7, схему «ИЛИ 8, сумматоры 9 и 10. Приемный регистр / служит для приема числа последовательности последовательным или параллельным кодом; выходные шины регистра 1 соединены с одним входом вентиля 5 и логическим блоком 2, состоящим из схем совпадения на два входа, выход логического блока соединен со входом вентиля 4; выходы вентилей 4, 5 и 6 соединены с соответствующими входами сумматора 9 через схему «ИЛИ 8. Выходные щины старщих разрядов сумматора 9 через вентиль 7 соединены со входами младщих разрядов сумматора 10; инверсные выходы сумматора 10 через вентиль 6 и схему «ИЛИ 8 соединены со входами сумматора Р. Вторые входы вентилей 4-7 соединены с выходами блока управления 3, представляющего собой регистр опроса, на вход которого подается сигнал окончания приема числа в приемный регистр /.

Число А, представленное двоичным кодом А{ап, . ., йо}, подается параллельным или последовательным кодом на приемный регистр /. По окончании приема числа А, т. е. в тот момент, когда все разряды приемного регистра установятся в соответствующие состояния ui, на вход блока управления 3 подается сигнал окончания приема числа. Блок управления вырабатывает управляющий сигнал разрещения УИ1 на вентиль 5. Выходные сигналы от регистра / через вентиль 5 и схему «ИЛИ 8 подаются на сумматор таким образом, что сигнал /-ГО разряда регистра 1 подается на 2/-Й разряд сумматора 9, т. е. после окончания действия импульса разрешения от блока 3 в сумматоре 9 будет установлено число (ип. О, fln-i. О, ..., О, fli. О, ао} и блок управления вырабатывает второй сигнал разрешения УИ2, который подается на вентиль 4. Па второй вход вентиля 4 подаются сигналы с выходов логического блока 2, состоящего из схем совпадения, где - число сочетаний. На каждую из этих схем совпадения подаются сигналы с выходов двух разрядов регистра /; сигналы с выходов блока 2 через вентиль 4 и схему «ИЛИ 8 поступают на входы сумматора 9 таким образом, что на вход fe-oro разряда сумматора 9 -подаются сигналы с выхода той схемы совпадения логического блока 2, на вход которой поданы сигналы с выходов /-ГО и 1-го разрядов регистра /, причем . Указанная операция равносильна введению поправки S2«ja; для определения квадрата числа , un-i, ...,

йо}2.

Таким образом, но окончании УИ в сумматоре 9 будет получено число . Затем блок управления 3 вырабатывает сигнал УИз, подаваемый на вход вентиля 6. Иа второй вход вентиля 6 подаются сигналы с инверсных выходов сумматора 10. Под действием сигнала УЯз сигналы с вентиля 6 через схему «ИЛИ

8подаются па одноименные входы сумматора Я при этом осуществляется операция вычитания и по окончании УЯз в сумматоре 9 будет находиться число Л г-Di-i, где Dt-i - значение оценки дисперсии для предыдущего отсчета, хранимое в сумматоре 70. По окончании УЯз блок управления 3 вырабатывает

сигнал УЯ4, подаваемый на вентиль 7. Сигналы с выходов младщих разрядов сумматора

9подаются на входы младщих разрядов сумматора 10 со смещением на т разрядов, а на входы старщих разрядов сумматора W подаются сигналы со знакового разряда сумматора 9. Таким образом, по окончании УИ/, в сумматоре 10 будет установлено число

D, D,,,4--ilA-A--iI,

соответствующее несмещенной оценке дисперсии. Приемный регистр может вновь принимать следующее число по окончании дейст30 ВИЯ УЯ2.

Предмет и з о б р е т е н и я

Устройство для вычисления оценки дисперсии, содержащее приемный регистр, логический блок, блок управления, вентили и схему «ИЛИ, отличающееся тем, что, с целью

расщирения области применения устройства, оно содержит два сумматора, выход первого сумматора подключен к первому входу первого вентиля, ко второму входу которого подключен первый выход блока управления, а

выход первого вентиля соединен со входом второго сумматора, первый выход которого подключен к выходной клемме устройства, а второй - к первому входу второго вентиля, второй вход которого соединен со вторым выходом блока управления, а выход - с первым входом схемы «ИЛИ, ко второму входу которой подключен выход третьего вентиля, первый вход которого соединен с третьим выходом блока управления, а второй - с выходом логического блока, ко входу которого подключен выход приемного регистра, четвертый выход блока управления соединен с первым входом четвертого вентиля, КО второму входу которого подключен выход приемного

регистра, выход четвертого вентиля соединен с третьим входом схемы «ИЛИ, выход которой подключен ко входу первого сумматора.

гт

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТАТИСТИЧЕСКИХ ДАННЫХ | 1970 |

|

SU272674A1 |

| ППРППЮГ^М'^Я | 1973 |

|

SU362298A1 |

| ВЕРОЯТНОСТНЫЙ АНАЛИЗАТОР | 1972 |

|

SU342191A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| Цифровой определитель дисперсии | 1978 |

|

SU767772A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1095190A1 |

,

Авторы

Даты

1973-01-01—Публикация