пересчета, а выход - с нулевыми входами второго и четвертого триггеров, единичный вход которого соединен с выхоДом первого элемента ИЛИ, а выход с входом первого формирователя коротких импульсов, при этом третий вход второго ключа соединен с выходом элемента задержки, а выход третьего элемента И - с вторым входом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Устройство для сигнализации | 1985 |

|

SU1278913A1 |

| Устройство для измерения температуры | 1986 |

|

SU1432348A1 |

| Устройство для измерения радиального зазора в турбомашинах | 1989 |

|

SU1670370A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243039A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

АНАЛОГО-ДИСКРЕТНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий преобразователь напряжения в частоту, вход которого соединен с входной шиной, а выход с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и выходом первого триггера, а выход с первым входом счетчика импульсов, выход которого соединен с выходной шиной, первый элемент ЛПИ, первый вход которого соединен с шиной Пуск и единичным входом второго триггера, а выход - с единичным входом первого триггера, генератор опорной частоты, выход которого соединен с вторым входом второго элемента И, выход которого соединен с входом первого блока пересчета, выход которого соединен с нулевым входом первого триггера, выход второго триггера соединен с первым входом третьего элемента И, а нулевой вход - с нулевы входом третьего триггера, четвертый элемент И, первый компаратор, четвертьй триггер, отл ичающийся тем, что, с целью повышения помехоустойчивости, в него введены второй и третий элементы ИЖ, второй блок пересчета, два формирователя коротких импульсов, элемент задержки, второй компаратор, два запоминающих устройства, три ключа, формирователь сигнала скорости, вход которого соединен с входной шиной, первый выход - с первыми входами первого и второго ключей, второй выход - с первым входом третьего ключа, второй вход которого соединен с выходом первого формирователя коротких импульсов, а выход - с входом первого запоминающего устройства, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с первым входом второго О) компаратора и выходом второго ключа, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И и первым входом четвертого элемента И, а второй вход соединен с выходом второго компаратора, второй вход которого соединен с выходом второго запоминающего устройства, вход которого соединен с выходом первого ключа, второй вход которого соединен с выходом второго формирователя коротких импульсов, вход которого соединен с входом элемента задержки и выходом третьего триггера, единичный вход которого соединен с выходом первого блока пересчета, вторым входом счетчика импульсов, входом второго блока пересчета и вторым входом четвертого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго блока

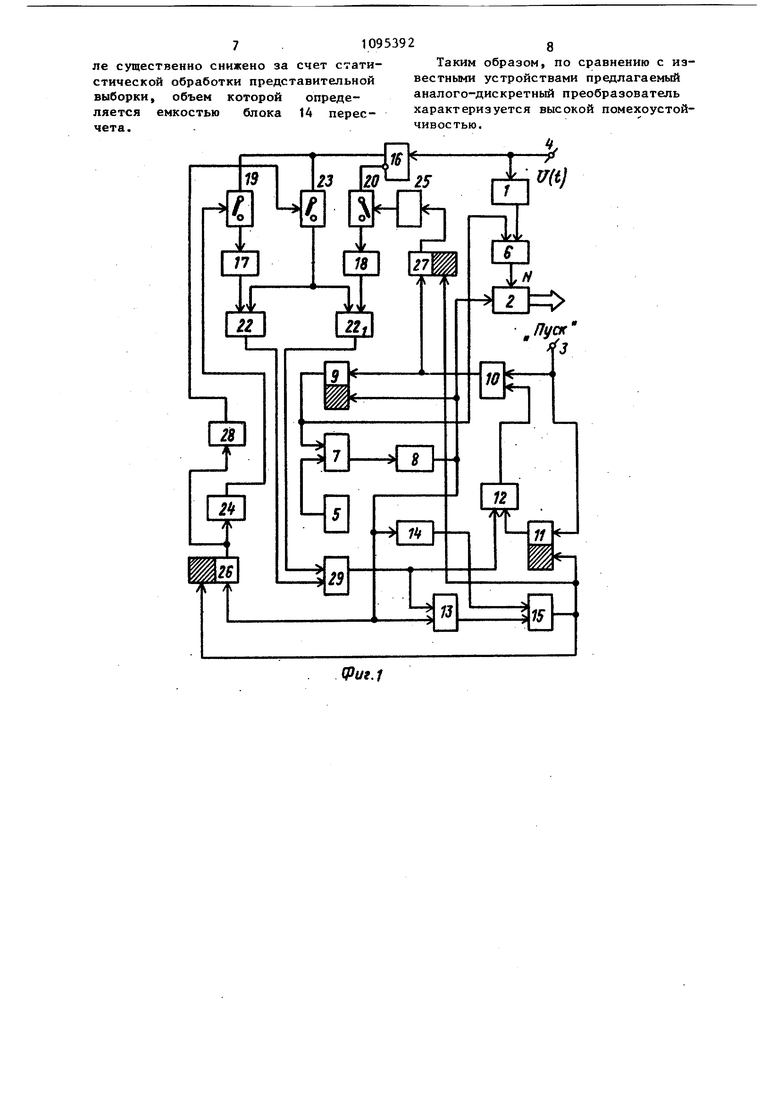

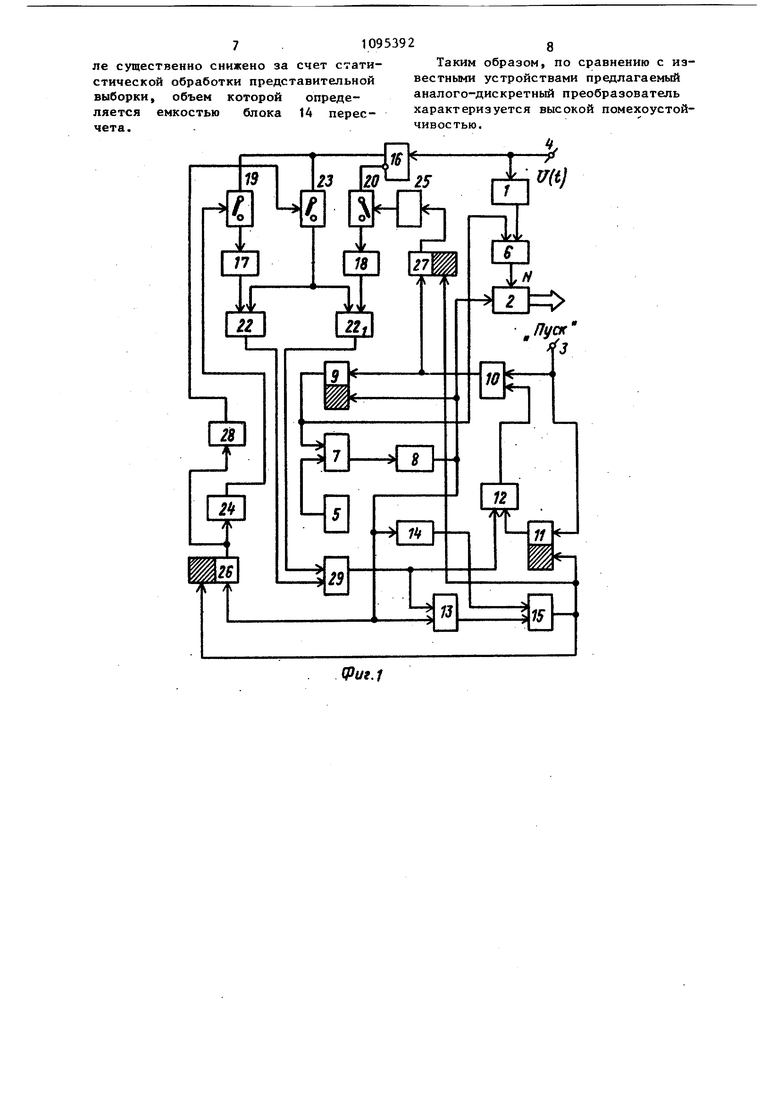

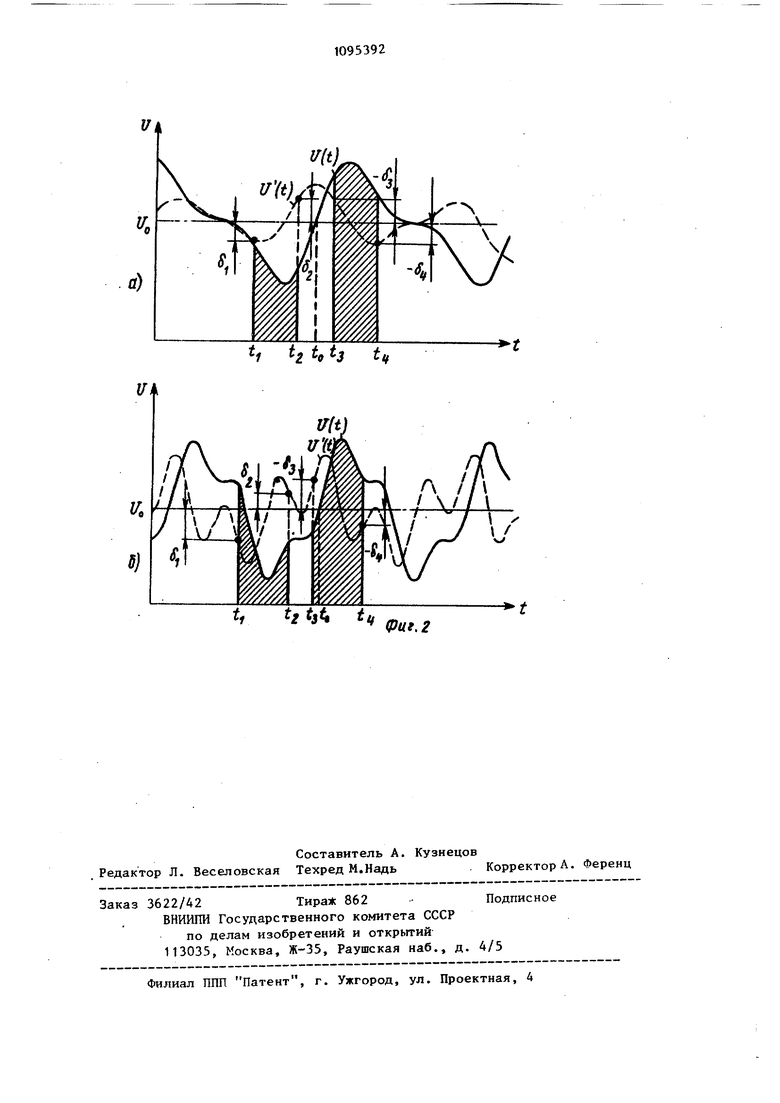

Изобретение относится к электроиз мерительной технике и используется в информационно-измерительной технике. Известен помехоустойчивый дискретный преобразователь частотноимпульсного кодирования с преобразов нием измеряемой величины в частоту следования электрических импульсов за фиксированный интервал времени ti Однако такое устройство характеризуется недостаточной помехоустойчивостью при некратности периода помехи фиксированному интервалу измерения.. Наиболее близким к предлагаемому является аналого-дискретный преобразователь, содержащий преобразователь напряжения в частоту, вход которого соединен с входной шиной а выход с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и выходом первого триггера, а выход - с первым входом счетчика импульсов, вы ход которого соединен с выходной шиной, первый элемент ИЖ, первый вход которого соединен с шиной Пуск и единичньм входом второго триггера, а выход - с единичным входом первого триггера, генератор опорной частоты, выход которого соединен с вторым вхо дом второго элемента И, выход которого соединен с входом первого блока пересчета, выход которого соединен с нулевым входом первого триггера, выход второго триггера соединен с первым входом третьего элемент И, а нулевой вход - с нулевым входом третьего триггера, четвертый элемент И, первьй компаратор, четвертый триггер 23. Однако известный преобразователь характеризуется недостаточной помехоустойчивостью при любом виде симметрии периодической помехи и числе переходов через нулевое значение, большем минимального (три за период), а также при непериодической случайной помехе. Целью изобретения является повышение помехоустойчивости преоб разователя. Поставленная цель достигается тем, что в аналого-дискретньА преобразователь, содержащий преобразова:тель напряжения в частоту, вход которого соединен с входной шиной, а выход с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и выходе первого триггера, а выход с первым входом счетчика импульсов, выход которого соединен с выходнрй шиной, первый элемент ИЛИ, первый вход которого соединен с шиной Пуск и единичньм входом второго триггера, а выход - с единичным входом первого триггера, генератор опорной частоты, выход которого соединён с в то-, рым входом второго элемента И, выход которого соединен с входом первого блока пересчета, выход которого соединен с нулевым входом первогр.триггера, выход второго триггера соединен с первым входом третьего элемента И, а нулевой вход с нулевым входом третьего триггера, четвертый элемент И,, первый компаратор, четвертый триггер, введены второй и третий элементы .ИЛИ, второй блок пересчета, два формирователя коротких импульсов, элемент задержки, второй компаратор, два запоминающих устройства, три ключа, формирователь сигнала скорости,вход которого соединен с входной шиной, первый выход - с первыми входами первого и второго ключей, второй выход - с первым входом третьего ключа, второй вход которого соединен с выходом первого формирователя коротких импульсов, а выход - с входом 3 первого запоминающего устройства, выход которого соединен с первым входом первого компаратора, второй вход которого соедин.ен с первым вхо дом второго компаратора и выходом , второго ключа, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И и первым входом четвертого элемента И, а второй вход 10 соединен с выходом, второго компаратора, второй вход которого соединен с выходом второго запоминающего устройства вход которого соединен с выходом первого ключа, второй вход которого соединен с выходом второго формирователя коротких импульсов, вход которого соединен с входом элемента задержки и выходом третьего триггера, единичный вход которого соединён с выходом первого бло ка пересчета, вторым входом счетчика импульсов, входом второго блока пересчета и вторым входом четвертого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ второй вход которого соединен с выходом второго блока пересчета, а выход - с нулевыми входами второго и, четвёртого триггеров, единичный вход которого соединен с выходом первого элемента ИЛИ, а выход - с входом пер вого формирователя коротких импульсов при этом третий вход второго ключа соединен с выходом элемента задержки, а выход третьего элемента И - с вторым входом первого элемента ИЛИ. На фиг. 1 представлена функциональная схема предлагаемого аналогодискретного преобразователя; на фиг. 2 - временные диаграммы, пояс- няющие принцип действия преобразователя при нгшичии двух типичных в измерительной практике случаев симметрии кривой периодического процесса: П рода (а); Ш рода (б). Преобразователь содержит преобразователь 1 напряжения в .частоту, счетчик 2 импульсов, шину3 Пуск, и входную шину 4, генератор 5 опор ной частоты, элементы 6и7И, блок 8 пересчета, триггер 9, элемент 10 ИЛИ, триггер 11, элементы 12 и 13 И, блок 14 пересчета, элемент 15 ИЛИ, формирователь 16 сигнала скорости, запоминающие устройства 17 и 18, ключи 1 и 20, компараторы 21 и 22, ключ 23, формирователи 24 и 25 корот 92 ких сигналов, триггеры 26 и 27, элемент 28 задержки, элемент 29 И.ПИ. Преобразователь 1 напряжения в частоту входом соединен с входной шиной 4 и входом - с первым входом элемента 6 И, выход которого соединен с входом счетчика 2 импульсов. Шина 3 Пуск соединена с первым входом элемента 10 ИЛИ. Выход генератора 5 соединен с вторым входом элемента 7 И, выход которого соединен с входом блока 8 пересчета. Единичный вьтход триггера 9 подсоединен к вторым входам элементов 6 и 7 И, нулевой входк выходу блока 8 пересчета, единичный вход - к выходу элемента 10 ИЛИ, первый вход которого соединен с ши ной 3 Пуск преобразователя и единичным входом триггера 11, подключенного единичным выходом к первому элемента 12 И, второй вход элемента 12 И соединен с первым вХо sj MeHTa 1J И, причем второй, вход этого элемента подключен к выходу блока 8 пересчета и входу блока 14 пересчета выход которого и выод элемента 13 И соединены с входами элемента 15 ИЛИ. Выход элемента 15 ИЛИ связан с нулевым входом триггера 11,а выход элемента 12 И с вторым входом элемента 10 ИЛИ. Вход формирователя 16 сигнала скорости соединен с входной шиной 4, а входы запоминающих устройств 17 и 18 подключены соответственно к прямому и инв.ерсмому ,вы-. ходам формирователя 16 через ключи 19 и 20. Первый вход калщого из компараторо з 21 и 22 через ключ 23 соединен с прямым выходом формирователя 16 сигнала скорости. Входы , формирователей 24 и 25 коротких импульсов подключены к единичным выходам триггеров 26 и 27 соответственно. Выход формирователя 24 подсоединен к третьему входу ключа. 19, выход триггера 26 через элемент 28 задержки - к третьему входу ключа 23, а выход формирователя 25 - к третьему входу ключа 20, причем выходы компараторов 21 и 22 через элемент 29 ИЛИ соединены с вторыми входами элементов 12 и 13 И. Единичный вход триггера 26 подключен к входу блока 14 пересчета и к выхрду блока 8 пересчета, а также к входу считывания счетчика 2, аединичньй вход триггера 27 к единичному входу триггера 9. Нулевые входы триггеров 26 и 27 подключены к выходу элемента 15 ИЛИ. Преобразователь работает следующим образом. Импульс начала измерения по шине 3 Пуск через первый вход элемента 10 ИЛИ попадает на вход триггера 9, переводя его в единичное состояние, тем самым подготавливаются к работе элементы 6 и 7 И. Импульсы с выхода преобразователя 1 напряжения в частоту поступают через элемент 6 И в счетчик 2, причем частота импульсов пропорциональна уровню измеряемой величины. Выходные импульсы генератора 5 поступают на вход элемента 7 И и проходят на вход блока 8 пересчета. Через интервал времени фиксированной длительности на-выходе блока 8 пересчета формируется импульс, который возвращает триггер 9 в исходное нулевое состояние, прекращая поступление частотных сигналов на вход счетчика 2 и блок 8 пересчета, поступает на вход блока 14 пересчета и на второй вход счетчика 2, производя выдачу цифрового результата измерения потребителю и сброс счетчика на нуль. Пусковой импульс подается также на единичный вход триггера 11. Последний переводится в едй яичное состояние и подготавливает элемент 12 И к работе. В единичное состояние в момент начала измерения переводится также триггер 27. При эт срабатывает формирователь 25, вызывая кратковременное замыкание ключа В момент окончания первого интервала измерения импульс с выхода блока 8 пересчета поступает также на единичный вход триггера 26, переводя его в единичное состояние. В связи с этим срабатьтает формирователь 24, кратковременно ёамыкая ключ 19. Спус тя установленное время задержки замыкается ключ 23 (все указанные ключи нормально-разомкнутые). Врезульта те в устройствах 17 и 18 запоминаются мгновенные прямое и инверсное зна чения сигнала, пропорционального ско рости изменения измеряемой величины, соответствующие началу и концу первого интервала измерения, которые, каг и текущее значение указанного сигнала, поступают на входы компараторов 21 и 22. Для-того, чтобы на вход компаратора 21 попадали только разнесенные во времени значения сигнала скорости вводится элемент задержки 28, причем величина задержки выбирается с учетом динамических свойств указанного сигнала. По достижении текущим значением сигнала на выходах формирователя 16 запомненного значения выходной импульс компаратора через элемент 29 ИЛИ поступает на вход элемента 12 И, вызывая повторный запуск преобразователя. Если в момент окончания второго временного интервала измерения фиксированной длительности, когда на выходе блока 8 пересчета формируется импульс, поступающий на первый вход элемента 13 И, произойдет срабатывание втЗрого компаратора, в результате чего на второй вход элемента 13 И также поступит сигнал, импульс с выхода элемента 13 И через элемент 15 ИЛИ. возвращает все триггеры в исходное положение, и цикл измерений завершается. Если же совпадения во времени сигналов на входе элемента 13 И не произойдет, то поступает команда на третье, четвертое и т.д. измерение, пока на выходе блока 14 пересчета не появится импульс, который прерывает цикл измерений, приводя схему преобразователя в исходное состояние готовности к очередному циклу измерения. На фиг. 2 приведены временные диаграммы изменения сигнала, содержащего измеряемую постоянную составляющую DO и полигармоническую периодическую помеху U{t). Причем на фиг.2а помеха обладает симметрией II рода, а на фиг. 26 - сиь метрией Ш рода. На фиг. 2 приняты следующие обозначения: и (t) - сигнал скорости изменения Измеряемой величины: t и t- - моменты начала и конца первого интервала измерения фиксированной длительности; tj и t - такие же моменты второго интервала измерения; сГ:, cT-jjc - перетады сигнала скорости в точках t л : и t с учетом проставленного знагде д U(t -ь 0) - и (); t - ближайщий после окончания первого интервала измерения переход помехи через нуль. Как видно из приведенных временных диаграмм, предлагаемый преобразователь обеспечивает эффективное подавление помех при любом виде симметрии кривой процесса. Если же помеха представляет собою слз 1айный процесс, то ее влияние на результат измерения в предлагаемом преобразовате-

ле существенно снижено за счет стати- Таким образом, по сравнению с изстической обработки представительной вестными устройствами предлагаемый выборки, объем которой опреде- аналого-дискретный преобразователь ляется емкостью блока 14 перес- характеризуется высокой помехоустой-14 Г

3

.„. ..

Vui.l

чивостью.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровые электроизмерительные приборы | |||

| Под ред | |||

| В.М.Шпяндина, , М., Энергия, 1972, с | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 0 |

|

SU367545A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-30—Публикация

1983-02-02—Подача