Изобретение относится к информационно-измерительной технике и может быть использовано в автоматизированных измерительных системах регистрации быстропротекающих процессов.

Целью изобретения является расширение функциональных возможностей путем графического представления информации, управления режимом запуска от аналогового сигнала, внешнего тактирования, хранения результатов, обработки, повышения быстродействия и уменьшения динамической погрешности при регистрации аналоговых и цифровых сигналов.

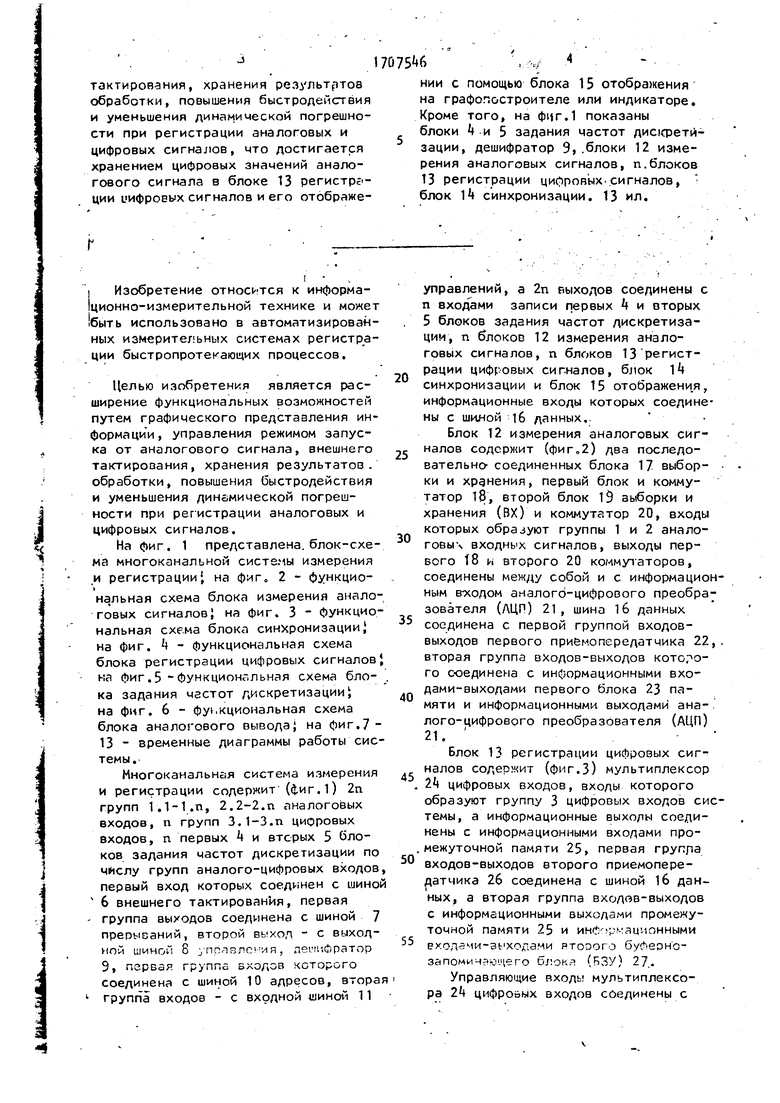

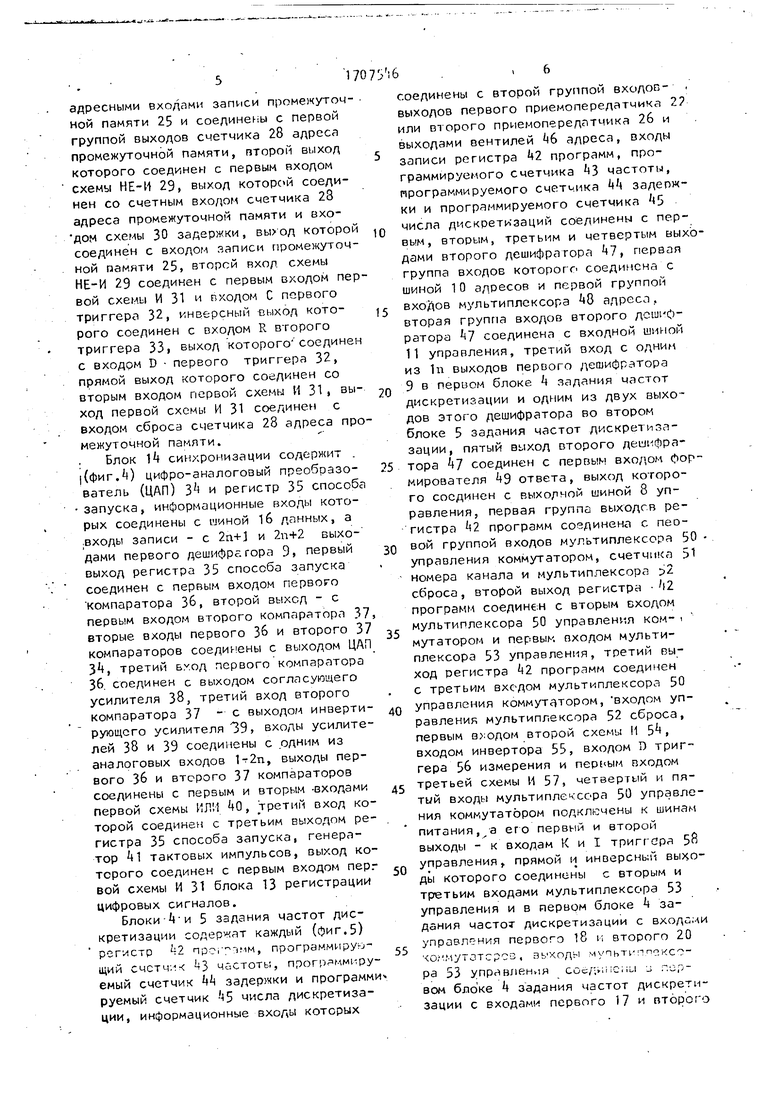

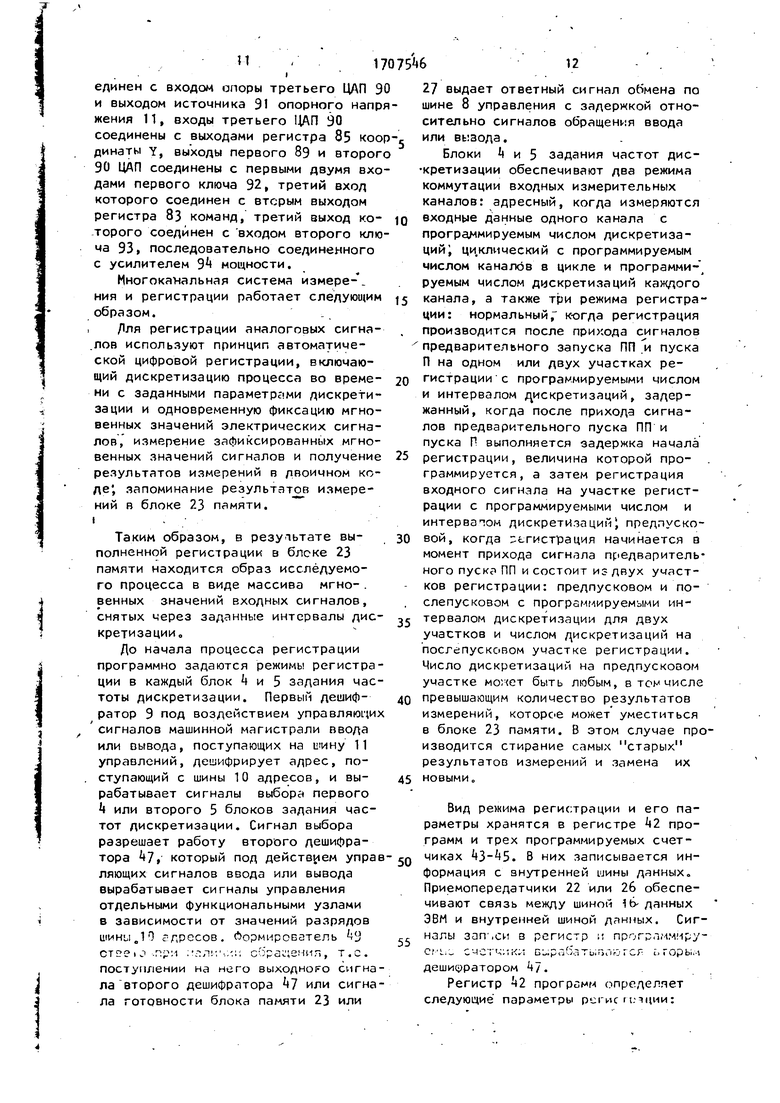

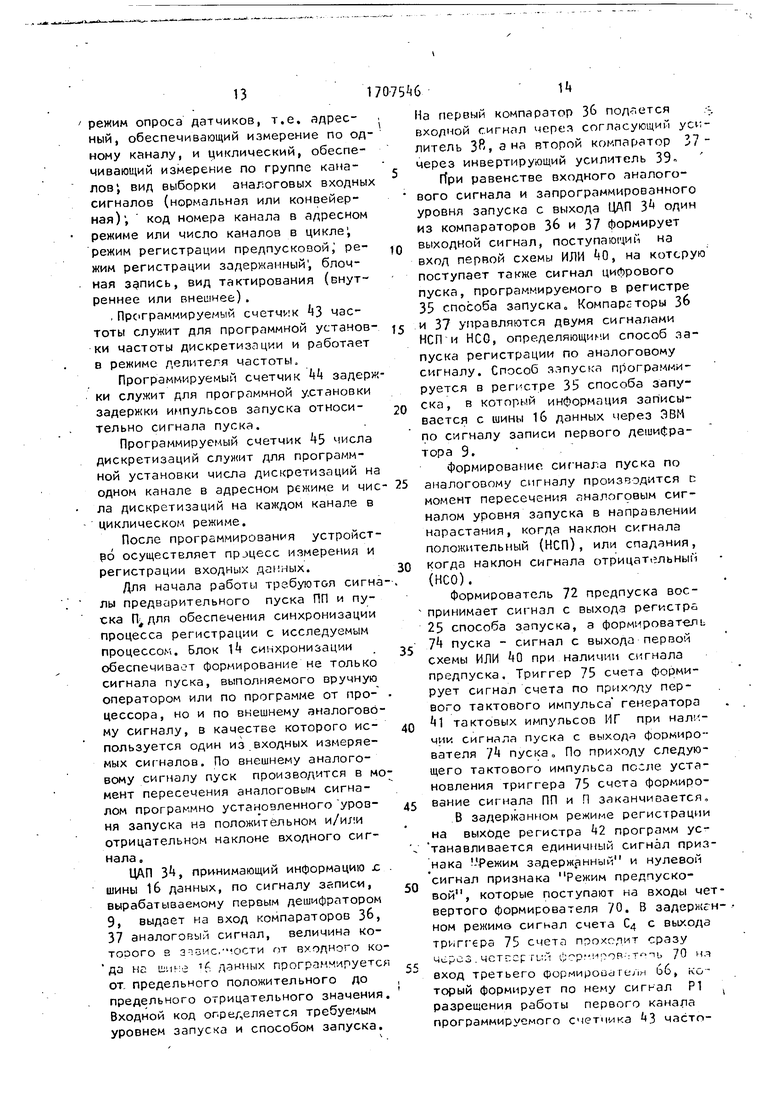

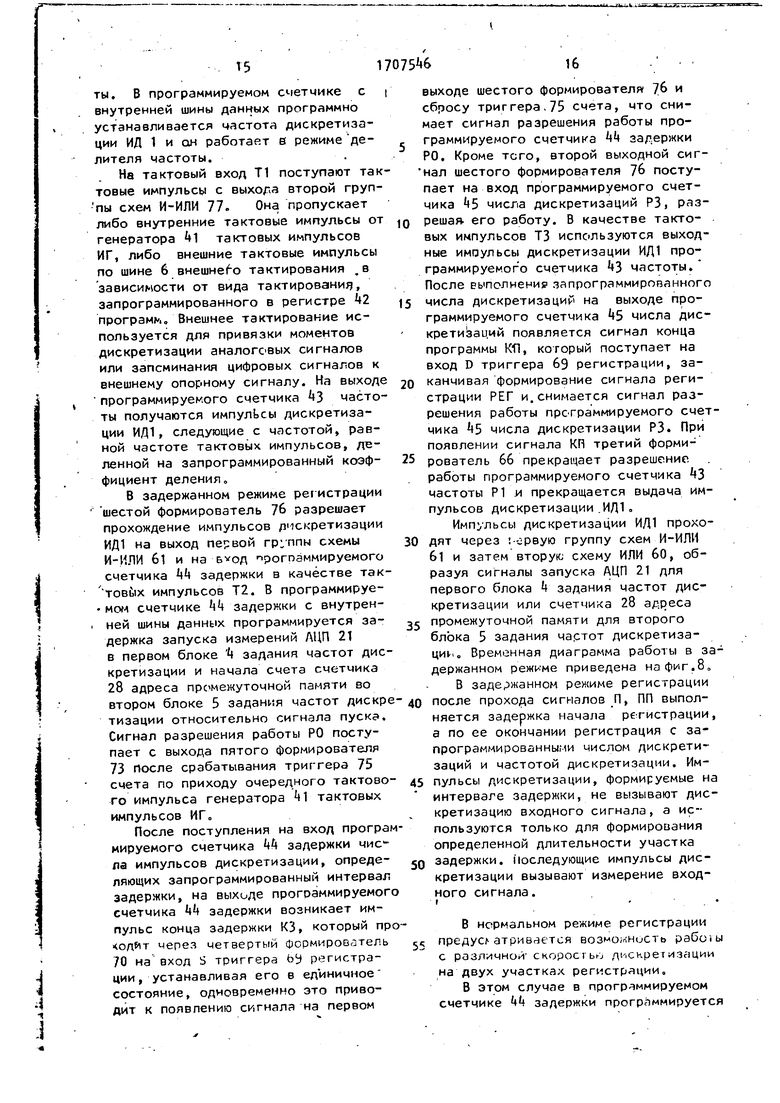

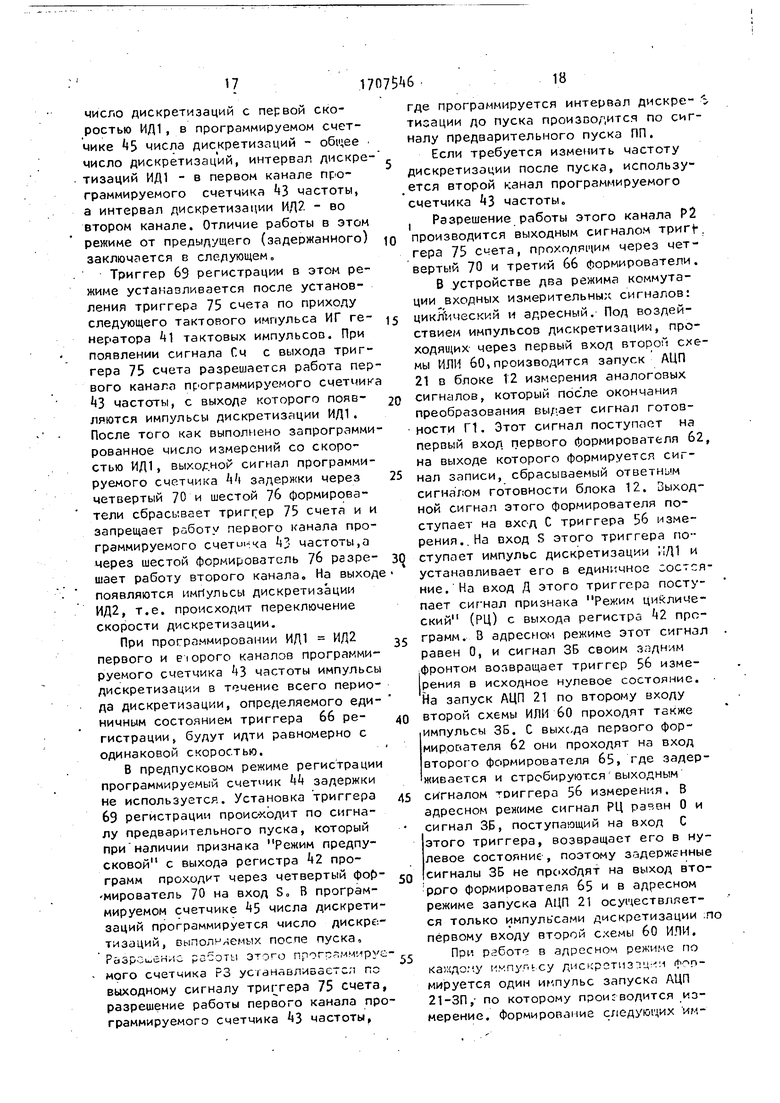

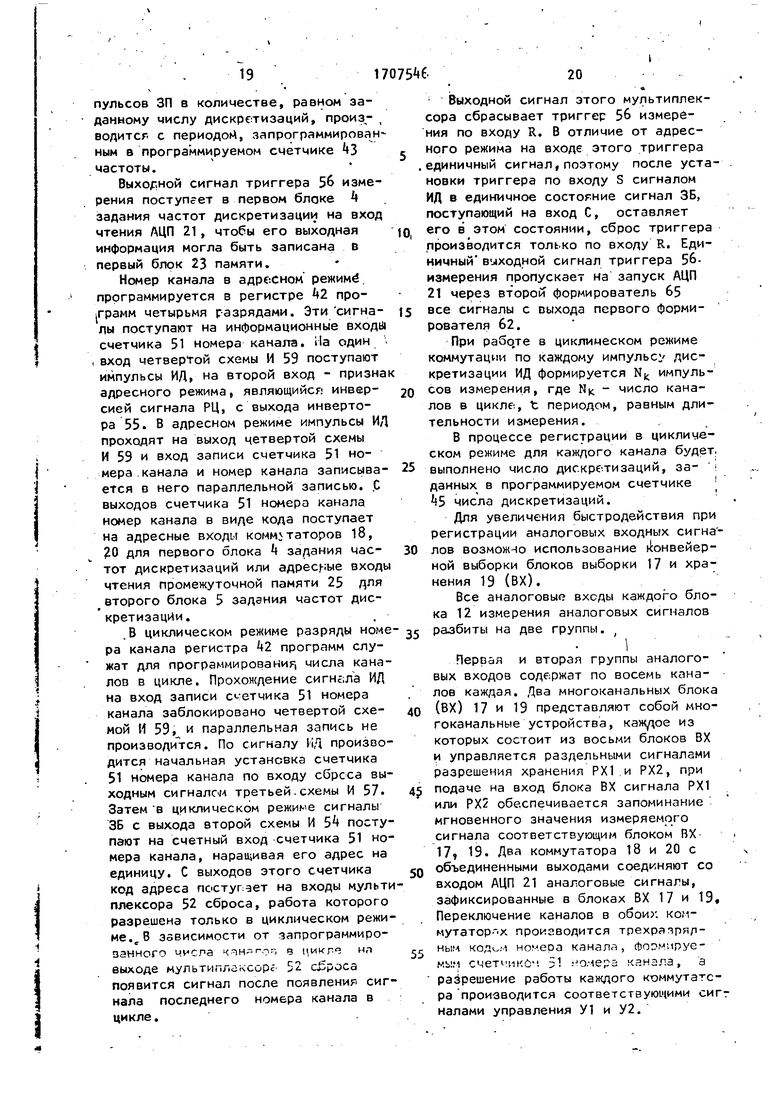

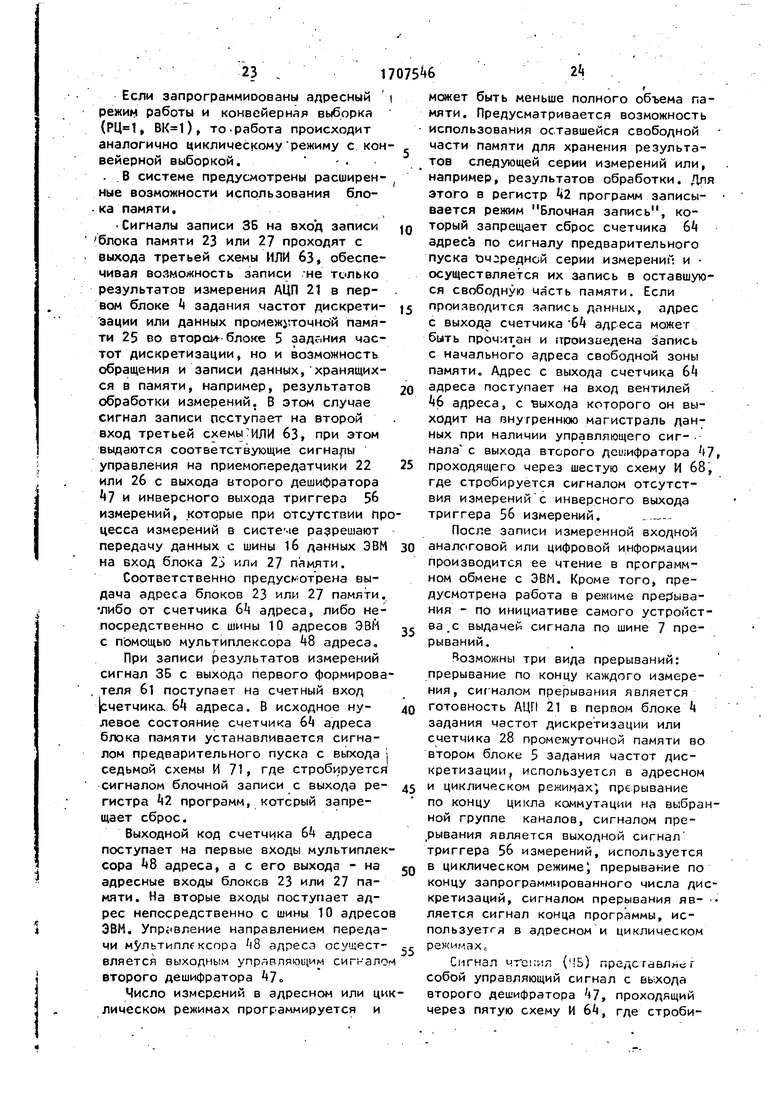

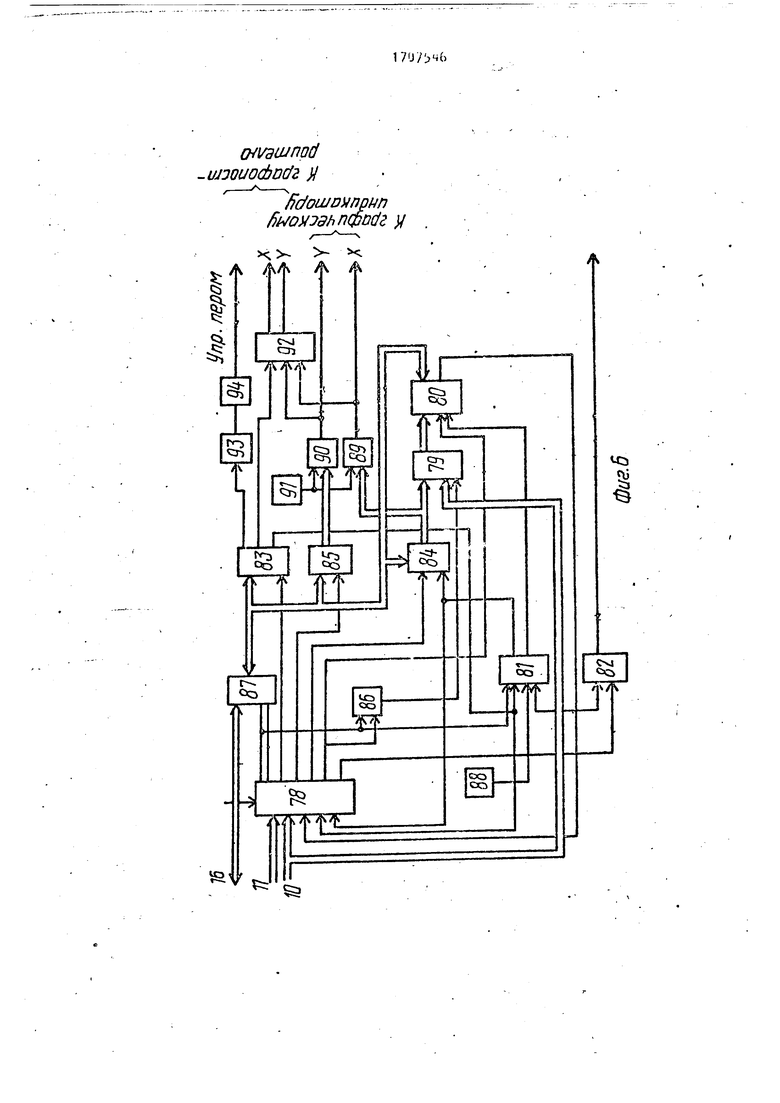

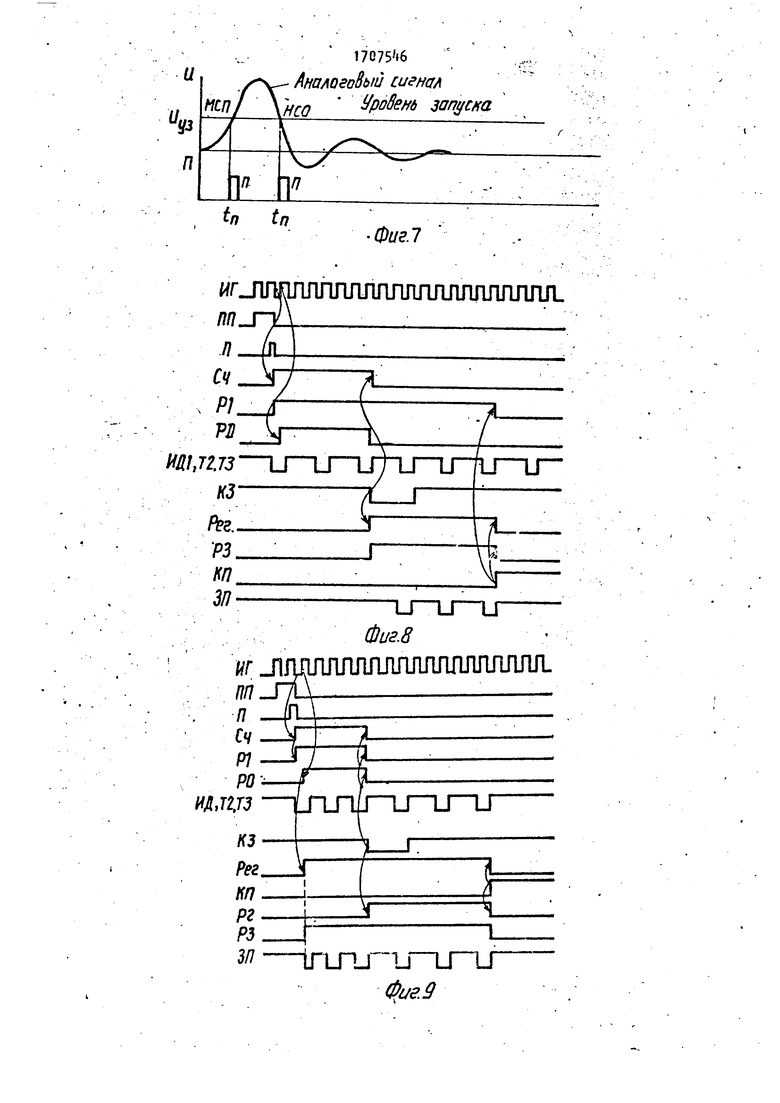

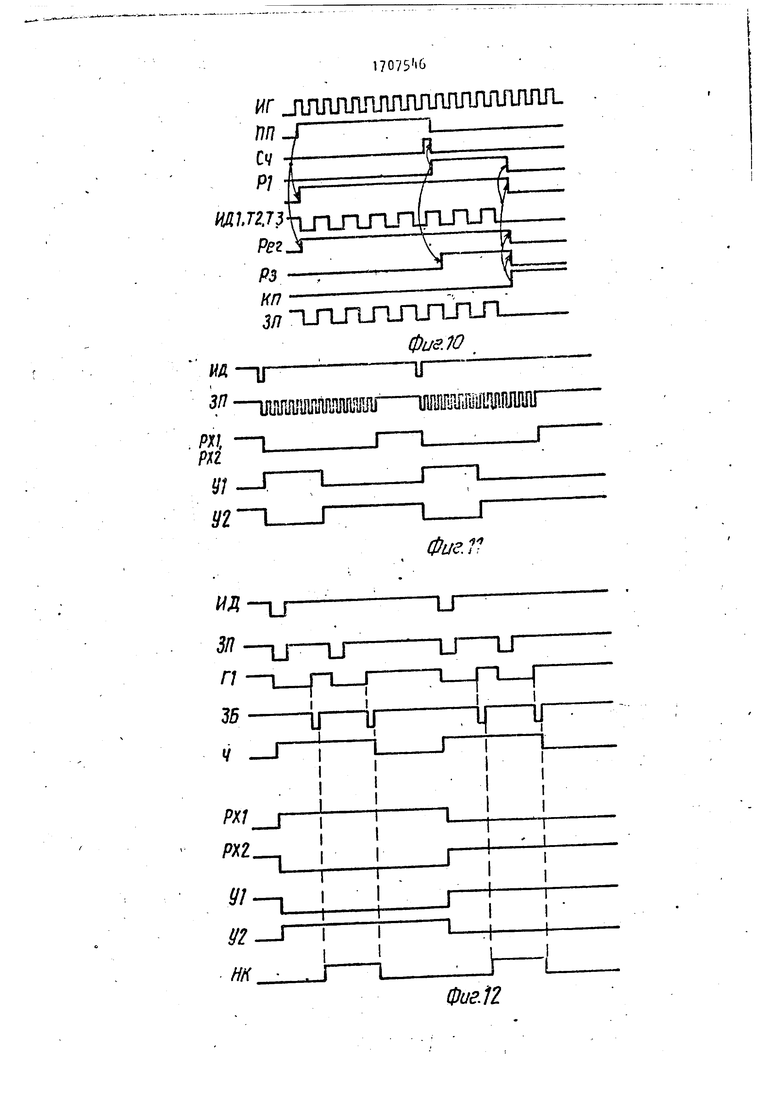

На фиг. 1 представлена, блок-схема многоканальной системы измерения .и регистрации1, на фиг. 2 - функциональная схема блока измерения аналоговых сигналов} на фиг. 3 - функциональная схема блока синхронизации) на фиг. Ь - функциональная схема блока регистрации цифровых сигналов4, на фиг.5 -функциональная схема бло- . ка задания частот дискретизации на фиг. 6 - функциональная схема блока аналогового вывода} на фиг.7 - 13 - временные диаграммы работы системы.

Многоканальная система измерения и регистрации содержит (иг.1) 2п групп 1.1-l.n, 2.2-2.П аналоговых входов, п групп 3.1-З.п циоровых входов, п первых А и втсрых 5 блоков задания частот дискретизации по числу групп аналого-цифровых входов, первый вход которых соединен с шиной 4 6 внешнего тактирования, первая - группа выходов соединена с шиной 7 прерываний, второй выход с выходной шиной 8 управления, дешифратор 9, парная группа входов которого соединена с шиной 10 адресов, вторая 1 группа входов - с входной шиной 11

0

5

0

5

0

5

0

55

управлений, а 2п выходов соединены с п входами записи первых k и вторых 5 блоков задания частот дискретизации, п блоков 12 измерения аналоговых сигналов, п блоков 13 регистрации цифровых сигналов, блок 1 синхронизации и блок 15 отображения, информационные входы которых соединены с шиной 16 данных..

Блок 12 измерения аналоговых сигналов содержит (фиг„2) два последовательно- соединенных блока 17 выборки и хранения, первый блок и коммутатор 18, второй блок 19 выборки и хранения (ВХ) и коммутатор 20, входы которых образуют группы 1 и 2 аналоговых входных сигналов, выходы первого Т8 и второго 20 коммутаторов, соединены между собой и с информационным в-ходом аналого-цифрового преобразователя (АЦП) 21, шина 16 данных соединена с первой группой входов- выходов первого приемопередатчика 22,. вторая группа входов-выходов которого соединена с информационными входами-выходами первого блока 23 памяти и информационными выходами ана- лого-цифрового преобразователя (АЦП) 21.

Блок 13 регистрации цифровых сигналов содержит (фиг.З) мультиплексор 2 цифровых входов, входы которого образуют группу 3 цифровых входов системы, а информационные выходы соединены с информационными входами про- .межуточной памяти 25, первая группа входов-выходов второго приемопередатчика 26 соединена с шиной 16 данных, а вторая группа входов-выходов с информационными выходами промежуточной памяти 25 и информационными входами-зь ходами PTODOTO буФерн о- запоминающего блока (БЗУ) 2..

Управляющие входы мультиплексора 2k цифро&ых входов соединены с

адресными входами записи промежуточ- ной памяти 25 и соединены с первой группой выходов счетчика 28 адреса промежуточной памяти, второй выход которого соединен с первым входом схемы НЕ-И 29, выход которой соединен со счетным входом счетчика 23 адреса промежуточной памяти и входом схемы 30 задержки, выход которой соединен с входом записи промежуточной памяти 25, второй вход схемы НЕ-И 29 соединен с первым входом первой схемы И 31 и входом С первого триггера 32, инверсный -выход которого соединен с входом R второго триггера 331 выход которого соединен с входом D - первого триггера 32, прямой выход которого соединен со вторым входом первой схемы И 31 выход первой схемы И 31 соединен с входом сброса счетчика 28 адреса промежуточной памяти.

Блок 1 синхронизации содержит . (фиг.)) цифро-аналоговый преобразователь (ЦАП) 3 и регистр 35 способа

запуска, информационные входы которых соединены с шиной 16 данных, а входы записи - с 2п+ и 2п+2 выходами первого дешифратора 9, первый выход регистра 35 способа запуска соединен с первым входом первого компаратора 36, второй выход - с первым входом второго компаратора 37, вторые входы первого 36 и второго 37 компараторов соединены с выходом ЦАП 3, третий вход первого компаратора 36. соединен с выходом согласующего усилителя 38, третий вход второго компаратора 37 - с выходом инвертирующего усилителя 39, входы усилителей 38 и 39 соединены с одним из аналоговых входов 1-г2п, выходы первого 36 и второго 37 компараторов соединены с первым и вторым -входами первой схемы ИЛИ +0, третий вход которой соединен с третьим выходом регистра 35 способа запуска, генератор М тактовых импульсов, выход которого соединен с первым входом перг вой схемы И 31 блока 13 регистрации цифровых сигналов.

БлокиV и 5 задания частот дискретизации содержат каждый (фиг.5) регистр ч2 прегог)мм, программирующий счстч .к 3 частоты, программируемый счетчик й задержки и программа руемый счетчик 45 числа дискретизации, информационные входы которых

5

0

5

0

5

0

5

0

5

соединены с второй группой входов- . выходов первого приемопередатчика 2 или второго приемопередатчика 26 и выходами вентилей 6 адреса, входы записи регистра 2 программ, программируемого счетчика 3 частоты, программируемого счетчика задержки и программируемого счетчика числа дискретизаций соединены с первым, вторым, третьим и четвертым выходами второго дешифратора 7, первая группа входов которого соединена с шиной 10 адресов и первой группой входов мультиплексора 8 адреса, вторая группа входов второго дешифратора 7 соединена с входной шиной 11 управления, третий вход с одним из 1п выходов первого дешифратора 9 в первом блоке k задания частот дискретизации и одним из двух выходов этого дешифратора во втором блоке 5 задания частот дискретиза- зации, пятый выход второго дешифратора 7 соединен с первым входом формирователя 9 ответа, выход которого соединен с выходной шиной 8 управления, первая группа выходг.в регистра 2 программ соединена с пео- вой группой входов мультиплексора 50 управления коммутатором, счетчика 51 номера канала и мультиплексора 2 сброса, второй выход регистра (2 программ соединен с вторым входом мультиплексора 50 управления ком- i мутатором и первым входом мультиплексора 53 управления, третий выход регистра 2 программ соединен с третьим входом мультиплексора 50 управления коммутатором, входом управления мультиплексора 52 сброса, первым входом второй схемы И 5, входом инвертора 55, входом I) триггера 56 измерения и первым входом третьей схемы И 57, четвертый и пя- тий входы мультиплексора 50 управления коммутатором подключены к шинам питания, а его первый и второй выходы - к входам К и I триггера 5Й управленияг прямой и инверсный выходы которого соединены с вторым и третьим входами мультиплексора 53 управления и в первом блоке А задания частот дискретизации с входами управления первого 18 и второго 20

.МУТО. , ВЬ ХОДЫ мупьТИПпекС ра 53 управления соединены u первом блоке k задания частот дискретизации с входами первого 17 и второго

- 7

19 блока выборки и хранения, выходы счетчика 51 номера канала соединены, с информационными входами мультиплексора 52 сброса и в первом блоке k задания частот дискретизации с адресными входами первого 16 и второго

20 коммутаторов, а во втором блоке 5 задания частот дискретизации - с адресными входами чтения промежуточной памяти 25, выход инвертора 55 соединен с первым входом четвертей схемы И 59, второй вход которой соединен с входом S триггера 56 измерения, входом С триггера 58 управления вторым входом третьей схемы И 57, первым входом второй схемы ИЛИ 60, первым выходом первой группы схемы И-ИЛИ 61, выход мультиплексора 52 сброса соединен с входом R триггера 56 измерения, вход С которого соели нен с вторым вхолом второй схемы 5 И, с первым выходом первого формирователя 62, первым входом третьей схемы ИЛИ 63 и счетным входом ч счетчика 6 адреса, первый вход пер вого формирователя 6 соединен с шиной 7 прерываний и в первом блоке А задания частот дискретизации - с выходом готовности АЦП 21 , а во втором блоке 5 задания u-стот дискретизации - со вторым выходом счетчи-- ка 28 адреса промежуточной памяти, второй вход первого формирователя 62 соединен со вторым входом форми- рователя 9 ответа и выходом готовности первого блока памяти 23 или второго буферчо-запоминающего блока 27 для первого или второго блоков 4 и 5 задания частот дискретизации соответственно, выход третьей схемы ИЛИ 63 соединен с входом записи первого или второго запоминающих блоков 23 или 27 для первого или второго 5 блоков задания частот дискретизации соответственно, счетный вход счетчика 51 номера кангла соединен с выходом второй ххемы И 5, вход записи - с выходом четвертой схемы И 59, а вход сбора с выходом третьей схемы И 57, прямой выход триггера 56 измерения соединен с чевертым входом мультиплексора 53 управления (ВХ), с первым входом второго формирователя 65, первым входом третьего формирователя 6Ј, шиной 7 прерыьдми. и с входом чтения АЦП 8 для. первого блока k зада- ния частот дискретизации или с

8

0

0

входом чтения промежуточной памяти 25 для второго блока 5 задания частот дискретизации, второй вход второго формирователя 65 соединен с вторым выходом первого формирователя 62. первый вход пятой схемы И 67 соединен с шестым выходом второго до- , шифратора 7, седьмой выход которого соединен с входом управления мультиплексора .8 адреса, восьмой выход - с первым входом управления приемопередатчиков 22 или 26 для первого или второго блока I или ; 5 задания частот дискретизации соответственно, девятый выход - с первым входом шестой схемы И 68, второй вход которой соединен с инверсным выходом триггера 56 измерений, вторым входом пятой схемы И 67, входом С триггера 69 регистрации и вторым входом управления приемопередатчиками 22 или 26, а выход шестой схемы И 68 - с входом управления вен5 тилей 6 адреса, десятый выход второго дешифратора 7 соединен с вторым входом третьей схемы ИЛИ 63, выход пятой схемы И 67 соединен с входом чтения первого 23 или второго 27 блока памяти для первого А или второго 5 блоков задания частот дискретизаций соответственно, выход второго формирователя 65 содеинен с вторым входом второй схемы ИЛИ 60, выход которой соединен с входом пуска АЦП 21 для первого блока k задания частот дискретизации и входом С второго триггера 33 для второго .блока 5 задания частот дискретиза40. ции, вход S триггера 69 регистрации соединен с первым выходом четвертого формирователя 70, первые два входа которого соединены с четвертым и пятым выходами регистра 2 программ, третий вход - с выходом программируемого счетчика й задержки, четвертый вход - с первым входом седьмой схемы 71 И, первым входом формирователя 72 предпуска и четвертым выходом регистра 35 способа запуска, пятый вход - с входом разрешения программируемого счетчика задержки и-выходом пятого формирователя 73 шестой вход - со вторым входом фор55 мирователя 72 лредпуска, первыми

входами пятого формирователя 73 и формирователя 7 г.уска, л аыхо-дом ipur- гора 75 счета, вход D триггера 69 регистрации соединен со вторым вхо30

35

45

50

дом третьего формирователя 66, первым входом шестого формирователя 76, выходом программируемого счетчика 5 числа дискретизаций и шиной 37 пре- .рываний, третий вход третьего формирователя 66 соединен со вторым , выходом четвертого формирователя 70, второй вход шестого формирователя 76

или второго 27 блоков памяти для пер вого 1 или второго 5 блоков зада- VWH частот дискретизации соответ- I ственноо

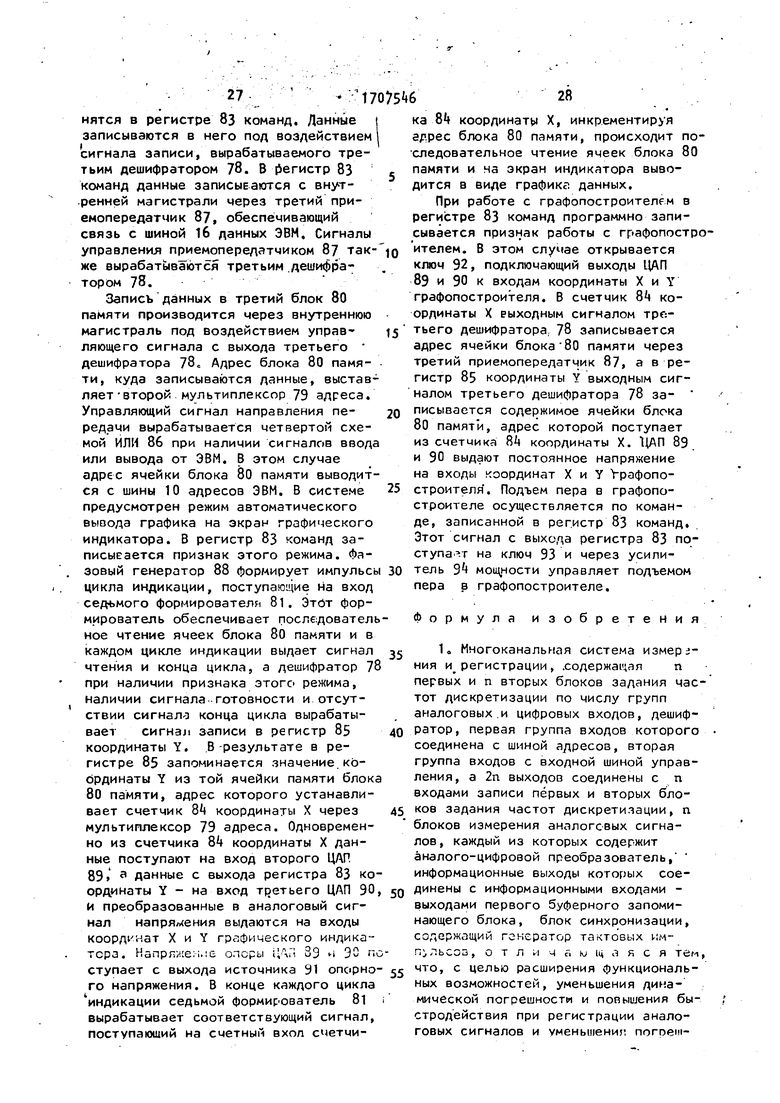

Блок 15 отображения содержит (фиг.6), третий дешифратор 78, первая группа входоз которого соединена С входной шиной 11 управления, соединен с третьим выходом четвертого JQ вторая группа входов - с шиной 10 формирователя 70, третий вход - с вы- адресов и первой группой входов ходом триггера 69 регистрации и пер- второго мультиплексора 79 адреса,

третий вход - с 2п+3-м выходом пер- вого дешифратора 9, четвертый вход - с выходом третьего блока 80 памяти и первыми входами седьмого формирователя 81 и второго формирователя 82

вым входом первой группы схем И-ИЛИ 61; второй и третий входы которой соединены с первым и вторым выходами 15 программируемого сметчика (3 частоты, четвертый вход - с первым выходом

шестого формирователя 76 и входом разрешения второго канала программируемого счетчика 3 частоты, вход разрешения первого канала которого соединен с выходом третьего формирователя 66, втор ой выход пер- .вой группы схем И-ИЛИ 61 соединен с тактовыми входг.ми программируемых счетчиков й и 5 задержки и чис- |Ла дискретизаций, второй выход шестого формирователя 76 соединен с входом разрешения программируемого счетчика 5 число дискретизаций, третий выход - с входом R триггера 75, вход С которого соединен о вторым входом формирователя 7 пуска, третьим входом формирователя 72 предответа, пятый вход - с вторым входом седьмого формирователя 81 и первым

2Q выходом регистра 83 команд, шестой вход - с первым выходом седьмого формирователя 81 и счетным входом счетчика 8 координаты X, первые три выхода третьего дешифратора 78 сое25 динены с входами записи регистра 83 команд, счетчика 8 координаты X, регистра 85 координаты Y, четвертый выход соединен с вторым входом второго формирователя 82 ответа, выход ко30 торого соединен с выходной шиной 8 управления, пятый выход - с пемным управляющим входом третьего блока памяти 81 и первым входом четвертой схемы 86 ИЛИ, шестой выход - с первым

пуска, первым входом второй группы 35 вх°дом третьего приемопередатчика 87,

схем И-ИЛИ 77 и выходом генератора М тактовых импульсов, второй вход пятого формирователя 73 соединен с тактовыми входами первого и второго каналов программируемого счетчика 3 частоты и с выходом второй группы схем И-ИЛИ 77, второй вход которой соединен с седьмым выходом регистра 52 программ, а третий вход - с шиседьмои - с вторым входом четвертой схемы ИЛИ 86, третьим входом седьмого формирователя 81 и рторым входом . третьего приемопередатчика 87, первая 40 группа входов-выходов которого соединена с шиной 16 данных, а вторая группа входов-выходов - с информационными входами регистра 83 команд, счетчика 8Ц координаты X регистра 85

ной 6 внешнего тактирования,- вход I 45 координаты Y и группой входов-выхо- триггера 75 счета соединен с выходом дов третьего блока 80 памяти, адресные входы которого соединены с выходами мультиплексора 79 адреса, втоформирователя 7 пуска, третий вход которого соединен с выходом первой схемы ИЛИ ЙО, а четвертый - с выходом формирователя 72 предпуска, второй вход седьмой схемы 71 И соединен с шестым выходом регистра

прогрг мм, а ее выход - с входом установки счетчика адреса, выходы счетчика 6А , ,-реса соединены с входами вентилей 6 адреса и со вто- рбй группой входов мультиплексора

8 адреса, выходы которого соединены с адресными входами первого 23

50

рой управляющий вход третьего блока 80 памяти соединен с. вторым выходом седьмого формирователя 81, четвертый вход которого соединен с выходом фа- зового генератора 88, выход четвертой схемы ИЯИ 86 соединен с управляющим входом мультиплексора 79 адреса, вторая группа ахсдсс которого .м- нена с информационными выходами счетчика 8А координаты X и входами второго ЦЛП 89, вход опоры которого со

или второго 27 блоков памяти для пер вого 1 или второго 5 блоков зада- VWH частот дискретизации соответ- I ственноо

Блок 15 отображения содержит (фиг.6), третий дешифратор 78, первая группа входоз которого соединеответа, пятый вход - с вторым входом седьмого формирователя 81 и первым

выходом регистра 83 команд, шестой вход - с первым выходом седьмого формирователя 81 и счетным входом счетчика 8 координаты X, первые три выхода третьего дешифратора 78 соединены с входами записи регистра 83 команд, счетчика 8 координаты X, регистра 85 координаты Y, четвертый выход соединен с вторым входом второго формирователя 82 ответа, выход которого соединен с выходной шиной 8 управления, пятый выход - с пемным управляющим входом третьего блока памяти 81 и первым входом четвертой схемы 86 ИЛИ, шестой выход - с первым

седьмои - с вторым входом четвертой схемы ИЛИ 86, третьим входом седьмого формирователя 81 и рторым входом . третьего приемопередатчика 87, первая группа входов-выходов которого соединена с шиной 16 данных, а вторая группа входов-выходов - с информационными входами регистра 83 команд, счетчика 8Ц координаты X регистра 85

0

рой управляющий вход третьего блока 80 памяти соединен с. вторым выходом седьмого формирователя 81, четвертый вход которого соединен с выходом фа- зового генератора 88, выход четвертой схемы ИЯИ 86 соединен с управляющим входом мультиплексора 79 адреса, вторая группа ахсдсс которого .м- нена с информационными выходами счетчика 8А координаты X и входами второго ЦЛП 89, вход опоры которого со10

15

20

25

единен с входом опоры третьего ЦАП 90 и выходом источника 91 опорного напряжения 11, входы третьего ЦАП 90 соединены с выходами регистра 85 коор-, динаты у, выходы первого 89 и второго 90 ЦАП соединены с первыми двумя входами первого ключа 92, третий вход которого соединен с вторым выходом регистра 83 команд, третий выход которого соединен с входом второго ключа 93, последовательно соединенного с усилителем 9 мощности.

Многоканальная система измере- ния и регистрации работает следующим образом.Л-Пя регистрации аналоговых сигна- .лов используют принцип автоматической цифровой регистрации, включающий дискретизацию процесса во времени с заданными параметрг ми дискретизации и одновременную фиксацию мгновенных значений электрических сигналов, измерение зафиксированных мгновенных значений сигналов и получение результатов измерений в двоичном коде , запоминание результатов измерений в блоке 23 памяти, i .

Таким образом, в результате вы- 30 полненной регистрации в блоке 23 памяти находится образ исследуемого процесса в виде массива мгно- . венных значений входных сигналов, снятых через заданные интервалы дис- ,5 кретизациио

До начала процесса регистрации программно задаются режимы регистрации в каждый блок и 5 задания частоты дискретизации. Первый дешиф- до ратор 9 под воздействием управляющих сигналов машинной магистрали ввода или вывода, поступающих на шину 11 управлений, дешифрирует адрес, поступающий с шины 10 адресов, и вы- 45 рабатывает сигналы выбора первого k или второго 5 блоков задания частот дискретизации. Сигнал выбора разрешает работу второго дешифра27 выдает ответный сигнал обмена по шине 8 управления с задержкой относительно сигналов обращения ввода или вывода.

Блоки I и 5 задания частот дис- кретизации обеспечивают два режима коммутации входных измерительных каналов: адресный, когда измеряются входные данные одного канала с программируемым числом дискретизаций 1 циклический с программируемым числом каналов в цикле и программи- руемым числом дискретизаций каждого канала, а также три режима регистрации: нормальный, когда регистрация производится после прихода сигналов предварительного запуска ПП .и пуска П на одном или двух участках регистрации с программируемыми числом и интервалом дискретизаций, задержанный, когда после прихода сигналов предварительного пуска ПП и пуска П выполняется задержка начала регистрации, величина которой программируется, а затем регистрация входного сигнала на участке регистрации с программируемыми числом и интервалом дискретизаций предпусковой, когда -ьгистрация начинается в момент прихода сигнгэла предварительного пуска ПП и состоит из двух участков регистрации: предпусковом и по- слепусковом с программируемыми интервалом дискретизации для двух участков и числом дискретизаций на посгепусковом участке регистрации. Число дискретизаций на предпусковом участке монет быть любым, в тем числе превышающим количество результатов измерений, которое может уместиться в блоке 23 памяти. В этом случае про изводится стирание самых старых

результатов новыми о

измерении и замена их

Вид режима регистрации и его параметры хранятся в регистре А2 программ и трех программируемых счеттора 7 который под действием управ- Q чиках . В них записывается инляющих сигналов ввода или вывода вырабатывает сигналы управления отдельными функциональными узлами в зависимости от значений разрядов

шини.Ю адресов. Лормировзтель 9 CT«ei; -.при ::г.... сбра1 ;емип, т.е. поступлении на него выходного сигнала второго дешифратора 7 или сигнала готовности блока памяти 23 или

55

формация с внутренней шины данных. Приемопередатчики 22 или 26 обеспечивают связь между шиной Ib- данных ЭВМ и внутренней шиной данных. Сиг налы записи в регистр и прогрлмммру Cf- t; счетчик;; Б1,.рлЬзть;г о;огся ьгорым дешифратором 7.

Регистр 2 программ определяет следующие параметры регис г i.-чции:

5

0

5

0 5

о 5

27 выдает ответный сигнал обмена по шине 8 управления с задержкой относительно сигналов обращения ввода или вывода.

Блоки I и 5 задания частот дис- кретизации обеспечивают два режима коммутации входных измерительных каналов: адресный, когда измеряются входные данные одного канала с программируемым числом дискретизаций 1 циклический с программируемым числом каналов в цикле и программи- руемым числом дискретизаций каждого канала, а также три режима регистрации: нормальный, когда регистрация производится после прихода сигналов предварительного запуска ПП .и пуска П на одном или двух участках регистрации с программируемыми числом и интервалом дискретизаций, задержанный, когда после прихода сигналов предварительного пуска ПП и пуска П выполняется задержка начала регистрации, величина которой программируется, а затем регистрация входного сигнала на участке регистрации с программируемыми числом и интервалом дискретизаций предпусковой, когда -ьгистрация начинается в момент прихода сигнгэла предварительного пуска ПП и состоит из двух участков регистрации: предпусковом и по- слепусковом с программируемыми интервалом дискретизации для двух участков и числом дискретизаций на посгепусковом участке регистрации. Число дискретизаций на предпусковом участке монет быть любым, в тем числе превышающим количество результатов измерений, которое может уместиться в блоке 23 памяти. В этом случае производится стирание самых старых

результатов новыми о

измерении и замена их

Вид режима регистрации и его параметры хранятся в регистре А2 программ и трех программируемых счетчиках . В них записывается ин

формация с внутренней шины данных. Приемопередатчики 22 или 26 обеспечивают связь между шиной Ib- данных ЭВМ и внутренней шиной данных. Сигналы записи в регистр и прогрлмммру- Cf- t; счетчик;; Б1,.рлЬзть;г о;огся ьгорым дешифратором 7.

Регистр 2 программ определяет следующие параметры регис г i.-чции:

режим опроса датчиков, т.е. адресный, обеспечивающий измерение по одному каналу, и циклический, обеспечивающий измерение по группе каналов , вид выборки аналоговых входных сигналов (нормальная или конвейерная), код номера канала в адресном режиме или число каналов в цикле1, режим регистрации предпусковой; режим регистрации задержанный , блочная запись, вид тактирования (внутреннее или внешнее).

,Программируемый счетчик 3 частоты служит для программной установки частоты дискретизации и работает в режиме делитег-я частоты,

Программируемый счетчик kk задержки служит для программной установки задержки импульсов запуска относительно сигнала пуска.

Программируемый счетчик 5 числа дискретизаций служит для программной установки числа дискретизаций на одном канале в адресном режиме и числа дискретизаций на каждом канале в циклическом режиме.

После программирования устройст- рб осуществляет процесс измерения и регистрации входных данных.

Для начала работы требуются сигналы предварительного пуска ПП и пуска обеспечения синхронизации процесса регистрации с исследуемым процессом. Блок k синхронизации обеспечивает формирование не только сигнала пуска, выполняемого вручную оператором или по программе от про- цессора, но и по внешнему аналоговому сигналу, в качестве которого используется один из.входных измеряемых сигналов. По внешнему аналоговому сигналу пуск производится в момент пересечения аналоговым сигналом программно установленного уровня запуска на положительном и/ияи отрицательном наклоне входного сигнала,

ЦАП 3, принимающий информацию Ј шины 16 данных, по сигналу записи, вырабатываемому первым дешифратором 9, выдает на вход компараторов 36, 37 аналоговый сигнал, величина которого В 3-Т ВИС,«ОСТИ ОТ ВХОДНОГО КО да на 1иине данных программируется от. предельного положительного до предельного отрицательного значения. Входной код определяется требуемым уровнем запуска и способом запуска.

5

0

5

0

5

0

5

0

C,

На первый компаратор 36 подается :- входной сигнал через согласующий усилитель второй компаратор 11- через инвертирующий усилитель 39

равенстве входного аналогового сигнала и запрограммированного уровня запуска с выхода ЦАП 3 один из компараторов 36 и 37 формирует выходной сигнал, поступающий на вход первой схемы ИЛИ 0, на которую поступает также сигнал цифрового пуска, программируемого в регистре 35 способа запуска. Компарсторы 36 и 37 управляются двумя сигналами НСП и НСО, определяющими способ запуска регистрации по аналоговому сигналу. Способ запуска программируется в регистре 35 способа запуска, в который информация записывается с шины 16 данных через ЭВМ по сигналу записи первого дешифратора 9.

Формирование сигнала пуска по аналоговому сигналу производится с момент пересечения аналоговым сигналом уровня запуска в направлении нарастания, когда наклон сигнала положительный (НСП), или спадания, когда наклон сигнала отрицательный (НСО).

Формирователь 72 предпуска воспринимает сигнал с выхода регистра 25 способа запуска, а формирователь пуска - сигнал с выхода первой схемы ИЛИ 0 при наличии сигнала предпуска. Триггер 75 счета формирует сигнал счета по приходу первого тактового импульса генератора 1 тактовых импульсов ИГ при наличии сигнала пуска с выхода формирователя пуска. По приходу следующего тактового импульса после установления триггера 75 счета формирование сигнала ПП и П заканчивается,

В задержанном режиме регистрации на выходе регистра 2 программ ус- танавливается единичный сигнал признака - -Режим задержанный и нулевой сигнал признака Режим предпусковой, которые поступают на входы четвертого формирователя 70. В задержгн- ном режиме сигнал счета Сд с выхода триггера 75 счета проходит сразу ЧС.РСЗ . четссртий фсрг-. /0 н.ч вход третьего формирователи 66, который формирует по нему сигнал Р1 разрешения работы первого канала программируемого счетчика 3 частоты. В программируемом счетчике с внутренней шины данных программно устанавливается частота дискретизации ИД 1 и он работает в режиме делителя частоты..

На тактовый вход Т1 поступают тактовые импульсы с выхода второй груп- пы схем И-ИЛИ 77. Она пропускает либо внутренние тактовые импульсы от генератора k тактовых импульсов ИГ, либо внешние тактовые импульсы по шине 6 внешнего тактирования .в зависимости от вида тактирования, запрограммированного в регистре k2 программ. Внешнее тактирование используется для привязки моментов дискретизации аналоговых сигналов или запсминания цифровых сигналов к внешнему опорному сигналу. На выходе

программируемого счетчика 3 частоты получаются импульсы дискретизации ИД1, следующие с частотой, равной частоте тактовых импульсов, деленной на запрограммированный коэф- фициент деления.

В задержанном режиме регистрации шестой формирователь 76 разрешает прохождение импульсов дискретизации ИД1 на выход первой группы схемы И-ИЛИ 61 и на рогпзммируемого счетчика й задержки в качестве так товых импульсов Т2. В программируе мом счетчике Й задержки с внутренней шины данных программируется за- держка запуска измерений АЦП 21 в первом блоке k задания частот дискретизации и начала счета счетчика 28 адреса промежуточной памяти во втором блоке 5 задания частот дискре тизации относительно сигнала пускэ. Сигнал разрешения работы РО поступает с выхода пятого формирователя 73 После срабатывания триггера 75 счета по приходу очередного тактово го импульса генератора 1 тактовых импульсов ИГ.

После поступления на вход програмируемого счетчика М задержки чис ла импульсов дискретизации, опреде- ляющих запрограммированный интервал задержки, на выходе программируемог счетчика kk задержки возникает импульс конца задержки КЗ, который пр чодйт через четвертый формирователь 70 на вход S триггера ЬУ регистрации, устанавливая его в единичное состояние, одновременно это приводит к появлению сигнала на первом

выходе шестого формирователя 1& и сбросу триггера,75 счета, что снимает сигнал разрешения работы программируемого счетчика № задержки РО. Кроме тсго, второй выходной сиг- нал шестого формирователя 76 поступает на вход программируемого счетчика 5 числа дискретизаций РЗ, разрешая его работу. В качестве тактовых импульсов ТЗ используются выходные имгэульсы дискретизации ИД1 программируемого счетчика 3 частоты. После выполнения запрограммированного числа дискретизаций на выходе программируемого счетчика 5 числа дискретизаций появляется сигнал конца программы Kfl, который поступает на вход D триггера 69 регистрации, заканчивая формирование сигнала регистрации РЕГ и.снимается сигнал разрешения работы программируемого счетчика 5 числа дискретизации РЗ. При появлении сигнала КП третий формирователь 66 прекращает разрешение работы программируемого счетчика 3 частоты Р1 и прекращается выдача импульсов дискретизации.ИД1.

Импульсы дискретизации ИД1 проходят через :-орвую группу схем И-ИЛИ 61 и затем вторую схему ИЛИ 60, образуя сигналы запуска АЦП 21 для первого блока k задания частот дискретизации или счетчика 28 адреса промежуточной памяти для второго блока 5 задания чартот дискретизации. Временная диаграмма работы в задержанном режиме приведена на фиг.8.

В задержанном режиме регистрации после прохода сигналов П, ПП выполняется задержка начала регистрации, а по ее окончании регистрация с запрограммированными числом дискретизаций и частотой дискретизации. Импульсы дискретизации, формируемые на интерваге задержки, не вызывают дискретизацию входного сигнала, а используются только для формирования определенной длительности участка задержки, последующие импульсы дискретизации вызывают измерение входного сигнала.

г. .

В нормальном режиме регистрации предуо атривается возможность рэбслы с различной скоростью дискретизации на двух участках регистрации,

В этом случае в программируемом счетчике 4 задержки программируется

число дискретизаций с первой скоростью ИД1, в программируемом счетчике 5 числа дискретизаций - общее число дискретизаций, интервал дискре тизаций ИД1 - в первом канале программируемого счетчика 3 частоты, а интервал дискретизации ИД2. - во втором канале. Отличие работы в этом режиме от предыдущего (задержанного) заключается в следующем,

Триггер 69 регистрации в этом режиме устанавливается после установления триггера 75 счета по приходу следующего тактового импульса ИГ ге нератора Al тактовых импульсов. При появлении сигнала Сч с выхода триггера 75 счета разрешается работа первого канала программируемого счетчик 3 частоты, с выходе которого появ- ляются импульсы дискретизации ИД1. После того как выполнено запрограммированное число измерений со скоростью ИД1, выходной сигнал программируемого счетчика А задержки через четвертый 70 и шестой 76 формирователи сбрасывает триггер 75 счета и и запрещает работу первого канала программируемого .ча 3 частоты,а через шестой формирователь 76 разре- шает работу второго канала. На выход появляются имПульсы дискретизации ИД2, т.е. происходит переключение скорости дискретизации.

При программировании ИД1 ИД2 первого и еюрого каналов программируемого счетчика 3 частоты импульсы дискретизации в течение всего периода дискретизации, определяемого единичным состоянием триггера 66 ре- гистрации, будут идти равномерно с одинаковой скоростью.

В предпусковом режиме регистрации программируемый счетчик й задержки не используется. Установка триггера 69 регистрации происходит по сигналу предварительного пуска, который при наличии признака Режим предпусковой с выхода регистра 2 программ проходит через четвертый фор- мирователь 70 на вход 8„ В программируемом счетчике А 5 числа дискретизаций программируется число дискретизаций, выполняемых после пуска. Разрешение работы этого программируемого счетчика РЗ устанавливается пс выходному сигналу триггера 75 счета, разрешение работы первого канала программируемого счетчика 3 частоты,

g

0 5 0

0

5 Q

5

где программируется интервал дискре- тизаций до пуска производится по сигналу предварительного пуска ПП.

Если требуется изменить частоту дискретизации после пуска, используется второй канал программируемого счетчика 3 частоты. Разрешение работы этого канала Р2 производится выходным сигналом тригг. гера 75 счета, проходящим через четвертый 70 и третий 66 формирователи.

В устройстве два режима коммутации входных измерительных сигналов: циклический и адресный. Под воздействием импульсов дискретизации, проходящих через первый вход втором схемы ИЛИ 60,производится запуск АЦП 21 в блоке 12 измерения аналоговых сигналов, который после окончания преобразования выдает сигнал готовности П. Этот сигнал поступает на первый вход первого формирователя 62, на выходе которого формируется сигнал записи, сбрасываемый ответным сигналом готовности блока 12. Выходной сигнал этого формирователя поступает на вход С триггера 56 измерения.. На вход S этого триггера поступает импульс дискретизации ИД1 и устанавливает его в единичное еостся- ние. На вход Д этого триггера поступает сигнал признака Режим цийличе- ский (РЦ) с выхода регистра 2 программ. В адресном режиме этот сигнал равен 0, и сигнал ЗБ своим задним фронтом возвращает триггер 56 измерения в исходное нулевое состояние. На запуск АЦП 21 по второму входу второй схемы ИЛИ 60 проходят также импульсы 35. С выхс.да первого формирователя 62 они проходят на вход второго формирователя 65, где задерживается и стрсбируются выходным сигналом триггера 56 измерения. В адресном режиме сигнал РЦ равен 0 и сигнал ЗБ, поступающий на вход С этого триггера, возвращает его в нулевое состояние, поэтому задержанные сигналы ЗБ не прохо дят на выход вто- ;рого формирователя 65 и в адресном режиме запуска АЦП 21 осуществляется только импуль сами дискретизации ;по первому входу второй схемы 60 ИЛИ.

При работе в адресном режиме по каждому импульсу дискретизации формируется один импульс запуска АЦП 21-ЗП,- по которому прои: водится измерение. Формирование следующих имЮ,

15

25

ульсов ЗП в количестве, равном заанному числу дискретизаций, произ,- ОДИТСР с периодом, запрограммирован ым в программируемом счетчике 3 астоты.

Выходной сигнал триггера 56 измеения поступает в первом блоке А адания частот дискретизации на вход тения АЦП 21, чтобы его выходная нформация могла быть записана в ервый блок 23 памяти.

Номер канала в адресном режиме, рограммируется в регистре Ь2 про- грамм четырьмя разрядами. Эти сигналы поступают на информационные входи счетчика 51 номера канала. На один вход четвертой схемы И 59 поступают импульсы ИД, на второй вход - признак адресного режима, являющийся инвер- 20 сией сигнала РЦ, с выхода инвертора 55. В адресном режиме импульсы ИЛ проходят на выход четвертой схемы И 59 и вход записи счетчика 51 номера, канала и номер канала записывается в него параллельной записью. С выходов счетчика 51 номера канала номер канала в виде кода поступает на адресные входы коммутаторов 18, 20 для первого блока k задания частот дискретизаций или адресные входы чтения промежуточной памяти 25 для второго блока 5 задания частот дис

кретизацйи.

.В циклическом режиме разряды номе- 35 ра канала регистра 42 программ служат для программирование, числа каналов в цикле. Прохождение сигнала ИД на вход записи сметчика 51 номера канала заблокировано четвертой схемой И 59, и параллельная запись не производится. По сигналу ИД производится начальная установка счетчика 51 номера канала по входу сброса выходным сигналом третьей.схемы И 57. Затем в циклическом режиме сигналы ЗБ с выхода второй схемы И 54 поступают на счетный вход счетчика 51 номера канала, наращивая его адрес на единицу. С выходов этого счетчика код адреса поступает на входы мультиплексора 52 сброса, работа которого разрешена только в циклическом режиме. сВ зависимости от запрограммированного числа . 8 цикле нл выходе мультиплексора 52 сброса появится сигнал после появления сигнала последнего номера канала в цикле.

30

40

45

50

55

,

5

5

0

35

0

40

45

50

55

Выходной сигнал этого мультиплексора сбрасывает триггер 56 измерения по входу R. В отличие от адресного режима на входе этого триггера .единичный сигнал,поэтому после установки триггера по входу S сигналом ИД в единичное состояние сигнал ЗБ, поступающий на вход С, оставляет его в этом состоянии, сброс триггера производится только по входу R. Единичный выходной сигнал триггера 56- измерения пропускает на запуск АЦП 21 через второй формирователь 65 все сигналы с выхода первого формирователя 62.

При рабо.те в циклическом режиме коммутации по каждому импульсу дискретизации ИД формируется Nk импульсов измерения, где М - число каналов в цикле, t периодом, равным длительности измерения.

В процессе регистрации в циклическом режиме для каждого канала будет, выполнено число дискре-.тизаций, за- Ч данных в программируемом счетчике 45 числа дискретизаций.

Для увеличения быстродействия при регистрации аналоговых входных сигналов возможно использование конвейерной выборки блоков выборки 17 и хранения 19 (ВХ).

Все аналоговые входы каждого блока 12 измерения аналоговых сигналов разбиты на две группы.

Первая и вторая группы аналоговых входов содержат по восемь каналов каждая. Два многоканальных блока (ВХ) 17 и 19 представляют собой многоканальные устройства, каждое из которых состоит из восьми блоков ВХ и управляется раздельными сигналами разрешения хранения РХ1.и РХ2, при подаче на вход блока ВХ сигнала РХ1 или РХ2 обеспечивается запоминание мгновенного значения измеряемого сигнала соответствующим блоком ВХ 17, 19. Два коммутатора 18 и 20 с объединенными выходами соединяют со входом АЦП 21 аналоговые сигналы, зафиксированные в блоках ВХ 17 и 19, Переключение каналов в обоих коммутатор X производится трехразрял- ным код.м номера канала, Формируемом счетчики. 51 номера канала, а разрешение работы каждого коммутатора производится соответствующими сиг: налами управления У1 и У2.

При работе с нормальной выборкой измеряемых входных сигналов подклю- i чаются на вход каждого из восьми каналов блоков ВХ 17 и 19. Сигналы управления коммутаторами У1 и У2 формируются триггером 58 управления, а разрешения ВУ, РХ1 и РХ2 - мультиплексором 53 управления ВХ„

На входы управления мультиплексора 50 управления коммутатором по- ступа гат сигналы Режим циклический (РЦ) и Выборка конвейерная (ВК) с выходов регистра 2 программ на информационные входы - выходы номера канала регистра Д2 программ и сигналы от шин питания таким образом, что если запрограммирован режим циклический и выборка нормальная (, ) , на первом выходе мультиплексора 50 управления коммутатором устанавливается нулевой сигнал, а на втором - единичный, но только, в том случае, если число каналов в цикле не превышает восемь.Выходные сигналы мультиплексор 50 управления коммутатором поступают на входы К и I триггера 58 управления, на выходах которого при поступлении на вход С импульсов дискретизации устанавливается единичный сигнал на первом выходе и нулевой на втором, т.е. выбирается первый коммутатор 18.

Если число каналов в цикле 16, . то с нулевого до восьмого канала работает первый коммутатор 18, при переходе на восьмой канал триггер 58 управления перебрасывается в исходное состояние, т.е. выбирается второй коммутатор 20, Мультиплексор 53 управления управляется сигналом - ВК и если выбррка нормальная, на оба выхода мультиплексора 53 управления проходит сигнал триггера $6 измерения и под воздействием сигналов оба блока ВХ 17 и 19 работают синхронно. После перевода обоих блоков ВХ 17 и 19 в режим хранения производится по20

25

При конвейерной выборке () две группы аналоговых входов 1 и 2 объединяются, каждый датчик подклю с чается на входы двух блоков ВХ 17 13 и. число входных измерительных к налов сокращается в два раза до восьми.

На обоих выходах мультиплексора 10 50 управления коммутатором устанав ливаотся единичные сигналы и триггер 58 управления начинает работат в счетном режиме, сиг-малы на его выходах У1 и У2 находятся в проти- 15 вофа зах, т.е. коммутаторы 18 и 20 выбираются поочередно. На оба выхода мультиплексора 53 управления УВХ проходят выходные сигналы триг ра 58 управления и сигналы РХ1 и РХ2 изменяются в соответствии с сигналами У1 и У2 и находятся таки в противофазе. В режим-, хранения находится один из блоков ВХ 17 и 1 включенный на вход выбранного кемму тато ра, другое находится в режиме выборки.

В момент фиксации значений вхол ных сигналов один из блоков ВХ переходит в режим хранения, а другой 30 в режим выборки. Выходы блоков ВХ, . находящихся в режиме хранения1, последовательно спрашиваются соответ ствующим коммутатором и измеряются AL JI 21 , в течение восьми циклов 35 преобразования.

После окончания игмерений быть произведена фиксация следующи значений входных сигналов по этим же каналам, т.е. время выборки бло 40 ка ВХ исключается из интервала вре мени измерения входного сигнала.

Если запрограммирован режим работы адресный и выборка нормальная 45 (, ВК-О), на первом выходе мул типлексора 50 управления коммутат.о ром устанавливается нулевой сигнал а на втором - единичный, Если номе выбранного канала меньше восьми, р

следовательное измерение входных сиг - 50 ботает первый коммутатор 18, если

0

5

При конвейерной выборке () . две группы аналоговых входов 1 и 2 объединяются, каждый датчик подклю- чается на входы двух блоков ВХ 17 и 13 и. число входных измерительных каналов сокращается в два раза до восьми.

На обоих выходах мультиплексора 50 управления коммутатором устанав- .. ливаотся единичные сигналы и триггер 58 управления начинает работать в счетном режиме, сиг-малы на его выходах У1 и У2 находятся в проти- 5 вофа зах, т.е. коммутаторы 18 и 20 выбираются поочередно. На оба выхода мультиплексора 53 управления УВХ проходят выходные сигналы триггера 58 управления и сигналы РХ1 и РХ2 изменяются в соответствии с сигналами У1 и У2 и находятся такие в противофазе. В режим-, хранения находится один из блоков ВХ 17 и 19 включенный на вход выбранного кем- му тато ра, другое находится в режиме выборки.

В момент фиксации значений вхол, ных сигналов один из блоков ВХ переходит в режим хранения, а другой - 0 в режим выборки. Выходы блоков ВХ, . находящихся в режиме хранения1, последовательно спрашиваются соответствующим коммутатором и измеряются AL JI 21 , в течение восьми циклов 5 преобразования.

После окончания игмерений быть произведена фиксация следующих значений входных сигналов по этим же каналам, т.е. время выборки бло- 0 ка ВХ исключается из интервала времени измерения входного сигнала.

Если запрограммирован режим работы адресный и выборка нормальная 5 (, ВК-О), на первом выходе мультиплексора 50 управления коммутат.о- ром устанавливается нулевой сигнал, а на втором - единичный, Если номер выбранного канала меньше восьми, ра

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к информационно-измерительной технике и может быть использрвано в автоматизированных измерительных системах регистрации быстропротекаюцих процессов. Цель изобретения - расширение функциональных возможностей путем графического.представления информации, управления режимом запуска от аналогового сигнала, внешнего

налов по всем каналам, коммутирующим коммутаторами 18, 20 в течение 16 циклов поробр-:1.овр.иия. После выполнения измерений по всем каналам оба блока ВХ 17, 19 переводятся в режим, выборки путем подачи сигналов . Временная диаграмма лля случая 16 каналов в цикле и нор- , мальной .- г.рЯоСмС - н иг.11,

номер канала больше восьми, работает второй коммутатор 20. Мультиплексор 53 управления блоком ВХ, как и & цик- личес ;с.м ре.ч .-члс с нсрмпль- ой 5 кой, пропускает на выходы сигналы триггера 56 измерения (), оба блока ВХ 17 и 19 работают синхронно. Временная диграмма приведена на фиг.13.

23

Если запрограммиоованы адресный t режим работы и конвейерная выборка (, ), то.работа происходит аналогично циклическому режиму с конвейерной выборкой. - . . .В системе предусмотрены расширенные возможности использования блока памяти.

Сигналы записи ЗБ на вход записи блока памяти 23 или 27 проходят с выхода третьей схемы ИЛИ 63, обеспечивая возможность записи -не только результатов измерения АЦП 21 в первом блоке 4 задания частот дискретизации или данных промежуточной памяти 25 во втором- блоке 5 задания частот дискретизации, но и возможность обращения и записи данных, хранящихся в памяти, например, результатов обработки измерений. В этом случае сигнал записи поступает на второй вход третьей схемы ИЛИ 63, при этом выдаются соответствующие сигналы управления на приемопередатчики 22 или 26 с выхода второго дешифратора 47 и инверсного выхода триггера 56 измерений, которые при отсутствии Процесса измерений в системе разрешают передачу данных с шины 16 данных ЭВМ на вход блока 23 или 27 памяти.

Соответственно предусмотрена выдача адреса блоков 23 или 27 памяти, либо от счетчика 64 адреса, либо непосредственно с шины 10 адресов ЭВМ с помощью мультиплексора 48 адреса. При записи результатов измерений сигнал ЗБ с выхода первого формирова , теля 61 поступает на счетный вход |счетчика. 64 адреса. В исходное нулевое состояние счетчика 6k адреса блока памяти устанавливается сигналом предварительного пуска с выходаj седьмой схемы И 71, где стробируется сигналом блочной записи с выхода регистра 42 программ, который запрещает сброс.

Выходной код счетчика 64 адреса поступает на первые входы мультиплексора 48 адреса, а с его выхода - на адресные входы блоков 23 или 27 памяти. На вторые входы поступает адрес непосредственно с шины 10 адресо ЭВМ. Управление направлением передачи мультиплексора 48 адреса осущест- вляется выходным управляющим сигнало второго дешифратора 47

Число измерений в адресном или цилическом режимах программируется и

|

10

15

20

25

t о

-j ков- 5г ом

70754624

г

| может быть меньше полного объема памяти. Предусматривается возможность - использования оставшейся свободной части памяти для хранения результатов следующей серии измерений или, например, результатов обработки. Для этого в регистр 42 программ записывается режим Блочная запись, который запрещает сброс счетчика 64 адреса по сигналу предварительного пуска очередной серии измерений и осуществляется их запись в оставшуюся свободную часть памяти. Если производится запись данных, адрес с выхода счетчика 64 адреса может быть прочитан и произведена запись с начального адреса свободной зоны памяти. Адрес с выхода счетчика 64 адреса поступает на вход вентилей 46 адреса, с выхода которого он выходит на внутреннюю магистраль данных при наличии управляющего сиг- нала4 с выхода второго дешифратора 47, проходящего через шестую схему И 68, где стробируется сигналом отсутствия измерений с инверсного выхода триггера 56 измерений. -После записи измеренной входной аналоговой или цифровой информации производится ее чтение в программном обмене с ЭВМ. Кроме того, предусмотрена работа в режиме прерывания - по инициативе самого устройства.с выдачей сигнала по шине 7 прерываний.

Возможны три вида прерываний: прерывание по концу каждого измерения, сигналом прерывания является готовность АЦП 21 в первом блоке 4 задания частот дискретизации или счетчика 28 промежуточной памяти во втором блоке 5 задания частот дискретизации f используется в адресном и циклическом режимах4, прерывание по концу цикла коммутации на выбранной группе каналов, сигналом прерывания является выходной сигнал триггера 56 измерений, используется в циклическом режиме прерывание по концу запрограммированного числа дискретизаций, сигналом прерывания я в-

30

35

40

45

50

ляется сигнал конца программы, ис- пользуетгя в адресном и циклическом режимах,

Сигнал чтения (МБ) представляв г собой управляющий сигнал с выхода второго дешифратора 47, проходящий через пятую схему И 64, где строби25

руется сигналом отсутствия измерений с инверсного выхода триггера 53 измерений. С выхода пятой схемы И 67 сигнал ЧВ поступает на вход чтения блока 23 или 27 памяти.

Система обеспечивает регистрацию как аналоговых, так и цифровых входных сигналов от одинаковых блоков k и 5 задания частот дискретизации,.

Для регистрации входных цифровых сигналов используется блок 13 регистрации цифровых сигналов (фигг.З) и блок 5 задания частот дискретизации, аналогичный блоку 4 (фиг.5).

Третья группа входов 3 системы предназначена для регистрации цифровых входных сигналов.

При поступлении сигнала ЗП от блока 5 задания частот дискретизации на вход с второго триггера 33 на его выходе устанавливается единичный уровень напряжения. По переднему фронту импульса ИГ с выхода генератора 1 тактовых импульсов, частота которых превышает частоту измерений, на выходе первого триггера 32 устанавливается единичный уровень напряжения и тем самым разрешается прохождение импульса1сброса мерез первую схему И 3i на счетчик 28 адреса промежуточной памяти. Одновременно сбрасывается второй триггер 33.

По переднему фронту каждого следующего импульса ИГ сбрасывается первый триггер 32 и импульсы ИГ через схему 29 НЕ-И воздействуют на счетный вход счетчика 28 адреса промежуточной памяти и через схему задержки 30 на вход записи промежуточной памяти 25. При этом выходы счетчика 28 адреса промежуточной памяти выставляют адрес ячейки промежуточной памяти 25 и управляют мультиплексором 2k цифровых входов.

Таким образом, за промежуток времени Т, равный

N

п+ Чпп

).

где NK

t

МП

- число каналов

- время задержки в мультиплексоре у tjnn - время записи в промежутоную память

происходит запись с тактовой частотой цифрового сигнпла по каналам в промежуточную память 25. По окон- чании записи выдается сигнал готовности И, который воспринимается

7075 62-6

блоком 5 задания частот дискретизации. ч

По сигналу готовности Г.1 блок 5 производит передачу содержимого промежуточной памяти 25 в блок памяти 27 и выдает следующий сигнал запуска ЗП„

Динамическая погрешность преястав- ляет собой погрешность датирования, связанную с недостаточной временной привязкой начала регистрации нескольких входных цифровых сигналов.к единому моменту времени,

Погрешность датирования регистрации цифровых сигналов:

: kg Njt ), .

10

15

0

5

0

5

0

5

0

5

где 11П - время записи в память.

Уменьшение погрешности датирования достигается за счет уменьшения времени t , так как промежуточная пэ- мять может быть построена На инте- тральных микросхемах быстродействующей памяти; имеющих существенно бог лее BfciCOKoe быстродействие, чем блок памяти, основным требованием к которому является большой объем памяти.

Поэтому twnЈ t гп.

Предусмотрен вывод информационно массива в виде графиков на экран графического индикатора или на графопостроитель с использованием блока 15 отображения (фиг.6).

ь

Первый дешифратор 9 при соответствующем адресе-на шине 10 адресов ЗВК и наличии управляющих сигналов вырабатывает сигнал выбора блока 15 отображения, который разрешает работу третьего дешифратора 78„ ,

Третий дешифратор 78 под воздействием управляющих сигналов ввода или вывода вырабатывает сигналы управления отдельными функциональными узлами. Второй формирователь 82 ответа при наличии обращения к блоку |15 воспринимает выходной сигнал третьего дешифратора и выдает ответный сигнал обмена с ЭВМ по шине - 8 .управления с задержкой относительно

сигналов обращения ввода или вывода, ответный сигнал- выдается по сигналу готовности третьего блока ВО памяти, поступающему на второй вход GJOpCTC фОрМЧрСРмТеЛЛ 62 OTROT i. ЛйНные . определяю -;; режим (5г;л:са 15 с графическим индикатором или

.графопостроителем запоминаются и хра27 . - :117075 6

нятся в регистре 83 команд. Данные записываются в него под воздействием сигнала записи, вырабатываемого третьим дешифратором 78. В регистр 83 команд данные записываются с внут- .ренней магистрали через третий приемопередатчик 87, обеспечивающий связь с шиной 16 данных ЭВМ. Сигналы

управления приемопередатчиком 87 так- ю ителем. В этом случае открывается

же вырабатываются третьим .дешифратором 78.

Запись данных в третий блок 80 памяти производится через внутреннюю магистраль под воздействием управляющего сигнала с выхода третьего дешифратора 78 Адрес блока 80 памяти, куда записываются данные, выставключ 92, подключающий выходы ЦАП 89 и 90 к входам координаты X и Y графопостроителя. В счетчик 8 координаты X выходным сигналом тре1$ тьего дешифратора. 78 записывается адрес ячейки блока 80 памяти через третий приемопередатчик 87, а в регистр 85 координаты Y выходным сигналом третьего дешифратора 78 за-

20 писывается содержимое ячейки блока 80 памяти, адрес которой поступает из счетчика 84 координаты X. ЦАП 89 и 90 выдают постоянное напряжение на входы координат X и У Урафопо25 строителя . Подъем пера в графопостроителе осуществляется по команде, записанной в регистр 83 команд. Этот сигнал с выхода регистра 83 поступает на ключ 93 и через усилиформирует импульсы 30 тель 9 мощности управляет подъемом

пера в графопостроителе.

ляетвторой мультиплексор 79 адреса. Управляющий сигнал направления передачи вырабатывается четвертой схемой ИЛИ 86 при наличии сигналов ввода или вывода от ЭВМ. В этом случае адрес ячейки блока 80 памяти выводится с шины 10 адресов ЭВМ. В системе предусмотрен режим автоматического вывода графика на экран графического индикатора. В регистр 83 команд записывается признак этого режима. Фазовый генератор {

цикла индикации, поступающие на вход седьмого формирователя 81. Этот формирователь обеспечивает последовательное чтение ячеек блока 80 памяти и в каждом цикле индикации выдает сигнал $$ чтения и конца цикла, а дешифратор 78 при наличии признака этого режима, наличии сигнала готовности и отсутствии сигнал-з конца цикла вырабатывает сигнал записи в регистр 85 40 координаты Y. В-результате в регистре 85 запоминается значение.координаты Y из той ячейки памяти блока 80 памяти, адрес которого устанавливает счетчик 84 координаты X через 45 мультиплексор 79 адреса. Одновременно из счетчика 84 координаты X данные поступают на вход второго ЦАП 89 а данные с выхода регистра 83 координаты Y - на вход третьего ЦАП 90, 50 и преобразованные в аналоговый сигнал напряжения выдаются на входы координат X и Y графического индикатора. Напряжение оперы ЦЛП 39 и 90 псФормула изобретения

1 „ Многоканальная система измерения и регистрации , .содержащая п первых и п вторых блоков задания частот дискретизации по числу групп аналоговых.и цифровых входов, дешифратор, первая группа входов которого соединена с шиной адресов, вторая группа входов с входной шиной управления, а 2п выходов соединены с п входами записи первых и вторых блоков задания частот дискретизации, п блоков измерения аналоговых сигналов, каждый из которых содержит аналого-цифровой преобразователь, информационные выходы которых соединены с информационными входами - выходами первого буферного запоминающего блока, блок синхронизации, содержащий генератор тактовых им- п льсоз, о т л и ц a w щ л к с я тем,

ступает с выхода источника 91 опорно- 55 что с челью расширения функциональго напряжения. В конце каждого цикла индикации седьмой формирователь 81 вырабатывает соответствующий сигнал, поступающий на счетный вхол счетчиных возможностей, уменьшения динамической погрешности и повышения быстродействия при регистрации аналоговых сигналов и уменьшения погоеш28

ка 84 координаты X, инкрементируя адрес блока 80 памяти, происходит последовательное чтение ячеек блока 80 памяти и на экран индикатора выводится в виде графика данных.

При работе с графопостроителем в регистре 83 команд программно записывается признак работы с графопостроФормула изобретения

1 „ Многоканальная система измерения и регистрации , .содержащая п первых и п вторых блоков задания частот дискретизации по числу групп аналоговых.и цифровых входов, дешифратор, первая группа входов которого соединена с шиной адресов, вторая группа входов с входной шиной управления, а 2п выходов соединены с п входами записи первых и вторых блоков задания частот дискретизации, п блоков измерения аналоговых сигналов, каждый из которых содержит аналого-цифровой преобразователь, информационные выходы которых соединены с информационными входами - выходами первого буферного запоминающего блока, блок синхронизации, содержащий генератор тактовых им- п льсоз, о т л и ц a w щ л к с я тем

ных возможностей, уменьшения динамической погрешности и повышения быстродействия при регистрации аналоговых сигналов и уменьшения погоеш

ности при регистрации цифровых сигналов, в нее введены п блоков регис- рации цифровых сигналов и блок отображения, информационные входы которых соединены с информационными входами блоков измерения аналоговых сигналов и блока синхронизации и шиной данных причем в каждый из п блоков измерения аналоговых сигналов введены два ПОСЛС довательно соединенных блока выборки и хранения и коммутатора, входы которых соединены с первой и второй группами аналоговых входных сигналов, и первый приемопередатчик, при этом выходы первого и второго коммутаторов соединены между собой и с информационным входом аналого-цифро- вого преобразователя, первая группа входов-выходов первого приемопередатчика соединена с шиной данных, а вторая с информационными входами- выходами первого буферного запоминающего блока и информационными выходами аналого-цифрового преобразователя, в каждый из п блоков регистрации цифровых сигналов введены мультиплексор цифровых входов, входы ;которого соединены с цифровыми входами системы промежуточная память, информационные входы которой соединены с информационными выхоДами мультиплексора цифровых входов, второй приемопередатчик, второй буферный запоминающий блок, счетчик адреса промежуточной памяти, схема НЕ-И,- .схема задержки, схема И, два триггера, причем первая группа входов-выходов второго приемопередатчика соединена с шиной данных,вторая группа входов-выходов соединена с информационными выходами промежуточном памяти и информационными входами-выходами второго буферно-запоминающе- го блока, управляющие входы мультиплексора цифровых входов соединены с адресными входами записи промежуточной памяти и соединены с первой группой выходов счетчика адреса промежуточной памяти, второй выхо д которого соединен с первым входом схемы HE-Mj выход которой соединен со счетным входом счетчика адреса промежуточной памяти и входом схемы

ЗаДСр;: .:-1 f UtlXC-Д Которой СОеДННСН С

входом записи промежуточной г: смят и, второй вход схемы НЕ-И соединен с первым входом первой схемы И, выхо дом генератора тактовых импульсов

5

0

5

0

5

0

5

0

5

блока синхронизации и С-входом первого триггера, инверсный выход которого соединен cR-входом второго триггера.выход которого соединен с D-входом первого триггера, прямой выход которого соединен с вторым входом первой схемы И, выход первой схемы И соединен с входом сброса счетчика адреса промежуточной памяти,

бходы записи регистра программ, трех программируемых счетчиков соединены с первым, вторым, третьим и четвертым выходами второго дешифратора, первая группа входов которого соединена с шиной адресов и первой группой входов мультиплексора адреса буферно- запоминающего блока, вторая группа входов-выходов второго дешифратора соединена с входной шиной управления третий вход - с одним из 1п выходов первого дешифратора в первом блоке задания частот дискретизации и одним ,из 2п выходов этого дешифратора во втором блине.. задания частот дискретизации , пятый выход второго дешифратора соединен с первым входом формирователя ответа, выход которого соединен с выходной шиной управления, первая группа выходов регистра программ соединена с первой группой входов мультиплексора управления коммутатором, счетчика номера канала и мультиплексора сброса, второй выход регистр программ соединен с вторым входом мультиплексора управления коммутатором, первым входом мультиплексора управления блока выборки и хранения, третий выход регистра программы соединен с третьим входом, мультиплексора управления коммутатором, входом управления мультиплексора сброса, первым входом второй схемы И, входом инвертора, D-входом триггера измерения и первым входом третьей схемы И, четвертый и пятый входы мультиплексора управления коммутатором подключены к шинам питания а его первый и второй выходы - к К- и I-входам триггера управления, прямой и инверсный выходы которого соединены с вторым и третьим входами мультиплексора управления блока выборки и хранения и в первом блоке за дания частот дискретизации с входами управления первого и второго коммутаторов, выходы мультиплексора управления блока выборки и хранения соединены в первом блоке задания -vac тот дискретизации с входами первого и второго блоков- выборки и хранения, выходы счетчика номер канала соединены с информационным входами мульч

типлексора сброса и в первом блоке задания частот дискретизации с адресными входами коммутаторов, а во втором блоке задания частот дискретизации с адресными входами чтения

JQ 15 20 25 30 .,, 40 45 g

55

промежуточной памяти, выход инвертора соединен с первым входом четвертой схемы И, второй вход которой соединен с S-входом триггера измерения, С-входом триггера управления, вторым входом третьей схемы И, первым входом второй схемы ИЛИ и первым выходом пер вой группы схем И-Г1ЛИ, выход мультиплексора сброса соединен с R-вхо- дом триггера измерения, С-вход которого соединен с вторым входом второй схемы И, с первым выходом первого формирователя, первым входом третьей схемы ИЛИ и счетным входом счетчика адреса буферного запоминающего блока, первый вход первого формирователя соединен с шиной прерываний и в первом блоке задания частот дискретизации с выходом готовности аналого-Циф- рового преобразователя, а во втором блоке задания частот дискретизации- с вторым выходом счетчика адреса промежуточной памяти, второй вход первого формирователя соединен с вторым входом формирователя ответа и выходом готовности первого или второго буферно-запоминающего блока для первого или второго блоков задания час- стот дискретизации соответственно ход третьей схемы ИЛИ соединен с входом записи первого или второго буферного запоминающего блока для первого или второго блоков задания час-1- тот дискретизации соответственно, счетный вход счетчика номера канала соединен с выходом второй схемы И, вход записи - с выходом четвертой схемы И, а вход сброса - с выходом третьей схемы И, прямой выход триггера измерения соединен с четвер- тым входом мультиплексора управления блока выборки и хранении, с первым входом второго формирователя, первым входом третьего формирователя, .шиной прерываний и с входом чтения аналого-цифрового преобразователя для первого блока задания частот дискретизации или с входом чтения промежуточной памяти для второго блока задания частот дискретизации, второй вход второго формирователя соединен с вторым выходом первого формироаателя, пеовый вхол пятой схемы И соединен с шестым выходом второго дешифратора, седьмой выход которого соединен с входом управления мультиплексора адреса буферно- запоминающего блокл, восьно й выхо д - с первым входом управления первого или второго приемопередатчиков для первого или второго блока задания частот дискретизации соответственно; девятый выход - с первым входом шестой схемы И, второй вход которой соединен с инверсным выходом триггера измерений, вторым входом пятой схемы И, С-входом триггера регистрации и вторым входом управления первого или второго приемопередатчиков, а выход шестой схемы И - с входом управления вентилей адреса, десятый выход второго дешифратора соединен с вторым входом третьей схемы ИЛИ, выход п я- той схемы И соединен с входом чтения первого или второго буферно- запоминающего блока для первого или второго блоков задания частот дискретизации соответственно, выход второго формирователя соединен с вторым входом второй схемы ИЛИ, выход которой соединен с входом запуска аналого-цифрового преобразователя для первого блока задания час- тот дискретизации или С-входом второго триггера для второго блока задания частст дискретизации, S-вход :триггера регистрации соединен с пе вым выходом Четвертого формировате- ля, первые два входа которого сое- динены с четвертым и пятым выходами регистра программ, третий вход - с выходом программируемогс счетчика задержки, четвертый вход-- с первым входом седьмой схемы И, первым входом формирователя предпуска и четвертым гыходом регистра способа запуска блока синхронизации, пятый вход - с входом разрешения программируемого счетчика задержки и выходом пятого формирователя, шестой вход - с вторым входом формирователя предпуска, первыми входами пятого формирователя и формирователя пуска и еыхоломтриггера счета, D-вход триггера регистрации соединен с вторым входом третьего фбр- мирователя, первым входом шестого формирователя, выходом программируемого счетчика числа дискретизаций и шиной прерываний, третий вход третьего формирователя соединен с вторым выходом четвертого форг..о- вателя, второй вход шестого формирователя соединен с третьим выходом четвертого формирователя, третий

20

вход - с выходом триггера регистрации и первым входом первой группы ххем И-ИЛИ, второй и третий входы которой соединены с первым и вто- рым выходами программируемого счетчика частоты, четвертый вход - с первым выходом шестого формирователя и входом разрешения второго канала

1f) программируемого счетчика частоты, вход разрешения первого канала которого соединен с выходом третьего формирователя, второй выход первой группы схем И-ИЛИ соединен с товымм входами программируемых

счетчиков задержки и числа дискретизации, второй выход шестого формирователя соединен с входом разрешения программируемого счетчика числа дискретизации, третий выход - с R-входом триггера счета, С-вход которого соединен с вторым в ходом формирователя пуска, третьим входом формирователя предпуска , пер25 вым входом второй группы схем И-ИЛП и выходом генератора тактовых им- пульсов, второй вход пятого формирователя соединен с тактовыми входами первого и второго каналов прогрэм30 мируеиого счетчика частоты и BI;XO- дом второй группы схем И-ИЛИ, втог.-м вход которой соединен с седьмым выходом регистра программ, а третий вход - с шиной внешнего тактирования, I-вход триггера счета сойди-.. нен с выходом формирователя пуска, третий вход которого соединен с выходом первой схемы ИЛИ блска синхронизации, а четвертый - с выходом

4Q формирователя предпуска, второй вход седьмой схемы И соединен с шестым выходом регистра программ, а ее выход- .с входом установки счетчика адреса буферно-запоминающего блока, выходы

45 счетчика адреса буферно-запоминающе- го блока соединены с второй группой входов мультиплексора адреса бу- ферно-запсминающего блока, выходы, которого соединены с адресными входами первого или второго буферно- запоминающего блока для первого или второго блоков задания частот дискретизации соответственно.

. Система по п. 1 , о т л и ч аю- щ а я с я тем, что блок аналогового вывода содержит третий дешифратор, второй мультиплексор адреса иу ферно-запоминоющего блока, третий ..буферно-запрминающчй блок, седьмой

35

50

55

формирователь, второй формирователь ответа, регистр команд, счетчик координаты X, регистр координаты Y, четвертую схему ИЛИ, третий приеме- передатчик, фазовый генератор, два цифроаналоговых преобразователя, источник опорного напряжения, два ключа и усилитель мощности, причем первая группа входов третьего дёшифра- тора соединена с входной шиной управления, вторая группа входов - с шиной адресов и первой группой входов второго мультиплексора адреса буферно-запо минающего блока, третий вход - с 2п+3 выходом первого дешифратора, четвертый вход с выходом третьего буферно-запоминакнцего блока и первыми входами седьмого формирователя и второго формирователя ответа, пятый вход - с вторым входом седьмого формирователя и переым выходом регистра команд, шестой вход - с пер- вым выходом седьмого формирователя и счетным входом счетчика координаты X, первые три выхода третьего дешифратора соединены с входами записи регистра команд, счетчика координаты X, регистра координаты Y, четвертый выход соединен с вторым входом вто- рого формирователя ответа, выход которого соединен с выходной шиной управления, пятый вход - с первым управляющим входом третьего буферно- запоминающего блока и первым входом четвертой схеуы ИЛИ, шестой выход - с первым входом третьего приемопередатчика, седьмой - с вторым входом четвертой схемы ИЛИ, третьим входом седьмого формирователя и вторым

входом третьего приемопередатчика, первая группа входов-выходов которого соединена с шиной данных, а вторая группа входов-выходов - с информационными входами регистра команд, счетчика координаты X, регистра координаты Y и группой входов-выходов третьего буферно-запоминающего блока, адресные входы которого соединены с выходами второго мультиплексора адреса буферно-запоминающего блока, второй управляющий вход третьего буферно-запоминающего блока соединен с вторым выходом седьмого формирователя, четвертый .вход которого соединен с выходом фазового генератора выход четвертой схемы ИЛИ соединен с управляющим входом второго мультиплексора адреса буферно-запоминающего блока, вторая группа входов кото рого соединена с информационными выходами счетчика координаты X и входами второго цифроаналогового преобразователя, вход опоры которого соединен с входом опоры третьего цифро- аналогового преобразователя и выходо источника опорного напряжения, входы третьего цифроаналогового преобразователя соединены с выходами регистра координаты Y, выходы первого и второго цифроаналоговых преобразователей соединены с первыми двумя входами первого ключа, третий вход которого соединен с вторым выходом регистра команд, третий выход которого соединен с входом второго ключа, последовательно соединенного с усилителем мощности.

1 гпф

к

I trj

-ii. 7е.

: . i.л.

calI -

jgj|

:1

uodau dufi

91 ,

17C75 6

Аналоговый сигнал нсо УроВень запуска

ГР

fe /7

injTJTTj LriJ Фие.9

Фиг.7

Фиг.8

I7075 i6

иг jinnjTjuinnj пп

CV Р7

WlJWh PezJS

РЗ

ил зл

-ц-----

I

3/7 л ьжжи1шт1ш-шгжгжвшишг

w ш

фие.Ю т

j-т.

Фие.Г;

t

фие.П

т зя

п

36

ии

fe.

U Ц TJ LT

0tfc. /J

| Авторское свидетельство СССР № , кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| г () МНОГОКАНАЛЬНАЯ СИСТЬИА ИЗМЕРЕНИЯ И РЕГИСТРАЦИИ | |||

Авторы

Даты

1992-01-23—Публикация

1988-10-11—Подача