112

Изобретение относитсг к вычислительной технике, в частности к технике запоминающих устройств, и может быть использовано для контроля блоков аналоговой памяти.

Целью изобретения является повышение быстродействия устройства.

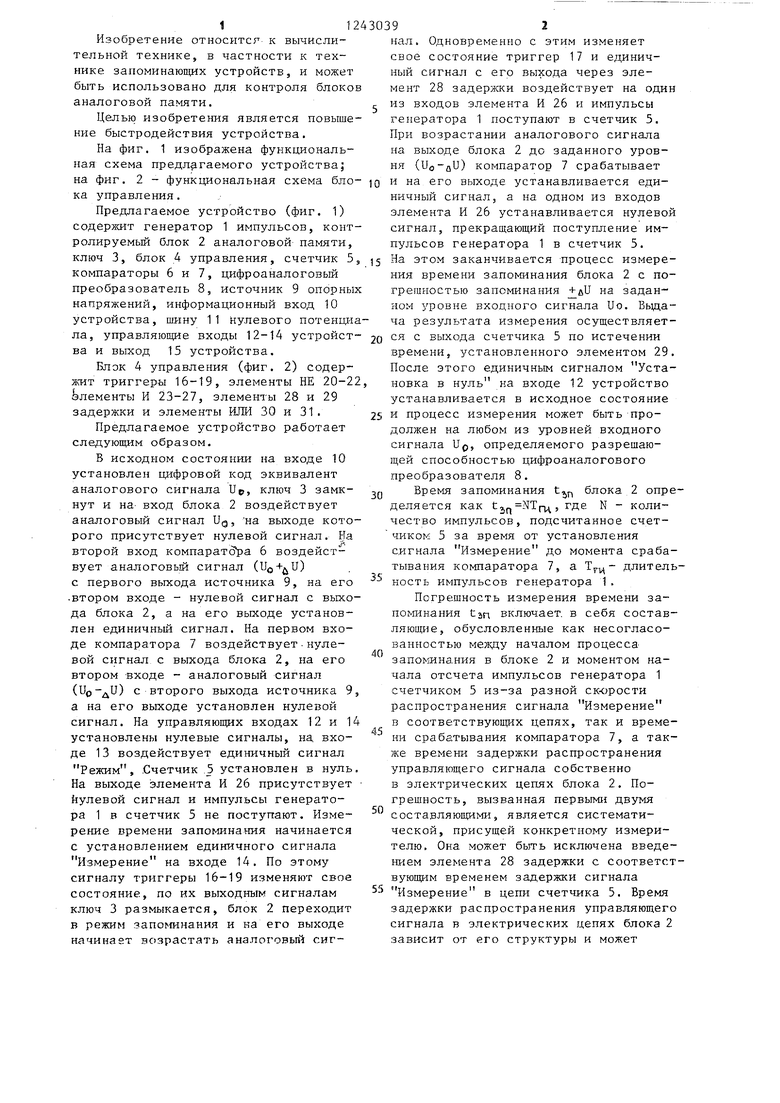

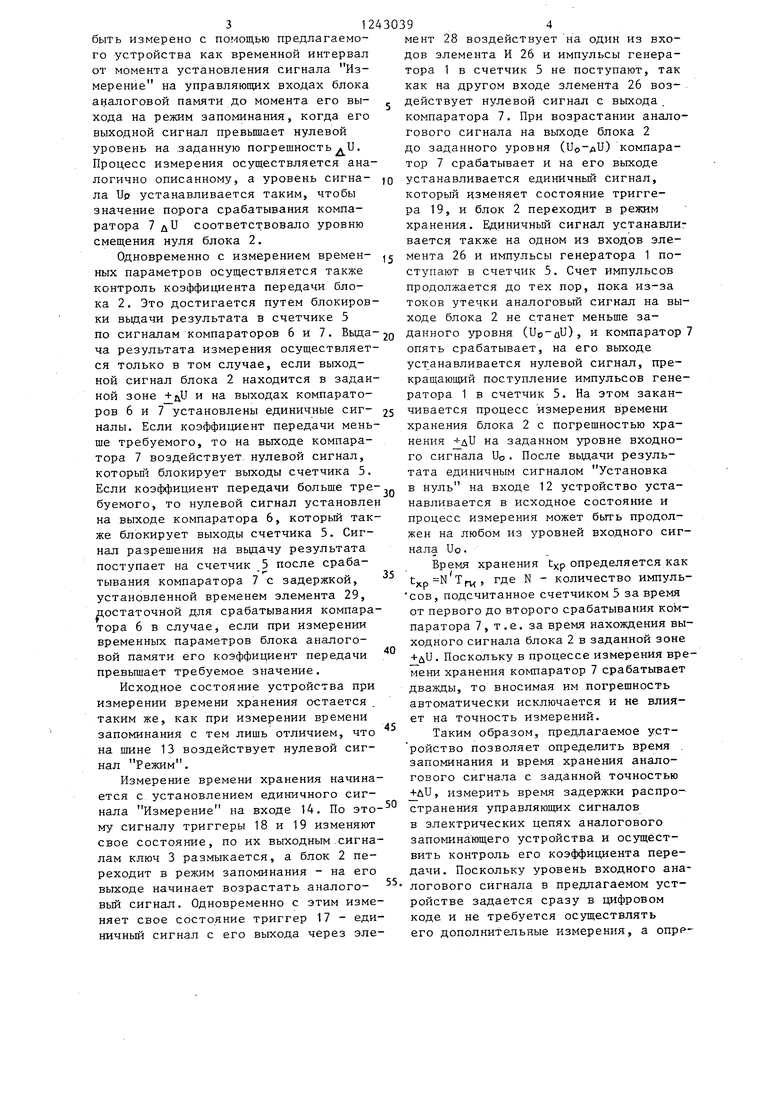

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления.

Предлагаемое устройство (фиг, 1) содержит генератор 1 импульсов, контролируемый блок 2 аналоговой памяти, ключ 3, блок 4 управления, счетчик 5, компараторы 6 и 7, цифроаналоговый преобразователь 8, источник 9 опорных напряжений, информационный вход 10 устройства, шину 11 нулевого потенциала, управляющие входы 12-14 устройства и выход 15 устройства.

Блок 4 управления (фиг. 2) содержит триггеры 16-19, элементы НЕ 20-22 Элементы И 23-27, элементы 28 и 29 задержки и элементы ИЛИ 30 и 31.

Предлагаемое устройство работает следующим образом.

В исходном состоянии на входе 10 установлен цифровой код эквивалент аналогового сигнала Up, ключ 3 замкнут и на вход блока 2 воздействует аналоговый сигнал Ug, на выходе которого присутствует нулевой сигнал. На второй вход компарато ра 6 воздействует аналоговьй сигнал () с первого выхода источника 9, на его -втором входе - нулевой сигнал с выхода блока 2, а на его выходе установлен единичный сигнал. На первом входе компаратора 7 воздействуетнулевой сигнал с выхода блока 2, на его втором -входе - аналоговый сигнал (иф-ди) с второго выхода источника 9, а на его выходе установлен нулевой сигнал. На управляющих входах 12 и 14 установлены нулевые сигналы, на входе 13 воздействует единичный сигнал Режим, .Счетчик .5 установлен в нуль. На выходе :элемента И 26 присутствует йулевой сигнал и импульсы генератора 1 в счетчик 5 не поступают. Измерение времени запоминания начинается с установлением единичного сигнала Измерение на входе 14. По этому сигналу триггеры 16-19 изменяют свое состояние, по их выходным сигналам ключ 3 размыкается, блок 2 переходит в режим запоминания и на его выходе начинает возрастать аналоговьй сиг92

нал. Одновременно с этим изменяет свое состояние триггер 17 и единичный сигнал с его выхода через элемент 28 задержки воздействует на один

из входов элемента И 26 и импульсы генератора 1 поступают в счетчик 5. При возрастании аналогового сигнала на выходе блока 2 до заданного уровня (UO-QU) компаратор 7 срабатывает

и на его выходе устанавливается единичный сигнал, а на одном из входов элемента И 26 устанавливается нулевой сигнал, прекращающий поступление импульсов генератора 1 в счетчик 5.

На этом заканчивается процесс измерения времвни запоминания блока 2 с погрешностью запоминания ,V на заданном уровне входного сигнала Uo. Выда- la результата измерения осуществляется с выхода счетчика 5 по истечении времени, установленного элементом 29. После этого единичным сигналом Установка в нуль ка входе 12 устройство устанавливается в исходное состояние

и процесс измерения может быть продолжен на любом из уровней входного сигнала Up, определяемого разрешающей способностью цифроаналогового преобразователя 8.

Время запоминания t блока 2 определяется как , где N - количество импульсов, подсчитанное счетчиком 5 за время от установления сигнала Измерение до момента срабатывания компаратора 7, а - длительность импульсов генератора 1 .

Погр€ .шность измерения времени запоминания tan включает, в себя составляющие, обусловленные как несогласованностью мелсду началом процесса запоминания в блоке 2 и моментом начала отсчета импульсов генератора 1 счетчиком 5 из-за разной скорости распространения сигнала Измерение в соответствующих цепях, так и времени срабатывания компаратора 7, а также времени задержки распространения управляющего сигнала собственно в электрических цепях блока 2. Погрешность, вызванная первыми двумя составляющими, является систематической, присущей конкретному измерителю. Он:а может быть исключена введением элемента 28 задержки с соответствующим временем задержки сигнала

Измерение в цепи счетчика 5. Время задержки распространения управляющего сигнала в электрических цепях блока 2 зависит от его структуры и может

быть измерено с помощью предлагаемого устройства как временной интервал от момента установления сигнала Измерение на управляющих входах блока аналоговой памяти до момента его выхода на режим запоминания, когда его выходной сигнал превышает нулевой уровень на заданную погрешностьдЧ. Процесс измерения осуществляется аналогично описанному, а уровень сигнала Up устанавливается таким, чтобы значение порога срабатывания компаратора 7 ди соответствовало уровню смещения нудя блока 2.

Одновременно с измерением временных параметров осуществляется также контроль коэффициента передачи блока 2. Это достигается путем блокировки выдачи результата в счетчике 5

по сигналам компараторов 6 и 7. Выда-2о данного уровня (Uo-aU), и компаратор 7

ча результата измерения осуществляется только в том случае, если выходной сигнал блока 2 находится в заданной зоне +uU и на выходах компараторов 6 и 7 установлены единичные сиг- налы. Если коэффициент передачи меньше требуемого, то на выходе компаратора 7 воздействует нулевой сигнал, которьм блокирует выходы счетчика 5. Если коэффициент передачи больше требуемого, то нулевой сигнал установлен на выходе компаратора 6, которьш также блокирует выходы счетчика 5. Сигнал разрешения на выдачу результата поступает на счетчик 5 после срабатывания компаратора 7 с задержкой, установленной временем элемента 29, достаточной для срабатывания компаратора 6 в случае, если при измерении временных параметров блока аналоговой памяти его коэффициент передачи превьшгает требуемое значение.

Исходное состояние устройства при измерении времени хранения остается таким же, как при измерении времени запоминания с тем лишь отличием, что на шине 13 воздействует нулевой сигнал Режим.

Измерение времени хранения начинается с установлением единичного сигнала Измерение на входе 14. По этому сигналу триггеры 18 и 19 изменяют свое состояние, по их выходным сигналам ключ 3 размыкается, а блок 2 переходит в режим запоминания - на его выходе начинает возрастать аналого- вый сигнал. Одновременно с этим изменяет свое состояние триггер 17 - единичный сигнал с его выхода через эле

мент 28 воздействует на один из входов элемента И 26 и импульсы генератора 1 в счетчик 5 не поступают, так как на другом входе элемента 26 воздействует нулевой сигнал с выхода компаратора 7. При возрастании аналогового сигнала на выходе блока 2 до заданного уровня (Uo-AU) компаратор 7 срабатывает и на его выходе устанавливается единичньш сигнал, который изменяет состояние триггера 19, и блок 2 переходит в режим хранения. Единичньш сигнал устанавливается также на одном из входов элемента 26 и импульсы генератора 1 поступают в счетчик 5. Счет импульсов продолжается до тех пор, пока из-за токов утечки аналоговый сигнал на выходе блока 2 не станет меньше за

5 .

5

опять срабатывает, на его выходе устанавливается нулевой сигнал, пре- кращаюшдй поступление импульсов генератора 1 в счетчик 5. На этом заканчивается процесс измерения времени хранения блока 2 с погрешностью хранения -i-ди на заданном уровне входного сигнала Uo. После выдачи результата единичным сигналом Установка в нуль на входе 12 устройство устанавливается в исходное состояние и процесс измерения может быть продолжен на любом из уровней входного сигнала Uo.

Время хранения определяется как , где N - количество импуль- сов, подсчитанное счетчиком 5 за время от первого до второго срабатывания компаратора 7, т.е. за время нахождения выходного сигнала блока 2 в заданной зоне . Поскольку в процессе измерения времени хранения компаратор 7 срабатывает дважды, то вносимая им погрешность автоматически исключается и не влияет на точность измерений.

Таким образом, предлагаемое уст- ройство позволяет определить время . запоминания и время хранения аналогового сигнала с заданной точностью jHiU, измерить время задержки распространения управляюш:их сигналов в электрических цепях аналогового запоминающего устройства и осуществить контроль его коэффициента передачи. Поскольку уровень входного аналогового сигнала в предлагаемом устройстве задается сразу в цифровом коде и не требуется осуществлять его дополнительные измерения, а опррделение каждого из параметров блока аналоговой памяти производится за один такт работы-измерителя, то по сравнению с известным устройством изобретен|{е отличается быстродействием.

Формула изобретения

| етвертым входами блока управления, выходы первого и второго элементов НЕ соединены соответственно с первыми входами: первого и второго злементовИ второй вход первого элемента И соеди нен с входом.второго элемента НЕ, второй вход второго элемента И и пер вый вход третьего элемента И соедине ны, соответственно с выходами первого

1. Запоминающее устройство с самоконтролем, содержащее блок аналоговой JQ триггера, первьш вход которого явля- памяти, первый выход которого соеди- ется первым входом блока управления ней с первьм входом ключа, второй и соединен с первым входом первого вход ключа соединен с первым выходом элемента РШИ, первым входом второго блока управления, выход ключа соеди- триггера и первым входом третьего нен с шиной нулевого потени 1ала, пер- 5 триггера, второй вход первого тригвый компаратор, генератор импульсов, счетчик, выход которого является выходом устройства, первый, второй и третий входы блока управления являются первым, вторым и третьим входами устройства, отличающее с я тем, что, с целью повьшения быстродействия устройства, в него введены второй компаратор и источн.ик опорных напряжений, вход которого является информационным входом устройства, второй выход блока аналого- }3ой памяти соединен с первыми входам компараторов, вторые входы которых соединены соответственно с первым и вторым вьгходами источника опорных напряжений, выходы компараторов соединены соответственно с четвертым и пятым входами блока управления, шестой вход которого соединен с выходом генератора импульсов, первый вход блока аналоговой памяти соединен с третьим выходом источника опорных

3Q торого соединен с первым входом четвертого элемента И, второй вход четвертого элемента И является шестым входом блока управления, выход второго элемента ИЛИ соединен с входом третьего элемента НЕ и третьим входом четвертого элемента И, выход которого является третьим выходом блока управления, выход третьего элемента НЕ соединен с первым входом пятонапряжений, второй выход блока управления соединен с вторым входом блока , го элемента И, второй вход которого аналоговой памяти, третий ц четвер- является пятым входом блока управле- тьш выходы блока управления соединены соответственно с первым и вторым входами счетчика, третий вход которого соединен с первым входом блока управления,

2. Устройство по п. 1, о т л и - чающееся тем, управления содержит элементы И, элементы задержки, элементы ИЛИ, триггеры и элементы НЕ, входы первого и второго которых являются вторым и

45

50

ния, выход пятого элемента И соединен с Е ходом второго элемента задержки, вых:од которого- является четвертым вькодом блока управления, выход первого элемента ИЛИ соединен с вторым входом четвертого триггера, выходы четЕ1ертого триггера и первый выход третьего триггера являются вторым выходом блока управления, второй выход третьего триггера является первым выходом блока управления.

| етвертым входами блока управления, выходы первого и второго элементов НЕ соединены соответственно с первыми входами: первого и второго злементовИ второй вход первого элемента И соединен с входом.второго элемента НЕ, второй вход второго элемента И и первый вход третьего элемента И соединены, соответственно с выходами первого

триггера, первьш вход которого явля- ется первым входом блока управления и соединен с первым входом первого элемента РШИ, первым входом второго триггера и первым входом третьего триггера, второй вход первого триггера соединен с входом первого элемента НЕ, второй вход второго триггера является третьим входом блока управления и соединен с первым входом

четвертого триггера и вторым входом третьего триггера, второй вход третьего элемента И соединен с входом второго элемента НЕ, выход первого элемента И соединен с вторьм входом первого элемента ИЛИ, выходы второго и третьего элементов И соединены с входами второго элемента ИЛИ, выход второго Триггера соединен с входом первого элемента задержки, выход которого соединен с первым входом четвертого элемента И, второй вход четвертого элемента И является шестым входом блока управления, выход второго элемента ИЛИ соединен с входом третьего элемента НЕ и третьим входом четвертого элемента И, выход которого является третьим выходом блока управления, выход третьего элемента НЕ соединен с первым входом пято

го элемента И, второй вход которого является пятым входом блока управле-

го элемента И, второй вход которого является пятым входом блока управле-

ния, выход пятого элемента И соединен с Е ходом второго элемента задержки, вых:од которого- является четвертым вькодом блока управления, выход первого элемента ИЛИ соединен с вторым входом четвертого триггера, выходы четЕ1ертого триггера и первый выход третьего триггера являются вторым выходом блока управления, второй выход третьего триггера является первым выходом блока управления.

Составитель А.Воронин Редактор А.Ворович Техред М.Моргентал Корректор В.Синицкая

Заказ 3711/52 Тираж 543 Подписное БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Устройство для определения экстре-МАльНыХ зНАчЕНий СлучАйНыХпРОцЕССОВ | 1978 |

|

SU805358A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для ввода информации | 1989 |

|

SU1649529A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ОБЪЕКТОВ | 1992 |

|

RU2065569C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Изобретение относится к вычислительной технике, в частности к технике запоминающих устройств, и может быть использовано для контроля блоков аналоговой памяти. Цель изобретения - повышение быстродействия устройства. Запоминающее устройство coдepж iт генератор импульсов, контролируемый блок аналоговой памяти, ключ, блок управления, счетчик, компараторы, цифро- аналоговый преобразователь, источник опорных напряжений. Блок управления состоит из триггеров, элементов НЕ, элементов И, элементов задержки и элементов ИЛИ. Повьгаение быстродействия . достигается за счет того, что уровень входного аналогового сигнала задается сразу в цифровом коде и не требуется осуществлять его дополнительные измерения, а каждый из параметров блока аналоговой памяти определяется за один такт работы измерителя. 1 з.п.ф-лы, 2 ил. с е 1чЭ 4: СС

| Journees De lectronique Conversion A/J RD/Л Ecole Polvtechnique Federall (fe Lausanne, 19.73, pp | |||

| Устройство для одновременного приема и передачи по радиотелефону | 1921 |

|

SU373A1 |

| Усилитель выборки и запоминания для аналого-цифрового преобразователя | 1978 |

|

SU942131A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-10—Подача