Изобретение относится к технике передачи данных и может.быть исполь эовано в устройствах защиты информации от ошибок систем передачи с решающей обратной связью (рОС).

Известно устройство для исправления ошибок в кодовой комбинации, содержащее однопороговый и двухпороговый блоки, соединенные с входом устройства, сумматор по модулю два, один йход которого соединен с выходом блока формирования полиномов ошибок г другой вход через последова- тельно соединенные буферный и основной блоки памяти подсоединен к выходу однопорогового блока а выход сумматора по модулю два подключен к первому входу элемента И, блок обнаружения ошибок, первый выход которого соединен с выходом устройства. Второй выход - с вторымвходом элемента И, выход которого соединен с вторым выходом устройства, а выхоД двухпорогового блока подсоединен к первому входу блока Формирования полиномов ошибок, второй вход которого подсоединен к второму выходу блока обнаружения ошибок, вы- ход сумматора по модулю два подсоединен к входу блока обцаружения ошибок через элемент ИЛИ, другой вход которого подключен к выходу буферного блока памяти, выход сумматора по модулю два подключен к дополнительному входу ocJfjOBHoro блока памяти, а дополнительный вход сумматора по модулю два-подключен к соответствующему выходу блока формирования полиномов ошибок И .

Недостатками данного устройства дутя исправления ошибок в кодовой комбинации являются сложность аппаратурной реализации и невысокая достоверность .

Наиболее близким техническим решением к предлагаемому является устройство для обнаруй ения ошибок, содержащее последовательно соединенные входной блок, блок фазирования, стробирующий блок, первый счетчик несовпадения и элемент совпадения, к второму входу которого подключен выход второго счетчика несовпадения, вход которого подключен к выходу стробирующего блока, последовательно соединенные интегратор, элемент сборки и регистр памяти, а также блок Обнаружения ошибок, выход которого через дополнительный элемент совпадения подключен к второму входу элемента сборки, второй выход интегратора через дешифратор подключен к второму входу дополнительного элемента совпадения, к второму

входу дешифратора подключен выход . интегратора, к входу которого подсоединен второй выход блока фазирования через элемент совпадения, при этом второй выход первого счетчика несовпадения подсоединен к входу блока обнаружения ошибок и второму входу регистра памяти 2 . Недостатками известного устройства для обнаружения ошибок являются невысокая достоверность, обусловленная ошибочным приемом сообщения в случае отсутствия недостоверных

0 символов (стираний) при искажении информационной части кодовой комбинации; ложная браковка сообщения изза искажения проверочных разрядов кодовой комбинации при правильном

5 приеме информационной части и допустимом кбличестве стираний.

Цель изобретения - повышение достоверности.

Цель достигается тем, что В

0 устройство для обнаружения ошибок, -содержащее последовательно соединен ные входной.блок, блок фазирования, стробирующий, блок, первый счетчик, несовпадения и элемент совпадения,

5 к второму входу которого подключен . выход второго счетчика несовпадения, вход которого подключен к выходу стробирующего блока, последовательно соединенные интегратор, элемент

0 сборки и регистр памяти, а также блок обнаружения ошибок, введены последовательно соединенные ключ, датчик комбинации, первый сумматор по модулю два, элемент И, второй сум5 матор по модулю два и первый переключатель, а также последовательно соединенные второй переключатель и элемент запрета, выход которого подсоединен к второму входу элемента

сборки, к третьему входу которого подключен выход блока обнаружения ошибокi к входу которого подключен выход первого переключателя, второй вход которого объединен с вторым входом регистра памяти, вторыми

5 входами обоих сумматоров по модулю дна и подключен к второму выходу первого счетчика несовпадения, третий вход первого переключателя объединен с третьим входом регистра па0 мяти, первым входом ключа, первым входом второго переключателя и подключен к второму выходу блока фазирования, при, этом первый выход второго переключателя подсоединен

5 к второму входу элемента И, выход регистра памяти подсоединен к второму входу ключа, а второй выход второго переключателя подсоединен к входу интегратора, причем выход

0 первого сумматора по модулю два

подсоединен к прямому входу элемента запрета.

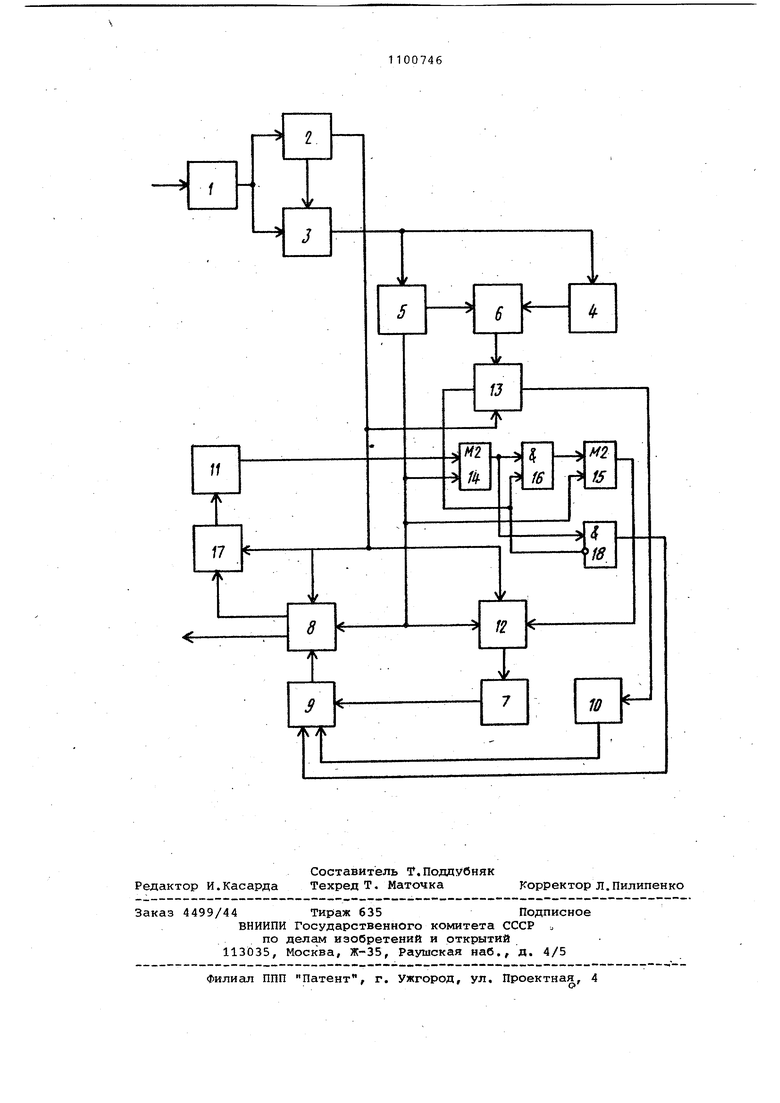

На чертеже представлена структурно-электрическая схема устройства

5 для обнаружения ошибок.

Устройство для обнаружения ошибок содержит входной блок 1, блок 2 фазирования, стробирующий блок 3, первый и второй счетчики 4 и 5 несовпадения, элемент 6 совпадения, блок 7 обнаружения ошибок, регистр 8 памяти, элемент 9 сборки, интегратор 10, датчик 11 комбинаций, первый и второй переключатели 12 и 13, первый и второй сумматоры 14 и 15 по модулю два, элемент И 16, ключ 17, элемент 18 запрета.

Устройство для обнаружения ошибок работает следующим образом.

Передаваемая информация кодируется избыточным разделимым (п.к) кодом, где п - длина кодовой комбинации, к - число информационных разрядов. Проверочные разряды, число которых равно п-к, передаются пос,ле информационных.

Двоичные сигналы кодовых комбинаций подаются в последовательном виде, начиная с информационных разрядов , с входа устройства для обнаружения ошибок на входной блок 1. В входном блоке 1 сигналы преобрадуготся в соответствующий вид, согласуются по току и напряжению с входом и поступают на входы блока 2 и стробирующего блока 3. Блок 2 формирует тактовые стробирующие импульсы, которые подаются на тактовый вход стробирующего блока 3, где формируются кодовые последовательности. В счетчиках 4 и 5 несовпадения анализируются кодовые последовательности противоположных полярностей, причем на информационном выходе счетчика 5 образуются значащие позиции кодовых комбинаций. На управляющих выходах счетчикой 4 и 5 образуются двоичные сигналы, которые поступают в элемент б совпадения.

С информационного выхода счетчика 5 несовпадения кодовые элементы поступают в регистр 8 ламяти для временного запоминания пpини aeмoй инфомационной части комбинации-, а также в блок 7 обнаружения ошибок через переключатель 12,управление которым осуществляется. сигналом с разрешакллего выхода блока 2.

Если сигналы на управляющих выходах обоих счетчиков 4 и 5 несовпадения отсутствуют, на выходе, злемента 6 совпадения образуется импульс, свидетельствующий о наличии недостоверного символа (стирание). Этот импульс поступает на вход интегратор 10, вход которого с помощью разрешаняцего сигнала с блока 2, поступающего на переключатель 13, подключен к выходу элемента 6 совпадения на время приема информационных символов в кодовой комбинации.

Если число недостоверных информационных элементов превышает величи ну порогового значения на выходе интегратора 10 появляется сигнал переполнения, который поступает через элемент 9 сборки на сбросовый вход регистра 8 памяти. По этому сигналу прекравдается прием проверочных разрядов кодовой комбинации, информация в регистре 8 стирается, устройство для обнаружения ошибок переходит в режим приема очередного сообщения, а по Обратному каналу в системах РОС посылается сигнал переспроса на повторную передачу забракованной ко„ довой комбинации.

Если недостоверные символы отсутствуют в информационной части или их число не превышает порогового значения, устройство продолжает прием проверочных разрядов кодовой комбинации. По сигналу с разрешающего выхода блока 2 вход переключателя 13 отключается от входа, интегратора счетчика 10 и подключается к одному из входов элемента И 16, а выход переключателя 12 отключается от инфор мацйонного выхода счетчика 5 несовпадения и соединяется с выходом сумматора 15 по модулю 2. При этом отключается вход регистра 8 памяти, предотвращая запись в его разряды проверочных символов кодовой комби нации, и открывается кЛюч 17, подготавливая вьщачу информационных разрядов из регистра 8 памяти в датчик 11 комбинации. Устройство для обнаружения ошибок переходит в режим приема проверочной части кодовой , комбинаций.

Проверочные разряды, поступающие с выхода счетчика 5 несовпадений, одновременно подаются на вход сумматора 14 по модулю два, ,а через сумматор 15 по модулю два и переключатель 13 - в блок 7, в котором осуществляется анализ кодовой комбинации на наличие или отсутствие искажений. Одновременно на второй вход сумматора 14 по модулю два синхронно с элементами, выдаваемыми с выхода счетчика 5 несовпадения, поступают проверочные символы из датчика 11 комбинации, сформированные путем ко дирования информационной части комбинации, принятой и записанной в регистре 8 памяти.

Проверочные символы, выдаваемые с выходов счетчика 5 несовпадения и датчика 11 комбинации, поразрядно сравниваются между собой на сумматоре 14 по модулю два. Результат сравнения поступает на вход элемента И 16 и на запрещакяций вход элемента 18 запрета.

На другие входы элементов через переключатель 12 подается сигнал с выхода элемента 6 совпадения, о наличии или отсутствии недостоверных символов (стираний). В случае идентичности сравнивае№jx разрядов на выходе сумматора 14 по модулю два сигнал отсутствует, значащие разряды с выхода счетчика 5 несовпадения через сумматор 15 по модулю два и переключатель 13 вводятся в блок 7, При необнаружении ояибок информация из регистра 8 пё№1яти поступает на выход. Устройст во для обнаружения ошибок переходит в режим приема очередного сообщения Если информационная часть кодово комбинации принята правильно, а про верочная искажена, устройство для обнаружения ошибок обеспечивает исправление оитбочно принятых значащих разрядов, на местах которых/появляются сзтирания (недостоверные элементы), выявленные с помощью сче чиков 4 и 5 несовпадения и элемента 6 совпадения. В случае искажения проверочной части кодовой комбинации на выходе сумматора 14 по модулю два формируется сигнал, который поступает на один из входов элемента И 16, на другой вход которой d большой вероя ностью поступает сигнал о наличии недостоверного элемента. В результа те на выходе элемента И 16 появляет ся сигнал, который поступает на оди из входов сумматора 15 по модулю дв а на вторЬй вход последнего подается искаженный проверочный символ кодовой комбинации, .поступающей из канала связи. При этом на сумматоре 15 по модулю два происходит инвертирование искаженного разряда. Таким образом, инвертирование искаженного элемента проверочной части осуществляется каждый раз, когда возникает данная ситуация. В абсолютном большинстве случаев это будет соответствовать исправлению ошибочно принятой комбинации. В случае несовпадения одноименных разрядов и отсутствия недостоверных символов на местах ,этих несовпадений, сигнал с выхода сумматора 14 по модулю два через открытый элемент 18 запрета и/ элемент 9 сборки бракует информационные разряды кодовой комбинации, записанной в регистре 8 памяти. Это осуществляется для устранения необнаруженных ошкбок, возникающих в Результате искажения информационной части и Отсутствия недостоверных символов в процессе приема сообщения. Предлагаемое устройство обладает более высокой технико-экономической эффективностью по сравнению с известным. Введение в него новых элементов и связей позволяет существенно повысить достоверность приема без значительного уменьшения относительной скорости передачи информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок | 1974 |

|

SU517173A1 |

| Устройство для обнаружения ошибок | 1980 |

|

SU932636A2 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ПРАВИЛЬНОСТИ ФОРМИРОВАНИЯ и АНАЛИЗА ОШИБОК ЦИКЛИЧЕСКИХ КОДОВ | 1971 |

|

SU301864A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК, содержащее последовательно , соединенные входной блок, блок, фа- эирования, стробирующий блок, первый счетчик несовпадения и элемент сов- . падения, к второму входу которого подключен выход второго счетчика несовпадения, вход которого подключен к выходу стробирующёго блока, последовательно соединенные интегратор, элемент сборки и регистр памяти; а также блок обнаружения ошибок, о тличающеес. я тем, что, с целью повышения достоверно.сти,введены последовательно соединенные ключ,, датчик комбинации, первый сумматор по модулю два, элемент И, второй сумматор по модулю два и первый переключатель , а также последовательно соединенные второй переключатель и элемент запрета, выход которого подсоединен к второму входу элемента сборки, к третьему входу которого подключен выход блока обнаружения ошибок,, к входу KOTOpoiro подключен выход первого переключателя, второй вход которого объединен с вторым входом регистра памяти,вто.рыми входами обоих сумматоров по модулю два и подключен к второму выходу первого счетчика несовпадения, третий вход первого переключателя объединен с третьим входом регистра i памяти, первым входом ключа, перрым входом второго переключателя и под(Л ключен к второму выходу блока фазирования, при этом первый выход второго переключателя подсоединен к второму входу элемента И, выход регистра памяти подсоединен к второму входу ключа, а второй выход второго переключателя подсоединен к входу интегратора, причем выход первого сумматора по модулю два подсоединен к прямому входу «лемента запрета. . ... ki 4 с

Авторы

Даты

1984-06-30—Публикация

1983-04-06—Подача