1

Изобретение относится к технике передачи дискретной информации и может использоваться при построении аппаратуры передачи данных.

Известное устройство для исправления

ошибок содержит ключи, буферный регистр, кодовые фильтры, ячейки памяти, сумматоры, умножители. Перед приемом сообщения ключи находятся в разомкнутом состоянии. При этом открывается свободный доступ

информации в буферный регистр и во все кодовые фильтры.

Состояние фильтра устанавливается за два полутакта. За первый полутакт содержимое всех ячеек памяти переписывается в сумматоры, одновременло ячейки памяти приводятся в нулевое состояние. За второй полутакт результат суммирования из сумматора переписывается в фильтр. После приема сообщения по.пностью, ключи открываютс На выходах сумматоров на каждом такте появляется значение контрольной суммы . Если контрольная сумма обратится в ноль, то символ, покидающий в данный момент буферный регистр,должен быть исправлен.

Известно и другое устройство для исправления ошибок, которое содержит последовательно соед щенные вход1 ой блок, декодер, управляемый генератором кодовой последовательности, и выходной накопитель, причем информащютшый выход декодера подключен к счетчику ощибок через последовательно соед1шенные регистр памяти и схему сравнения, ко второму входу которой подключен проверочный выход декодера, а также передатчик сигнала запрос.

Это устройство является наиболее близки по технической сущности и достигаемому результату к описываемому изобретению.

Недостатком известного устройства является недостаточно высокая скорость передачи иэ-за необходимости выполнять повторение после каждого обнаружения ошибки,

Цель изобретения - повыщение быстродействия за счет уменьшения числа запросов.

Для этого в устройство для исправления ошибок, содержащее последовательно соединенные входной блок, декодер, управляемый генератором кодовой последовательноетн, и ВЫХОД110Й лакопытелЬ: причем ннфо мациоииый выход декодера П1-;дк.-юче}1 к счетчику ошибок через 1госледоаательпо соедине11иь;е регистр памят) i; схему сравнения , к BTOpovj входу которой подключен проверочный выход декоде1эа, ,м также пере- д;;тч1 К сигна.па запрос, введены дополни- тель.1ые регнстр налаятИ; к.пюч, анализатор II элегмоить ИЛИ и НЕ. ;фи этом проверочный выход декодера последовательно соедипеннь е донол1п-1тельиьш регист ; ri;.,;-,.-я-ти и кгцеч подключен 11 донолнитель}, тму входу выходного накопителя, а вь;хс; схомы сравнения через элемент НН н./дключен к одному из входов элемента ИЛ1-1, подключенного ко входу сброс счетчика ошибок, н одному нз входов анализатора, к другим входам которого нодключены выхэдт соответств тещих разрядов счетч1и-:а оюнбок кром е того один из вь i ходов анализ атора поа ключен к соответств 1ещим входа.: нередатчк 1 сигнала Запрос и элемента liJTii и к входу cTHpiuuie выходного згакопителя, а другой выход - к у 1равля1ошим входам -;лэмен та ИЛИ 11 клоч.и

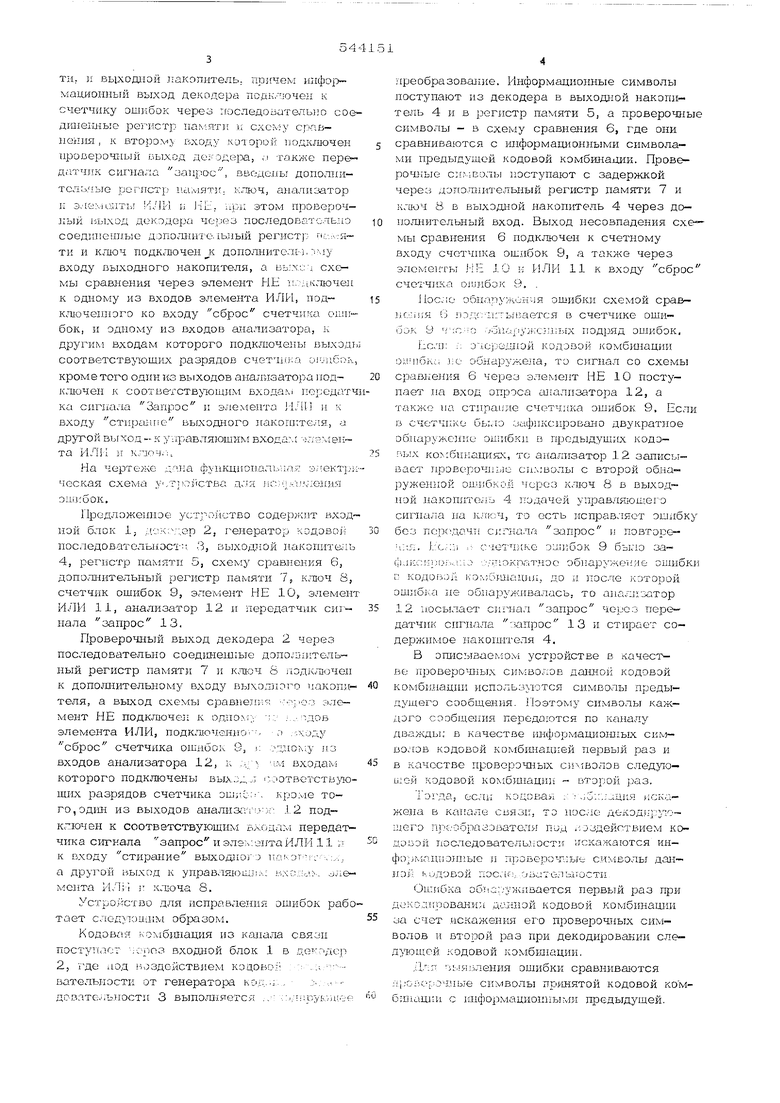

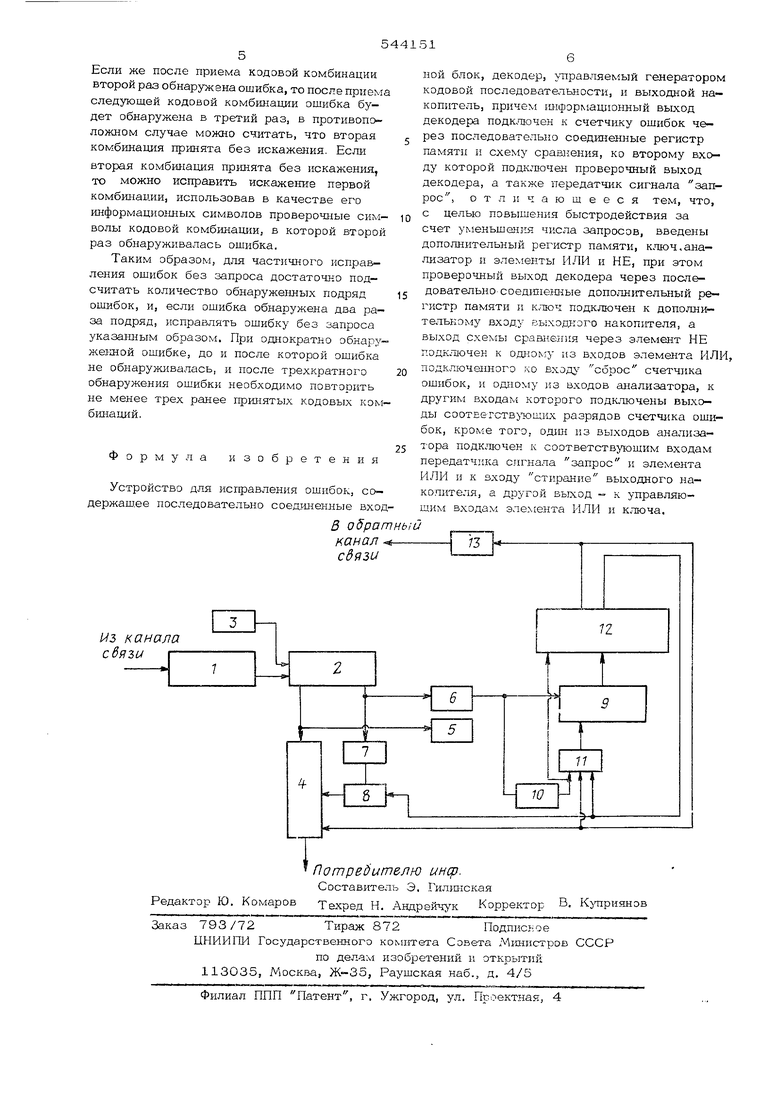

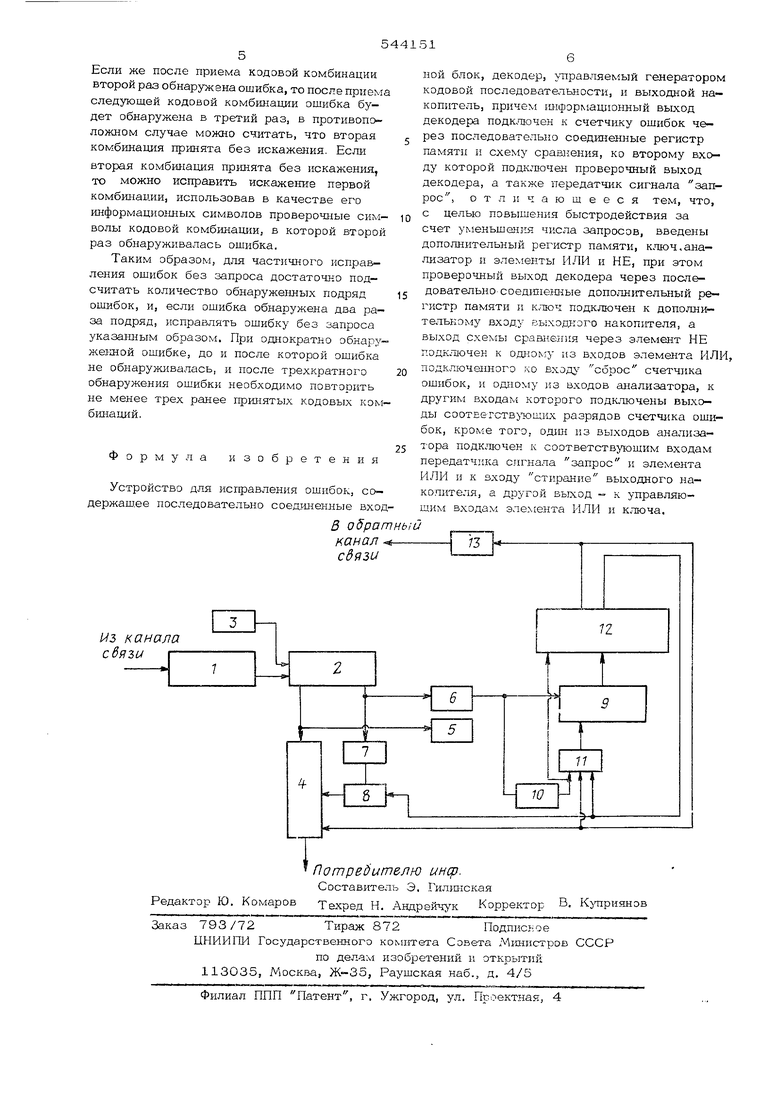

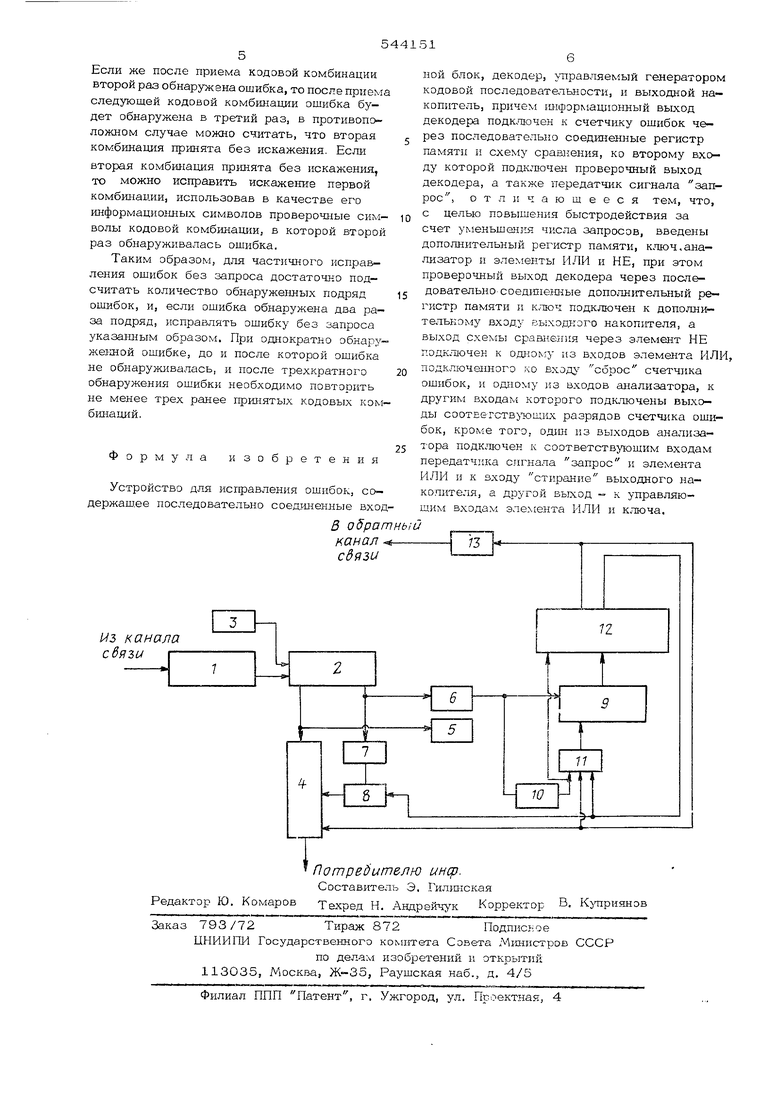

На чертеххе uia функциональная электрическая схема y,T:);;iicTBa для Jic: -l ;;eния oiiiKooK.

Предложенное устр-СНство содержит входной блок 1; :-|-: К: -;ер 2, генератор кодовой последовательное -:; 3, выходной наконитаиь 4, регнстр памяти 5, схему сравнения 6, допо.лннтельньп регистр памяти 7, клоч 8, счетчик ошибок 9, элемент НЕ 10, элемен ИЛИ 11, анализатор 1.2 п передатчик сигнала запрос 13,

Проверочный выход декодера 2 через последовательно соедшгешшге дополнительный регистр памяти 7 и ключ S подгс.гшзчен к допош нтельному входу выхолнэг-о накопителя, а выход схемы сравнен :-; Г-рмэ.-з эле- vieHT НЕ подключен к одно,г.у -;;. ; , тдов элемента ИЛИ, подключенное--, п .-.коду сброс счетчика ошибок 9, ; ;-::,но;-..гу из входов анализатора 12, i-. .;,-;; -uv; входам которого подключены ВЫА.::-„-:; Г-оотвегств пощнх разрядов счетчика ошис-:-, кроме того, один из выходов аналнза- - ;-;;: 1,2 подключен к соответствующим Бл(-дам передат чика сигнала запрос иэл9 ;-зн-таИЛИ 11 -,;. к входу стирание выход. паьэт--;ч- ,:.,., а другой выход к управляющл;-.: вхс;,:..- элемента ИЛИ к ключа 8.

Устройство для исправления ошибок работает с.ледук)иа1м образом.

Кодова.я iNOM6imaiiHn из канала связи HOCTyT-faor -:-::ч-;оз входной блок 1 в декодер 2, -1де аод воздействием кодово;- : ,. вательности от генератора код..:-, , - дс-вательностп 3 вынолняе-гся .,-- ::..-г :-оуь-...;е

преобразование. Информационные символы поступают из декодера в выходной накопитель 4 н в регнстр памяти 5, а проверочн символы - в схему сравнения 6, где они сравниваются с шгформационными символами предыдущей кодовой комбинации. Провеpo4Jibie символы )юступают с задержкой через допо.л-ннтельный регистр памяти 7 и кгооч 8 в выходной накопитель 4 через до- нолнительный вход. Выход несовпадения схмы сравнения 6 нодключен к счетному входу счетчнка ошибок 9, а также через элементы НЕ 10 н ИЛИ 11 к входу сбро счетчика о инбок 9. .

После обнару;.кон-.;я ошибки схемой сравнс.-и)Я в лэдг:-1и-тьи5ается в счетчике ошибок 9 г:СТг; .Зиару :с};1Л:.1Х подряд ошибок,

Ьс.лк :. э).с):;еднай кодовой 1 омбинации оиИбк;, КС обнаружена, то сигнал со схемы сравнения 6 через элемент НЕ 10 поступает на вход опроса гшализатора 1.2, а также на стн-раиле счетчика ошибо ; 9. Есл в с-четчике было .: афнксирова1-ш двукратное обнаружение ошибки в нродыдуших кодор.ьх комбннаниетс, то ана.лизатор 12 записывает проверочные снмволы с второй обнаружен}10й ошибкой через ключ 8 в выходной наконитель 4 г.одачей управляюшег-о снгпала на );...1(н::ч, то есть исправляе-т ошибк без персдачн снгна.ла ааирос и повторе- ч:;;-.. h:(., ,- Clei-HiUve 9 было заф,но:; ;;;:о)..:; ---лнократное обнаружение ошнб п кодо1: :.й i-;o;..;Gtuiainu;j до н после которой н.э обнаружлшалась, то аналн-затор 12 11ось лает сигнал занрос через пере- датчнк сигнала ланрос 13 и стирает содержимое наконителя 4,

В ош.1сываемом устройстве в качестве проверочных символов дшшой кодовой комбинации использлтэтся снмв-о.лы предыдущего сообш.ення. Поэтому снмволы каждого сообщения передаются по каналу дважды; в качестве информациошхых символов кодовой комб1шацией первый раз и в качестве проверочных си- лволов шей кодовой комбшшцни - в-торой jja3.

Тогда, ecjii; кодовая :- : ,;3::.;,дия искажена в канале С1зязи, то носле декодирую- щегэ преобразователя под .-;эздейптвием кодоиэй последователылости -скажаются информпп1Ю1Н1ые н npoBepo4ibffc символы данной кодовой noc,-Lfi; О1:..ителы;ости

Ошибка об 1а;;-уживается нервый раз при де;-;олнрован:ил д.:-нной кодовой комбинации за счет искажения его проверочных символов и второй раз при декодировании еле- дувэш ей кодовой комбилации.

Дл1п Я;.я;.иения ошибки сравниваются ;- |;олг.;.-..зчнь;е си-мволы ттр)-шятой кодовой комбгшации с информационными предыдущей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ИСПОЛЬЗОВАНИЕМ БЛОЧНЫХ РАЗДЕЛИМЫХ КОДОВ, ОТ ИМИТИРУЮЩИХ ДЕЙСТВИЙ ЗЛОУМЫШЛЕННИКА | 2019 |

|

RU2738789C1 |

| "Устройство для исправления ошибок в системах передачи дискретной информации | 1977 |

|

SU663120A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Устройство для исправления ошибок в системах передачи дискретной информации | 1980 |

|

SU896777A2 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1969 |

|

SU251253A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

Авторы

Даты

1977-01-25—Публикация

1974-09-23—Подача