(5) УСТРОЙСТВО для ОБНАРУЖЕНИЯ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок | 1974 |

|

SU517173A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1985 |

|

SU1256670A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С ФУНКЦИЕЙ ИСПРАВЛЕНИЯ ОШИБОК | 2011 |

|

RU2486682C2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство циклового фазирования для приема двоичной информации | 1975 |

|

SU554631A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

Изобретение относится к технике передачи данных, может использоваться в устройствах защиты от ошибок в системах передачи данных с многократным повторением. , .

По основному авт. св. № 517173 известно устройство для обнаружения ошибок, содержащее входной блок, выход которого подключен к входу блока фазирования, а через стробирующий блок и первый счетчик несовпадений - к входу первой схемы совпадения, к второму,входу которой подключен выход стробирующего блока через второй счетчик несовпадений, второй выход которого подключен к входам блока обнаружения ошибок и региетра памяти, соединенного с выходом схемы сборки, при этом тактовый выход блока фазирования подключен к второму входу стробирующего блока, интегратор, дешифратор и вторая схема совпадения, при этом выход интегратора подключен к первому входу схемы сборки, а через последовательно соединенные дешифратор и вторую схему совпадения к второму входу схемы сборки, выход блока фазирования через последовательно соединенные первую схему совпадения и интегратор подключен к второму входу дешифратора.

Однако известное устройство не обеспечивает контроль работоспособности.

10

Цель изобретения - повышение точности обнаружения путем контроля работы блока обнаружения ошибок.

Указанная цель достигается тем,

«5 что в известное устройство веедены последовательно соединенные инвертор, третья схема совпадения и счетчик ошибок, при этом выходы дешифратора, блоки обнаружения ошибок и счетчик

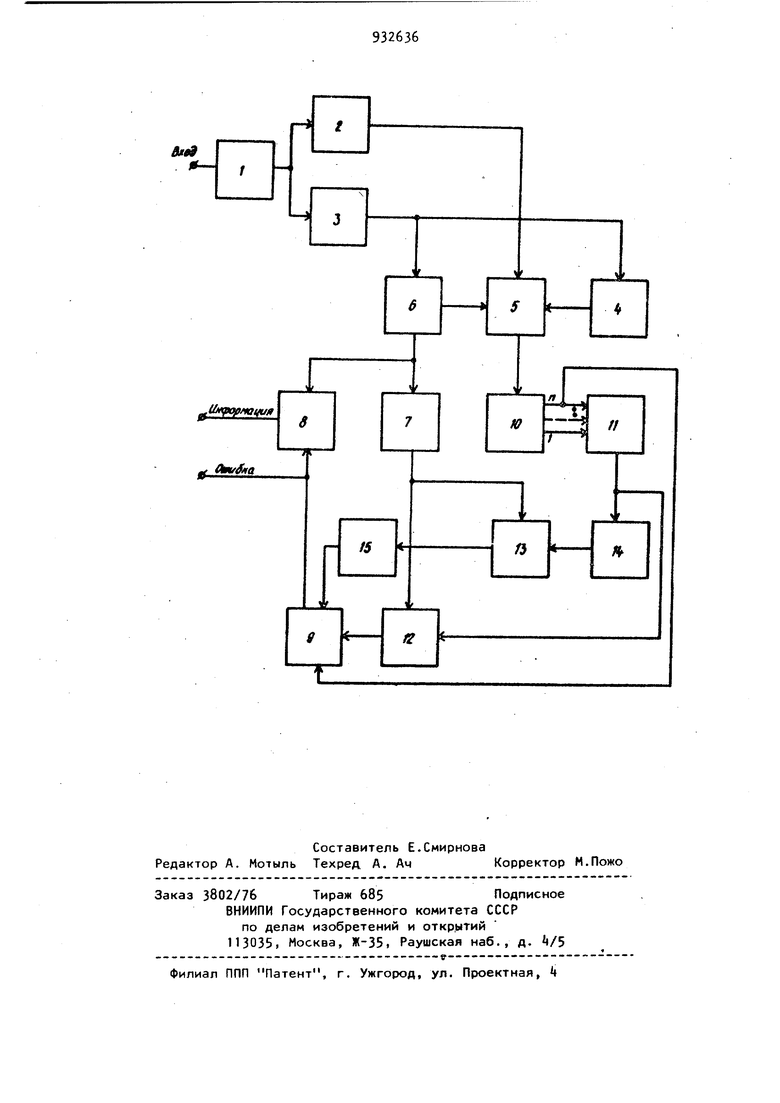

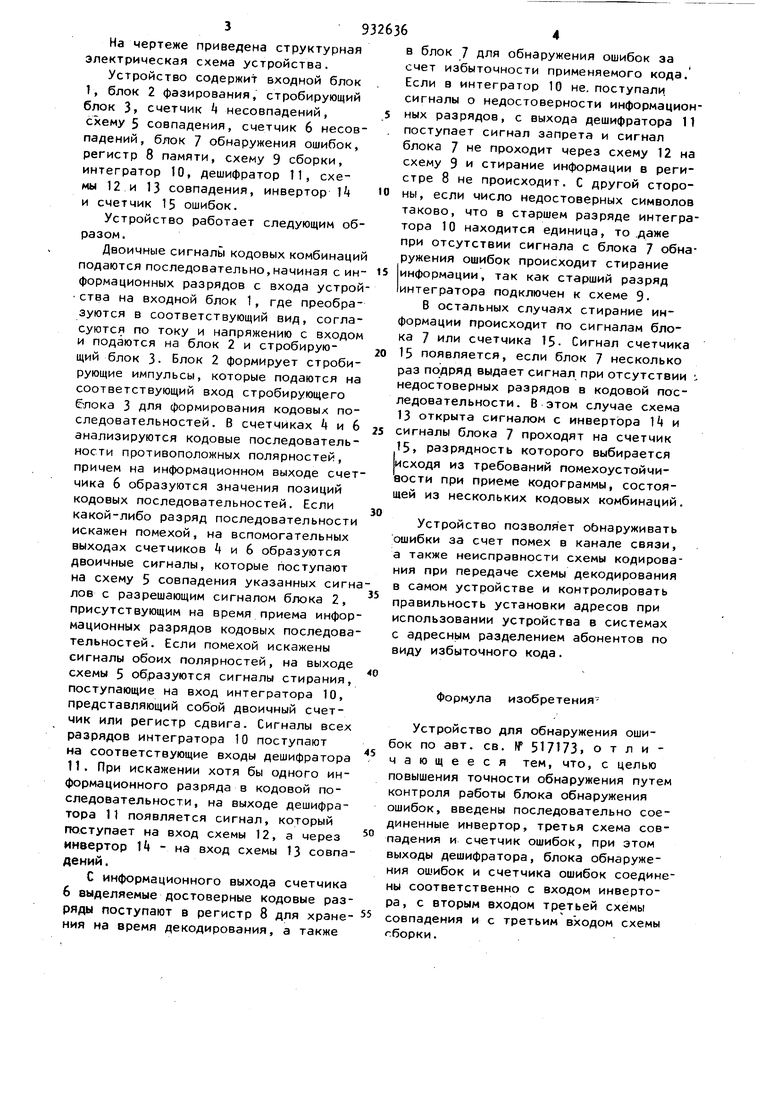

га ошибок соединены соответственно с входом инвертора, с вторым входом третьей схемы совпадения и с третьим входом схемы сборки. На чертеже приведена структурная электрическая схема устройства. Устройство содержит входной блок I,блок 2 фазирования, стробирующий блок 3, счетчик Ц несовпадений, схему 5 совпадения, счетчик 6 несовпадений, блок 7 обнаружения ошибок, регистр 8 памяти, схему 9 сборки, интегратор 10, дешифратор 11, схемы 12 и 13 совпадения, инвертор 14 и счетчик 15 ошибок. Устройство работает следующим образом. Двоичные сигналы кодовых комбинаций подаются последовательно,начиная с информационных разрядов с входа устрой ства на входной блок 1, где преобразуются в соответствующий вид, согласуются по току и напряжению с входом и подаются на блок 2 и стробирующий блок 3. Блок 2 формирует стробирующие импульсы, которые подаются на соответствующий вход стробирующего блока 3 для формирования кодовых последовательностей. В счетчиках t и 6 анализируются кодовые последовательности противоположных полярностей, причем на информационном выходе счет чика 6 образуются значения позиций кодовых последовательностей. Если какой-либо разряд последовательности искажен помехой, на вспомогательных выходах счетчиков t и 6 образуются двоичные сигналы, которые поступают на схему 5 совпадения указанных сигн лов с разрешающим сигналом блока 2, присутствующим на время приема инфор мационных разрядов кодовых последова тельностей. Если помехой искажены сигналы обоих полярностей, на выходе схемы 5 образуются сигналы стирания, поступающие на вход интегратора 10, представляющий собой двоичный счетчик или регистр сдвига. Сигналы всех разрядов интегратора 10 поступают на соответствующие входы дешифратора II.При искажении хотя бы одного информационного разряда в кодовой последовательности, на выходе дешифратора 11 появляется сигнал, который поступает на вход схемы 12, а через инвертор 1 - на вход схемы 13 совпа дений . С информационного выхода счетчика 6 выделяемые достоверные кодовые раз ряды поступают в регистр 8 для хране ния на время декодирования, а также В блок 7 для обнаружения ошибок за счет избыточности применяемого кода. Если в интегратор 10 не, поступали сигналы о недостоверности информационных разрядов, с выхода дешифратора 11 поступает сигнал запрета и сигнал блока 7 не проходит через схему 12 на схему 9 и стирание информации в регистре 8 не происходит. С другой стороны, если число недостоверных символов таково, что в старшем разряде интегратора 10 находится единица, то .даже при отсутствии сигнала с блока 7 обнаружения ошибок происходит стирание информации, так как старший разряд интегратора подключен к схеме 9В остальных случаях стирание информации происходит по сигналам блока 7 или счетчика 15- Сигнал счетчика 15 появляется, если блок 7 несколько раз подряд выдает сигнал при отсутствии недостоверных разрядов в кодовой последовательности. В этом случае схема 13 открыта сигналом с инвертора Т и сигналы блока 7 проходят на счетчик 15 разрядность которого выбирается исходя из требований помехоустойчивости при приеме кодограммы, состоящей из нескольких кодовых комбинаций. Устройство позволяет обнаруживать ошибки за счет помех в канале связи, а также неисправности схемы кодирования при передаче схемы декодирования в самом устройстве и контролировать правильность установки адресов при использовании устройства в системах с адресным разделением абонентов по виду избыточного кода. Формула изобретенияУстройство для обнаружения ошибок по авт. св. ff 517173i отличающееся тем, что, с целью повышения точности обнаружения путем контроля работы блока обнаружения ошибок, введены последовательно соединенные инвертор, третья схема совпадения и счетчик ошибок, при этом выходы дешифратора, блока обнаружения ошибок и счетчика ошибок соединены соответственно с входом инвертора, с вторым входом третьей схемы совпадения и с третьим входом схемы сборки.

Авторы

Даты

1982-05-30—Публикация

1980-12-29—Подача