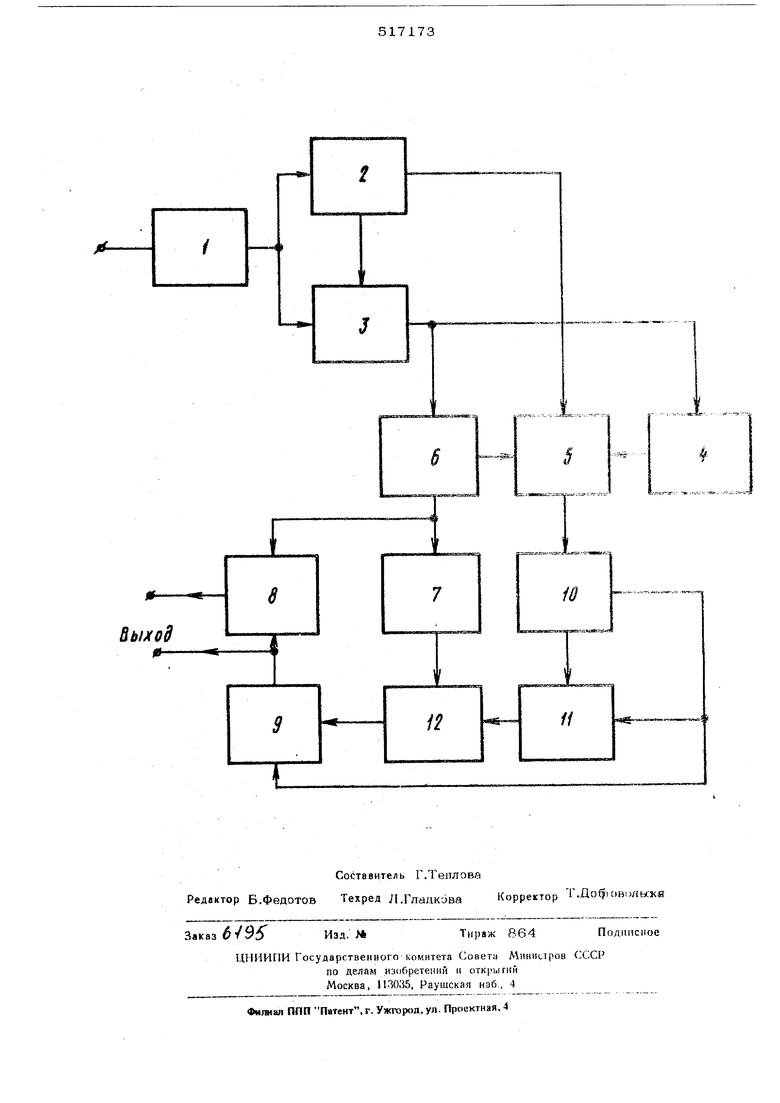

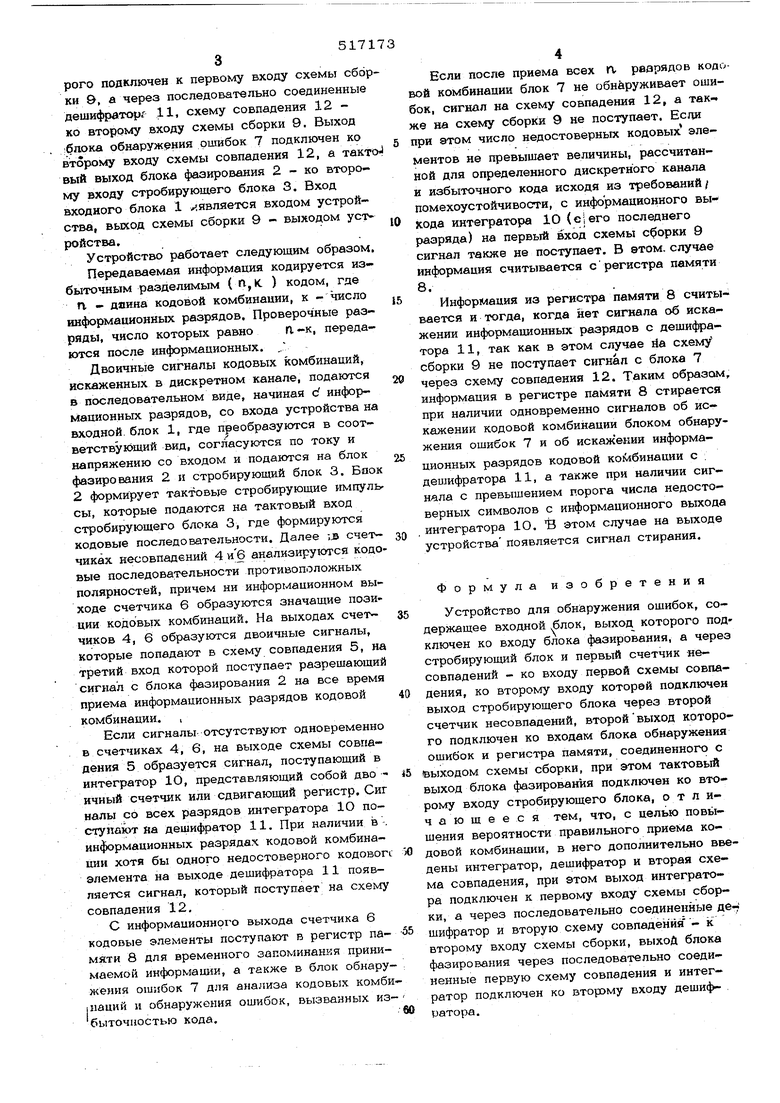

Изоб ретение относится к технике перёДЖчи данных, может использоваться в устройствах зашиты от ошибок в системах передачи данных без обратной связи.i Известно устройство для обнаружения ошибок, содержащее входной блок, выход которого подключен ко входу блока фазирования, а через стробирующий блок и первый счетчик несовпадений - ко входу первой схемы совпадения, ко второму входу которой (Подключен выход стробируюшего блока через второй счетчик несовпадений, второй выход которого подключен ко входам блока обнаружения ошибок и регистра памяти, соединенного с выходом схемы сборки, при этом тактовый выход блока фазирования ;Подключен ко второму входу стробирующего (блока. Однако известное устройство характера- .зуется невысокой вероятностью правильного {приема кодовой комбинации из-за искаже- ;ния проверочных разрядов избыточного кода. Цель изобретения - повышение вероятно сти правильного приема кодовой комбинации. В предлагаемое устройство дополнитвль но введены интегратор, деши4 атор. и вто.рая схема совпадения; при этом выход интегратора подключен к первому входу схемы сборки, а через последовательно соединенные дешифратор, вторую схему совпадения- ко BTOpoNiy входу схемы сборки, выход блока фазирования через последовательно соединенные первую схему совпадения и интегра тор подключен ко второму входу дешифрато На чертеже приведена структурная схеме устройства. Выход входного блока 1 подключен ко ВХОДУ блока фазирования 2, ачерюз стробц. рующий блок 3, счетчнк несовпадений 4 ко входу схемы совпадения 5, ко вторрйУ входу которой подключен выход стробирующего блока 3 через счетчик иесовпаде й в, второй выход которого подключен ifo входам блока обнаружения ошибок 7 и регистра па мяти 8, соединенного с выхЬдом схемы сборки 9. При этом выход блока фазирова- ния 2 через схему совпадения 5 подключен ко входу интегратора 1О, один выход кото рого подключен к первому входу схемы сбо ки &, а через поспедовательно соединенные дешифраторг 11, схему совпадения 12 ко второму входу схемы сборки 9. Выход ;бпока обнаружения ошибок 7 подключен ко второму входу схемы совпадения 12, а такт вый выход блока фазирования 2 - ко второму входу стробируюшего блока 3, Вход входного блока 1 является входом устройства, выход схемы сборки 9 - выходом устройства. Устройство работает следующим образом Передаваемая информация кодируется избыточным разделимым ( Г1,к. ) кодом, где rt - дяина кодовой комбинации, к - число информационных разрядов. Проверочные разряды, число которых равно п. -к, передаются после информационных. Двоичные сигналы кодовых комбинаций, искаженных в дискретном канале, подаются в последовательном виде, начиная d информационных разрядов, со входа устройства на входной, блок 1, где преобразуются в соответствующий вид, согласуются по току и напряжению со входом и подаются на блок фазирования 2 и стробирующий блок 3. Баок 2 формирует тактовые стробирующие импуль сы, которые подаются на тактовый вход стробирующего блока 3, где формируются кодовые последовательности. Далее ija счетчиках несовпадений 4 и6 анализируются кодо вые последовательности противоположных полярностей, причем ни информационном выходе счетчика 6 образуются значащие позиции кодовых комбинаций. На выходах счетчиков 4, 6 образуются двоичные сигналы, которые попадают в схему совпадения 5, на третий вход которой поступает разрешающий сигнал с блока фазирования 2 на все время приема информационных разрядов кодовой комбинации. I Если сигналы- отсутствуют одновременно в счетчиках 4, 6, на выходе схемы совпадения 5 образуется сигнал, поступающий в интегратор 10, представляющий собой дво ичный счетчик или сдвигающий регистр. Сиг налы со всех разрядов интегратора 1О поступают йа Дешифратор 11. При наличии в . информационных разрядах кодовой комбинации хотя бы одного недостоверного кодовоп элемента на выходе дешифратора 11 появляется сигнал, который поступает на схему совпадения 12, С информационного выхода счетчика 6 кодовые элементы поступают в регистр памяти 8 для временного запоминания принимаемой информации, а также в блок обнаружения ошибок 7 для анализа кодовых комби1паций и обнаружения ошибок, вызванных избыточностью кода. Если после приема всех rv рварядов кодовой комбинации блок 7 не обнаруживает ошибок, сигнал на схему совпадения 12, а также на схему сборки 9 не поступает. Еслл при атом число недостоверных кодовых элементов не превышает величины, рассчитанной для определенного дискретного канала и избыточного кода исходя из требований/ помехоустойчивости, с информационного выхода интегратора 1О (с;его последнего разряда) на первый вход схемы сборки 9 сигнал также не поступает. В этом, случае информация считывается с регистра памяти 8. Информация из регистра памяти 8 считывается и тогда, когда нет сигнала об искажении информационных разрядов с дешифратора 11, так как в этом случае йа схему сборки 9 не поступает сигнал с блока 7 через схему совпадения 12. Таким образам, информация в регистре памяти 8 стирается при наличии одновременно сигналов об искажении кодовой комбинации блоком обнаружения ошибок 7 и об искажении информационных разрядов кодовой комбинации с дешифратора 11, а также при наличии сигнала с превышением порога числа недостоверных символов с информационного выхода интегратора 1О. В этом случае на выходе устройства появляется сигнал стирания. Формула изобретения Устройство для обнаружения ошибок, содержащее входной лок, выход которого подключен ко входу блока фазирования, а через стробирующий блок и первый счетчик -несовпадений - ко входу первой схемы совпадения, ко второму входу которей подключен выход стробирующего блока через второй счетчик несовпадений, второйвыход которого подключен ко входам блока обнаружения ошибок и регистра памяти, соединенного с ЫХОДОМ схемы сборки, при этом тактовый ыход блока фазирования подключен ко втоому входу стробирующего блока, от л иающееся тем, что, с целью повыения вероятности правильного приема коовой комбинации, в него дополнительно ввеены интегратор, дешифратор и вторая схеа совпадения, при этом выход интегратоа подключен к первому входу схемы сбори, а через последовательно соединенные де-7 ифратор и вторую схему совпадения- к торому входу схемы сборки, выхоД блока азирования через последовательно соедиенные первую схему совпадения и интегатор подключен ко вторэму входу дешифатора.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок | 1980 |

|

SU932636A2 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| Адаптивное устройство для анализаКОдОВыХ КОМбиНАций B СиСТЕМАХ пЕРЕ-дАчи диСКРЕТНыХ СООбщЕНий C РЕшАю-щЕй ОбРАТНОй СВязью | 1979 |

|

SU809613A1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для приема информации с обнаружением ошибок | 1975 |

|

SU556480A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

Выход

«

Авторы

Даты

1976-06-05—Публикация

1974-08-20—Подача