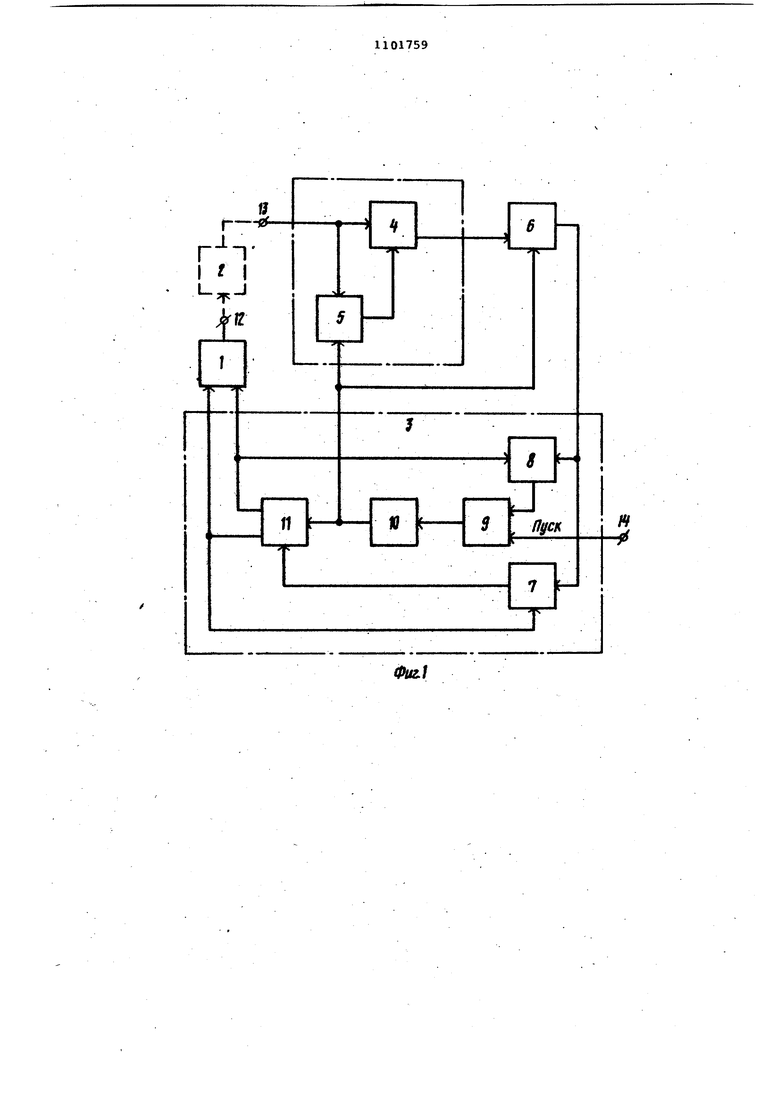

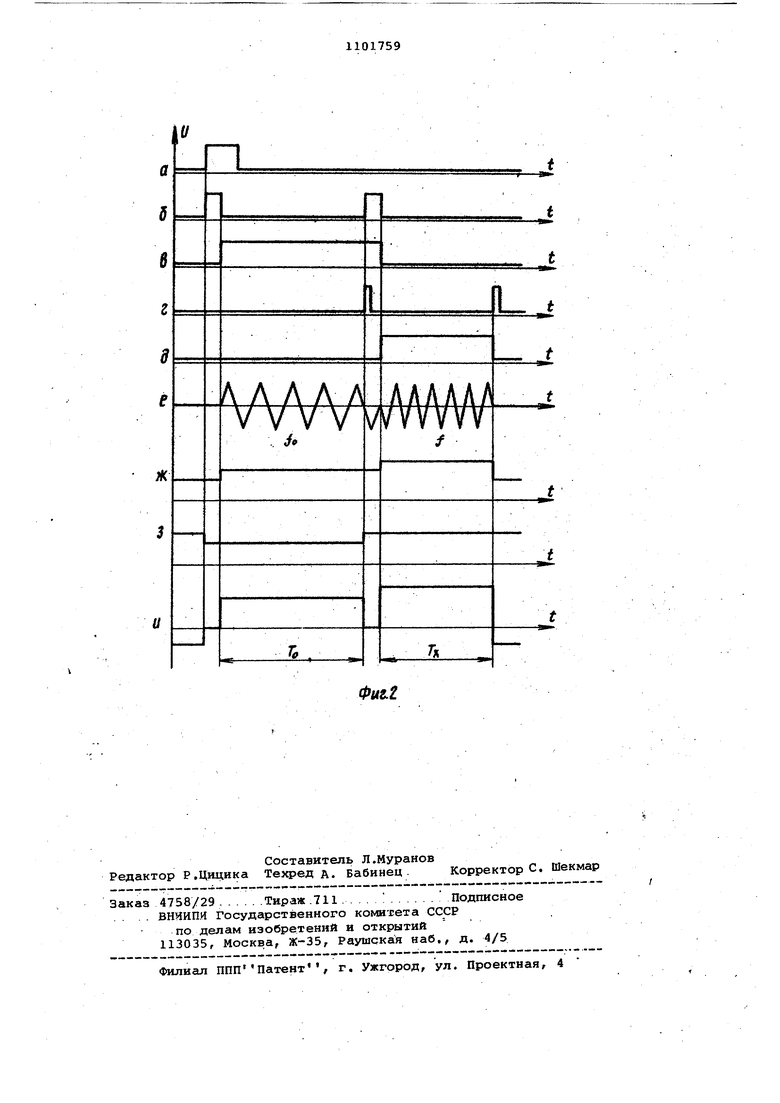

Изобретение относится к технике измерений и может быть использовано для измерения отклонения переходной частоты частотных дискриминаторов, в системах автоматизированного изме рения и контроля параметров радио электронной аппаратуры, в том числе приемников цветного изображения при контрольно-регулировочных работах. Известно устройство для измерения частотной расстройки частотного дискриминатора, содержащее генератор с плавной перестройкой частоты ксшебаний сигнала в пределах линейного участка характеристики испытуемого частотного дискриминатора, выходом соединенного с входом измерителя напряжения постоянного тока, и частотомер, вход которого соединен с выходом генератора, к которому под ключен вход устройства с испытуемым частотным дискриминатором l . Недостатком известногочустройства является значительное время измерения частотной расстройки частотного дискриминатора, обусловленное использованием стандартных измерител ных приборов и отсутствием средств автоматического измерения частотной расстройки. Целью-изо,бретения является сокращение времени измерений. Цель достигается тем, что и устройство для измерения частотной расстройки частотного дискриминатора, содержащее генератор испыт.ательных сигналов, выход которого соединен с первой входной клеммой устройства, и регистрирующий прибор, введены диф ференциальный усилитель, запоминающи блок и блок управления, при этом вторая входная клемма устройства сое динена с одним из входов дифференциального усилителя и с входом запоминающего блока, выход которого соеданен с вторым входом дифференциального усилителя, выход последнего соейинен с входом регистрирующего прибора, выполненного в виде вычислителя отношения напряжений, выходом сое диненного с входом блока управления, первый выход которого соединен с управляющими входами запомнНаютаего бло ка и вычислителя отношения напряжеНИИ, второй и третий выходы блока уп равления соединены ссоответствующим управляющими входами генератора испы тательных сигналов Блок управления выполнен в виде двух элементов И, элемента ИЛИ, формирователя импульсов и распределител импульсов, при этом вход распределителя импульсов соединен с первым выходом блока управления и с выходом формирователя импульсов, а один из выходов распределителя импульсов под ключен к второму выходу блока управления и к одному из входов первого элемента И, а второй выход распределителя импульсов соединен с третьим выходом блока управления и с одним из входов второго элемента И, второй вход которого подключен к входу блока управления и к второму входу .первого элемента И, выход которого соединен с управляющим входом распределители импульсов, выход второго элемента И соедине.н с одним из входов элемента ИЛИ, второй вход которого подключен к входной клемме устройства .Пуск, выход элемента ИЛИ соединен с входом формирователя импульсов. На фиг. 1 приведена структурная схема устройства на фиг, 2 - временные диагракв.1ы, поясняющие его работу. Устройство (фиг. 1) содержит генератор 1 испытательных сигналов фиксированной частоты, испытуемый частотный дискриминатор 2, блок 3 управления, дифф.еренциальный усилитель 4, запоминающий блок 5 и вычислитель 6 отношения напряжений. Блок 3 управления содержит первый и второй элементы И 7 и 8, элемент ИЛИ 9, формирователь 10 импульсов, : распределитель 11 импульсов, входные клеммы устройства 12 и 13 и входную клемму 14 Пуск, Генератор 1 испытательных сигналов выходом соединен с первой входной клеммой 12 устройства, вторая входная клемма 13 устройства соединена с одним из входов диффёренцисшьного усилителя 4 и с входом запоминающего блока 5, выход которого соединен с вторым входом дифференциального усилителя 4, выход последнего соединён с входом регистрирующего прибора, выполненного в виде вычислителя 6 отношения напряжений, выходеом соединенного с входом блока 3 управления, первый выход которого соединен с управляющими входами запомингцощего блока 5 и вычислителя 6 отношения напряжений, второй и третий выходы блока 3 управления соединены с соответствующими управляющими входами генератора 1 испытательных сигналов. Блок 3 управления выполнен в виде двух элементов И 7 и 8, элемента ИЛИ 9, формирователя 10 импульсов и распределителя 11 импульсов . При этом вход распределителя 11 импульсов соединен с первым выходом блока 3 управления и с выходом формирователя 10 импульсов, а один из выходов распределителя 11 импульсов подключен к второму выходу блока 3 управления и к одному из входов первого элемента И 7, а второй выход распределителя 11 импульсов соединен с третьим выходом блока 3 управления и с одним из входов второго элемента И 8, второй вход кото рого подключен к входу блока 3 управления и к второму входу первого элемента И.7, выход которого соединен с управляющим входом распределителя 11 импульсов, выход второго эле мента И 8 соединен с одним из входов элемента ИЛИ 9, второ: вход кото рого подключен к входной клемме 14 устройства Пуск выход элемента ИЛИ 9 соединен с входом формировате ля 10 импульсов. Временные диаграммы (фиг, 2) ото бргокают: а - импульс nycKf S импульсы на первом выходе блока 3 управления; Ь - импульс на втором вы ходе блока 3 управления; 2. - импул сы обратной связи иа выходе вычисли теля 6; (j - импульс на третьем выходе блока 3 управления; в - испыта тельные сигналы на выходе генератор 1; - напряжение на выходе испытуе мого частотного дискриминатрра 2; - напряжение на выходе эапоми- нающего блока 5; ч - напряжение на выходе дифференциального усилителя 4. Устройство работает в три.такта. Перед измерением на генераторе 1 устанавливается одно из фиксированных значений частоты, равное извест ному номинальному значению частоты fjj. настройки нуля испытуемого частотного дискриминатора 2. Генератор 1 снабжен двумя входами управления и выполнен таким образом, что при подаче управляющего сигнала на один его вход частота колебаний выходного сигнала равна f, а при под че ансшогичного сигнала на другой вход на выходе генератора устанавливается сигнал другой частоты f. При .этом независимо от значения частоты первого сигнала fo разность частот i.f f - f const, a амплитуды колебаний обоих сигналов одинаковы. Разность частот if обоих сигналов выбирается таким образом, чтобы выполнялось условие |bf j ufoMj,,,, где u. fo ам максимальное допустимое значение расстройки, частотных дискриминаторов. В первом такте сигнал на входе частотного дискриминатора 2 отсутствует (фиг. 2е). Импульсом Пуск (фиг. 2о|), поступающим через элемент ИЛИ 9 от входной одноименной клеммы 14 устройства, запускается формирователь 10. По первому импульсу, поступающему с выхода формирователя 10 через первый выход блока 3 управления (фиг. 2$) на вхбд запоминающего блока 5, в последнем фиксируется напряжение (фиг. 2) смещеНИН UCM на выходу частотного дискриминатора 2 в случае отсутствия сигнала на его входе. Этим же импульсом вычислитель & устанавливается в исходное состояние. Спадом первого импульса (фиг. 25) распределитель 11 устанавливается в начальное состояние. На этом первый такт завершается, Во втором такте по импульсу, поступающему с выхода распределителя 11 с второго выхода блока 3 (фиг, 2S) на вход генератора 1, на выходе последнего устанавливается СИГНЕШ частоты f(j (фиг, 2е), Этот сигнал-детектируется частотным дискриминатором 2, Напряжение на выходе частотного дискриминатора (фиг, 2) представляет собой алгебраическую сумму напряжений , + U, U|, где U, напряжение первого детектированного сигнала. Это напряжение прикладывается к одному из входов дифференциального усилителя 4, к другому входу которого приложено напряжение UCM (фиг. 2 ) с выхода запоминающего блока 5 На выходах дифференциального усилителя 4 устанавливсиотся два противофазных напряжения с абсолютным значением, равным lKnUJ,| , где Кп - коэффициент передачи дифференциального усилителя. Напряжения с прямого и инверсного выходов дифференциального усилителя 4 поступают на вход вычислителя 6. В последнем реализуется известный принцип двухтактного интегрирования сравниваемых напряжений. Первый такт интегрирования длится в течение эталонного времени Т.) . По истечении этого времени первым импульсом обратной связи (фиг. 2г следующим с выхода вычислителя 6 через последовательно соединенные элемент И 8 и элемент ИЛИ 9, запускается формирователь 10. Второй импульс (фиг. 25) с выхода формирователя 10 через первый выход .блока 3 управления воздействует на управляющий вход вычислителя 6, запрещая интегрирование напряжения. По это:Му же импульсу запоминающий блок 5 фиксир/ет напряжение U с выхода частотного дискриминатора 2, Спадом второго импульса (фиг. 2S) распределитель 11 устанавливается во второе состояние. На этом второй такт заканчивается. В третьем такте работы по третьему выходу блока 3 управления с выхода распределителя 11 на второй вход генератора 1 следует импульс (фиг, 2), по которому на вход частотного дискриминатора 2 поступает сигнал (фиг, 2е) частоты f. На выходе частотного дискриминатора 2 устанавливается напряжение (фиг. 2 равное алгебраической сумме напряжений и + - Uj Я® А2 пряжение детектированного второго сигнала. Это напряжение прикладывает ся к входу дифференциального усилителя 4, к другому входу которого приложено напряжение U| с выхода запоминающего блока 5. На выходе диф ференци ального усилителя 4 устанавли ваются два противофазных напряжения с абсолютным значением, равным IUjp| к„-ид 1 , Эти напряжения прикладываются к входу вычислителя б. По спа ду второго импульса (фиг. 2S) в вычислителе 6 разрешается интегрирование напряжения. Выбор полярности напряжения осуществляется в вычислителе б таким образом, чтобы сумма интегралов напряжений в первом и вто ром тактах интегрирования равнялась нулю. При выполнении указанного усло вия вторым импульсом (фиг. 2г) с вых да вычислителя 6 через элемент И 7 распределитель 11 устанавливается в исходное состояние. На этом цикл измерэния завершается. Подачей импульса Пуск на вход элемента ИЛИ 9 цикл измерений может быть повторен. Математическое выражение, характе ризующее принцип двухтактного интегрирования, имеет вид т - - Uj и TQ - соответственно длите где Т ности второго и перв тактов интегрировани напряжений Uj и U . Из равенства (1) следует, что д тельность Т .второго такта интегрирования однозначно определяет абсолютное отношение напряжений, так как Тд const. интервал Т квантуется импульсами со стабильным периодом to, а интервал Тд задается постоянным числом NO периодов t. При этом равенство (1) имеет вид N - цифровой эквивалент отн шения напряжений. По аналогии с вырг1жснием (2) вычисление отношения напряжений tJ, и ид2 характеризуется равенством где UjL. и и соответственно напряжения детектированных первого и ВТО рого сигналов. Напряжения J и ид2 связаны с параметрами частотного дискриминатора и информативными параметрами испытательных сигналов зависимостями At S.Af, ид2 So Af , где SQ - крутизна демодуляционной характеристики частотного дискриминатора в окрестности номинального значения частоты f(j его настройки; ufo fo fg- частотная расстройка нуля частотного дискриминатора. Здесь ЕО - измеренное значение частоты настройки. С учетом выражений (4) и (5) равенство (3) преобразуется к виду Afo. „ If 0 Соответствующим выбором постоянных величин NO и uf можно получить результат измерения частотной расстройки частотного дискриминатора непосредственно в единицах частоты. При этом знак расстройки нуля также может быть определен, поскольку известен знак крутизны S конкретного частотнЪго дискриминатора, возможность определения знака расстройки нуля вытекает из зависимости (4). Устройство обеспечивает сокращение времени измерений частотной расстройки в 3,2 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2002 |

|

RU2235335C2 |

| Частотный дискриминатор | 1984 |

|

SU1241142A1 |

| Устройство для измерения характеристики частотной избирательности радиоприемника по побочным каналам приема | 1986 |

|

SU1363089A1 |

| Частотный дискриминатор | 1982 |

|

SU1116527A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Анализатор частотных характеристик | 1985 |

|

SU1307373A1 |

| ЧАСТОТНО-МОДУЛИРОВАННЫЙ РАДИОВЫСОТОМЕР | 2003 |

|

RU2263330C2 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для автоматического измерения амплитудно-частотных характеристик | 1986 |

|

SU1379749A1 |

1. УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТНОЙ РАССТРОЙКИ ЧАСТОТНОГО ДИСКРИМИНАТОРА, содержащее генератор испытательных сигналов, выход которого соединен с первой входной клеммой устройства, и регистрирующий прибор, отличающееся тем, что, с целью сокращения времени измерений, в него введены дифференциальный усилитель, запоминающий блок и блок управления, при этом вторая входная клемма устройства соединена, с одним из входов дифференциального усилителя и с входом запоминающего блока, выход которого соединен с вторым входом дифференциального усилителя, выход последнего соединен с входом регистрирующего прибора, выполненного в виде вычислителя отношения напряжений выходом соединенного с входом блока управления, первый выход которого соединен с управляющими входами запоминающего блока и вычислителя отношения напряжений, второй и третий выходы блока управления соединены с соответствующими управляющими входами генератора испытательных сигналов. 2. Устройство по п. 1, отличающееся тем, что блок управления выполнен в виде двух элементов И, элемента ИЛИ, формирователя импульсов и распределителя импульсов, при Этом вход распределителя импульсов соединен с первым выходом блока управления и с выходом формирователя импульсов, а один из выходов распределителя импульсов подключен к второму выходу блока управления и к одi ному из входов первого элемента И, а второй выход распределителя импуль(Л сов соединен с третьим выходом блока управления и с одним из входов втоCZ рого элемента И, второй вход которого подключен к входу блока управления и к второму входу первого элемента И, выход которого соединен с управляющим входом распределителя импульсов, выход второго элемента И соединён с одним из входов элемента ИЛИ, второй вход которого подключен к входной клемме устройства Пуск выход элемента ИЛИ соединен с входом фор мирователя импульсов. сл со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для сцепления и расцепления копровой бабы с бесконечной подъёмной цепью | 1929 |

|

SU21042A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1984-07-07—Публикация

1981-11-19—Подача