настройки амплитуды тестового сигнала, блок 9 контроля амплитуды, масштабный блок 5, переключатель 6, де- мультиплексор 14, блоки 17, 18 интегрирования, вычислители 10, 19. Устройство также содержит исследуемый объект 1, генератор 2 гармонических тестовых сигналов, масштабный блок 4, аналого-цифровой преобразователь 7, формирователь 8 опорных функций, перемножители 11, 12, блок 13 управлеИзобретение относится к информационно-измерительной технике, в частности к устройствам, представляющим собой аналого-дискретные измерители коэффициентов рядов Фурье, используемые для экспериментального определения частотных характеристик приборов и устройств автоматики.

Цель изобретения - повышение точности и быстродействия измерений..

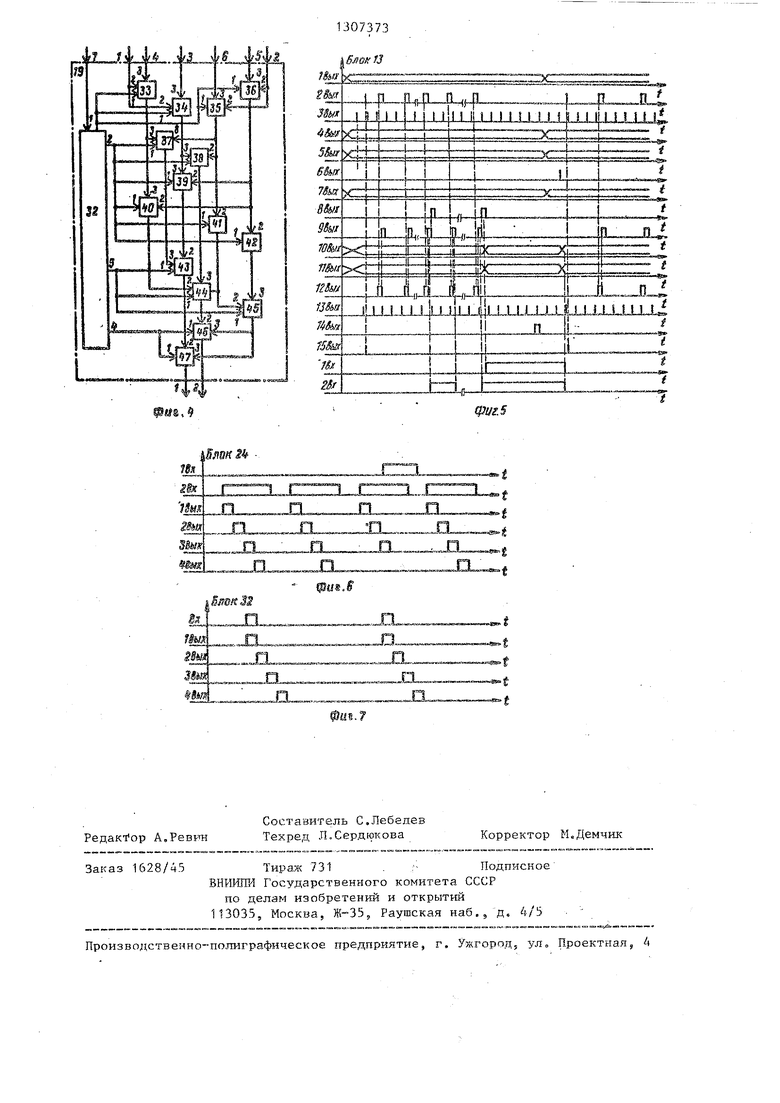

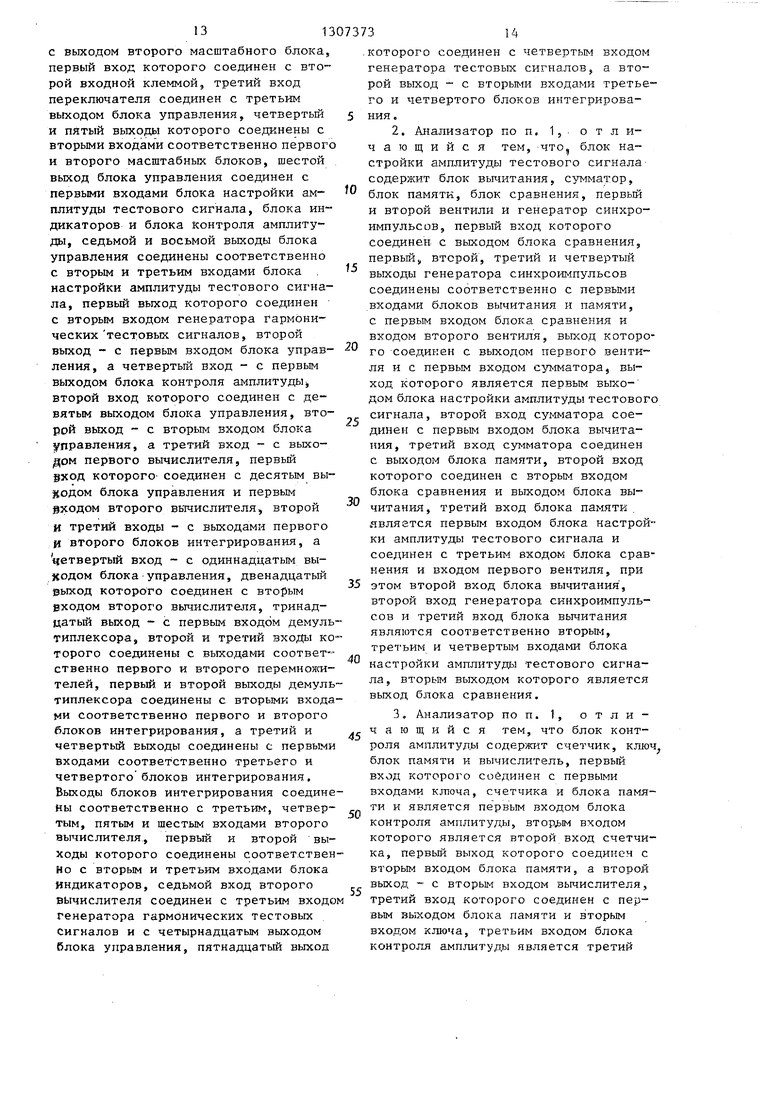

На фиг. 1 - 4 изображены структурная схема анализатора частотных характеристик и его отдельных блоков, на фиг.5-7- временные диаграммы выходных сигналов блоков анализатора.

Анализатор частотных характерис - тик содержит исследуемый объект 1, генератор 2 гармонических тестовых сигналов, блок 3 настройки амплитуды тестового сигнала, первый 4 и второй 5 масштабные блоки, переключатель 6, аналого-цифровой преобразователь 7, формирователь 8 опорных функций, блок 9 контроля амплитуды, пер- вьш вычислитель 10, первый 11 и второй 12 перемножители, блок 13 управления, демультиплексор 14, первый 15, второй 16, третий 17 и четвертый 18 блоки интегрирования, второй вычислитель 19 и блок 20 индикаторов.

Блок 3 настройки амплитуды тестового сигнала содерлшт блок 2П вычита- ния, блок 22 сравнения, блок 23 памяти, генератор 24 синхроимпульсов, первьй 25 и второй 26 вентили и сумматор 27.

ния, блоки 15, 16 интегрирования, блок 20 индикаторов, В описании изобретения приведены также схемы блока 3 настройки амплитуды тестового сигнала, блока 9 контроля амплитуды, вычислителя 19. Устройство обеспечивает автоматическую установку требуемого уровня амплитуды первой гармоники на выходе объекта, что позволяет достичь поставленной цели. 3 з.п. ф-лы, 7 ил.

5

0

5

0

5

Блок 9 контроля амплитуды содержи л ключ 28, блок 29 памяти, вьиислитель 30 и счетчик 31.

Второй вычислитель 19 содержит генератор 32 синхроимпульсов, блоки - 33-40 умножения, первый 41 и второй 42 квадраторы, первый сумматор 43, блок 44 вычитания, второй сумматор 45, первый 46 и второй 47 блоки деления.

Первый выход генератора 2 гармонических тестовых сигналов соединен с выходной клеммой, первый вход с пе зым входом блока 13 управления, второй выход - с входом формирователя 8 опорных функций,-два выхода которого соединены с выходами первого 11 и второго 12 перемножителейу вторые входы которых соединены с выходами аналого-цифрового преобразователя 7. Первые входы первого 15 и второго 16 блоков интегрирования соединены с вторым выходом блока.13 управления. Первый вход первого масштабного блока 4 соединен с первой входной клеммой. Выход переключателя 6 соединен с входом аналого-цифрового преобразователя 7. Первый вход переключателя 6 соединен с выходом первого масштабного блока 4, второй вход - с выходом второго масштабного блока 5, первьш вход которого соединен с второй входной клеммой. Третий вход переключателя 6 соединен с третьим выходом блока 13 управления, четвер- тьй и пятый выходы которого соединены с вторыми входами соответственно первого 4 и второго 5 масштабных

3 , п

блоков. Шестой выход блока 13 управления соединен с первыми входами блока 3 настройки амплитуды тестового сигналаэ блока 20 индикаторов и блока 9 контроля амплитуды. Седьмой и восьмой выходы блока 13 управления соединены соответственно с вторьгм и третьим входами блока 3 настройки амплитуды тестового сигнала, первый выход которого соединен с вторьм входом генератора 2 гармонических тетовых сигналов, второй выход - с первым входом блока 13 управления, а четвертый вход - с первым выходом блка 9 контроля амплитуды, второй вход которого соединен с девятым выходом блока 13 управления, второй выход - с вторым входом блока 13 управления, а третий вход - с выходом первого вычислителя 10, первьш вход которого соединен с десятым входом блока 13 управления и первым входом второго вы вычислителя 19, второй и третий входы с выходами первого 15 и второго 16 блоков интегрирования 5 а четвертый вход с одиннадцатым выходом блока 13 управления, двенадцатый выход которого соединен с вторым входом второг вычислителя 19, тринадцатый выход - с первым входом демультиплексора 14, второй и третий входы которого соединены с вьпсодами соответственно первого 11 и второго 12 перемножителей. Первый и второй выходы демультиплексора 14 соединены с вторыми входами соответственно первого 15 и второго 16 блоков интегрирования, а третий и четвертый выходы с первыми входами соответственно третьего 17 и четвертого 18 блоков интегрирования, Выходы блоков 15-18 интегрирования соединены соответственно с третьим, четвертым, пятым и шестым входами второго вычислителя 19, первый и второй выходы которого соединены соот- ветственно с вторьм и третьш входами блока 20 индикаторов. Седьмой вход второго вычислителя 19 соединен с третьи - входом генератора 2 гармо- ническртх тестовых сигналов и с че- тырнадцатым выходом блока 13 управления, пятнадцатый выход которого сое- д -1нен с четвертым входом генератора 2 гармонических тестовых сш-налов, а второй выход - с вторьтми входами третьего 17 и четвертого 18-блоков интегрирования,

В блоке 3 настроЙ1 и амплитуды тестового сигнала первый вход генератора 24 синхроимпульсов соедпне с выходом блока 22/гравнення, первый, второй, третий и четвертыт: выхоль: генератора 24 синхроимпульсов соеди. нень соответственг{о с первьг- и входами блоков 21 и 23 Бьтитания и памят с первым входом блока 22 сравне пш и входом второго вентиля-26, выход которого соединен с выхода и первог вентиля 25 и с первым входом сумматра 27, выход которого является перв выходом блока 3 настройки амплитуды тестового сигнала. Второй вход сумматора 27 соединен с первьм входом блока 21 вычитания. Третий вход сумматора 27 соединен с выходом блока памяти, второй вход которого соединен с вторым входом блока 22 сравнения и выходом блока 21 вычитания. Третий вход блока 23 памяти является первым входом блока 3 настройки амплитуды тестового сигнала и соединен с третьим входом блока 22 сравнения. Второй вход блока 21 вычитания, второй вход генератора 24 i-i третий вход блока 21 BbrqnTaiinsi являются соответственно вторым,, третью; и четвертым входами блока 3 настройки амплитуды тестового сигнала, вторым вькодом которого является выход блока 22 сравнения,

В блоке 9 контроля амплитуды первый вход вьиислителя 30 соединен с первыми входами ключа 28, счет-с ика 31 и блока 29 памяти и является пер- вьм входом блока 9 контроля амплитуды, вторым входом которого является второй вход счетчика 31, первьш вы- , ход которого соединен с вторым входом блока 29 памяти, а второй выход- со вторьгм входом вычислителя 30, третий вход которого соединен с пер- вЕлм выходом блока 29 памяти и вторьм входом ключа 28. Третьим входом блока 9 контроля амплитуды является третий вход блока 29 памят, второй вькод которого соединен с четвертым входом вычислителя 30, БЬ1ход которого соединен с третьим входом ключа 28, выход которого является первьм выходом блока 9 контроля амплитуды, вторым выходом которого является выход вычислителя 30,

Во втором вычислителе 19 первый выход ге.чзратора 32 синхроимпульсов соединен с первым - - входами первого 33, второго 34, третьего 35 и четвертого 36 блоков :5 ыпожерия,. второй

выход - с первыми входами пятого 37, шестого 38, седьмого 39 и восьмого 40 блоков умножения и первого 41 и второго 42 квадраторов, третий выход - с первыми входами первого

43и второго 45 сумматоров и блока

44вычитания, четвертый выход - с. первыми входами первого 46 и второго 47 блоков деления, вторые входы которых соединены соответственно с вы-

,ходами блока 44 вычитания и первого сумматора 43, а выходы являются пер- Bbw и вторым выходами второго вычислителя 19.Третьи входы блоков 46 и 7 деле- ния соединены с выходом второго сум- .матора 45, второй вход которого соединен с выходом первого квадратора 41, а третий вход - с выходом второго квадратора 42, второй вход кото- рого соединен с вторыми входами седьмого 39 и восьмого 40 блоков умножения и выходом четвертого блока 36 умножения, второй вход-которого соединен с вторым входом третьего блока 35 умножения, выход которого соединен со вторыми входами пятого 37 и шестого 38 блоков умножения и первого квадратора 41. Второй вход первог блока 33 умножения соединен с вторым входом второго блока 34 умножения, выход которого -соединен с третьими входами шестого 38 и седьмого 39 блоков умножения. Выход седьмого блока 39 умножения соединен со вторым . входом первого сумматора 43, третий вход которого соединен с выходом пятого блока 37 умножения, третий вход которого через восьмой блок 40- умножения соединен со вторым входом блока 44 вычитания, а также соединен с выходом блока 33 умножения, третий вход блока 44 вычитания соединен с выходом шестого блока 38 умножения. Первым, вторым, третьим, четвертым, пятым, шестым и седьмым входами второго вычислителя 19 являются соответ ственно второй вход первого блока 33. умножения, второй вход четвертого блока 36 умножения, третий вход второго блока 34 умножения, третий вход первогр блока 33 умножения, третий вход четвертого блока 36 умножения, третий вход третьегб блока 35 умножения и первый вход генера 32 синхроимпульсов.

В качестве исследуемого объекта 1 может быть широкий класс систем

автоматического управления (гидравлические, электрические, системы управления движением различных объектов и др.), состояш;ие из последовательно включенных блоков (например, усилитель мощности, корректирующее устройство, устройство управления, исполнительный механизм и т.п.), которые могут быть охвачены обратными связями (по положению, по скорости и т.д.).

Анализатор частотных характеристик работает следующим образом.

Перед началом работы на задатчи- ках кодов частоты, амплитуды, периода усреднения и масштабов блока 13 управления, предназначенного для формирования сигналов управления парамет- рами синусоидального тестового сигнала, а также синхронизации и управления работой отдельных блоков анализатора в процессе вычисления частотных характеристик,, устанавливаются их величины, определяемые конкретными требованиями эксперимента. Величина кода частоты с первого выхода блока 13 управления поступает на первый вход генератора 2 гармонических тестовых сигналов,, предназначенного для выработки синусоидального сигнала заданной амплитуды и частотв и представляющего собой цифро-аналоговый синтезатор частоты и подготавливает его к генерированию сигнала заданной частоты. Величина масштабных коэффициентов с четвертого и пятого выходов блока 13 управления поступает на вторые (управляющие) входы масштабных блоков 4 и 5- и устанавливаются с помощью преобразователей код-сопротивление требуемые масштабы считывания входного и выходного сигналов;

При включении блока 13 управления на его шестом выходе появляется сигнал, который, поступая на.первые входы блоков 3 настройки амплитудыj блока 20 индикаторов и блока 9 контроля амплитуды, осуществляет обнуление блока 23 памяти,.- блока 22 сравнения, блока 29 памяти,- ключа 28, счетчика 31 и вычислителя 30, а также вызывает- срабатывание сумматора 27 и на его выход поступает сигнал с его второго входа, пропорциональный задаваемой амплитуде выходного сигнала объекта 1, при котором снимается частотная характеристика. Величина амплитуды, установленная на соответ7

ствующем задатчике блока 13 управления, поступает с седьмого выхода блока 13 управления на второй вход блока 3 настройки амплитуды. Сигнал с вьпсода сумматора 27 поступает на второй вход генератора 2 гармонических тестовых сигналов. При этом масштаб выходного усилителя генератора 2 тестовых сигналов устанавливается таким, чтобы он генерировал гармонический сигнал с заданной амплитудой.

На десятом и двенадцатом выходах блока 13 управления появляются сигналы, равные и , которые поступают в вычислители 10 и 19. а на третьем и тринадцатом выходах появляются импульсы . (фиг. 5),. сдвинутые по времени, по которым переключатель 6 соединяет с выходом то свой первый, то второй входы, а в де мультиплексоре 14 третий вход подключается то к первому, то к третьему его выходам, а второй вход - то ко второму, то к четвертому выходам. Затем сигнал с пятнадцатого выхода блока 13 управления поступает на запускающий четвертый вход генератора 2 тестовых сигналов, который начинае 1 енерировать гармонический тестовый сигнал заданной амплитуды и частоты, а также появляется сигнал на втором выходе блока 13 управления, по которому объединяются и перезапускаются блоки 15-18 интегрирования.

Сигнал с первого выхода генератора 2 гармонических тестовых сигналов поступает на исследуемый объект 1 и начинает раскачивать его, а сигнал со второго выхода поступает на вход формирователя 2 опорных функций, в котором формируются коды ортогональ- ньк функций sincojt (первый выход)

и COSCO;t (второй ВЫХОд) .

в блоке 13 управления начинает . работать синхрогенератор,. который определяет порядок появления сигналов на его втором, восьмом, девятом, одиннадцатом и четырнадцатом входах. При этом анализатор находится в режиме контроля окончания переходного процесса в исследуемом объекте 1 ,- и обработке подвергается только выходной сигнал исследуемого объекта l-j .

Сигнал с выхода исследуемого объекта 1- через масштабный блок 5,. в котором его амплитудный диапазон приводится в соответствие с динами-

O

5

073738

ческим диапазоном блоков и устройств анализатора, и переключатель 6 поступает на вход аналого-цифрового преобразователя 7, где сигнал преобразу- .5 ется в цифровой код и поступает на вторые входы перемножителей 11 и 12, на первые входы которых поступает с выходов формирователя 8 опорных функций коды опорных синусов и косинусов. Сигналы с выходов перемножителей 11 и 12, равные соответственно y(t)sinco,-t и y(t)cosQ;t, через де- мультиплексор 14 поступают на вторые входы интеграторов 16 и 15 соответственно, которые осуществляют интегрирование сигналов произведений. Через промежуток времени, равный одному периоду формируемого тестового сигнала, на одиннадцатом выходе блока 13 управления появится сигнал, ко- торьй поступает на четвертьй вход вычислителя 10, в котором по этому сигналу начинается вычисление вели- чины амплитуды первой гармоники,

Через промежуток времени, необходимый для записи выходных сигналов интеграторов 15 и 16 в вычислитель

0 10, на втором выходе блока 13 управления появляется сигнал, по которому интеграторы 15-18 обнуляются и начинается новый цикл интегрирования. Сигнал с выхода вычислителя 10

поступает на третий вход блока 9

контроля амплитуды, который начинает работать по сигналу, поступающему на его второй вход с девятого выхода блока 13 управления. По первому сиг0 налу срабатывает счетчик 31 и на его первом выходе появляется сигнал, а на втором выходе сигнал не появляется. При этом в первой ячейке блока 29 памяти записывается значение ам5 плитуды первой гармоники на первом периоде формирования сигнала, Однаг- ко, так как не срабатывает вычислитель 30, то сигнал на выходе ключа 28 не появляется, а следовательно,

Q не появляются и сигналы на выходах блока 9 контроля амплитуды. При этом блок 3 настройки амплитуды тестового сигнала не срабатывает и генератор 2 гармонических тестовых сигналов

е продолжает генерировать тестовый синусоидальный сигнал с первоначальной заданной амплитудой

При появлении сигналов на одиннадцатом, а затем и на втором выходал блока 13 управления в конце второго периода формируемого тестового сигнала происходит новое сраба- тьгоание вычислителя 10, а интеграторы 15 и 16 обнуляются и запускаются снова. После срабатывания всех блоков вычислителя 10 на его выходе вычисляется значение амплитуды первой гармоники выходного сигнала исследуемого объекта 1 на втором периоде, которое поступает на третий вход блока 9 контроля амплитуды. На второй вход блока 9 контроля амплитуды с девятого выхода блока 13 управления поступает управляющий импульс, по которому сначала появляется сигнал на первом выходе счетчика 31, а затем с некоторой задержкой и на втором его выходе.. При этом записанные значения амплитуд первой гармоники на двух последовательных периодах колебаний поступают в вычислитель 30, в котором вначале вычисляется значение S по формуле

R 9 A n +ATn-f

j

а затем осуществляется сравнение S и- S}.

Если 5 S э, j то сигнал на выходе вычислителя 30 отсутствует, ключ 28 закрыт и анализатор продолжает в режиме контроля окончания переходного процесса в исследуемом объекте 1. Если на одном из периодов -формируемого синусоидального сигнала начинает вьтолняться неравенство & fc э , что сооответствует окончанию переходного процесса в исследуемом объекте 1; и достижению устойчивых колебаний, то на выходе вычислителя 30 появится сигнал. При этом сработает ключ 28 и значение амплитуды первой гармоники выходного сигнала исследуемого объекта 1; поступает на четвертый вход блока 3 настройки амплитуды тестового сигнала, в котором он поступает на третий вход блока 21 вьтитанияс, Одновременно сигнал с выхода вычислителя 30 поступает на второй вход блока 13 управления, разрешая появление на его восьмом выходе управляющего сигнала, Анализатор переходит в режим настройки амплитуды выходного сигнала исследуемого объекта 1,

Сигнал с восьмого выхода блока 13 управления поступает через третий

10

0737310

вход блока 3 настройки амплитуды тестового сигнала на второй вход генератора 24 синхроимпульсов (фиг. 6), Вначале срабатывает блок 21 вычитания и сигнал на его выходе равен разности между кодом установленной амплитуды в блоке 13 управления и кодом амплитуды установившихся колебаний. Эта разность записьшается в блоке 23 памяти при подаче на его второй вход управляющего сигнала, а также поступает на второй вход блока- 22 сравнения, где она сравнивается с нулем при поступлении на его первый вход сигнала с третьего выхода генератора 24 синхроимпульсов. Если этот сигнал отличен от нуля, то сигнал на выходе блока 22 сравнения отсутствует, по сигналу с четвертого выхода генератора 24 синхроимпульсов срабатывает сумматор 27 и происходит вычисление скорректированного сигнала управления амплитудой . генерируемого тестового сигнала. Сигнал с выхода сумматора 27 поступает на первьй вход генератора 2 гармонических тестовых сигналов и изменяет масштаб его выходного усилителя. При этом изменяются величины амплитуды сигнала на выходе исследуемого

15

20

25

30

5

0

5

0

5

объекта 1; и анализатор снова работает в режиме контроля окончания переходного процесса. Если сигнал на выходе блока 21 вычитания близок к нулю, то срабатывает блок 22 сравнения и на его выходе появляется сигнал, который поступает на первый вход генератора 24 синхроимпульсов и на второй выход блока 3 настройки амплитуды тестового сигнала. При подаче сигнала на первый вход генератора 24 синхроимпульсов он возвращается в исходное состояние, сигнал на его чатвертом выходе не появляется и сигнал на вькоде сумматора 27 не изменяется.

Сигнал со второго выхода блока 3 настройки амплитуды тестового сигнала поступает на первый вход блока 13 управления, который переводится в режим вычисления вещественной и мнимой частотных характеристик исследуемого объекта 1, При этом на десятом и двенадцатом выходах блока 13 управления вычисляются новые значения и 2Кц,/Т с учетом числа N периодов усреднения, второй, восьмой, девятьй и одиннадцатьй выходы отклю1

чаются от генератора-синхроимпульсов в результате чего блок 3,настройки амплитуды тестового сигнала, блок 9 контроля амплитуды и вычислитель 10 отключаются.

В одном такте работы анализатора на выходах перемножителей 11 и 12 вычисляются X sincot и X со scot, а в другом -,у sinut и у cosQt соответственно. Эти сигйалы проходят через демультиплексор 14 и по сигналу с тринадцатого выхода блока 13 управления распределя,ются по соответствующим блокам 15-18 интегрирования.

В момент, соответствующий концу времени усреднения, появляется сигнал на четырнадцатом выходе блока 13 управления. Этот сигнал поступает на третий вход генератора 2 гармонических тестовых сигналов -и генерирование тестового синусоидального сигнала прекращается. Этот же сигнал поступа,ет на первый вход генератора 32 синхроимпульсов (фиг. 7) вычислителя 19, запуская его.. По сигналам генератора 32 синхроимпульсов сигналы с выходов блоков 15-18 интеграторов записываются на входных регистрах блоков 33-36 умножения. В вычислителе 19 и блоках 33-36 осуществляется вычисление величины ag , Ьц , вых вых затем по сигналам на выходах генератора 32 синхроимпульсов осуществляется вычисление вещественной и мнимой частоты характеристи исследуемого объекта 1 по формулам

2КА, (1-е

.

)

.,

ZTT.

и.

..-.l /Ч

-сТ,

Значение вещественной частотной характеристики Р(со;) вычисляется на выходе блока 47 деления, мнимой частотной характеристики Q(tt;) - на выходе блока 46 деленияj а генератор 32 возвращается в исходное ждущее состояние. Значения Р(сэ;) и Q(Q;) выводятся на блок 20 индикаторов. На этом процесс вычисления частотных характеристик на заданной частоте прекращается. Для вычисления Р(со;) и Q(cD;) на всех частотах вышеописанный процесс необходимо повторить.

Ш

t5

,

35

30737312

Таким образом, предлагаемый анализатор частотных характеристик позволяет определять частотные характеристики блоков, входящих в состав сложных объектов, когда непосредственная подача на их вход тестового синусоидального сигнала невозможна, или исследовать разомкнутые системы в условиях работы замкнутых систем. При этом происходит автоматическая установка требуемого уровня амплитуды первой гармоники на выходе исследуемого объекта, что особенно важно при исследовании нелинейных систем, и автоматическое определение момента окончания переходных процессов в системе, что существенно повышает точность и быстродействие анализатора (так как не надо вручную устанавливать число периодов раскачки системы с запасом) при исследова- - ниях,систем или звеньев со слабой с. тепенью демпфирования, или с большими постоянными времени.

20

25

т мтик 35

30

40

45

х50

55

Фор мула, изобретения

1. Анализатор частотных характеристик, содержащий генератор гармонических тестовых сигналов, первый выход которого соединен с выходной клеммой, первый вход - с первым выходом блока управления, второй выход - с выходом формирователя опорных функций, два выхода которого соединены с первыми входами соответственно первого и второго перемножителей, вторые входы которых соединены с выходом аналого-цифрового преобразователя, первый и второй блоки интегрирования, первые входы которых соединены с вторым выходом блока управления, блок индикаторов и первый масштабный блок, первый вход которого соединен с первой входной клеммой,. отличающийся тем, .что, с целью повышения точности и быстродействия измерений, в него введены блок настройки амплитуды тестового сигнала, блок контроля амплитуды, второй масштабный блок, переключатель, демультиплексор, третий и четвертый блоки интегрирования и первый и второй вычислители, причем выход перек1почателя соединен с входом аналого-цифрового преобразователя , первый вход переключателя соединен с выходом первого масштабного блока, второй вход -.

131

с выходом второго масштабного блока, первый вход которого соединен с второй входной клеммой, третий вход переключателя соединен с третьим выходом блока управления, четвертый и пятый выхода которого соединены с вторыми входами соответственно первог и второго масштабных блоков, шестой выход блока управления соединен с первыми входами блока настройки амплитуды тестового сигнала, блока индикаторов и блока контроля амплитуды, седьмой и восьмой выходы блока управления соединены соответственно с вторым и третьим входами блока . настройки амплитуды тестового сигнала, первьш выход которого соединен с вторым входом генератора гармонических тестовых сигналов, второй выход - с первым входом блока управления, а четвертый вход - с первым выходом блока контроля амплитудыj второй вход которого соединен с девятым выходом блока управления, второй вькод - с вторым входом блока управления, а третий вход - с выходом первого вычислителя, первый §ход которого- соединен с десятым выводом блока управления и первым уходом второго вычислителя, второй И третий входы - с выходами первого И второго блоков интегрирования, а четвертый вход - с одиннадцатым выходом блока управления, двенадцатый выход которого соединен с вторым входом второго вычислителя, тринадцатый выход - с первым входом демуль типлексора, второй и третий входы которого соединены с выходами соответственно первого и второго перемнояси- телей, первый и второй выходы демуль типлексора соединены с вторыми входами соответственно первого и второго блоков интегрирования, а третий и четвертый выходы соединены с первыми входами соответственно третьего и четвертого блоков интегрирования. Выходы блоков интегрирования соединны соответственно с третьим, четвер

3, Анализатор по п. 1, отличающийся тем, что блок контроля амплитуды содержит счетчик, клю блок памяти и вычислитель, первый вход которого соединен с первыми входами , счетчика и блока памя ти и является первым входом блока контроля амплитуды, входом которого является второй вход счетчи ка, первый выход которого соединен с вторым входом блока памяти, а второй выход - с вторым входом вычислителя.

вычислителя, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока индикаторов, седьмой вход второго вычислителя соединен с третьим входом третий вход которого соединен с пер- генератора гармонических тестовых сигналов и с четырнадцатым выходом блока управления, пятнадцатый выход

вым выходом блока памяти и вторым входом кл50ча, третьим входом блока контроля амплитуды является третий

3

14

которого соединен с четвертым входом генератора тестовых сигналов, а второй выход - с вторыми входами третьего и четвертого блоков интегрирования ,

2. Анализатор по п, 1, отличающийся тем, что блок настройки амплитуды тестового сигнала содержит блок вьтитания, сумматор, блок памяти, блок сравнения, первый и второй вентили и генератор синхроимпульсов, первый вход которого соединен с выходом блока сравнения, первый, второй, третий и четвертый выходы генератора синхроимпульсов соединены соответственно с первыми .входами блоков вычитания и памяти, с первым входом блока сравнения и входом второго вентиля, выход которого соединен с выходом первого вентиля и с первым входом сумматора, выход, которого является первым выхо- дом блока настройки амплитуды тестовог сигнала, второй вход сумматора соединен с первым входом блока вычитания, третий вход сумматора соединен с выходом блока памяти, второй вход которого соединен с вторым входом блока сравнения и выходом блока вычитания, третий вход блока памяти .

является первым входом блока настройки амплитуды тестового сигнала и соединен с третьим входом блока сравнения и входом первого вентиля, при этом второй вход блока врлчитания , второй вход генератора синхроимпульсов и третий вход блока вычитания являются соответственно вторьш, третьим и четвертым входами блока настройки амплитудд51 тестового сигнала , вторым выходом которого является выход блока сравнения.

3, Анализатор по п. 1, отличающийся тем, что блок контроля амплитуды содержит счетчик, ключ блок памяти и вычислитель, первый вход которого соединен с первыми входами , счетчика и блока памяти и является первым входом блока контроля амплитуды, входом которого является второй вход счетчика, первый выход которого соединен с вторым входом блока памяти, а второй выход - с вторым входом вычислителя.

третий вход которого соединен с пер-

третий вход которого соединен с пер

вым выходом блока памяти и вторым входом кл50ча, третьим входом блока контроля амплитуды является третий

151

вход блока памяти, второй выход которого соединен с четвертым входом вычислителя, выход которого соединен с третьим входом ключа, выход которого является первым выходом блока контроля амплитуды, вторым выходом которого является выход вычислителя.

4. Анализатор по п. 1, отличающийся тем, что второй вьиислитель содержит генератор синхроимпульсов, восемь блоков умножения, два квадратора, первый и второй сумматоры, блок вычитания и два блока

10

второй вход которого соединен с вторыми входами седьмого и восьмого блоков умножения и выходом четвертого блока умножения,, второй вход которого соединен с вторым входом третьего блока умножения, выход кото рого соединен с вторыми вxoдa пI пято го и шестого блоков умножения и первого квадратора, второй вход первого блока умножения соединен с вторым входом второго блока умножения, выход которого соединен с третьими входами шестого и седьмого блоков умножения, выход седьмого блока умно

- J- - - Уделения, причем первьй выход генера- J жения соединен с вторым входом пертора синхроимпульсов соединен с первыми входами первого, второго, третьз- го и четвертого блоков умножения, второй выход - с первыми входами пятого, шестого седьмого, восьмого блоков умножения и первого и второго квадраторов,, третий выход - с первыми входами первого и второго сумматоров и блока вьртитания, четвертый выход - с первыми входами первого и второго блоков деления, вторые вхо- дь которых соединены соответственно с выходами блока вычитания и первого сумматора, а выходы являются первым и вторым вькодами второго вычислителя, третьи входы блоков деления соединены с выходом второго сумматора, второй вход которого соединен с выходом первого квадратора, а третий вход - с выходом второго квадратора.

20

25

вого сумматора, третий вход которого соединен с выходом пятого блока умно жения, третий вход которого через восьмой блок умножения соединен с вторым входом блока вычитания, а так же соединен с выходом первого блока умножения, третий вход блока вычитания соединен с выходом шестого блока умножения, при этом первьм, вторым третьим, четвертым, пятым, шестым и седьмым входами второго вычислителя являются соответственно второй вход первого блока умножения, втогГой вход четвертого блока умножения,

30 третий вход второго блока y iнoжeния, третий вход первого блока умножения, третий вход четвертого блока зТ Шоже- ния, третий вход третьего блока умножения И первый вход генератора син

35 хроимпульсов.

6

второй вход которого соединен с вторыми входами седьмого и восьмого блоков умножения и выходом четвертого блока умножения,, второй вход которого соединен с вторым входом третьего блока умножения, выход которого соединен с вторыми вxoдa пI пятого и шестого блоков умножения и первого квадратора, второй вход первого блока умножения соединен с вторым входом второго блока умножения, выход которого соединен с третьими входами шестого и седьмого блоков умножения, выход седьмого блока умножения соединен с вторым входом пер

вого сумматора, третий вход которого соединен с выходом пятого блока умножения, третий вход которого через восьмой блок умножения соединен с вторым входом блока вычитания, а также соединен с выходом первого блока умножения, третий вход блока вычитания соединен с выходом шестого блока умножения, при этом первьм, вторым третьим, четвертым, пятым, шестым и седьмым входами второго вычислителя являются соответственно второй вход первого блока умножения, втогГой вход четвертого блока умножения,

третий вход второго блока y iнoжeния, третий вход первого блока умножения, третий вход четвертого блока зТ Шоже- ния, третий вход третьего блока умножения И первый вход генератора синхроимпульсов.

ф{/«. I

фиг.З

I BJiGK 13

-iP ,jJl.,-....,.,,.,,. .„..,.:„,«„„„П,5„

njjjmjjjjj

,jJl.,-....,.,,.,,. .„..,.:„,«„„

njjjmjjjjj

tfg.

ткт

Ж5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения параметров динамического звена | 1987 |

|

SU1478194A1 |

| Устройство для измерения чистого запаздывания инерционного звена | 1984 |

|

SU1236430A1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

| Устройство для определения параметров передаточной функции линейного динамического объекта | 1988 |

|

SU1585782A1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ КООРДИНАТ ИСТОЧНИКА РАДИОИЗЛУЧЕНИЯ | 2005 |

|

RU2283505C1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 2007 |

|

RU2339988C1 |

| СПОСОБ ПЕЛЕНГАЦИИ РАДИОСИГНАЛОВ И ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2383897C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НАВИГАЦИОННЫХ СИГНАЛОВ ГЛОНАСС, GPS И ГАЛИЛЕО | 2010 |

|

RU2435307C1 |

| Устройство для регулирования давления | 1988 |

|

SU1674075A1 |

| СПОСОБ АДАПТИВНОГО ИЗМЕРЕНИЯ ПРОСТРАНСТВЕННЫХ ПАРАМЕТРОВ ИСТОЧНИКОВ РАДИОИЗЛУЧЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2423719C1 |

Изобретение относится к области ннйормацио Ко-измерительной техники. Может быть использовано для экспериментального определения частотных характеристик приборов и устройств автоматики. Цель изобретения - повышение точности и быстродействия измерений. Для достижения поставленной цели в устройство введены блок 3 sRshi л м i j BHajvl .

Редактор A.PesFfH

Составитель С.Лебелев Техред Л.Сердюкова

Заказ 1628/45 Тираж 731 . - Подписное ВНИЩШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул Проектная, 4

Корректор М.Демчик

| Края машиниста | 1937 |

|

SU54607A1 |

| СССР кл, Патент США № 3808526, G 01 R 23/16 | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1987-04-30—Публикация

1985-03-22—Подача