тыи вход которого соединены соответственно с выходом и вторым входом третьего элемента И, первый и второй входы - с одноименными входаьи третьего элемента ИЛИ, соединенного выходом через первый элемент задержки с первым входом четвертого элемента И, непосредственно - с первым входом вьгчитающего счетчика, выход которого соединен через дешифратор нуля с вторым входом четвертого элемента И, соединенного выходом с вторым входом второго элемента ИЛИ, вход второго формирователя импульсов соединен с выходом дешифратора нуля а выход - с третьим выходом блока и с первым входом счетчика адреса, соединенного вторым входом через второй элемент задержки с выходом второго элемента И и с первым входом блока памяти, соединенного вторым входом с выходом фотосчйтывающего блока, третьим входом - с выходом счетчика адреса, соединенного третьи входом с выходом клавишного переключателя, первый выход блока памяти соединен с первым входом дешифратора адреса, соединенного первым выходом с вторым входом первого триггера, вторые выходы блока памяти соединены с соответствующими первыми входами первого, второго, третьего и четвертого блоков элементов И, первый выход первого блока элементов И соединен с вторым входом вычитающего счетчика, второй вькод - с первым входом дешифратора адреса, второй и третий входы которого соединены с первыми выходами соответственно второго и третьего блоков элементов И, вторым выходом - с вторым входом четвертого блока элементов И, первые выходы четвертого блока элементов И соединены с первой группой первых выходов блока, вторые выходы третьего и второго блоков элементов И соединены соответственно с

второй и третьей гр/ппами выходов блока.

3, Устройство по п.1, о т л и чающееся тем, что формирователь готовности содаржит индикатор брака, соединенный зходом с первым выходом второго триггера и с первьтм входом четвертого элемента ИЛИ, соединенного вторым входом с первым входом второго триггера, с первым входом третьего триггера и через третий формирователь импульсов с третьим входом форм; рователя, вход индикатора годности соединен с выходом четвертого триггера, соединенного первым ВХОД1ТМ с выходом пятого элемента И, вторым входом с выходом четвертого :элемента ИЛИ, второй вход второго триггера соединен с выходом шестого элемента И, соединенного первым входом с вторым входом формирователя, вторым входом - с первым выходом третьего триггера, с вторым зыходом формировтеля, с первым входом пятого элемента И и с первым входом элемента И-Н второй выход третьего триггера через первый диод соединен с четверты выходом формирователя, первый вход которого соединен с вторым входом пятого элемента И, третий вход которого соединен с вторым выходом второго триггера, второй вход третьго триггера соединен с выходом седьмого элемента И, пе)вый вход которого соединен с пятым входом формирователя, второй вход - с первым выходом пятого тригге)а, соединенного первым входом с четвертым входом формирователя, вторим входом через замыкающую кнопку - с шиной питания устройства, вторым 1 ыходом - с вторым входом элемента И-НЕ, соединенного вькодом через второй диод с третьим выходом формирователя, через инвертор - с первым выходом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Устройство для оценки результатов допускового контроля | 1975 |

|

SU752232A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1357883A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

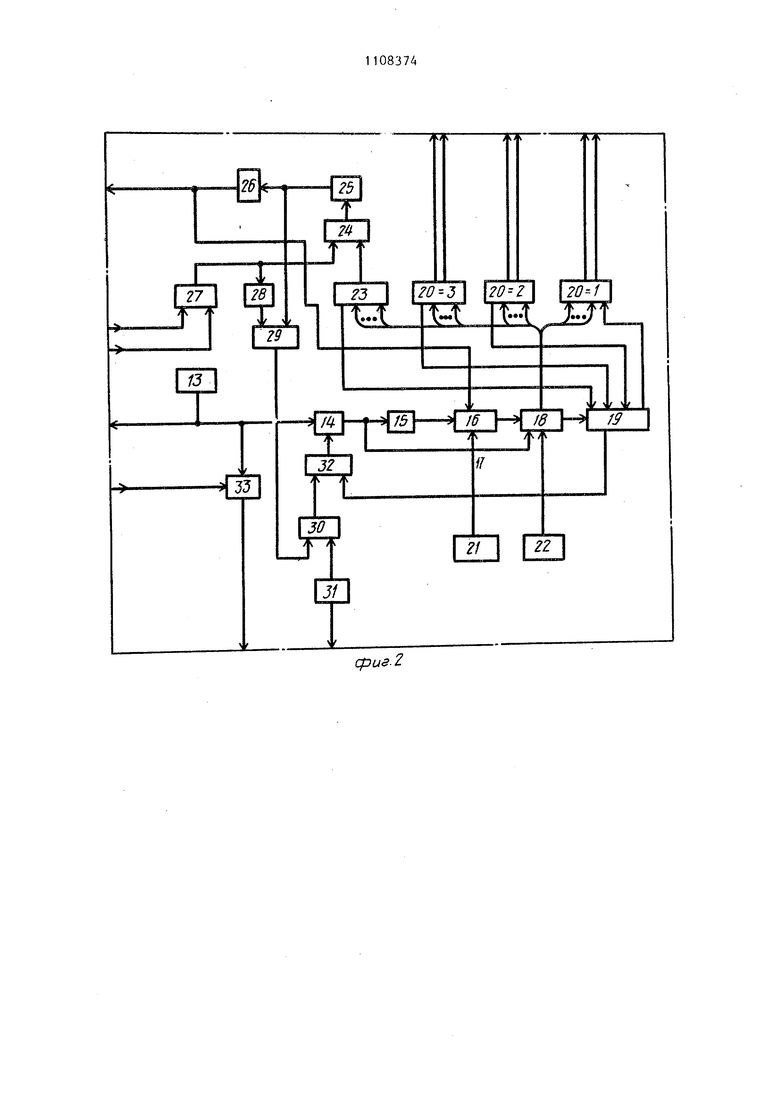

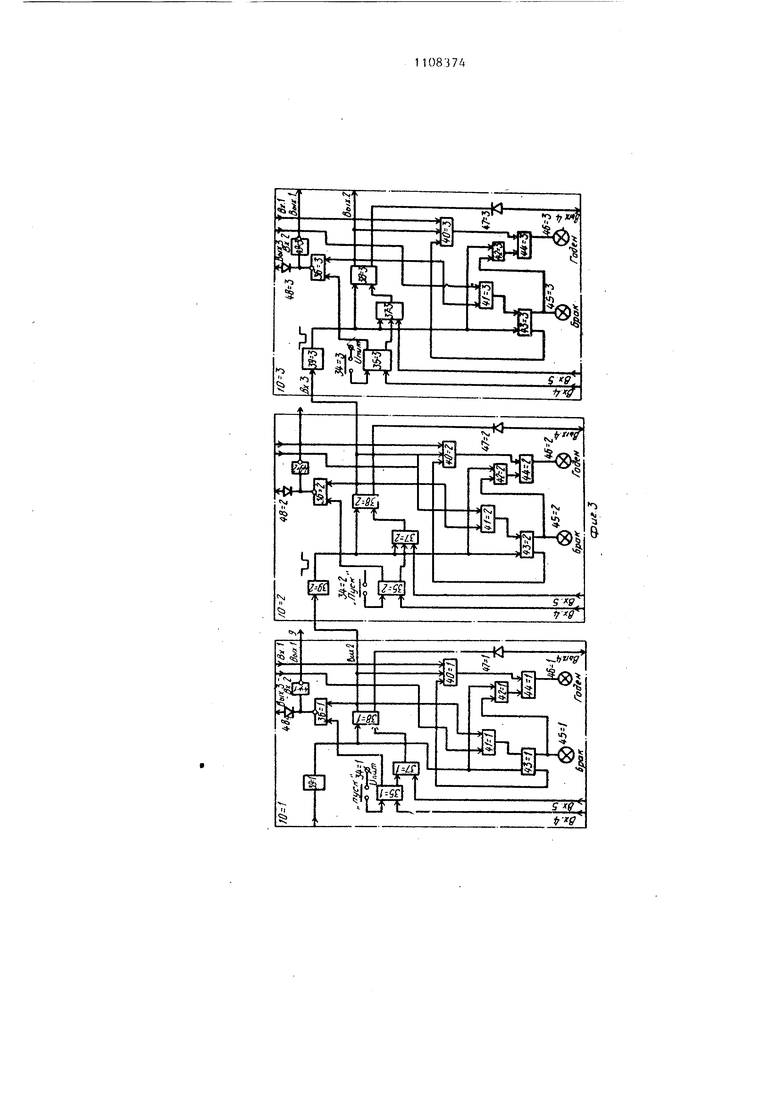

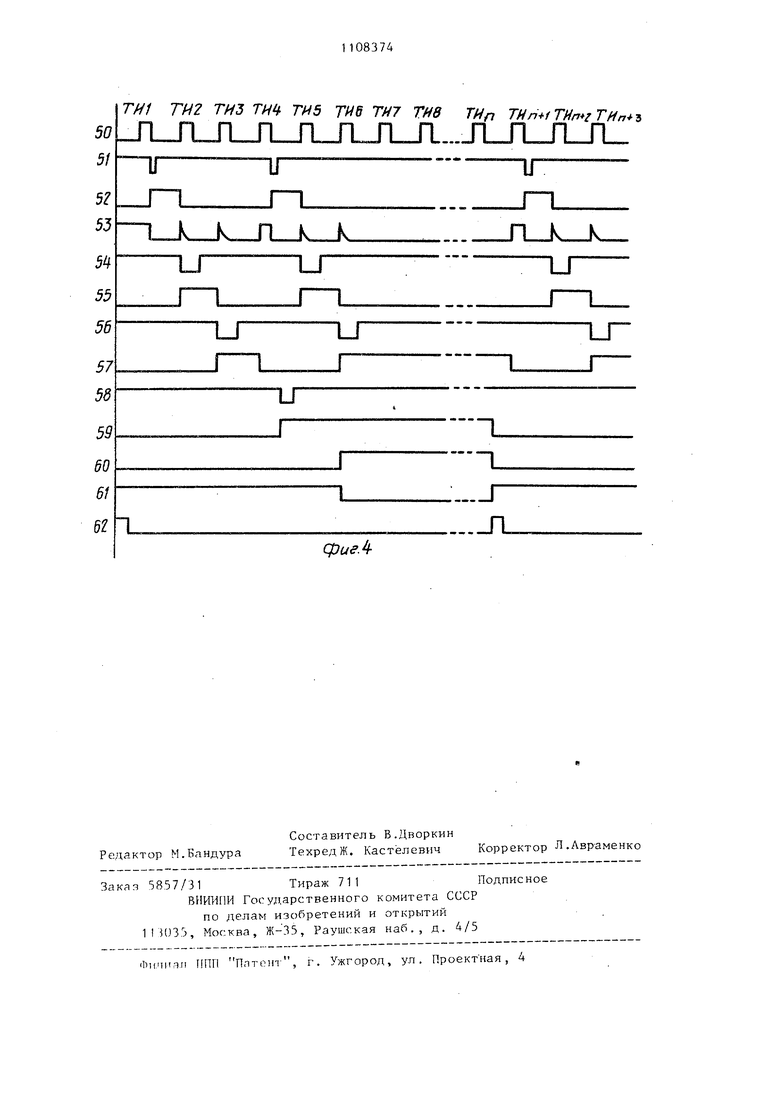

1. МНОГОПОСТОВОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ, содержащее блок источников сигналов воздействий и измерительный блок, подключенные выходами и входа-ми к соответствующим 1л-парам горизонтальных шин измерительно-матричного коммутатора, рабочие посты, содержащие элементы коммутации, каждая из k-nap вертикальных тин измерительноматричного коммутатора соединена через соответствующие элементы коммутации каждого из рабочих постов с клеммами для подключения выводов контролируемых электронных схем, управляющие входы измерительного матричного коммутатора подключены к выходам соответствующих регистров, управляюЕ(не входы блока источников сигналов Бездействий и измерительного блока соединены с соответствующими первой и второй группами первых выходов блока управления, первый и второй входы которого соединены соответственно с выходами Годен и Брак измерительного блока и с первым и вторьм входами формирователей готовности, третья группа первых выходов блока управления соединена с соответствующими входами ьЙБЛИнП регистров, второй выход - с третьим входом первого формирователя готовности, третий выход - с четвертыми входами формирователей готовности, четвертый выход - с пятыми входами формирователей готовности, третий вход - с третьими выходами формирователей готовности, четвертый вход с четвертыми выходами формирователей готовности, второй выход каждого i-го формирователя готовности соединен с третьим входом 1+1-го формирователя готовности, отличающееся тем, что, с целью расширения области применения, повышения надежности устройства, в него введены К первых элементов ИЛИ, (Л а в каждый рабочий пост введены К первых элементов И, входы каждого из К первых элементов ИЛИ соединены с выходами соответствующих регистров, их выходы - с первыми входами первых элементов И данного рабочего поста, выходы которых соединены с входами соответствующих элементов 00 коммутаций, а вторые входы - с персо вым выходом формирователя готовнос ти данного поста. 2. Устройство по п.1, о т л и 4 чающееся тем, что блок управления содержит генератор тактовых импульсов, соединенный выходом с четвертым выходом блока и с первьми входами второго и третьего элементов И, второй вход второго элемента И соединен с выходом первого триггера, первый вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен через первый формирователь импульсов с третьим входом бдока, второй выход и четвер

Изобретение относится к измерительной технике и предназначено для использования в системах контроля электрических параметров электронных схем, в частности интегральных микросхем. J1 Известно многопостовое устройство Для контроля параметров электронных схем, содержащее блок управления рабочие посты с коммутаторами для подключения контролируемых схем, коммутатор выводов схемы, к горизонтальным шинам коммутатора выводов (измерительного коммутатора) схемы подключены блоки программных источников и измерительньй блок, а к вертикальным шинам - входы коммутаторов рабочих постов, к выходам последних подключены выводы контролируемых схем t1. В данном устройстве по заданной блоком управления программе блоки nport)aMMHbJx источников и измерительный блок через выбранные вертикальные шины коммутатора вьгеодов и коммутатор рабочего поста подключаются к выводам контролируемой схемы, затем блоки программных источников и измерительный блок последовательно формируют тестовые условия, т.е. сигналы воздействия и режим измерения параметров контролируемой схемы Однако с вертикальными шинами соединяются все вьшоды контролируемой схе мы независимо от использования их по схеме измерения в данном тесте. А так как линия связи рабочего поста с коммутатором выводов имеет распре деленные емкости относительно корпу са устройства, то в тесте происходи заряд емкости СН невыбранных выводо контролируемой схемы. Между тестами заряд емкостей СН изменяется незначительно, и поэтому переключение коммутатора выводов происходит под током, так как коммутационные элементы выполнены часто на механических контактах (например, герконах типа КЭМ 1А), то это вызывает их повьпиенный износ. Если контролю подлежит микросхема с входными сигналами с нормированной длительностью фронта (среза) например многоразрядные счетчики, то из-за наличия емкости СН происхо дит завал фронта выходного импульса триггера первого разряда и триггер второго разряда переключаться не будет. Таким образом, данный класс микросхем на известном устройстве контролироваться не может, что. сужает область его применения. Наиболее близким техническим решением к предлагаемому является многопостовое устройство для контроля 4 параметров электронных схем, содержащее блок источников сигналов воздействий и измерительный блок, подключенный к соответствующим п-парам горизонтальных шин измерительно-матричного коммутатора, рабочие посты, содержащие элементы коммутации, каждая нз К-пар вертикальных шин измерительно-матричного коммутатора соединена через соответствующие элементы коммутации казвдого из рабочих постов с клеммами для подключения выводов контролируемых электронных сЛем, управляющие входы измерительного матричного коммутатора подключены к выходам соответствующих регистров, управляющие входы блока источников сигналов воздействий и измерительного блока соединены с соответствующими первой и второй группами первых выходов блока управления,, первый и второй входы которого соединены соответственно с выходами Годен и Брак измерительного блока и с первым и вторым входом формирователей готовности, третья группа первых выходов блока управления соединена с соответствующими входами регистров, второй выход - с третьим входом первого формирователя готовности, третий выход - с четвертыми входами формирователей готовности, четвертый выход - с пятыми -входами формирователей готовности, третий вход - с третьими выходами формирователей готовности, четвертый вход с четвертьми выходами формирователей готовности, .второй выход каждого (-ГО формирователя готовности соединен с третьим входом каждого i+1-го формирователя готовности 2. Известное устройство имеет шесть рабочих постов, причем последний пост удален от измерительного коммутатора на расстояние более 10 м. При этом величина емкости СН достигает 5-6 тыс.пФ. В устройстве все вьтоды контролируемой схемы подключаются к вертикальным шинам измерительного коммутатора также независимо от состояния последнего и переключение его коммутационных элементов производится под током разряда емкости СН, -j на который, кроме того, происходит завал фронтов. Поэтому известное многопостовое устройство контроля параметров электронных схем используется преимущественно для проверки

S

схем с комбинационной логикой (схемы типа И-НЕ, ИЛИ-НЕ и т.п.) с ненормированными переходными процессами. Для контроля микросхем, требующих для переключения нормированных по времени входных сигналов (например, многоразрядных счетчиков, регистров сдвига и т.п.), указанное устройство пе подходит.

Таким образом, недостатками известного многопостового устройства контроля параметров электронных схем являются ограниченность области применения и низкая надежность.

Цель изобретения - расширение области применения устройства и повышение его надежности.

Поставленная цель достигается тем, что в многопостовое устройство для контроля параметров электронных схем, содержащее блок источников сигналов воздействий и измерительный блок, подключенные выхог.ами и входами к соответствующим п-парам горизон тальных шин измерительно-матричного коммутатора, рабочие посты, содержащие элементы коммутации, каждая из К-пар вертикальных шин измерительноматричного коммутатора соединена через соответствующие элементы коммутации каждого из рабочих постов с клеммами для подключения выводов контролируемых электронных схем, управляющие входы измерительного матричного коммутатора подключены к выходам соответствующих регистров, управляющие входы блока источников сигналов воздействий и Р1змерительного блока соединены с соответствующими первой и второй группами первых выходов блока управления, первый и второй входы которого соединены соот ветственно с выходами Годен и Брак измерительного блока и с первым и вторым входами формирователей готовности,третья группа первых выходов блока управления соединена с соответствующими входами регистров, второй выход - с третьим входом первого формирователя готовности, третий выход - с четвертыми входами формирователей готовности, четвертый выход - с пятыми входами формирователей готовности, третий вход - с третьими выходами формирователей готовности, четвертый вход - с четвертыми выходами формирователей готовности, второй выход каждого -гп формирователя готовности соединен

0837А6

с третьим входом i+l-ro формирователя готовности, введены К первых элементов ИЛР:, а в каждый рабочий пост введены К первых элемен, тов И, входы каждого из К первых элементов ИЛИ соединены с выходами соответствующих регистров, их выходы - с первыми входами первых элементов И данного рабочего поста,

10 выходы которых соединены с входами соответствующих элементов коммутаций, а вторые входы - с первым выходом формирователя готовности данного поста о

t5 При этом блок управления содержит генератор тактовых импульсов, соединенньй выходом с четвертым выходом блока и с первыми входами второго и третьего элементов И, второй вход

20 второго элемента И соединен с выходом первого триггера, первый вход которого соединен с выходом второго элемента ИЛИ, первы) вход которого соединен через перв:зш формирователь

5 импульсов с третьим входом блока , второй выход и четвзртый вход которого соединены соответственно с выходом и вторым входом третьего элемента И, первый и второй входы - с одноименными входами третьего элемен0та ИЛИ, соединенного выходом через первый элемент задержки с первым входом четвертого элемента И, непосредствен ю - с первым входом вычитающего счетчика, выход которого

соединен через дешифратор нуля с вторым входом четвертого элемента И, соединенного выходом с вторым входом второго элемента ИЛИ, вход второго формирователя импульсов со0единен с выходом дешифратора нуля, а выход - с третьим выходом блока и с первым входом счетчика адреса, соединенного вторым входом через второй элемент задержки с выходом

второго элемента И ; с первым входом блока памяти, соединенного вторь м входом с выходом фотосчитывающего блока, третьим входом - с выходом счетчика адреса, соединенного

0 третьим входом с выходом клавищного переключателя, первой выход блока памяти соединен с первым входом дешифратора адреса, соединенного первым выходом с вторыч входом первого

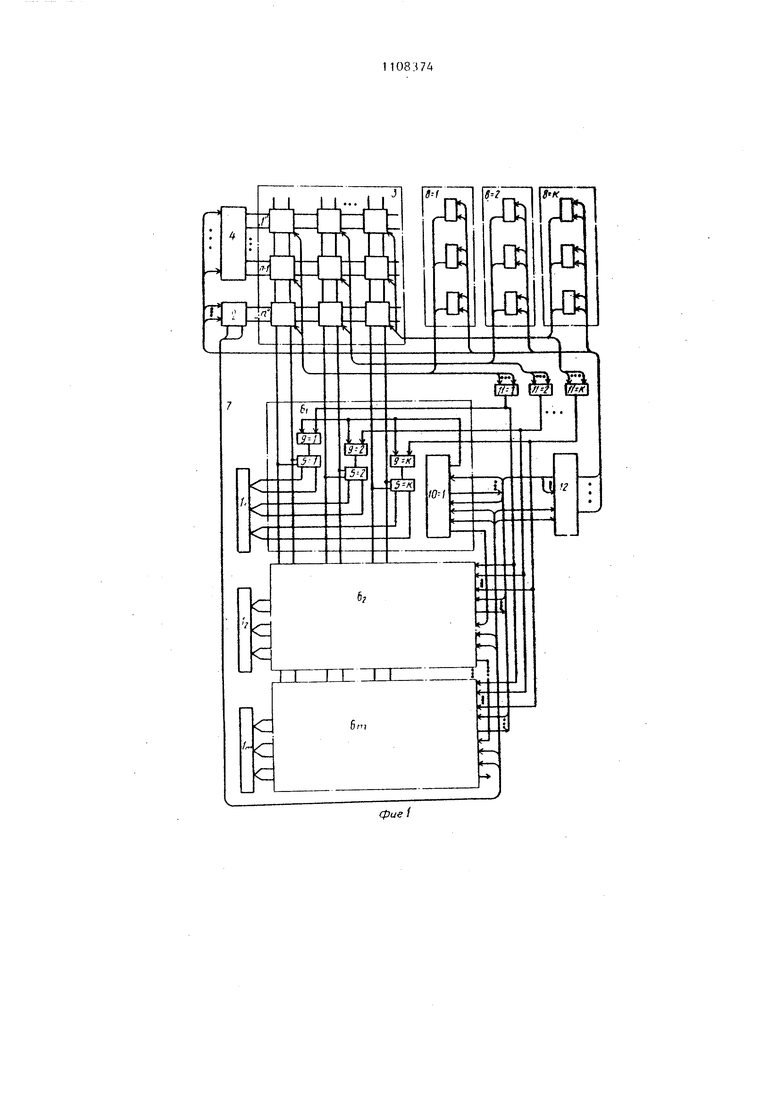

S триггера, вторые вык:оды блока памяти соединены с соответствующими первыми входами первого, второго, третьего и четвертого блоков эле7ментов И, первый выход первого блока элементов И соединен с вторым входом вычитающего счетчика, второй выход - с первым входом дешифратора а;чреса, второй и третий входы которого соединены с первыми выходами соответственно второго и третьего блоков элементов И, вторым выходом с вторым входом четвертого блока элементов И, первые выходы четверто го блока элементов И соединены с первой группой первых выходов блока вторые выходы третьего и второго блоков элементов И соединены соотве ственно с второй и третьей группами выходов блока, Кроме .того, формирователь готовности содержит индикатор брака, соединенный входом с первым выходом второго триггера и с первым входом четвертого элемента ИЛИ, соединенно го вторым входом с первым входом второго триггера, с первым входом третьего триггера и через третий фо мирователь импульсов с третьим входом формирователя, вход индикатора годности соединен с выходом четвертого триггера, соединенного первым входом с выходом пятого элемента И, вторым входом с выходом четвертого элемента ИЛИ, второй вход второго триггера соединен с выходом шестого элемента И, соединенного пе вым входом с вторым входом формирователя, вторым входом - с первым вы ходом третьего триггера, с вторым выходом формирователя, с первым вхо дом пятого элемента И и с первым входом элемента И-НЕ, второй выход третьего триггера через первый диод соединен с четвертью выходом формирователя, первый вход которого соединен с вторым входом пятого элеме та И, третий вход которого соединен с вторым выходONf второго триггзра, второй вход третьего триггера соеди нен с выходом седьмого элемента И, первый вход KOTjoporo соединен с пятьнч входом формирователя, второй вход - с первым выходом пятого триг гера, соединенного первым входом с четвертым входом формирователя, вто рым входом через замыкающую кнопку с шиной питания устройства, вторым выходом - с вторым входом элемента И-НЕ, соединенного выходом через второй диод с третьим выходом форми рователя, через инвертор - с первым вькодом формирователя. 48 На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2 структурная схема блока управления; на фиг. 3 - структурная схема формирователей готовности трех рабочих постов-, на фиг. 4 - временная диаграмма совместной работы трех рабочих постов. Устройство для контроля электронных схем 1 1-1 /г7 содержит измерительный блок 2, измерительный матричный коммутатор 3. блок 4 источников сигналов воздействий, элементы коммутации . рабочие посты , шину Годён-брак 7, регистры , первые элементы И, формирователи готовности, первые элементы 11 Н ИЛИ, блок 12 управления. Блок 4 источников сигналов воздействий состоит, например, из программируемых источников напряжения и тока, построенных на последЬвательно соединенных и охваченных обратной связью цифро-аналоговых преобразователей и усилителях мощности . Измерительный блок 2 состоит, например, из цифрового управляемого измерительного прибора, цифрового компаратора и регистров граничных значений. Блок 12 управления (фиг.2) содержит генератор 13 тактовых импульсов, второй элемент 14 И, второй элемент 15 задержки, счетчик 16 адреса, вход 17 счетчика 16 адреса, блок 18 памяти, дешифратор 19 адреса, четвертьй , третий , второй блоки элементов И, клавишный переключатель 21, фотосчитывающий блок 22, первый 23 блок элементов И, вычитающий счетчик 24, дептфратор нуля 25, второй формирователь 26 импульсов, третий элемент 27 ИЛИ, первый элемент 28 задержки, четвертый элемент 29 И, второй элемент 30 ИЖ, первый формирователь 31 импульсов, первый триггер 32, третий элемент 33 И. Формирователь 10 готовности содержит замыкающую кнопку Пуск 34, пятый триггер 35, элемент 36 И-НЕ, седьмой элемент 37 И, третий триггер 38, трети: формирователь 39 импульсов, пятый 40 и шестой 41 элементы И, четвертый элемент 42 РШИ, второй 43 и четвертый 44 триггеры, индикатор 45 брака и индикатор 46 готовности, первый 4 и второй 48 диоды, инвертор 49, выходы и входы блока 4 источников сигналов воздействий и измерительного блока 2 подключены к соответствующим i -парам горизонтальных шин измерительного матрично го коммутатора 3, каждая из к-пар вертикальных шин которого соединена через соответствующие элементы коммутации каждого из рабочих постов с клеммами для подключения выводов контролируемых электронных схем , управляюпше входы измерительного матричного коммутатора 3 подключены к выходам соответствую1цих регистров 8 , ут1равляю 151е входы блока 4 источников сигналов воздействий и измерительного блока 2 соединены с соответствующими первой и второй группа ми первых выходов блока 12 управления , первый и второй входы которого соединены соответственно с выходами Годен и Врак, измерительного блока 2 и с первым и вторым входами формирователей rrt готовности третья группа первых выходов блока 12 управления соединена с соответст вующими входами регистров , второй выход, - с третьим входом пер вого формирователя готовности, третий выход - с четвертыми входами формирователей 1т готовности четвертый выход - с пятыми входами формирователей готовности третий вход - с третьими выходами формирователей 10 1-10 т готовности четвертьй вход - с четвертьтми вы. ходами формирователей готовности, второй выход каждого из формироватепей готовности соединен с третьим входом формирователя готовности. Входы каж дого из К первых элементов ИЛИ соединены с вьгходами соответствующих регистров , их выходы - с первыми входами первых элеме тов И данного рабочего поста, выходы которых соединены с входами соответствующих элементов коммутации, а вторые входы - с первым выходом формирователя готов ности данного поста. В блоке 12 управления выход гене ратора 13 тактовых импульсов соединен с четвертым выходом блока и с первыми входами второго 14 и третье го 33 элементов И, второй рход вто 1 410 рого элемента 14 И соединен с выходом первого триггера 32, первый вход которого соединен с выходом второго элемента 30 ИЛИ, первый вход которого соединен через первый формирователь импульсов с третьим входом блока 12, второй выход и четвертый вход которого соединены соответственно с выходом и вторым входом третьего элемента 33 К, первый и второй входы - с одноименныг-ш входами третьего элемента 27 Р4ЛИ, соединенного выходом через первый элемент 28 задержки с первым входом четвертого элемента 29 И, непосредственно - с первым входом вычитающего счетчика 24, выход которого соединен через дешифратор нуля 25 с вторым входом четвертого элемента 29 И, соединенного выходом с вторым входом второго элемента 30 ИЛИ, вход второго формирователя 26 импульсов соединен с выходом дешифратора нуля 25, а выход - с третьим выходом блока 12 и с первым входом счетчика 16 адреса, соединенного вторым входом через второй элемент 15 задержки с выходом второго элемента 14 И и с первым входом блока 18 памяти, соединенного вторым входом с выходом фотосчитывающего блока 22, третьим входом - с выходом счетчика 16 адреса, соединенного третьим входом с выходом клавишного переключателя 21, первый выход блока 18 памяти соединен с первым входом дешифратора 19 адреса, соединенного первым выходом с вторым входом первого триггера 32, вторые выходы блока 18 памяти соединены с соответствующими первыми входами первого 23, второго , третьего и четвертого блоков элементов И, первый выход первого блока 23 элементов И соединен с вторым входом вычитающего счетчика 24, второй выход - с первым входом дешифратора 19 адреса, второй и третий входы которого соединены с первыми выходами соответственно второго и третьего блоков элементов И, вторым выходом - с вторым входом четвертого блока элементов И, первые выходы четвертого блоков элементов И соединены с первой группой первых выходов блока 12, вторые выходы третьего и второго блоков элементов И соединены соответственно с второй и третьей группами выходов блока 12. В формирователе 10 готовности выход индикатора 45 брака соединен с первым выходом второго триггера 43 и с первым входом четвертого элемента 42 ИЛИ, соединенного вторым входом с первым входом второго триггера 43, с первым входом третьего триггера 38 и через третий формирователь 39 импульсов - с третьим входом формирователя Ю, вход индикатора 46 годности соединен с выходом четвертого триггера 44, соединенного первым входом с выходом пятого элемента 40 И, вторым входом с выходом четвертого элемента 42 ИЛИ, второй вход второго триггера 43 соединен с выходом шестого элемента 41 И, соединенного первым входом с вторым входом формирователя 10, вторым входом - с первым выходом третьего триггера 38, с вторым выходом формирователя 10, с первым входом пятого элемента 40 И и с первым входом элемента 36 И-НЕ, второй выход третьего триггера 38 через первый диод 47. соединен с четвертым выходом формиро вателя 10, первый вход которого соединен с вторым входом пятого элемента 40 И, третий вход которого соединен с вторым выходом второго триггера 43. Второй вход третьего триггера 38 соединен с выходом седьмого элемента 37 И, первый вход кото рого соединен с пятым входом формирователя 10, второй вход - с первым выходом пятого триггера 35, соедине ноге первым входом с четвертым входом формирователя 10, вторым входом через замыкающую кнопку 34 - с шино питания устройства, вторым выходом с вторым входом ЭJfeмeнтa 36 И-НЕ, соединенного выходом через второй диод 48 с третьим выходом формирова теля 10, через инвертор 49 - с первым выходом формирователя 10. Устройство работает следующим образом. Работа устройства рассматриваетс на примере трех постов . Генератор 13 вырабатывает тактовые импуль сы (ТИ) . Формирователь готовности рабочего поста содержит формиро ватель 39 импульсов, который вырабатывает кратковременный импульс по отрицательному перепаду (по заднему фронту импульса генератора 13) Формирователи импульсов , формирователей готовности и 1 4 вырабатывают запрещающие им11 льсы по отридательному перепаду длительностью большей, чем длительность ТИ, но меньшей периода их повторения. Триггеры , , формирователей готовности , , соединяются меязду собой при подключении рабочих постов друг к другу так, что образуется кольцевой сдвиговый регистр, число разрядов которого равно числу постов. Работа сдвигового регистра синхронизируется ТИ, поступающими из блока 12 управления. На фиг. 4 показаны: 50 - тактовые импульсы с генератора 13; 51- импульсы с выхода формирователя52- импульсы с выхода триггера53- сигнал Контроль готовности ;54- сигнал с выхода формирователя55- сигнал с выхода триггера , 56- сигнал с выхода формирователя третьего поста; 57- сигнал с выхода триггера , сигнал с кнопки , сигнал с выхода триггера - сигнал с выхода инвертора 61- сигнал с выхода диода 62- сигнал Конед цикла с выхода формирователя 26. После включения питания устройства формирователь 26 вьфабатывает сигнал Конец цикла (62 фиг.4), а генератор 13 начинает вырабатывать ТИ (50 фиг.4). Рассмотрим работу сдвигового регистра на примере, когда подключены три рабочих поста (фиг.З) и ни одна кнопка , , не нажата. Сигнал Конец цикла устанавливает :триггеры , , в О, подготавливая элемент и элементы , И,на других входах имеются разрешающие уровни с выходов формирователей , импульсов соответственно. Первый ТИ через подготовленнъге элементы , , И поступает на входы установки в О триггеров , , и по переднему фронту устанавливает их в О. Диоды , , запираются и в цепи Контроль готов ности устанавливается высокий уровень, отпирающий элемент 33 И, Первый ТИ через элемент 33 И поступает на вход формирователя импульсов, на котором по заднему фронту формируется импульс (51 фиг,4), устанавливающий триггер в 1. На нулевом выходе триггера уст навливается низкий уровень, который открьшает диод и в цепи Контроль готовности также устанавливается низкий уровень (53 фиг.4). Вто рой ТИ по переднему фронту через подготовленный элемент И устанавливает триггер в О и в мо мент переключения по отрицательному перепаду с выхода 1 триггера формирователь генерирует запре щающий импульс (54 фиг.4) длительностью большей длительности ТИ. Импульс с выхода формирователя устанавливает по переднему фронту триггер в Г (55 фиг.4) и одновременно запирает элемент 37-2, запрещая, тем самым ,прохождение второго ТИ на вход установки в О триггера . При установке в 1 триггера на его нулевом выходе устанавливается низкий уровень, который открывает диод и в цепи Контроль готовности также устанавливается низкий уровень (53 фиг. запрей(йющий прохождение этого второго ТИ через элемент 33 И на вход формирователя , и триггер останется в нулевом состоянии. Следующий третий ТИ по переднему фронту через подготовленный элемент И устанавливает триггер в О и в момент пер;еключения по отрицательному перепаду с выхода 1 триггера формирователь генерирует запрещающий импульс (56 фиг.4) длительностью больше дли тельности ТИ. Импульс с выхода формирователя по переднему фронту устанавливает триггер в 1 (57 фиг.4) и одновременно запирает элемент И, запрещая, тем самым прохождение третьего ТИ на вход уст новки в О триггера . При уста новке в 1 триггера на его нулевом выходе устанавливается низкий уровень, который открывает диод и в цепи Контроль готовности также устанавливается низкий уровень (53 фиг,4), запрещающий прохож дение третьего ТИ через элемент 33 на вход формирователя . Следующий четвертый ТИ по переднему фронту через подготовленный элемент И устанавливает триггер 38-3 в О, диод высоким уровнем с выхода О запирается, в цепи Контроль готовности устанавливается высокий уровень, элемент 33 И отпирается по одному входу. Четвертый ТИ через элемент 33 И поступает на вход формирователя импульсов, на котором по заднему фронту формируется импульс, устанавливающий триггер в 1. Далее процесс переключения триггеров , , будет повторяться до тех пор, пока не будет нажата кнопка Пуск , , на каком-либо рабочем посту . Таким образом, если ни одна из кнопок , , Пуск не нажата, то по первому ТИ устанавливается в 1 триггер , по второму триггер устанавливается в О, а триггер устанавливается в 1, по третьему ТИ триггер устанавливается в О, а триггер - в 1, по четвертому ТИ триггер , устанавливается в О, а триггер - в 1, т.е. происходит сдвиг 1 по кольцевому регистру сдвига, образованному триггерами , , и замкнутому по шине Контроль готовности и элементу 33 И. При нажатии кнопки Пуск 34, например, на третьем посту () работа кольцевого сдвигового регистра сводится к следующему. Пусть кнопка Пуск нажата в момент времени, когда триггер был установлей в 1 (5В фиг.4). Сигнал с кнопки Пуск устанавливает в 1 триггер (39 фиг.4) который запирает элемент И по одному входу, запрещая, тем самым, прохождение тактовых импульсов в цепь установки в О триггера , Сдвиговый регистр продолжает свою работу, как быпо указано,до тех пор, пока не произойдет установка в 1 триггера , и последний будет находиться в состоянии 1 до тех пор пока триггер не будет установлен в О. Единичное состояние триггеров и обеспечивает вьщачу сигнала готовности через элемент И-НЕ и диод в цепь Пуск, а с выхода инвертора (60 фиг.4) подготавливает отпирание элементов9 1-9 К И поста . Высокий уровень с выхода 1 триггера подготавливает отпирание элементов , И. Сигнал готовности поступает на формирователь 31 блока 12 управления, где по переднему фронту формируется импульс, устанав ливающий через элемент 30 ИЛИ триггер 32 в 1, тем самым разрешая прохождение тактового импульса с генератора 13 через элемент 14 И, который обеспечивает запуск внутренней синхронизации блока 18 памяти. Блок 18 памяти последовательно выдает слова, состоящие из адресной и информационной частей, и записанных в него с фотосчитывающего блока 22, причем начальный адрес ячеек блока 18 памяти определяется кодом, занесенным в счетчик 16 адреса с клавишного регистра 21. Адресная часть слова поступает на дешифратор 19 адреса и определяет блоки элемен тов И , , , через которые будет передаваться информационная часть слова на блоки 1,2,8. Таким образом, в блок 4 источников сигналов воздействий будут записаны коды величины и полярности напряжений или токов, в измерительный блок 2 - коды рода работы (измерение тока или напряжения) и коды величины граничных значгииГ(, в регист ры 8 - коды, определяющие: подключе ние выводов контролируемых схем блоку 4 источников сигналов воздействий или к измерительно му блоку 2, а в вычитающий счетчик 24 заносится инфопмация о количест тестов в цикле испытаний. Тактовый импульс, задержанный на элементе 1 задержки на время, необходимое для выдачи исходных данных из блока 18 памяти, обеспечивает изменение адр са в счетчике 16 адреса. По оконча нии выдачи исходных данных из блока 18 памяти триггер 32 устанавливается в О с вькода дешифратора 19 адреса, запрещая прохождение следующего тактового импульса, через элемент 14 И. По информации, памяти, блок 4 выданной из б. 18 воздействий источников сигна.юп и измерительный блок 2 задают треб емые Д1тя контроля параметра режимы а по информации, г шгегсмшой в регис1ры 8 1-8 К, 1чЧ1ммутпционн1)1е элементы .(Ч II матричного 416 коммутатора 3 подключают горизонтальные шины к соответствующим вертикальным шинам. Информация из регистров через элементы lira. и элементы И, подготовленные сигналом Пуск, вызывает срабатьтание элементов коммутации . рабочих постов р}, обеспечивая подключение к выводам контролируемой схемы 1 только тех вертикальных шин, которые хотя бы одним коммутационным элементом измерительного матричного коммутатора 3 подключены к горизонтальным шинам. Если в регистр не занесена информация, то это означает, что ни один элемент коммутации соответствующего столбца измерительного матричного коммутатора 3 не включится, на выходе элемента ИЛИ низкий уровень и соответствующир элемент коммутации поста ке включится. Таким образом, в казвдом тесте к вертикальным оказываются подключенными только те выводы, которые задействованы по схеме измерения . По окончании измерений измерительный блок 2 по результатам сравнения измеренной величины с граничными значениями формирует сигнал Брак или Годен, KOTopbtfj по шине 7 передается в блок 12.-Этот сигнал через элемент 27 ИЛИ уменьшает содержимое счетчика 24 на единицу, а через элемент 28 задержки и элемент 29 И, подготовленный высоким уровнем с дешифратора нуля 25 и элемент 30 ИЛИ, устанавливает триггер 32 в 1, подготавливая элемент 14 И и разрешая прохождение тактового импульса с генератора 13 в блок 18 памяти, обеспечивая, тем самым, передачу исходных данных .для формирования следующего теста. Одновременно сигналы Годен или Брак через подготовленные элементы И или И соответственно устанавливают триггеры или в 1. При установке в 1 триггера триггер через элемент 42 ИЛИ по перепадам с выхода 1 триггера сбрасывается в О и установка в 1 его в дальнейшем запрещается, так как элемент И оказывается закрытым низким уровнем с выхода О триггера , следовательно, индикатор Брак остается включенным до конца цикла.

Таким образом, испытания продолжаются до последнего теста. При поступлений последнего сигнала Годен или Брак счетчик 24 обнуляется, на выходе дешифратора нуля 25 устанавливается низкий уровень, а формирователь 26 по перепаду с выхода депшфратора нуля 25 формирует сигнал Конец цикла, по которому счетчик 16 адреса устанавливается в О, а все элементы устройства устанавливаются в исходное состояние. Одновременно низкий уровень с выхода дешифратора нуля 25 запрещает прохождение сигналов Годен или Брак, задержанных на элементе 28 задержки, через элемент 29 И и триггер 32 остается в нулевом состоянии. Цикл испытаний закончен.

Таким образом, введение элементов И, ИЛИ обеспечивает в каждом тесте подключение к линиям связи с вертикальными шинаи ш измерительного матричного крммутатора 3 только тех выводов контролируемых схем , которые задействованы по схеме измерения. Поэтому

распределенные емкости невыбранных линий связи с вертикальных шин коммутатора не заряжаются и в последующих тестах подключение выводов контролируемых схем 1 линиям связи, а также вертикальных шин измерительного матричного коммутатора 3 к горизонтальным происходит сухими контактами коммутационных элементов соответственно, что повышает надежность устройства. Это, в свою очередь, исключает возможность возникновения переходных процессов (как показывает практика, зачастую превышакнцйх предельно допустимые режимы) на выводах контролируемых схем . Так как в предлагаемом многопостовом устройстве контроля обеспечено отключение (подключение) любого вывода контролируемой схемы 1 от (К) соответствующей линии связи непосредственно на рабочем посту, то имеется возможность конт:роля схем, например счетчиков, реjгистров сдвига и т.п., с нормированными по времени входными сиг-налами, что расширяет область применения устройства.

№

E

-J

J

16

cpus.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СИСТЕМА ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ" ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 0 |

|

SU302717A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЭЛЕКТРИЧЕСКАЯ ЛАМПА НАКАЛИВАНИЯ С РЕФЛЕКТОРОМ ВНУТРИ КОЛБЫ | 1926 |

|

SU4502A1 |

| Электронная промышленность, 1970, М 10, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

Авторы

Даты

1984-08-15—Публикация

1983-05-27—Подача