четвертого ключей, отличающееся тем, что в него введены последовательно соединенные блок па мяти и пятый ключ, вход блока памяти соединен с выходом выпрямителя, выход пятого ключа подключен к интегратору, управляющие входы блока памяти и пятого ключа соединены с управляющими входами первого ключа блока преобразования временного ичтервала Е код соответственно, а выход источника напряжения питания по ключен к третьему входу определителя, октантов. 3. Устройство по п. о т л И-. чающееся тем, что блок преобразования временного интервала в код выполнен в виде трех триггеров, генератора импульсов, четырех элеме тов И, двух элементов ИЛИ, реверсив ного счетчика, дешифратора нуля и блока выдачи кода, причем входы перв триггера соединены соответственно с выходом первого элемента ИЛИ и с пе вым входом блока преобразования, а прямой выход - с первым входом первого элемента И, входы второго триг гера соединены соответственно с вы66ходами второго элемента И и дешифратора нуля, а прямой выход - с первым входом третьего элемента И, выход генератора импульсов подключен к вторым входам первого и третьего элементов И, выходы которых соединены с входами реверсивного счетчика, выход которого подключен к входу дешифратора нуля, выход которого подключен к первым входам первого и второго элементов ИЛИ и треть.его триггера, второй вход которого соединен с вторыми входами первого элемента ИЛИ и блока преобразования, а прямой выход - с первым входом четвертого элемента И, второй вход которого соединен с вторым входом первого триггера и с первым входом второго элемента И, а выход - с управляющим входом блока вьщачи кода, вход которого подключен к выходу реверсивного счетчика, а выход - к первому выходу блока преобразования, второй вход второго элемента И соединен с инверсным выходом третьего триггера, а первый вход с вторым входом второго элемента ИЛИ, выход которого соединен с вторым выходом блока преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1986 |

|

SU1403373A1 |

| Способ преобразования угла поворота вала в код | 1976 |

|

SU732951A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1145479A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1989 |

|

SU1713103A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU972541A1 |

| Способ магнитной записи технологических параметров бурения и устройство для его осуществления | 1984 |

|

SU1203237A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1332534A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

1. Способ преобразования угла поворота вала в код, основанный на преобразовании уг.ла поворота вала в напряжения, пропорциональные синусу и косинусу угла поворота вала, сравнении этих напряжений, последовательном выпрямлении большего и меньшего напряжений, интегрировании опорного напряжения, обратного по знаку выпряцленному большему напряжению, в течение эталонного интервала времени, интегрировании выпрямленного большего напряжения до заданной величины и определении временного интервала его интегрирования, интегрировании выпрямленного меньшего напряжения за интервал времени интегрирования выпрямленного большего напряжения, интегрировании опорного напряжения, обратного по знаку выпрямленному меньшему напряжению, до заданной величины и определении временного интервала его интегрирования с последующим определением кода угла поворота вала по величине этого временного интервала, отличающийся тем, что, с целью повьш ения быстродействия, выпрямленное большее напряжение запоминают, выпрямляют меньшее напряжение непосредственно после выпрямления большего напряжения и его запоминания, .а выпрямленное меньшее напряжение интегрируют непосредственно после интегрирования выпрямленного и запомненного большего на-г пряжения. 2. Устройство для осуществления способа по п. 1, содержащее синуснокосинусный датчик, вход которого подключен к источнику напряжения питания , а выходы - к входам блока срав(Л нения и к первым двум входам опредес лителя октантов непосредственно и к входу выпрямителя через первый и второй ключи, опорный источник, вход которого подключен к источнику нат1ряжения питания, интегратор, вход которого через третий и четвертый ключи подключен соответственно к выходам опорного источника и выпрямителя, 00 О5 а выход через компаратор - к первому входу блока преобразования временного а интервала в код, первый.выход которого подключен к одному входу вычислительного блока, другой вход кото{)ого соединен с выходом определителя октантов, а выход является выходом устройства, и блок управления, входы которого соединены с выходом блока сравнения и вторым выходом блока преобразования временного интервала в код, а выходы подключены к второму входу блока преобразования временного интервала в код и к управляющим входам первого, второго, третьего и

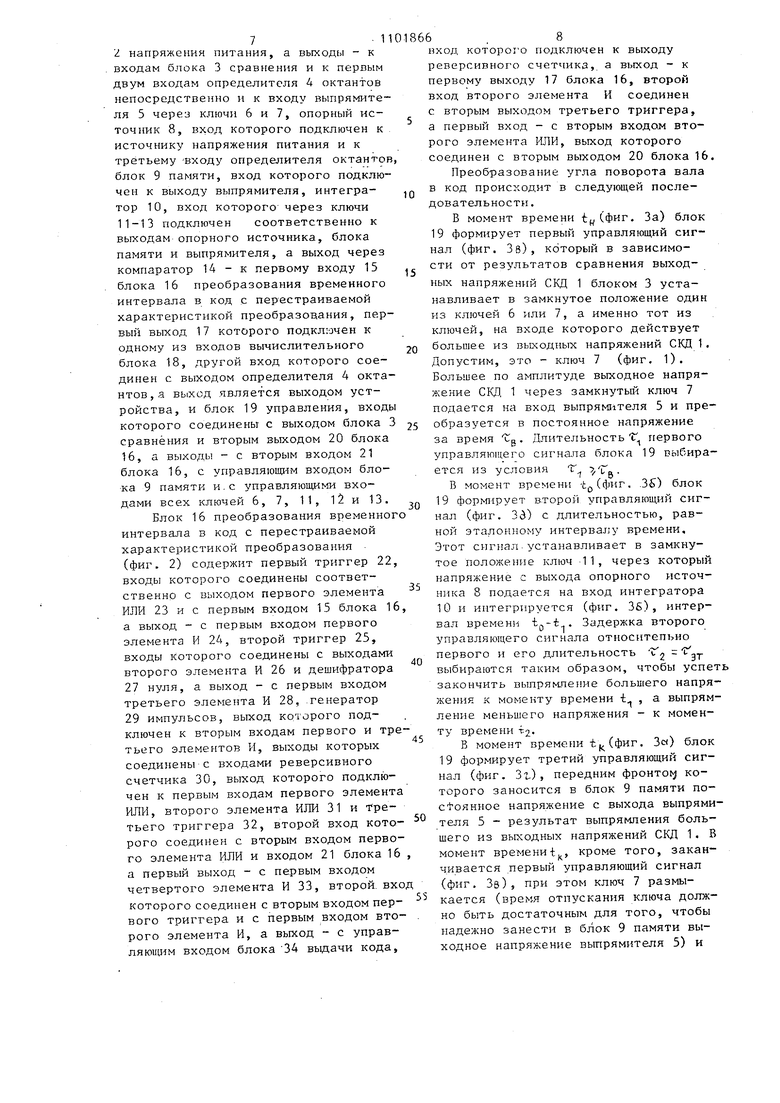

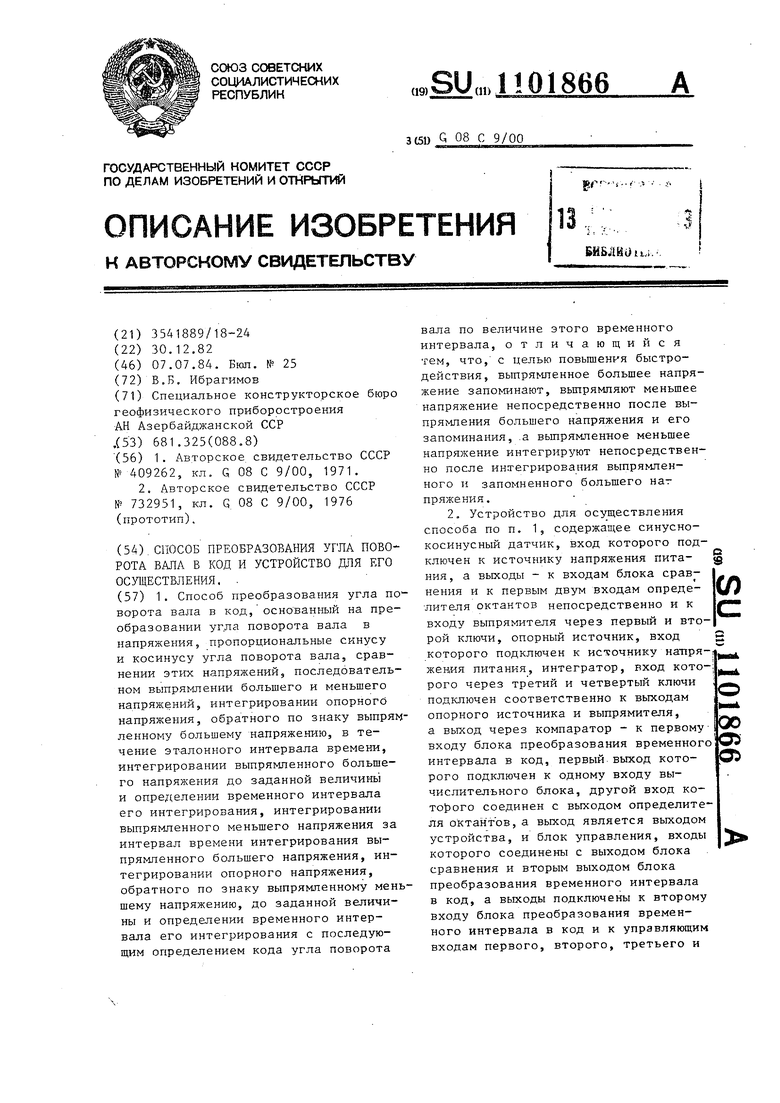

-. Изобретение относится к автомати ке и вычислительной технике и может быть использовано для построения ан лого-цифровых преобразователей угло вых перемещений и устройств сопрял :е ння аналоговых источников информации с микропроцессорами и ЭВМ. Известен способ преобразования угла поворота вала в код, в соответствии с которым формируют напряжения, пропорциональные синусу и косин су угла поворота вала, выпрямляют и сравнивают эти напряжения, а по результатам сравнения определяют меньшее и большее из них, интегрируют выпрямленное меньшее напряжение в те чение эталонного временного интервала, интегрируют выпрямленное большее напряжение с противоположным знаком до заданной величины, а временной интервал интегрирования выпрямленного большего напряжения преобразуют в код С 13Известно устройство для осуществления этого способа, содернсащее синусно-косинусный датчик, вход которого подключен к источнику напряжения питания, а выход - к первым двум входам определителя октантов, третий вход которого соединен с источником напряжения питания, первый и второй выпрямители и блок сравненияj выход которого подключен к входу блока управлени51, выходы которого соединены с управляющими входами двух ключей, выходы которых объединены и через последоватапьно соединенные интегратор и компаратор подключены к первому входу блока преобразования временного интервала в код. второй вход которого соединен с третьим выходом блока управления, а выход - с одним на входов вычислительного блока, другой вход которого подключен к выходу определителя октантов, а выход является выходом устройства, входы пер3 1 вого н второговыпрям 1телей соединены с выходами синусио-косннусного датчи ка, а выходы - с входами блока сравнения и с информационными входами соответствующих ключей 1 . Недостатком даннь х снособа и устройства является погрешность преобра зования выходных напряжений синуснокосинусного датчика в постоянные напряжения посредством двух выпрямителей с неидентичными характеристиками Наиболее близким к предложенному по технической сущности является спо соб преобразования угла поворота вал в код, основанный на преобразовании угла поворота вала в напряжения, про порциональное синусу и косинусу угла поворота вала, сравнении этих напряжений, последовательном выпрямлении большего и меньшего напряжений, интегрировании опорного напряжения, об ратного ,по знаку выпрямленному большему напряжению, в течение эталонного интервала времени, интегрировании от выпрямленного большего напряжения до заданной величины и определении временного интервала его интег рирования, интегрировании выпрямленного меньшего напряжения за интервал времени интегрирования выпрямленного большего напряжения, интегрировании опорного напрягкения, обратного до знаку выпрямленному меньшему напряжению, до заданной величины и определении временного интервала его интег рирования с последующим определением кода угла поворота вала.по величине этого временного интервала, при этом выпрямление меньшего напряжения осуществляют не сразу после выпрямления большего напряжения, а с некоторой задержкой, необходимой для выполнения операции интегрирования выпрямленного большего напряжения до задан ной величины, определения и запоминания (в виде кода) интервала времени его интегрирования; интегрирование выпрямленного меньшего напряжения осуществляют не сразу после интегрирования выпрямленного большего напряжения, а с некоторой задержкой, необходимой для выпрямления меньшего напряжения и восстанов ления запомненного ранее (в виде кода) интервала времени интегрирования выпрямленного большего напряжения, в течение которого должно интегрирова.ться выпрямленное меньшее напряжение С21. 66 . 4 Устройство для осуществления известного способа содержит синуснокосинусный датчик, вход которого подключен к источнику напряжения питания, а выходы - к входам блока сравнения и к первым двум входам определителя октантов непосредственно и к входу выпрямителя через первый и второй ключи, опорный источник, вход которого подключен к источнику напряжения питания и к третьему входу определи-, теля октантов , интегратор, вход которого через третий, и четвертый ключи подключен соответственно к выходам опорного источника и выпрямителя, а выход через компаратор - к первому входу блока преобразования временного интервала в код, первый выход которого подключен к одному входу вычислительного блока, другой вход которого соединен с выходом определителя октантов, а выход является выходом устройства, и блок управления, входы которого соединены с выходом блока сравнения и вторым выходом блока преобразования временного интервала в код с перестраиваемой характеристикой преобразования, а выходы подключены к второму входу блока преобразования временного интервала в код и к управляющим входам первого, второго, третьего и четвертого ключей L2 . Недостатком известных способа и устройства является низкое быстродействие. Целью изобретения является повышение быстродействия способа преобразования угла поворота вала в код и устройства для его осуществления. Поставленная цель достигается тем, что согласно способу преобразования угла поворота вала в код, основанному на преобразовании угла поворота в напряжения, пропорциональные синусу и косинусу угла поворота вала, сравнении этих напряжений, последовательном выпрямлении большего и меньшего напряжений, интегрировании опорного напряжения, обратного по знаку выпрямленному большему напряжению, в течение эталонного интервала времени, интегрировании выпрямленного большего надряжения до заданной величины и определении временного интервала его интегрирования, интегрировании выпрямленного меньшего напряжения за интервал времени интегрирования выпрямленного большего напряжения, интегрировании опорного напряжения., обратного по знаку выпрямленному меньшему напряжению, до заданной величиньг и опр делении временного интервала его интегрирования с последующим определением кода угла поворота вала по вели чине этого временного интервалаj выпрямленное большее напряжение запо минают, выпрямляют меньшее напряжение непосредственно после выпрямления большего напряжения и его запоминания, а выпрякшенное меньшее напр жение интегрируют непосредственно после интегрирования выпрямленного и запоминающего большего напряжения В устройство для осуществлен 1я способа, содержащее синусно-косинусный датчик, вход которого подключен к источнику напряжения питания, а вы ходы - к входам блока сравнения и к первым двум входам определителя октантов непосредственно и к входу выпрямителя через первый и второй клю чи, опорный источник,, вход которого подключен к источнику напряжения питания, интегратор, вхо/ которого чере третий и четвертый ICJIIOMH подключе соответственно к выходам опорного источника и вьiПpя яl eJIЯ,, а выход через компаратор - к первому входу блока преобразования временного интервала в код, первый выход которого подключен к одному входу вычнс.иитель ного блока, другой вход которого со ден с выходом oпpeдeJlнтeля октантов а выход я.вляется выходом устройст1г1а и блок управления5 входы которого соединены с выходом блока сравиемня и вторым выходом блока преобразования временного интервала в код. а выходы подключены к вто1)ому входу блока преобразования временного нитервала в код и к управляющим входам первого, второгоJ третьего и чет вертого ключей, вве/дены последовател но соединенные блок памяти и пятьй ключ, вход блока памяти соединен с вы ходом выпрямителя, вьжод пятого ключа подключен к интегратору, управляющие входы блока памяти и пятого ключа соеди нены с управляющими входами первого ключа и блока преобразования временного интервала в код соответственно, а выход источника напряжения питания подключен к третьему входу определителя октантов.. Кроме того, блок преобразования временного интервала в код выполнен в виде трех триггеров, генератора импульсов, четырех элементов И, двух элементов ИЛИ, .реверсивного счетчика, дешифратора нуля.и блока вьщачи кода, причем входы первого триггера соединены соответственно с выходом первого элемента ИЛИ и с первым входом блока преобразования, а прямой выход - с первым входом первого злемента И, входы второго триггера соединены соответственно с выходами второго элемента И и де.шифратора нуля, а прямой выход - с первым Входом третьего элемента И, выход генератора импульсов подключен к вторым входам первого и третьего элемента И, которых соединены с входами реверсивного счетчика., выход которого подключен к входу дешифратора нуля, выход которого подключен к первым входам первого и второго э;1емента ИЛИ и третьего триггера, второй вход которого соединен с вторыми зходамй первого элемента НИИ и блока преобразования, а прямой выход - с первым входом четвертого элемента И, второй вход которого соединея с вторым входом первого триггера и с первым входом второго элемента И, а выход - с управляющим входом блока ввудачи кода, вход которого подключен к выходу реверсивного счетчика, а выход - к первому выходу блока преобразования , второй вход второго элементаИ соединен с инверС1 Ь м выходом третьего триггера, а первый вход - с В7орым вход.ом второго злемента ИЛИ, выход которого соединен с вторым выходом блока преобразования , Способ заключается в том, что выпря шение меньшего напряжения осушест i:; л я ют непосредственно после получения результата вьтряьшения большего напряжения, который предварительно запоминают,, а интегрирование выпрямленного меньшего напряжения осуществляют епосредственно после интегрирования выпрямленного и запомненного большего напряжения. На фиг, 1 показана структурная схема предлагаемого устройства, реализующего способ; на фиг. 2 - схема блока преобразования временного интервала в код, входяш,его в состав устройства; на фиг. 3 - временные диаrpaMNtbi работы устройства. Устройство (фиг. 1) содержит си}1усно-косинусный датчик (СКД) 1, вход которого подключен к источнику 2 напряжения питания, а выходы - к входам блока 3 сравнения и к первым двум входам определителя k октантов непосредственно и к входу выпрямителя 5 через ключи 6 и 7, опорный источник 8, вход которого подключен к источнику напряжения питания и к третьему -входу определителя октанто блок 9 памяти, вход которого подключен к выходу выпрямителя, интегратор 10, вход которого через ключи 11-13 подключен соответственно к выходам опорного источника, блока памяти и выпрямителя, а выход через компаратор 14 - к первому входу 15 блока 16 преобразования временного интервала в код с перестраиваемой характеристикой преобразования, первый выход 17 которого подключен к одному из входов вычислительного блока 18, другой вход которого соединен с выходом определителя 4 окта нтов, а вь1ход является выходом устройства, и блок 19 управления, входы которого соединены с выходом блока сравнения и вторым выходом 20 блока 16, а выходы - с вторым входом 21 блока 16, с управляющим входом блока 9 памяти и.с управляющими входами всех ключей 6, 7, 11, 12и 13. Блок 16 преобразования временно интервала в код с перестраиваемой характеристикой преобразования (фиг. 2) содержит первый триггер 22 входы которого соединены соответственно с выходом первого элемента ИЛИ 23 и с первым входом 15 блока 1 а выход - с первым входом первого элемента И 24, второй триггер 25, входы которого соединены с выходами второго элемента И 26 и дешифратора 27 нуля, а выход - с первым входом третьего элемента И 28, .генератор 29 импульсов, выход которого подключен к вторым входам первого и тр тьего элeмe тoв И, выходы которых соединены с входами реверсивного счетчика 30, выход которого подключен к первым входам первого элемент ИЛИ, второго элемента ИЛИ 31 и Третьего триггера 32, второй вход кото рого соединен с вторым входом перво го элемента ИЛИ и входом 21 блока 1 а первый выход - с первым входом четвертого элемента И 33, второй, вх которого соединен с вторым входом пер вого триггера и с первым входом вто рого элемента И, а выход - с управляющим входом блока 34 выдачи кода. вход которого подключен к выходу реверсивного счетчика, а выход - к первому выходу 17 блока 16, второй вход второго элемента И соединен с вторым выходом третьего триггера, а первый вход - с вторым входам второго элемента ИЛИ, выход которого соединен с вторым выходом 20 блока 16. Преобразование угла поворота вала в код происходит в следующей последовательности . В момент времени ((Фиг. За) блок 19 формирует первый управляющий сигнал (фиг. Зв), который в зависимости от результатов сравнения выходных напряжений СКД 1 блоком 3 устанавливает в замкнутое положение один из ключей 6 или 7, а именно тот из ключей, на входе которого действует большее из выходных напряжений СКД 1. Допустим, это - ключ 7 (фиг. 1). Большее по амплитуде выходное напряжение CKJ, 1 через замкнутьш ключ 7 подается на вход выпрям11теля 5 и преобразуется в постоянное напряжение за время cg. Длительность f первого управляющего сигнапа блока 19 выбирается из условия Т момент времени Сфиг. .35) блок 19 фор шрует второй управляющий сигнал (фиг. 3d) с длительностью, равной эталонному интервалу времени. Этот сигьшл устанавливает в замкнутое положение ключ 11, через который напряжение с выхода опорного источника 8 подается на вход интегратора 10 и интегрируется (фиг. 3S), интервал времени t..,-t . Задержка второго управляющего сигнала относите.пьно первого и его длительность fj -эт выбираются таким образом, чтобы успеть закончить выпрямление большего напряжения к моменту времени -t , а выпрямление меньшего напряжения - к моменту времени г2. В момент времени t(фиг. Зи) блок 19 формирует третий управляющий сигнал (фиг. Зг) , передним фронтог которого заносится в блок 9 памяти поctoHHHoe напряжение с выхода выпрямителя 5 - результат выпрямпения большего из выходных напряжений СКД 1. В момент времени-t, кроме того, заканчивается первый управляющий сигнал (фиг. Зв)5 при этом ключ 7 размыкается (время отпускания ключа должно быть достаточным для того, чтобы надежно занести в блок 9 памяти выходное напряжение выпрямителя 5) и 91 большее напряжение отключается от вы прямителя, одновременно третьим упра ляющим сигналом блока 19 замыкается ключ 6 и к входу выпрямителя подключается меньшее из выходньгх напряжеНИИ СКД 1, которое преобразуется в постоянное напряжение. В момент времени t заканчивается второй управляющий сигнал (фиг, 33), в результате чего ключ 11 размыкается и напряжение с выхода опорного источника 8 отключается от интеграто ра 10; формируется блоком 19 четвертый управляющий сигнал (фиг. Зе), который устанавливает в замкнутое положение ключ 12, подключая к входу указанного интегратора выпрямленное и запомненное блоком 9 большее выходное напряжение СКД 1 Ug(3c(n Начинается такт интегрирования этого напряжения (фиг. ЗБ, интервал времени tj)- Четвертый управляющий сигнал, кроме того, подается на вход 21 блока 16, включая его в режим преобразования Временной интер вал - код. Передним фронтом этого си1нала устанавливается в положение О триггер 32 (фиг. 2), при этом триггер потенциал высокого уровня, соответствующего уровню логической 1 (в дальнейшем - разрешающий потенциал), с выхода и триггера (фиг. 3с) подготавливает; элемент И 26;устанавливается в положение 1 (через элемен ИЛИ 23) триггер 22, с выхода и которого разрешающий потенциал (фиг, подается на управляющий, вход элемента И 24 и открывает его, при этом счетные импульсы с выхода генератора 29 через элемент И 24 поступают на вход Сложение реверсивного счетчи-ка 30 и подсчитываются им (фиг. Зк). В момент времени 2 когда выход ное напряжение интегратора 10 достигает заданной величины (фиг, 35 , нулевое значение), срабатывает компаратор 14, импульс с выхода которого (фиг. 3л) поступает на вход, 15.блока 16 с перестраиваемой характеристикой преобразования и сразу же переводит го в режим преобразования кода во временной интервал. Для этого указан ный импульс перебрасывает триггер 22 в исходное положение О, при этом разрешающий потенциал с управлягадего входа элемента И 24 снимается (фиг. Зи) и поступление счетных импульсов генератора 29 на вхпп ело66женин реверсивного счетчика 30 прекращается (фиг. Зк) проходит через открытый элемент И 26 (фиг. Злл) и устанавливает в положение 1 триггер 25, разрешающий потенциал с выхода И которого (фиг. Зн) подается на управляющий вход элемента И 28 и открывает его, при этом счетные импульсы генератора 29 через элемент И 28 начинают поступать на вход вычитания реверсивного счетчика 30 (фиг. 3 о), содарж мое.которого уменьшается с каждым поступившим счетным импульсот-;; проходит через элемент ИЛИ 31 и с выхода 20 блока 16 поступает на блок 19, который формирует задний фронт четвертого управляющего сигнала (фиг, Зе);, разрешающий потенциал с управляющего входа ключа 12 снимается и он размыкается, отключая напряжение от интегратора и одновременно передний фронт пятого управляющего сигнала (фиг. Зж), устанавливающего в замкнутое положение ключ 13, через который выпрямленное к этому моменту времени меньшее выходное напряжение СКД 1 с выхода выпрямителя 5 подключается к входу интегратора и интегрируется им (фиг. 35, интервал времени t2t3)В момент времени t3(T.e. через интервал времени лъз с момента времени t , равный At2 /l-fcj i2-fc) содержимое реверсивного счетчика достигает нуля и срабатывает дешифратор 27, импульс с выхода которого (фиг. Зп) возвращает триггер 25 в исходное положение О, при этом разрешающий потенциал с управляющего входа элемента И 28 снимается (фиг. Зн) и поступление счетных импульсов генератора 29 на вход вычитания реверсивного счетчика 30 прекращается (фиг. Зо); устанавливает в положение 1 триггер 32, при этом разрешающий потенциал с выхода Q этого триггера (фиг. 3р) подготавливает элемент И 33; проходит через элемент ИЛИ 23 и вновь устанавливает триггер 22 в положение 1 (переводя вторично блок 16 в режим преобразования Временной интервал код)5 при этом разрешающий потенциал с выхода б, триггера (фиг. Зи) подается на управляющий вход элемента И 24, открывает его и разрешает постугшение счетных импульсов генератора 29 на вход сложения реверсивного счетчика 30 (фиг. Зк) проходит П.1101866 через элемент ИЛИ 31 на выход 20 блока 16 и далее на блок 19, который формирует задний фронт пятого управляющего сигнала (фиг. Зж, разрешающий потенциал с управляютцего входа 5 ключа 13 снимается и он размыкается, отключая напряжение U от интегратора)и одновременно передний фронт шестого управляющего сигнала (фиг. Зз), устанавливающего в замкнутое положение 10 ключ 11,. через который напряжение с выхода опорного источника 8 вновь подключается к входу интегратора 10 и интегрируется им (фиг. 35, интервал времени ).15 В момент времени -fc, когда выходное напряжение интегратора 10 достигает заданной величины, т.е. нулевого значения (фиг. 35), срабатывает компаратор 14, импульс с выхода 20 которого (фиг. 3л) возвращает триггер 22 в исходное положение О, при этом разрешающий потенциал с управляющего входа элемента И 24 снимается (фиг. 3 и), поступление счетных 25 импульсов генератора 29 на вход сложения реверсивного счетчика прекращается (фиг. 3к), а код в счетчике фиксируется{Проходит через открытый элемент,И 33 (фиг. 3т) и устанавлит зо вает блок 34 выдачи кода в положение, при котором код реверсивного счетчика считывается и (с выхода 17 преобразователя 16) поступает на вычислительный блок 18; проходит через элемент 5 ИЛИ 31 и (с выхода 20 преобразователя) поступает на блок 19, который формирует задний фронт шестого и третьего управляющих сигналов (фиг. 3 3 и -г соответственно, размы- Q каются ключи 11 и 6). На этом

управления и связанных с ним. Бл рота (в ци блок ление Та ворот ся (ф где/s .4- 2Л-t, /s-t. В стве чем Э

вания предлагаемого устройства определяется его техническими преимуществами. определяет октант угла пововыдает полученный результат ой форме) на вычислительный в котором происходит вычиспределах октанта. образом, измерение угла пола осуществляется за вре3) t 4i -b4t2 f tj-bdt -tAtj , эталонный интервал времени, в течение которого интегрируется опорное напряжение, обратное по знаку выпрямленному большему напряжению; - интервал времени, в течение которого интегрируется выпрямленное и запомненное блоком 9 большее напряжение U5(jc(n| - примыкающий к 4i, интервал времени, в течение которого интегрируется . выпрямленное меньшее напряжение ( g интервал времени, в течение которого интегрируется опорное напряжение, обратное по знаку выпрямленному меньшему напряжению-, - интервал времени,- в течение которого по измеренному М определяется (вычислительным блоком) угол поворота вала в пределах октанта. лагаемых способе и устрой- . я преобразования меньше, естных. ический эффект от использо16

29

15

20

11

L.

27

Л

laanisaaiiJ 1

Фиг.г

5(ЗЛП}

tn

и

л м

н

i- t

nnintniimiiiiiiiii

iiiiiiiiiiiiiii

/

liniimiinmiiium

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА В КОД | 0 |

|

SU409262A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ преобразования угла поворота вала в код | 1976 |

|

SU732951A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-07-07—Публикация

1982-12-30—Подача