2,Преобразователь по .п. 1, о т личающийся тем, что блок определения знака разности временных интервалов содержит первьш и второй элементы И, генератор тактовой частоты, реверсивный счетчик, первый и второй триггеры, при этом первый вхо первого триггера соединен с вторым входом блока, прямой и инверсньй выходы - сдответств,енно с первыми входами элементов И, вторые входы которых соединены с выходом генератора тактовой частоты и дополнитeл.ным выходом блока, а выходы соответственно с первым и вторым входами реверсивного счетчика, первый выход которого соединен е входом установки в 1 второго триггера, инверсный выход которого соединен с выходом блока, при этом первый вход блока соединен с третьим входом реверсивного счетчика и тактирующими входами триггеров, управляющие входы которых соединены с общей шино блока.

3.Преобразователь по п. 1, отличающийся тем, что бло управления содержит счетчик циклов, дешифратор, инверторjn логических

блоков и элемент И, причем первый и второй входы блока управления соединены соответственно с. первым входом счетчика циклов и первым входом элемента И, второй вход которого соединен с выходом инвертора, а выход через счетчик циклов соединен с входами дешифратора, первый выход которого соединен с первыми входами логических блоков, второй выход - с вторыми входами всех логических блоков, кроме первого логического блока, второй вход которого соединен с общей шиной блока, при этом третий вход блока соединен с третьими входами всех логических блоков, четвертый вход каждого предьщущего логического блока соединен с пятым входом последующего логического блока и соответств.ующими Л выходами дешифратора,начиная с третьего вькода, (1+3)-й выход которого соединен с входом инвертора, причем пятый вход первого логического блока соединен с общей шиной блока управления, а четвертый и пятьй входы п-го логического блока соединены с первым и вторым дополнительными выходами блока, выходы которого соединены с выходами логических блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство для измерения действующего значения переменного напряжения | 1986 |

|

SU1401388A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU911722A1 |

| Устройство контроля качества радиотелефонных каналов связи | 1986 |

|

SU1332546A2 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Спектрометр | 1991 |

|

SU1800291A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU661783A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

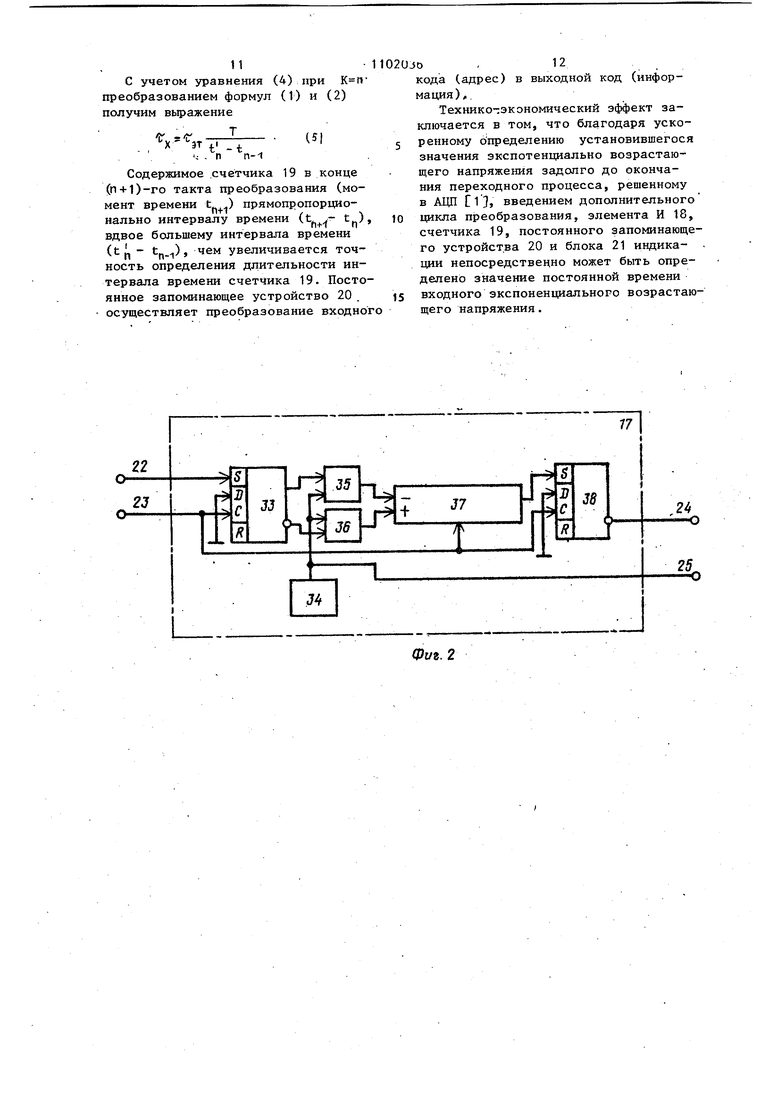

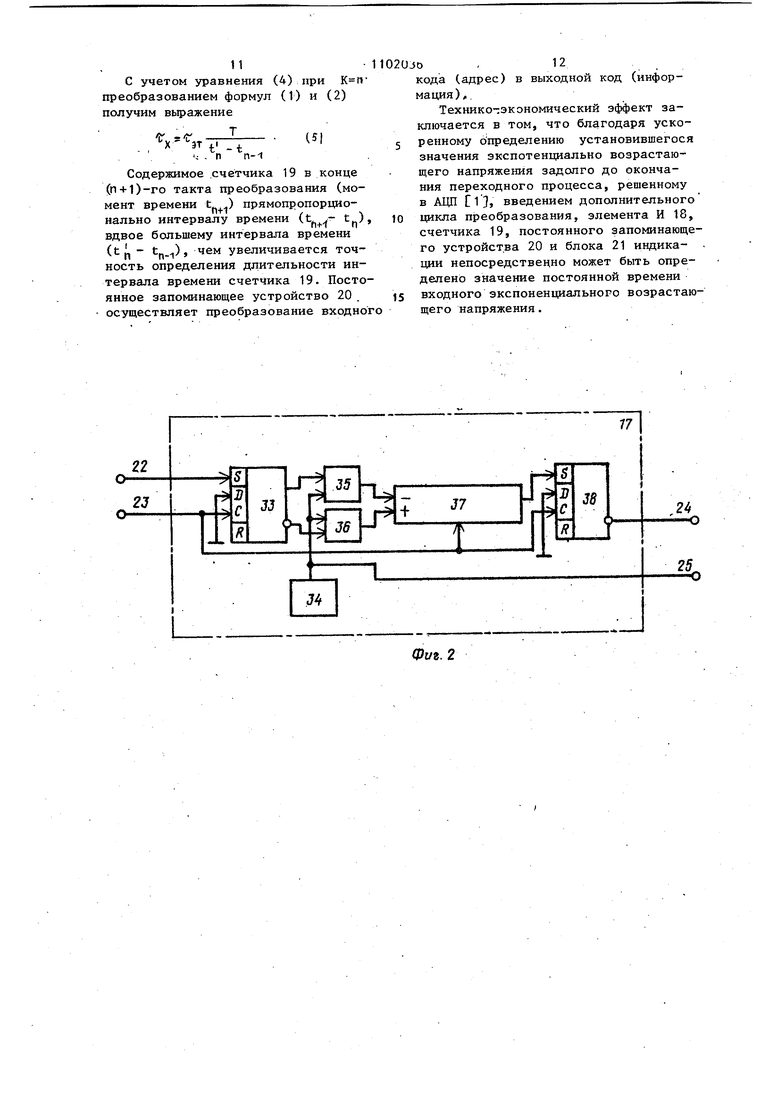

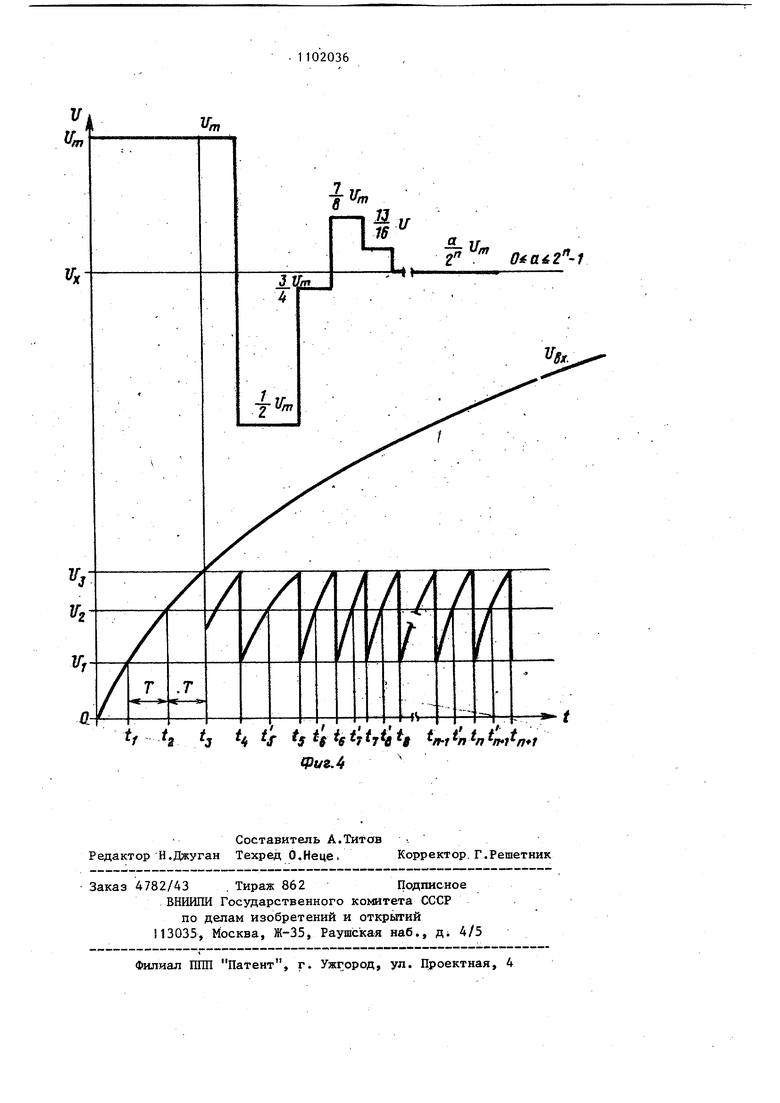

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, по авт. св. № 911722, о т,л йчающ, ийся тем, что. с целью расширения функциональных возможностей, в него введены счетчик, постоянное запоминающее устрой, ство, блок индикации и элемент И, первый вход которого соединен с дополнительным выходом блока определения знака разности временных интервалов, а второй вход - с первым дополнительным выходом блока управления второй дополнительный выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом элемента И, а выходы - с входами постоянного запоминающего устройства, выходы которого соединены с входами блока индикации. .« (Л с

Изобретение относится к автоматике, телемеханике, электронной изме рительной и вычислительной технике и может быть использовано в информагщонно-измерительных системах при

опросе датчиков, выходной сигнал которых представляет собой экспоненциально растущее напряжение с бoльши значением постоянной времени.

По основному авт. св. № 911722

известен аналого-цифровой преобразователь, содержащий усилитель входного сигнала, выход которого соединен с первым входом первого запоминающего уйтройства, второй вход которого

соединен с выходом усилителя импульza запуска, а выход - с первым входом первого нуль-органа, блок управления выходы которого соединены с входами регистра, выходы которого соединены с входами цифроаналогового преобразователя, второе и третье запоминающее устройство, два элемента задержки, второй и третий нуль-органы, интегрирующую КС-цепь, ключ, триггер и блок определения знака разности временных интервалов, причем пер-вые входы второго и третьего запоминающих устройств соединены с выходом усилителя входного сигнала, второй вход второго запоминающего устройства соединен с выходом первого элемента задержки и входом второго элемента задержки, второй вход третьего запоминающего устройства соединен с выходом второго элемента задержки и первьм входом блока управления, выходы второго и третьего запоминающих устройств соединены с первыми входами второго и третьего нуль-органа соответственно, вторые входы которых соединены со вторым входом первого нуль-органа, выходом интегрирующей КС-цепи и выходом клю3. ча, первый вход которого соединен с общей шиной, а второй вход - с вторым входом блока управления, первым входом блока определения знака разности временных интервалов и выходом триггера, первьш вход которого соединен с выходом первого нуль-органа Второй вход - с выходом третьего нуль-органа, причем выход второго нуль-органа соединен со вторым блока определения знака разности временных интервалов, выход которого соединен с третьим входом блока управления, вход первого элемента задержки соединен с выходом усилителя импульса запуска, а вход интегрирующей КС-цепи соединен с выходом цифроаналогового преобразователя 11 . Недостаток аналого-цифрового преобразователя заключается в отсут ствии возможности непосредственного определения постоянной времени переходного процесса, например постоянной времени, термодатчика, необходимость которого возникает при авто матической сортировке термодатчиков на заводах-изготовителях за возможно короткий промежуток времени. Целью изобретения является расши рение функциональных возможностей за счет непосредственного определения постоянной времени переходного процесса за короткий промежуток вре мени. Цель достигается тем, что в аналого-цифровой преобразователь введе ны счетчик, постоянное запоминающее устройство, блок индикации и элемент И, первый вход которого соединен с дополнительным выходом блока определения знака разности временны интервалов, а второй вход - с первы дополнительным выходом блока управления, второй дополнительный выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом элемента И, а выходы - с входами постоянного запомя- нающего устройства, выходы которого соединены с входами блока индикации Причем блок определения знака разности временных интервалов содер жит первый и второй элементы И, ген ратор тактовой частоты, реверсивньШ счетчик, первый и второй триггеры, первый вход первого, триггера соединен со вторым входом блока, прямой и инверсньй выходы - соответственно 64 с первыми входами элементов И, Ьторые входы которых соединены с выходом генератора тактовой частоты и дополнительным выходом блока, а выходы соответственно с первым и вторьтм входами реверсивного счетчика, первый выход которого соединен со вхлдом Установки в 1 второго триггера инверсный выход которого соединен с выходом блока, при этом первый вход блока соединен с третьим входом реверсивного счетчика и тактирую-, щими входами триггеров, управляющие входы которых соединены с общей шиной блока. При этом блок управления содержит счетчик циклов, дешифратор, инвертор, п логических блоков и элемент И, причем первый и второй входы блока управления соединены соответственно с первым входом счетчика ujiKлов и первым входом элемента И, второй вход которого соединен с выходом инвертора, а выход через счетчик циклов соединен с входами деишфратора, первый выход которого соединен с первыми входами логических блоков, второй выход - со вторыми входами всех логических блоков, кроме первого логического блока, второй вход которого соединен с общей шиной блока, при этом третий вход блока соединен с третьими входами всех логических блоков, четвертый вход каждого предьщущего логического блока соединен с пятым входом последующего логического блока и соответствующими Т выходами дешифратора, начиная с третьего выхода, Vi+3 выход которого соединен с входом инвертора. причем пятый вход первого логического блока соединен с общей шиной блока, а четверт.ьй и пятый входы п-го логического блока соединены с первым и вторым дополнительными выходами блока, выходы которого соединены с выходами логических блоков. На.фиг, 1 приведена структурная электрическая схема преобразователя, на фиг. 2 - .то же, блока определения .знака разности временных интервалов, на фиг. 3 - то же, блока управленид, на фиг. 4 - временные диаграммы, поясняющие принцип работы преобразователя. Аналого-цифровой преобразователь содержит усилитель 1 входного сигнала, запоминающие устройства 2-4, нуль органы 5-7, интегрирующую RC-цепь 8, ключ 9, усилитель 10 импульса за пуска, элементы 11 и 12 задержки, блок 13 управления, регистр 14, циф аналоговый преобразователь (ЦАП) 15 триггер 16, блок 17 определения зна ка разности временных интервалов,эл мент И 18, счетчик 19, постоянное запоминающее устройство 20, блок 21 индикации, блок -17 имеет входы 22 и 23, выходы 24 и 25. Блок 13 имеет входы 26-28 и выходы 29-32. Входом АЦП является вход усилите ля 1, подключенного своим выходом к входам запоминающих устройств 2-4, выходы которых соединены с входами нуль-органов 5-7, к вторым входам которых подключен выход интегрирующей RC-цепи 8, который через ключ 9 соединен также с общей шиной, а вход интегрирующей КС-цепи 8 подключен к выходу цифроаналогового преобразователя 15. Вход импульса запуска через усилитель 10 импульса запуска подключен к управляющему входу запо . минающего устройства 2 и через элемент 11 задержки к управляющему вход запоминающего устройства 3, а через элементы 11 и 12 задержки к управляющему входу запоминающего устройст ва 4 и ко входу 27 блока 13 управления, выходы нуль-органов 5 и 7 под ключены к входам триггера16, выход которого соединен с управляющим входом ключа 9, входом 26 блока 13 уп равления и входом 23 блока 17, на вход 22 которого подключен выход нУ(ПЬ-органа 6, а выход 24 соединен с входом 28 блока 13 управления, выходы 29 и 30 которого соединены с входами регистра 14, выходы которого соединены со входами цифроаналогового преобразователя 15, выход 31 блока 13 управления и выход 25 блока 17 подключены к входам элемента И 18, выход которого соединен с счетным входом счетчика 19, на вход установки в нуль которого под.ключей выход 32 блока 13. Постоянное запоминающее устройство 20,- подключенное своими адресными входами к выходам счетчика 19, своими выходными информационными шинами соединено с входами блока 21 йвдикации. Блок 17 содержит триггер 33, генератор ЗА тактовой частоты, элементы Vi 35 и 36, реверсивный счетчик 37 и триггер 38, вход 22 блока 17 соединен с входом установки в еди36ницу триггера 33, прямой и инверсный выходы которого через элементы И 35 и 36, к вторым входам которых подключен выход генератора 34 тактовой частоты, подключены к входам обратно го и прямого счетов реверсивного счетчика 37, вькод отрицатеньного переноса которого соединен с входом установки в единицу триггера 38, инверсный выход которого является выходом 24 блока 17, выход генератора,34 является его выходом 25, а вход 23 блока подключен к тактирующим входам триггеров 33 и 38 и входу установки в нуль, реверсивного счетчика 37. Блок 13 содержит элемент И 39, счет чик 40 циклов, дешифратор 41, инвертор 42,п логических блоков 43-1 - 43-п, вход 27 блока 13 подключен к входу установки в нуль счетчика 40 циклов, вход 26 через элемент 39 соединен с его счетным в-ходом, а своими выходами счетчик 40 циклов подключен к входам дешифратора 41, последний выход которого через инвертор 42 соединен со вторым входом элемента И 39, вход 28 и выходы дешифратора 41 подключены к входам логических блоков 43-1 - 43-п, выходы которых являются выходами 29, 30, выход дешифратора 41 является выходом 31, а м-ый выход дешифратора 41 выходом 32 блока 13. Преобразователь работает следующим образом. На его вход подается экспоненциально растущее напряжение Ugjj и( ), которое после усиления усилителей 1 поступает на входы запоминающих устройств 2-4. Работа преобразователя начинается после подачи импульса запуска, усиленного усилителем 10. Б момент времени t, соответствующий подаче импульса за- , пуска, входное напряжение запоминается в запоминающем устройстве 2 (и, фиг. 4). В момент времени t при котором импульс запуска появляется на элемента 11 задержки, входное напряжение запоминается в запоминающем устройстве 3 (U2 а в момент времени t.-, при котором импульс запуска появляется на выходе элемента 12 задержки, входное напряжение запоминается в запоминающем-устррйстве 4 (и). Импульсом на выходе элемента 12 задержки, действуя на вход 27 блока 13, устанавливается счетчик 40 циклов в нуль, в результате чего на первом выходе дешифратора 41 устанавливается потенциал логической единицы, поступающий на первый вход всех логических блоков 43-1 - 43-п, в результате чего все выходы 29 блока 13 принимают уровень логической единицы устанавливающие все разряды регистра 14 в единицу, что соответствует максимальному значению напряжения на выходе ЦАП 15 (и.) . Начинается экспоненциальный рост напряжения на конденсаторе интегрирующей КС-цепи 8 от произволь ного уровня с максимальной скоростью до достижения этим напряжением уровня напряжения U, поступающего из запоминающего устройства 4 на второй вход нуль-органа. 7, под воздействием выходного сигнала которого триггер устанавливается в состояние единиць замыкает ключ 9, через вход 26 блок 13 и элемент И 39, на втором входе которого имеется потенциал логической единицы, на счетный вход счетчика 40 циклов поступает один импульс, под воздействием которого на втором выходе дешифратора 41 устана ливается уровень логической единицы (а все остальные выходы дешифратора 41 находятся в состоянии логического нуля), в 1)езультате чего выход 30 блока 13 принимают уровень логической единицы, устанавливающие все кроме старшего разряда регистра 14 в состояние нуль, что срответствует напряжению 1/2 U на выходе ЦАП 15. Под воздействием сигнала выхода триггера 16 на вход 23 блока 17 триггер 33 и реверсивньй счетчик 37 устанавливаются в нуль,на вход прямого счета реверсивного счетчика 37 через элемент И 36 к второму входу которого подключен инверсньп выход триггера 33, поступают импуль сы генератора 34 тактовой частоты, а счет реверсивного счетчика 37 возможен только после снятия сигнгьп устанавливающего его в нуль. На выходе 24 блока 17 устанавливается потенциал логической еди-ницы. Разря ковденсатора КС-цепи 8 продолжается до достижения им уровня напряжения и , поступающего из запоминающего устройства1 2 на вход нуль-органа 5 на вход .нуль-органа (момент t), по выходному сигналу, которого триггер 16 возвращается .в состояние нуля, ключ 9 размыкается и триггер 38 блока 17 устанав6ливается в нуль. Конденсатор RC-цепн начинает заряжаться по экспоненте, устанс(вивш1-1мся значением которой является выходное напряжение ЦАП 15, равное в Данный момент /2 U. Импульсная последовательность генератора 34 тактовой частоты, поступающая через выход 25 блока 17 на вход зле- мента И.18 ввиду того, что, в данный момент времени выход 31 блока 13 находится в состоянии логического нуля, на счетный вход счетчика 19 не поступает. При равенстве значения напряжения на конденсаторе RC ,цепи 8 и значения напряжения на выходе запоминающего устройства срабатывает нуль-орган 6, выходной сигнал которого воздействием на вход 22 блока 17 устанавливает триггер 33 в состояние единицы, в результате чего прекращается подача импульсов генератора 34 через элемент И 36 на вход прямого счета реверсивного счетчика 37, через элемент И 35 импульсы генератора 34 поступают на вход обратного счета реверсивного счетчика 37. После заряда конденсатора RC-цепи 8 до-уровня срабатывания нуль-органа 7 (момент t) его выходным сигналом триггер 16 устанавливается в состояние едини1 1, под воздействием которой замыкается ключ 9 и начинается разряд конденсатора КС-цепи 8 через вход 26 блока 13 и элемент 39, на втором входе которого имеется потенциал логической единицы. На счетный вход счетчика 40 циклов поступает один импульс, под воздействием которого на третьем выходе дешифратора 41 устанавливается потенциал логической .единицы, в результате действия которой на первый и второй логические блоки 43-1, 43-2 на выходе 30 первого логического блока 43-1 сохраняется потенциал логического нуля, так как в данньш момент времени на входе 28 блока 13, соединенном с первыми входами логических блоков 43-1 - 43-п имеется потенциал Логического нуля, свидетельствующий о на выхотом, что де второго логического блока 43-2 (выход 29) появляется потенциал лог гической единицы, устанавливающий разряд регистра 14 с весом в состояние единицы. В итоге на выходе ЦАП 15 установится напряжени.е, равное 3/4 и.. Поступлением выходного импульса триггера 1b на вход 23 бло 17 триггер 33 и реверсивный счетчик 37 устанавливаются в нуль, а задним его фронтом, появляюпщмся после сра батывания нуль-органа 5, выходной сигнал которого переводит триггер 1 ;в состояние нуля, разряд конденсато ра КС-цепи 8 заканчивается, ключ 9 размыкается и начинается эаряд конденсатора КС-цепи по экспоненте, установившееся значение которой рав но 3/4 и, триггер 38 устанавливается в нуль. Начинается следующий цикл преобразования. Причем в конце каждого цикла преобразования на основе выходного сигнала блока 1 (выход 24) блоком 13 вырабатывается сигнал установки в нуль К-ого разря да регистра 14, если t(- t| кВ противном случае К-ый разряд оста нется в состоянии единицы. Следующи по порядку уменьшения веса разряда регистра 14 устанавливается в едини (пробное включение разряда) под воздействием потенциала логической единицы соответствующего выхода 29 блока 13. Работа АЦП продолжается до тех пор, пока не установлен самый младший разряд регистра 14, а выходное напряжение ЦАП 15 в этот момент времени отличается от выходного на пряжения и не больше, чем на эквивалент напряжения младшего разряда ЦАП 15. .. Это происходит задолго до достижения входным напряжением Ug своего установившегося значения И. После окончания п -го цИ1спа выходным импульсом триггера 16 счетчик 40 циклов устанавливается в состояние h + 1, на выходе 31 блока 13 появляется потенциал логической единицы и импульсная последовательность с выхода 25 блока 17 через элемент И 18 поступает на счетньй вход счетчика 19, который под воздействием выхода 32 блока 13 на п-ном цикле преобразования был устанОвден в нуль Содержимое счетчика 19 возрастает до момента срабатывания нуль-органа 7 и, в дальнейшем не изменится, что достигается действием выхода инверто ра 42, подключенного своим входом к последнему выходу дешифратора 41, на второй вход элемента И 39 блока 1 Содержимое счетчика 19 обратно пропорционально искомому значению постоянной времени входного экспо6ненциально возрастающего напряжения Uj( . Выходные сигналы счетчика 19 поступают на адресные входы постоянного запоминающего устройства 20, на выходных информационных шинах которого устанавливается код обратной величины по отношению к той величине, код которой подан на его адресные входы. Блок 21 индикации, на входы которого поступают выходные сигналы постоянного запоминающего устройства 20, индицирует значение постоянной времени. Из описанного принципа рсаботы АЦД и приведенной временной диаграммы видно, что для входного напряже- ния экспоненциальной формы можно записать и ( и)(1-е :) , (1) и,, - текуш;ие значения экспогде и , ненциального напряжения подаваемого на вход АЦП в моменты времени t и t, зафиксированные в запоминающих устройствах 2 и 3i иУ - значение напряжения, к которому стремится экспоненциально возрастаю щее напряжение; Т - время задержки элементов 11 и 12 задержки; t - исходное значение постоянной времени экспоненты, подаваемой на вход АЦП. С другой стороны, для вьфаботанного на выходе ЦАП 15 напряжения Е, подаваемого на интегрирующую КС-цепь, 8, можно записать эт U2-1J (Eg- U)(1-e гдеВд К С - постоянная времени интегрирующей КС-цепи 8 (); (t-t. ) - время между срабатыванием нуль-органов 5 и 6 на К-ом цикле АЦП. Равенство временных интервалов ч- чкоторое с минимальным расхождением соблюдается после п-го цикла преобразования, означает, что ЕО УХ с учетом уравнения (4) при преобразованием формул (1) и (2) получим выражение %-v-, Содержимое .счетчика 19 в конце (п + 1)-го такта преобразования (момент времени t ) прямопропоргщонально интервалу времени вдвое большему интервала времени (t|,- t|.), чем увеличивается точность определения длительности интервала времени счетчика 19. Посто янное запоминающее устройство 20 осуществляет преобразование входно

Фиг. 2 D кода (адрес) в выходной код (информация),. Технико-экономический эффект заключается в том, что благодаря ускоренному определению установившегося значения экспотенциально возрастающего напряжения задолго до окончания переходного процесса, решенному в АЦП введением дополнительного цикла преобразования, элемента И 18, счетчика 19, постоянного запоминающего устройства 20 и блока 21 индикации непосредственно может быть определено значение постоянной времени входного экспоненциального возрастающего напряжения.

Оо01

а

%

CS4

I

5

15

о о

о о

о

«м

ъ

«м

in

со

см

м

сэ

ts.

55

См см

о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU911722A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-07—Публикация

1983-04-12—Подача