Изобретение относится к речевой информатике и может быть использовано в различных системах речевого взаимодействия человека с ЭВМ.

Целью изобретения является увеличение объема хранимой речевой информации при фиксированном объеме памяти.

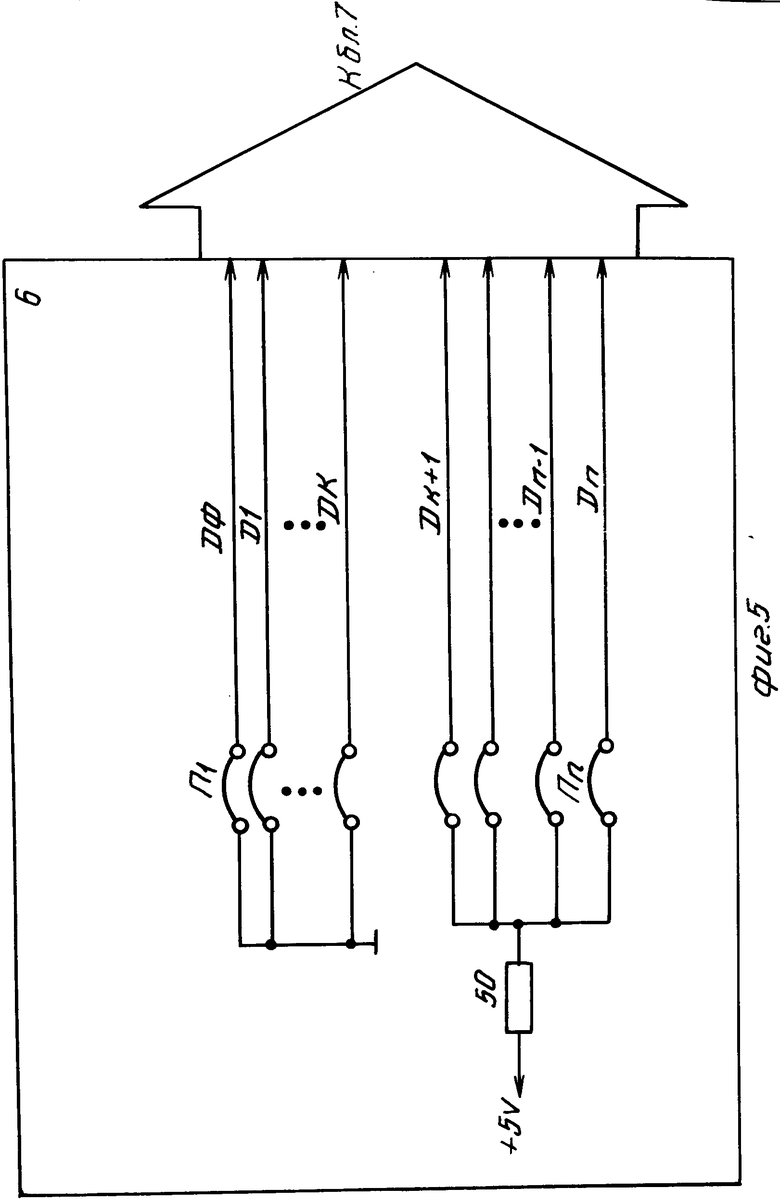

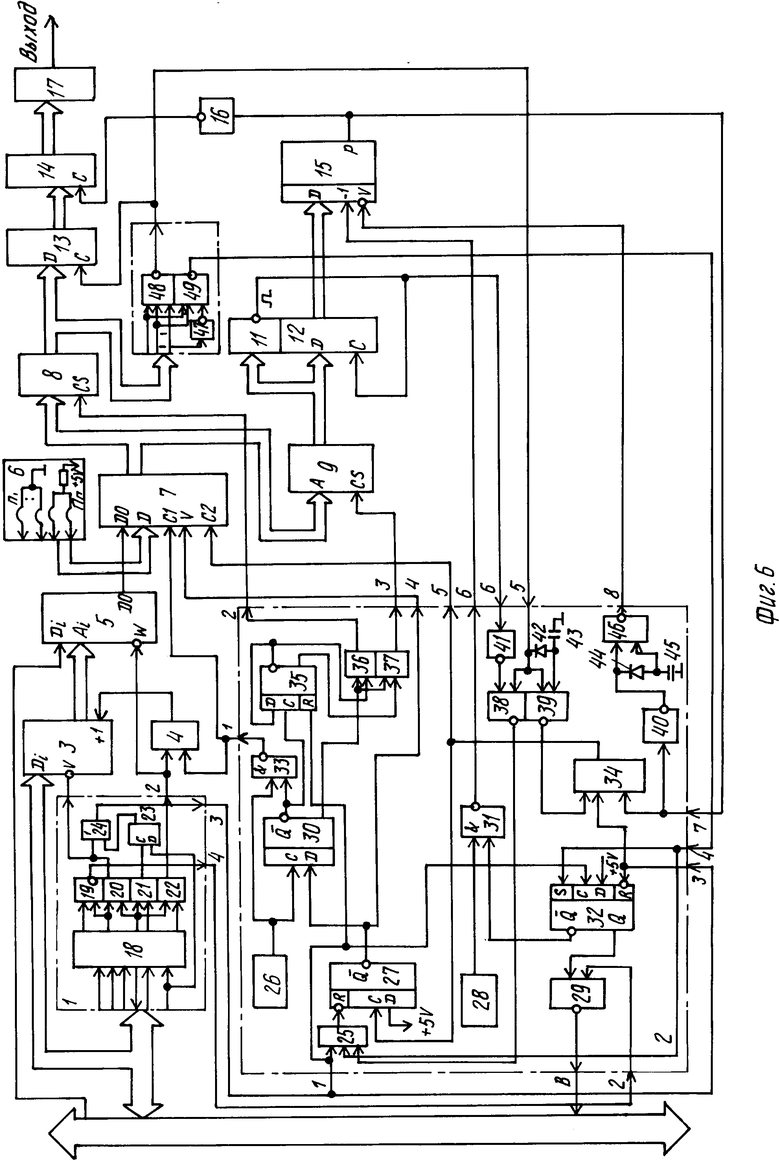

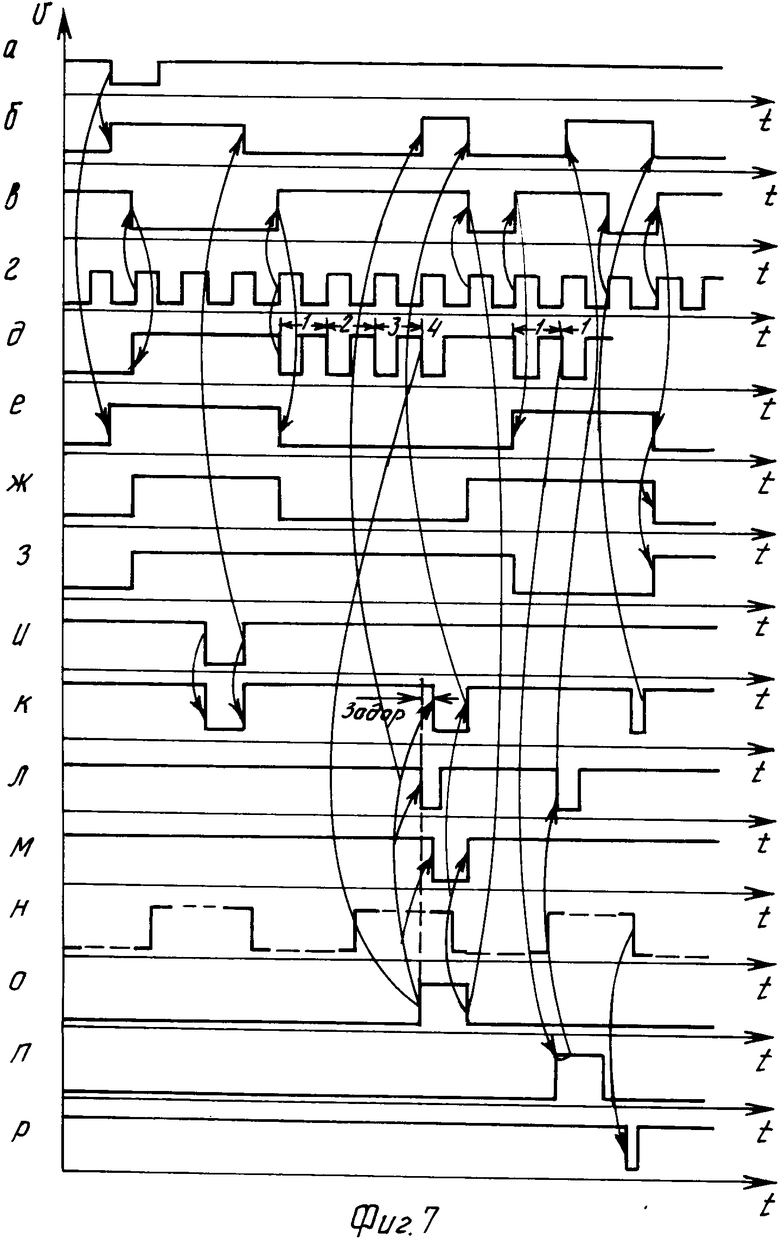

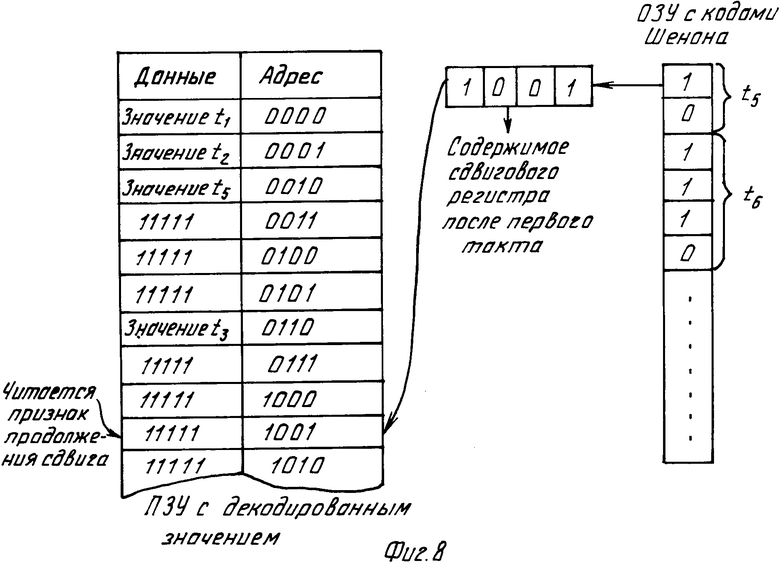

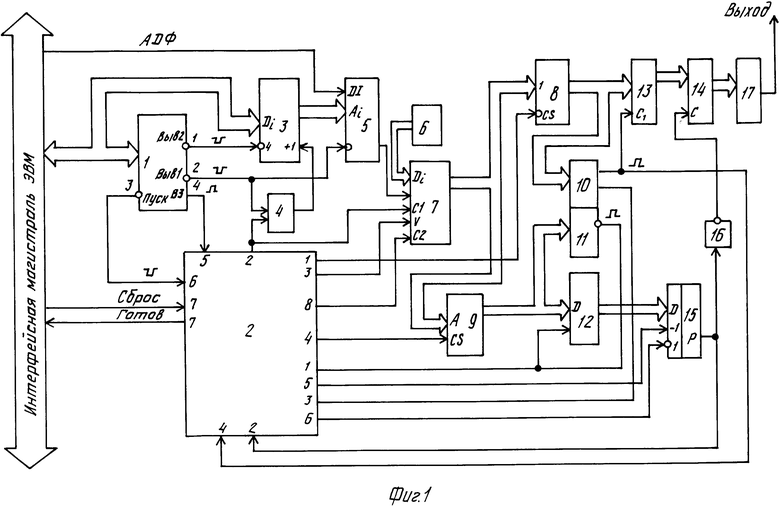

На фиг. 1 представлена структурная схема устройства для синтеза речевых сигналов; на фиг. 2 - вариант реализации дешифратора адреса с ЭВМ; на фиг. 3 - вариант реализации блока управления; на фиг. 4 - вариант реализации блока фиксации; на фиг. 5 - вариант реализации блока кода; на фиг. 6 - принципиальная схема устройства для синтеза речевых сигналов; на фиг. 7 - временная диаграмма работы устройства; на фиг. 8 и 9 - представлены схемы, иллюстрирующие процесс декодирования информации.

Устройство для синтеза речевых сигналов (фиг. 1) содержит дешифратор 1 адреса, блок 2 управления, генератор 3 адреса, элемент И 4, блок 5 памяти, блок 6 кода, сдвиговый регистр 7, блок 8 памяти амплитуд, блок 9 памяти времени, блок 10 фиксации, элемент И-НЕ 11, регистр 12 времени, регистр 13 амплитуд, выходной регистр 14, реверсивный счетчик 15, элемент НЕ 16, цифроаналоговый преобразователь (ЦАП) 17.

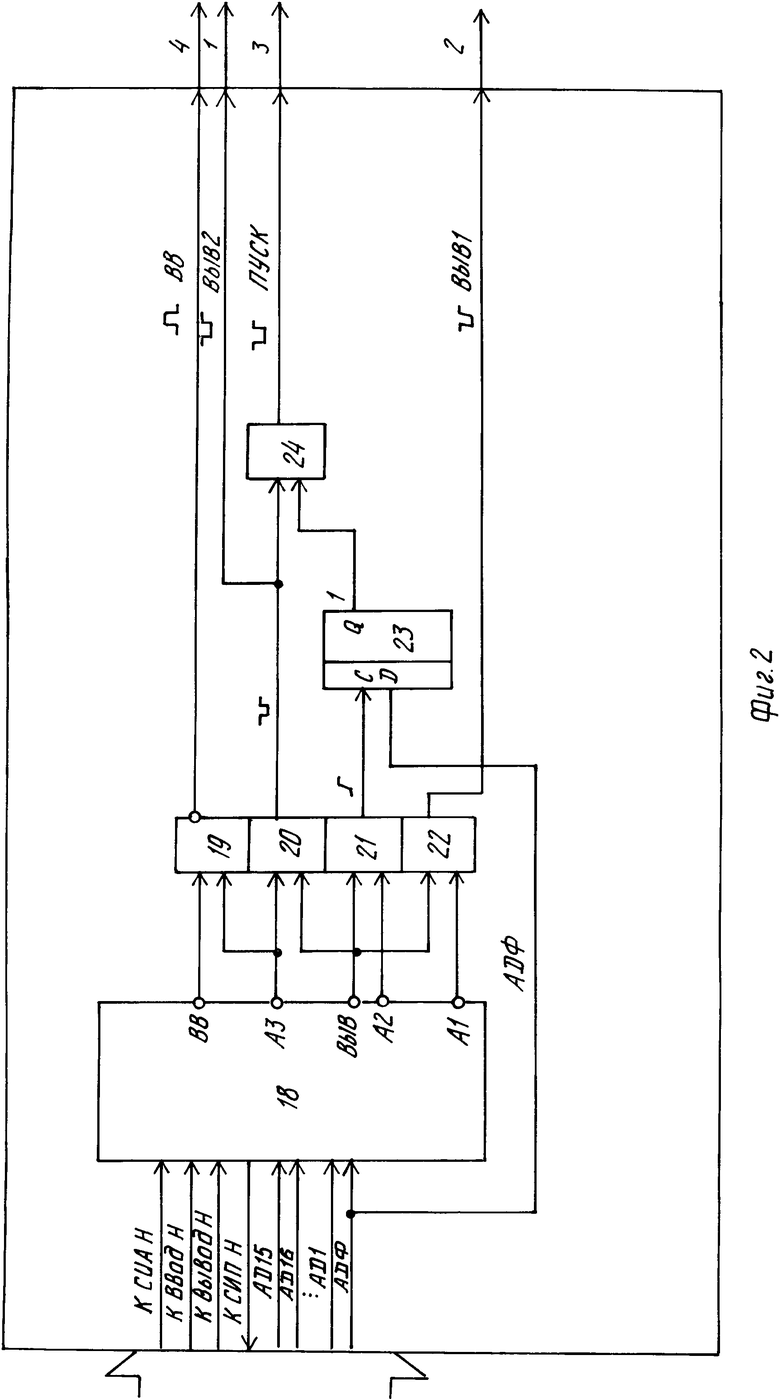

Дешифратор 1 адреса (фиг. 2) содержит селектор 18 адреса, элемент ИЛИ-НЕ 19, элементы ИЛИ 20, 21, 22, триггер 23, элемент ИЛИ 24.

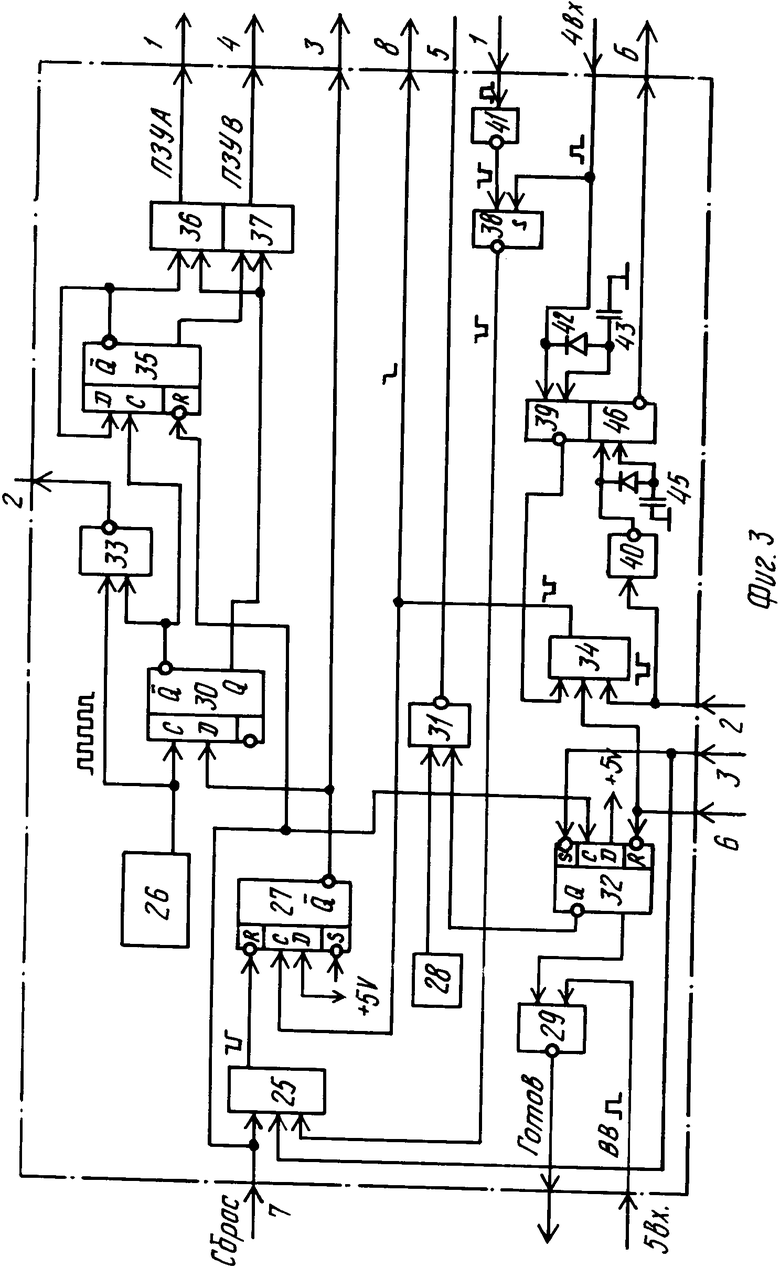

Блок 2 управления (фиг. 3) содержит элементы И 25, 34, тактовые генераторы 26, 28, триггеры 27, 30, 32, 35, элементы И-НЕ 29, 31, 33, 39, 46, элементы ИЛИ 36, 37, формирователь 38 импульса, инверторы (элементы НЕ) 40, 41, диоды 42, 44, конденсаторы 43, 45.

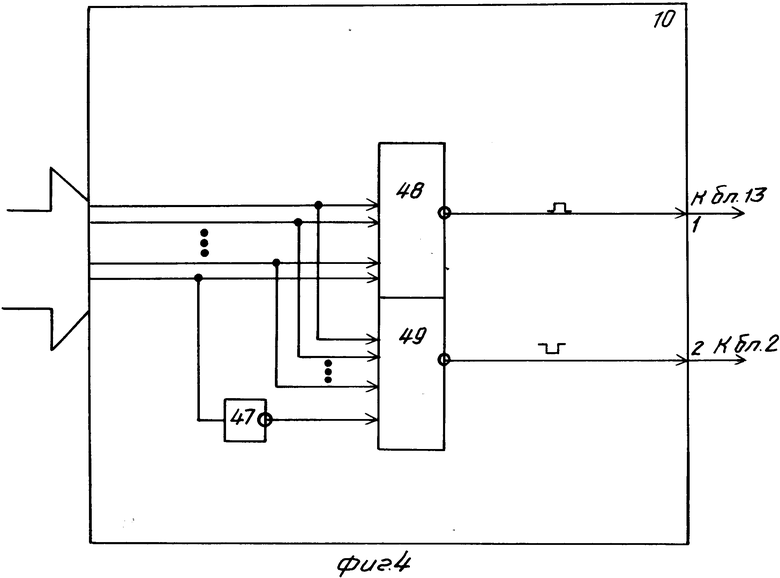

Блок 10 фиксации (фиг. 4 ) содержит элемент НЕ 47, элементы И-НЕ 48, 49.

Блок 6 кода (фиг. 5) содержит резистор 50 и перемычки П1-Пn, где n - разрядность сдвигового регистра 7.

На фиг. 7 изображены временные диаграммы работы устройства, где а - сигнал на седьмом входе блока 2 управления, б - инверсный выход триггера 27, в - инверсный выход триггера 30, г - тактовые импульсы тактового генератора 26, д - выход элемента И-НЕ 33, е - инверсный выход триггера 35, ж - выход элемента ИЛИ 36, з - выход элемента ИЛИ 37, и - сигнал "Пуск" на шестом входе блока 2 управления, к - выход элемента И 34, л - выход формирователя 38, м - выход элемента И-НЕ 39, н - инвертированные импульсы тактового генератора 28 на выходе элемента И-НЕ 31, о - второй выход блока 10 фиксации, n - выход элемента И-НЕ 11, р - импульс обнуления с выхода реверсивного счетчика 15 на втором входе блока 2.

Рассмотрим сущность изобретения.

В прототипе предполагается, что речь кодируется путем периодического аналого-цифрового преобразования величины звукового сигнала, логарифмирования и записи полученных двоичных кодов в постоянное запоминающее устройство (ПЗУ). При воспроизведении речи данные считываются из ПЗУ с такой же частотой, восстанавливаются (потенцируются) экспандером и подаются на ЦАП. Сущность изобретения заключается в использовании сжатого представления сигнала. Каждая полуволна аппроксимируется прямоугольным импульсом, после чего в память заносятся эффективные коды Шеннона или Хафмана длины и высоты импульса.

При воспроизведении эффективные коды восстанавливаются, т.е. преобразуются в позиционные двоичные коды, после чего код амплитуды импульса подается на ЦАП, а код времени записывается в счетчик для отсчета длительности импульса.

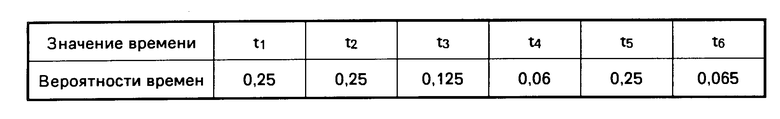

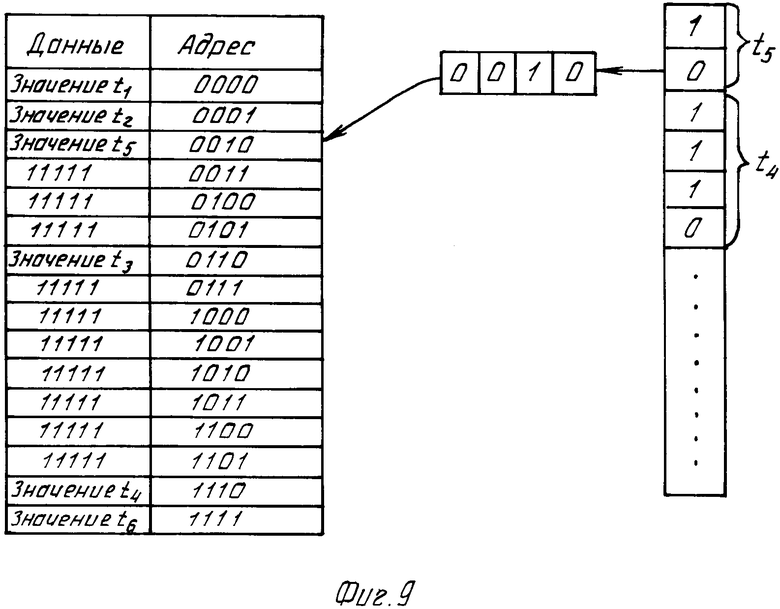

Увеличение длительности хранимой речи иллюстрируется таблицей вероятностного появления определенных временных интервалов и фиг. 8 и 9. Пусть длительности прямоугольных импульсов, последовательностью которых аппроксимирован звуковой сигнал, имеют шесть возможных значений, вероятности появления которых приведены в таблице. Если закодировать эти времена следующими кодовыми комбинациями: t1=00, t2=01, t5=10, t3=110, t4=1110, t6=1111, то на кодирование одного интервала времени расходуется в среднем 2˙0,25+2 x x0,25+30,125+4˙0,06+2˙ 0,25+ + 4˙0,065=2,375 битов.

Диапазон значений t1-t6 может быть таким, что для кодирования времени позиционным двоичным кодом требуется в несколько раз больше памяти. Например, если максимальное значение времени ti равно 20 единицам дискретности, то для кодирования длительности импульса требуется 5 битов. Аналогично достигается сокращение среднего числа разрядов, кодирующих амплитуду импульса.

Преобразование эффективных кодов в позиционный двоичный код основано на том, что ни одна из кодовых комбинаций не совпадает с началом другой, более длинной кодовой комбинации. Поэтому можно, как показано на фиг. 8 и 9, побитно считывать содержимое запоминающего устройства (в данном случае оперативного запоминающего устройства - ОЗУ), в котором хранятся коды Шеннона, в сдвиговый регистр и использовать содержимое сдвигового регистра как адрес ПЗУ. В сдвиговый регистр предварительно заносится начальный код, и его содержимое можно рассматривать как кодовую комбинацию эффективного кода, заполненную в старших разрядах до равномерного кода.

Пусть начальное состояние сдвигового регистра 1100 и из ОЗУ читается код t5. После первого такта сдвига в сдвиговом регистре оказывается код 1001 (фиг. 8), который не совпадает ни с одним из кодов t1-t6. По адресу 1001 в ПЗ У записан код (например, состоящий из всех единиц), который является признаком необходимости еще одного сдвига. По следующем такту (фиг. 9) в сдвиговом регистре записана кодовая комбинация интервала. По адресу 0010 из ПЗУ читается позиционный двоичный код интервала.

Декодирование интервала t4 осуществляется за четыре такта. После первых трех сдвигов по адресам 1001<<-, 0011<<-, 0111<<-, в ПЗУ читаются коды 11111, являющиеся признаком продолжения сдвига, а после четвертого сдвига по адресу 1110 читается значение интервала.

Поскольку при воспроизведении каждой полуволны сигнала необходимо декодировать две величины: длительность и амплитуду импульса, причем для их декодирования требуется различное количество тактов, необходимо включить в устройство два однотипных канала декодирования.

При подготовке данных должно быть предусмотрено ограничение максимальных значений высоты и длительности импульсов таким образом, чтобы ни одно из возможных значений не совпало с признаком продолжения сдвига. Кроме того, в ОЗУ может храниться одновременно несколько фраз, поэтому надо зарезервировать одно значение (например, код 11110) под признак конца фразы. В этом случае воспроизведение фразы начинается заданием адреса ее начала, а заканчивается при считывании из ОЗУ признака конца.

Необходимо отметить, что содержимое ПЗУ хранит набор декодированных значений длительности и высоты импульсов индивидуально для каждого диктора и ансамбля сообщений, т.е. необходимо предварительно записать на диск все возможные фразы, произвести их статистическую обработку, построить код на его основе, определить содержимое ПЗУ. Работает устройство следующим образом.

По сигналу "Сброс" (он подается из интерфейсной магистрали низким уровнем) триггер 27 блока 2 управления сбрасывается в ноль, на его инверсном выходе появляется единица, которая по переднему фронту импульса тактового генератора 26 заносится в триггер 30. Сигнал низкого уровня с инверсного выхода триггера 30 запрещает прохождение через элемент И-НЕ 33 тактовых импульсов генератора 26 на первый тактовый вход регистра 7 сдвига, на второй вход элемента И 4. По сигналу "Сброс" триггер 35 сбрасывается, и высокий уровень сигнала с его инверсного выхода устанавливает единицы на выходах элементов ИЛИ 36 и 37. Это устанавливает выходы блока 8 и блока 9 в третье состояние. По заднему фронту сигнала "Сброс" в триггер 32 заносится единица, которая является признаком готовности устройства. Состояние триггера 32 может читаться в интерфейсную магистраль через элемент И-НЕ 29, если на втором входе блока появляется сигнал высокого уровня. Кроме того, ноль с инверсного выхода триггера 32, попадая на вход элемента И-НЕ 31, запрещает прохождение импульсов тактового генератора 28 на вычитающий вход реверсивного счетчика 15.

Представленный на фиг. 2 дешифратор 1 обеспечивает обмен информацией между устройством и процессором ЭВМ с использованием интерфейса МПИ (ОСТ 11.305.903-80). При обращении процессора по одному из адресов А1, А2, А3 появляется активный низкий уровень на соответствующем выходе А1, А2 или А3 селектора 18 адреса и на его выходе ВВ или ВЫВ, если осуществляется соответственно интерфейсный цикл ВВОД или ВЫВОД (подробно работа селектора адреса описана, например, в справочнике Микропроцессоры и микропроцессорные комплекты интегральных микросхем, том. 1/Под ред. В.=Б.Б. Абрайтиск. М.: Радио и связь, 1988, с. 277-279). Для подготовки устройства к записи информации в блок 5 памяти необходимо выдать из процессора ЭВМ нулевой код по адресу А2. Логический "0" в интерфейсе МПИ задается высоким уровнем сигнала. Поэтому младший разряд кода, выводимый на интерфейсную шину АД, взводит триггер 23 и этим запрещает прохождение на выход дешифратора 1 сигнала низкого уровня с выхода АЗ селектора 18 адреса (через элементы ИЛИ 20 и 24). В этом случае при записи кода из процессора по адресу А3 сигнал ноль на третьем выходе дешифратора 1 (сигнал "Пуск") не появляется, а на первом выходе дешифратора 1 появляется импульс низкого уровня (сигнал ВЫВ), который записывает адрес ячейки блока 5 памяти в генератор 3 адреса.

Для записи информации в блок 5 памяти необходимо выдать информацию по адресу А1 в цикле ВЫВОД. В результате этого на вором выходе дешифратора 1 формируется (через элемент ИЛИ 22) импульс низкого уровня, который, попав на вход записи блока 5, записывает бит в блок 5 и, пройдя через элемент И 4, задним фронтом увеличивает на единицу содержимое генератора 3 адреса, установив следующий адрес для записи в блок 5 памяти. В результате повторения описанных действий в блоке 5 устройства записываются данные, необходимые для воспроизведения речи.

Для воспроизведения речи необходимо записать код единицы из процессора ЭВМ по адресу А2. При этом по переднему фронту сигнала ВЫВ сбрасывается триггер 23, сигнал низкого уровня с прямого выхода этого триггера попадает на вход элемента ИЛИ 24, разрешая формирование сигнала "Пуск", после чего необходимо сфомировать сигналы ВЫВ 2 и "Пуск" записью кода начального адреса фразы из процессора по адресу А3. Сформированный сигнал ВЫВ 2 записывает начальный адрес фразы в генератор 3 адреса, а сигнал "Пуск", попав на вход сброса триггера 32 и на вход элемента И 34, совершает следующие действия. Триггер 32 сбрасывается, и единица с его инверсного выхода разрешает прохождение через элемент И-НЕ 31 тактовых импульсов на вычитающий вход реверсивного счетчика 15. Этот счетчик начинает вычитание числа, которое занесено в него по включении питания (это может быть любой код от 0 до 3778 для восьмиразрядного счетчика). Кроме того, сигнал "Пуск", пройдя через элемент И 34, низким уровнем заносит в сдвиговый регистр 7 начальный код из блока 6 кода. Сдвиговый регистр 7 был уже установлен по управляющему входу V (высокий уровень с инверсного выхода триггера 27) в режим параллельного занесения информации. По заднему фронту сигнала "Пуск" в триггер 27 записывается единица. Ноль с инверсного выхода этого триггера попадает на управляющий вход сдвигового регистра 7 и устанавливает его в режим сдвига вправо. Кроме того, ноль с инверсного выхода триггера 27 записывается по переднему фронту тактового импульса генератора 26 в триггер 30, на инверсном выходе которого устанавливается единица, а на прямом - ноль. Переход сигнала на инверсном выходе триггера 30 из нуля в единицу заносит в триггер 35 единицу, а на его инверсном выходе устанавливается ноль. Таким образом, на выходе элемента ИЛИ 36 появляется низкий уровень сигнала, а на выходе элемента ИЛИ 37 - высокий уровень сигнала. Это разрешает блоку 8 работать в режиме опознания кода, а блоку 9 запрещает, и выходы его остаются в третьем состоянии, поэтому на выходе элемента И-НЕ 11 присутствует низкий уровень сигнала.

Тактовые импульсы с второго выхода блока 2 управления по перепаду из высокого уровня в низкий вдвигают информацию в сдвиговый регистр 7 из блока памяти 5. По переходу тактового импульса из низкого уровня в высокий увеличивается значение кода адреса в генератор 3 адреса, и новая информация по следующему тактовому импульсу опять вдвигается из блока 5 памяти в сдвиговый регистр 7. Этот процесс вдвига и наращивания адреса продолжается до тех пор, пока блок 8 не опознает одну из допустимых кодовых комбинаций. Это ведет к тому, что на выходе блока 10 фиксации появляется высокий уровень сигнала. По переднему фронту этого сигнала в регистр 13 записывается информация с выходов блока 8. Импульс опознавания с выхода блока 10 фиксации попадает, кроме того, на вход формирователя 38 и на вход элемента задержки на элементах И-НЕ 39, диоде 42 и конденсаторе 43. Формирователь 38 по переднему фронту импульса опознавания формирует короткий импульс низкого уровня (длительностью около 300 нс). Этот импульс, пройдя через элемент И 25, сбрасывает триггер 27, и на его инверсном выходе устанавливается единица. Тем самым на управляющем входе сдвигового регистра 7 устанавливается единица и он подготовлен к параллельному занесению информации, а элемент И-НЕ 33 оказывается запертым, и импульсы сдвига не поступают на первый выход блока 2 управления. Импульс опознавания с задержанным передним фронтом (эта задержка необходима для того, чтобы на управляющем входе сдвигового регистра установилась единица), пройдя элемент И 34, записывает по перепаду из высокого уровня в низкий информацию в сдвиговый регистр 7. По заднему фронту этого импульса в триггер 27 записывается единица. Ноль с инверсного выхода этого триггера опять подготавливает сдвиговый регистр 7 к сдвигу информации вправо, а на втором выходе блока 2 управления появляются тактовые импульсы. При этом, так как триггер 35 является делителем на два, то на его инверсном выходе (по перепаду с низкого в высокий на его стробирующем входе) устанавливается высокий уровень, а на прямом - низкий уровень. Поэтому на выходе элемента ИЛИ 36 устанавливается высокий уровень, а на выходе элемента ИЛИ 37 - низкий уровень, и теперь уже в третье состояние переведены выходы блока 8 (т. е. выходы устанавливаются в состояние с высоким выходным сопротивлением), а в режиме опознавания кода разрешено работать блоку 9.

Механизм опознавания здесь аналогичен опознаванию кода при работе блока 8. Как только блок 9 опознает код времени, на выходе элемента И-НЕ 11 появляется высокий уровень сигнала, который, пройдя через элемент НЕ 41, попадает на вход формирователя 38. На его выходе появляется низкий уровень, который сбрасывает триггер 27. Единица с его инверсного выхода устанавливает сдвиговый регистр 7 в режим параллельного занесения информации, и на втором выходе блока 2 управления нет тактовых импульсов. По переднему фронту импульса опознавания с выхода элемента И-НЕ 11 в регистр 12 заносится код времени с выходов блока 9. Как только в реверсивном счетчике 15 закончится отсчет занесенного в него кода, на выходе обнуления этого счетчика появляется импульс низкого уровня, который, пройдя через элемент НЕ 16, передним фронтом заносит код в регистр 14 с выходов регистра 13, и на выходе ЦАП 17 устанавливается другое напряжение. Кроме того, импульс обнуления с выхода реверсивного счетчика 15 попадает на второй вход блока 2 управления. Пройдя через элемент НЕ 40 и элемент задержки на элементах И-НЕ 46, диоде 44, конденсаторе 45, он низким уровнем записывает в реверсивный счетчик 15 код с выходов регистра 12. В то же время импульс обнуления с второго входа блока 2 управления, пройдя через элемент И 34, записывает в регистр сдвига информацию с выходов блока 6 кода, а по заднему фронту этого импульса в триггер 27 записывается единица, и весь процесс сдвига, увеличения адреса и опознавания кодов блоков 8 и 9 продолжается.

Задержка импульса обнуления с выхода реверсивного счетчика 15 необходима для того, чтобы уверенно занести параллельный код в сдвиговый регистр. Если бы эта задержка отсутствовала, то импульс обнуления был очень коротким (порядка 40 нс). Как только блоком 8 будет опознан код и на его выходах появится код, который содержит единицы во всех разрядах, кроме самого старшего (фиг. 4), элемент И-НЕ 49 выставляет низкий уровень сигнала на своем выходе - это является сигналом "Конец фразы". Этот сигнал через третий вход блока 2 управления попадает на установочный вход триггера 32. Триггер 32 устанавливается, и ноль с его инверсного выхода запрещает прохождение тактовых импульсов через элемент И-НЕ 31, реверсивный счетчик 15 прекращает вычитание импульсов. Сигнал "Конец фразы" с третьего входа блока 2 управления, пройдя через элемент И 25, сбрасывает триггер 27, и с первого выхода блока 2 управления перестают поступать тактовые импульсы. Устройство готово к воспроизведению следующей фразы.

Следует отметить, что при максимальной частоте тактового генератора 28 10 кГц, тактового генератора 26 1 МГц и минимальном коде в реверсивном счетчике 15, равном единице, существуют ограничения на максимальное время опознавания кода Шеннона амплитуд и времени. Оно ограничено 100 мкс. По истечении этого времени коды должны быть опознаны, так как каждый следующий импульс обнуления заново запускает цикл сдвига и опознавания. Если преобразование не успеет завершиться в течение 10 мкс, то возможны искажения кодов в сдвиговом регистре 7, что ведет к искажению воспроизведения фразы. Выход ЦАП 17 для воспроизведения речевых фраз можно подключить через усилитель низкой частоты к громкоговорителю.

Связь устройства синтеза речевых сигналов с ЭВМ осуществляется при помощи дешифратора 1 (фиг. 2). Реализация его зависит от типа интерфейса, используемого в ЭВМ, с которым должно работать устройство. Основой дешифратора 1, работающего с магистральным интерфейсом МПИ по ОСТ 11.305.903-80, является селектор 18 адреса, который реализуется одной микросхемой К588ВТ1. Интерфейсная магистраль в этом случае содержит шестнадцать шин АД1...АД16 для передачи адреса и обмена данными между ЭВМ и периферийными устройствами, т.е. по шинам АДi поочередно подаются код "АДРЕС" и код "ДАННЫЕ". Кроме того, при обращении к периферийному устройству (т.е. по адресу, большему 160.0008) одновременно с адресом устройства ЭВМ вырабатывает сигнал ВУ. В дешифратор поступают из ЭВМ также управляющие сигналы интерфейса: сигнал СИА, указывающий, что ЭВМ выставила на шинах АДi адрес обмена, сигнал "ВЫВОД", указывающий, что ЭВМ выставила на шинах АДi данные для занесения по ранее заданному адресу, и сигнал "Ввод", по которому устройство должно выставить данные для ввода в ЭВМ. После приема данных из ЭВМ по сигналу "Вывод" или передачи данных в ЭВМ по сигналу "Ввод" дешифратор 1 передает в ЭВМ сигнал СИП, разрешающий ЭВМ начать новый цикл обмена данными. Активные уровни всех сигналов низкие. Следует отметить, что, адрес, передаваемый по магистрали МПИ в дешифратор 1, это код, идентифицирующий данное периферийное устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтеза речевых сигналов | 1991 |

|

SU1798814A1 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

Изобретение относится к речевой информатике и может быть использовано в различных системах речевого взаимодействия человека с ЭВМ. Цель - увеличение объема хранимой речевой информации при фиксированном объеме памяти. Сущность изобретения: устройство содержит дешифратор 1, блок 2 управления, генератор 3 адреса, элемент И 4, блок 8 памяти амплитуд, блок 9 памяти времени, блок 10 фиксации, элемент И - НЕ 11, регистр 12 времени, регистр 13 амплитуд, выходной регистр 14, реверсивный счетчик 15, элемент НЕ 16, ЦАП-17 и характеризуется увеличенным количеством речевой информации в том же объеме запоминающего устройства, расширенными функциональными возможностями за счет оперативного изменения информации в запоминающем устройстве. 1 табл., 9 ил.

УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ, содержащее генератов адреса и блок памяти, причем информационный вход генератора адреса соединен с адресным входом устройства, цифроаналоговый преобразователь, выход которого является выходом устройства, отличающееся тем, что, с целью увеличения объема хранимой речевой информации при фиксированном объеме памяти, в него введены блок управления, элемент И, сдвиговый регистр, блок кода, блок памяти амплитуд, блок памяти времени, блок фиксации, элемент И - НЕ, регистр времени, регистр амплитуды, выходной регистр, реверсивный счетчик, элемент НЕ, дешифратор адреса, информационный вход которого соединен с адресным входом устройства, информационный вход устройства соединен с входом данных блока памяти, адресный вход которого соединен с выходом генератора адреса, вход записи которого соединен с первым выходом дешифратора адреса, второй выход которого подключен к первому входу элемента И и к входу записи блока памяти, выход которого соединен с информационным входом последовательных данных сдвигового регистра, разрядные выходы которого подключены к адресным входам блока памяти амплитуд и блока памяти времени, вход разрешения которого соединен с первым выходом поля управления блока управления, второй выход поля управления которого подключен к второму входу элемента И и к первому стробирующему входу сдвигового регистра, вход управления которого соединен с третьим выходом поля управления блока управления, четвертый выход поля управления которого соединен с входом разрешения блока памяти времени, выход которого объединен с информационным входом регистра времени и входами элемента И - НЕ, выход которого объединен с первым входом логического условия блока управления и стробирующим входом регистра времени, выход которого соединен с информационным входом реверсивного счетчика, выход которого объединен с вторым входом логического условия блока управления и через элемент НЕ соединен со стробирующим входом выходного регистра, выход которого соединен с информационным входом цифроаналогового преобразователя, а информационный вход выходного регистра соединен с выходом регистра амплитуд, информационный вход которого подключен к выходу блока памяти амплитуд и информационному входу блока фиксации, первый выход которого соединен с третьим входом логического условия блока управления, а второй выход блока фиксации объединен со стробирующим входом регистра амплитуд и четвертым входом логического условия блока управления, пятый выход поля управления которого соединен с вычитающим входом реверсивного счетчика, вход записи которого соединен с шестым выходом поля управления блока управления, пятый вход логического условия которого соединен с третьим выходом дешифратора адреса, четвертый выход которого соединен с шестым входом логического условия блока управления, седьмой вход логического условия и седьмой выход поля управления которого подключены к входу пуска устройства и выходу признака конца синтезирования, выходы блока кода соединены с входами данных сдвигового регистра, а выход элемента И соединен с суммирующим входом генератора адреса, восьмой выход поля управления блока управления соединен с вторым стробирующим входом сдвигового регистра.

| Способ синтеза речевых сигналов и устройство для его осуществления | 1986 |

|

SU1408450A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1994-09-30—Публикация

1991-03-12—Подача